Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 48MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART, USB                             |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 34                                                                         |

| Program Memory Size        | 64KB (32K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 3.8K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.15V ~ 3.6V                                                               |

| Data Converters            | A/D 13x10b/12b                                                             |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

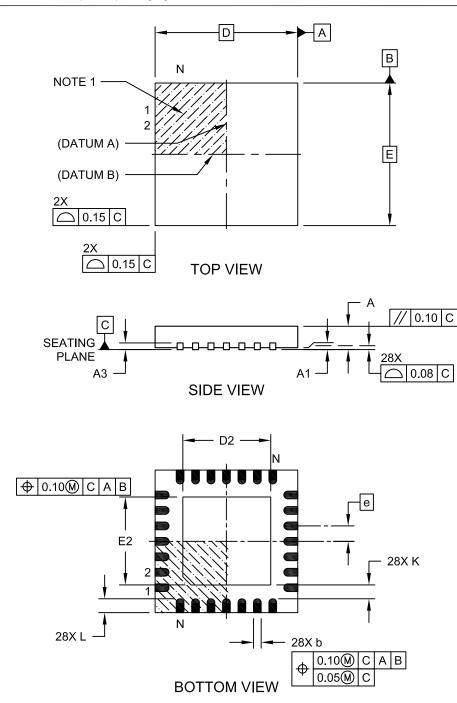

| Package / Case             | 44-VQFN Exposed Pad                                                        |

| Supplier Device Package    | 44-QFN (8x8)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f46j53-i-ml |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com**. We welcome your feedback.

### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Website at:

### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

Microchip's Worldwide Website; http://www.microchip.com

Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

### **Customer Notification System**

Register on our website at www.microchip.com to receive the most current information on all of our products.

|                                 | Pin Nu                     | ımber             |             |                        |                                                                                  |

|---------------------------------|----------------------------|-------------------|-------------|------------------------|----------------------------------------------------------------------------------|

| Pin Name                        | 28-SPDIP/<br>SSOP/<br>SOIC | 28-QFN            | Pin<br>Type | Buffer<br>Type         | Description                                                                      |

|                                 |                            |                   |             |                        | PORTB (continued)                                                                |

| RB4/CCP4/KBI0/SCK1/SCL1/        | 25 <sup>(2)</sup>          | 22 <sup>(2)</sup> |             |                        |                                                                                  |

| RP7                             |                            |                   | 1/0         |                        | Disting 1/0                                                                      |

| RB4<br>CCP4                     |                            |                   | 1/O<br>1/O  | TTL/DIG<br>ST/DIG      | Digital I/O.<br>Capture/Compare/PWM input/output.                                |

| KBIO                            |                            |                   | 1           | TTL                    | Interrupt-on-change pin.                                                         |

| SCK1                            |                            |                   | I/O         | ST/DIG                 | Synchronous serial clock input/output.                                           |

| SCL1                            |                            |                   | I/O         | I <sup>2</sup> C       | I <sup>2</sup> C clock input/output.                                             |

| RP7                             |                            |                   | I/O         | ST/DIG                 | Remappable Peripheral Pin 7 input/output.                                        |

| RB5/CCP5/KBI1/SDI1/SDA1/<br>RP8 | 26 <sup>(2)</sup>          | 23 <sup>(2)</sup> |             |                        |                                                                                  |

| RB5                             |                            |                   | I/O         | TTL/DIG                | Digital I/O.                                                                     |

| CCP5                            |                            |                   | I/O         | ST/DIG                 | Capture/Compare/PWM input/output.                                                |

| KBI1                            |                            |                   | I           | TTL                    | Interrupt-on-change pin.                                                         |

| SDI1<br>SDA1                    |                            |                   | I<br>I/O    | ST<br>I <sup>2</sup> C | SPI data input.                                                                  |

| RP8                             |                            |                   | 1/O         | ST/DIG                 | l <sup>2</sup> C data input/output.<br>Remappable Peripheral Pin 8 input/output. |

| RB6/CCP6/KBI2/PGC/RP9           | 27 <b>(2)</b>              | 24 <b>(2)</b>     | "0          | 01/210                 |                                                                                  |

| RB6                             | 2/( )                      | 2417              | I/O         | TTL/DIG                | Digital I/O.                                                                     |

| CCP6                            |                            |                   | 1/O         | ST/DIG                 | Capture/Compare/PWM input/output.                                                |

| KBI2                            |                            |                   | I           | TTL                    | Interrupt-on-change pin.                                                         |

| PGC                             |                            |                   |             | ST                     | ICSP™ clock input.                                                               |

| RP9                             |                            |                   | I/O         | ST/DIG                 | Remappable Peripheral Pin 9 input/output.                                        |

| RB7/CCP7/KBI3/PGD/RP10          | 28 <sup>(2)</sup>          | 25 <sup>(2)</sup> |             |                        |                                                                                  |

| RB7<br>CCP7                     |                            |                   | 1/O<br>1/O  | TTL/DIG<br>ST/DIG      | Digital I/O.<br>Capture/Compare/PWM input/output.                                |

| KBI3                            |                            |                   | 1/0         | TTL                    | Interrupt-on-change pin.                                                         |

| PGD                             |                            |                   | 1/O         | ST/DIG                 | In-Circuit Debugger and ICSP programming                                         |

|                                 |                            |                   |             |                        | data pin.                                                                        |

| RP10                            |                            |                   | I/O         | ST/DIG                 | Remappable Peripheral Pin 10 input/output.                                       |

| Legend: TTL = TTL compat        |                            |                   | lovala      |                        | MOS = CMOS compatible input or output                                            |

| ST = Schmitt Trig<br>I = Input  | ger input wi               |                   | ieveis      | Ar<br>O                | nalog = Analog input<br>= Output                                                 |

| P = Power                       |                            |                   |             | Ō                      | D = Open-Drain (no P diode to VDD)                                               |

| DIG = Digital output            | ıt                         |                   |             | 1 <sup>2</sup> (       | $C = Open-Drain, I^2C specific$                                                  |

### TABLE 1-3: PIC18F2XJ53 PINOUT I/O DESCRIPTIONS (CONTINUED)

**Note 1:** RA7 and RA6 will be disabled if OSC1 and OSC2 are used for the clock function.

2: 5.5V tolerant.

# 3.7 Effects of Power-Managed Modes on Various Clock Sources

When the PRI\_IDLE mode is selected, the designated primary oscillator continues to run without interruption. For all other power-managed modes, the oscillator using the OSC1 pin is disabled. Unless the USB module is enabled, the OSC1 pin (and OSC2 pin if used by the oscillator) will stop oscillating.

In secondary clock modes (SEC\_RUN and SEC\_I-DLE), the Timer1 oscillator is operating and providing the device clock. The Timer1 oscillator may also run in all power-managed modes if required to clock Timer1 or Timer3.

In internal oscillator modes (RC\_RUN and RC\_IDLE), the internal oscillator block provides the device clock source. The 31 kHz INTRC output can be used directly to provide the clock and may be enabled to support various special features regardless of the power-managed mode (see Section 28.2 "Watchdog Timer (WDT)", Section 28.4 "Two-Speed Start-up" and Section 28.5 "Fail-Safe Clock Monitor" for more information on WDT, FSCM and Two-Speed Start-up). The INTOSC output at 8 MHz may be used directly to clock the device or may be divided down by the postscaler. The INTOSC output is disabled if the clock is provided directly from the INTRC output.

If Sleep mode is selected, all clock sources which are no longer required are stopped. Since all the transistor switching currents have been stopped, Sleep mode achieves the lowest current consumption of the device (only leakage currents) outside of Deep Sleep. Sleep mode should not be invoked while the USB module is enabled and operating in Full-Power mode. Before Sleep mode is selected, the USB module should be put in the suspend state. This is accomplished by setting the SUSPND bit in the UCON register.

Enabling any on-chip feature that will operate during Sleep mode increases the current consumed during Sleep mode. The INTRC is required to support WDT operation. The Timer1 oscillator may be operating to support an RTC. Other features may be operating that do not require a device clock source (i.e., MSSP slave, PMP, INTx pins, etc.). Peripherals that may add significant current consumption are listed in Section 31.2 "DC Characteristics: Power-Down and Supply Current PIC18F47J53 Family (Industrial)".

# 3.8 Power-up Delays

Power-up delays are controlled by two timers so that no external Reset circuitry is required for most applications. The delays ensure that the device is kept in Reset until the device power supply is stable under normal circumstances and the primary clock is operating and stable. For additional information on power-up delays, see **Section 5.6 "Power-up Timer (PWRT)**".

The first timer is the Power-up Timer (PWRT), which provides a fixed delay on power-up (parameter 33, Table 31-14).

The second timer is the Oscillator Start-up Timer (OST), intended to keep the chip in Reset until the crystal oscillator is stable (HS mode). The OST does this by counting 1024 oscillator cycles before allowing the oscillator to clock the device.

There is a delay of interval, TCSD (parameter 38, Table 31-14), following POR, while the controller becomes ready to execute instructions. This delay runs concurrently with any other delays. This may be the only delay that occurs when any of the internal oscillator or EC modes are used as the primary clock source.

### 4.6.5 DEEP SLEEP BROWN-OUT RESET (DSBOR)

The Deep Sleep module contains a dedicated Deep Sleep BOR (DSBOR) circuit. This circuit may be optionally enabled through the DSBOREN Configuration bit.

The DSBOR circuit monitors the VDD supply rail voltage. The behavior of the DSBOR circuit is described in **Section 5.4 "Brown-out Reset (BOR)**".

### 4.6.6 RTCC PERIPHERAL AND DEEP SLEEP

The RTCC can operate uninterrupted during Deep Sleep mode. It can wake the device from Deep Sleep by configuring an alarm.

The RTCC clock source is configured with the RTCOSC bit (CONFIG3L<1>). The available reference clock sources are the INTRC and T1OSC/T1CKI. If the INTRC is used, the RTCC accuracy will directly depend on the INTRC tolerance.For more information on configuring the RTCC peripheral, see Section 17.0 "Real-Time Clock and Calendar (RTCC)".

# 4.6.7 TYPICAL DEEP SLEEP SEQUENCE

This section gives the typical sequence for using the Deep Sleep mode. Optional steps are indicated and additional information is given in notes at the end of the procedure.

- 1. Enable DSWDT (optional).<sup>(1)</sup>

- 2. Configure the DSWDT clock source (optional).<sup>(2)</sup>

- 3. Enable DSBOR (optional).<sup>(1)</sup>

- 4. Enable RTCC (optional).(3)

- 5. Configure the RTCC peripheral (optional).<sup>(3)</sup>

- 6. Configure the ULPWU peripheral (optional).<sup>(4)</sup>

- 7. Enable the INTO Interrupt (optional).

- 8. Context save SRAM data by writing to the DSGPR0 and DSGPR1 registers (optional).

- 9. Set the REGSLP bit (WDTCON<7>) and clear the IDLEN bit (OSCCON<7>).

- 10. If using an RTCC alarm for wake-up, wait until the RTCSYNC bit (RTCCFG<4>) is clear.

- Enter Deep Sleep mode by setting the DSEN bit (DSCONH<7>) and issuing a SLEEP instruction. These two instructions must be executed back to back.

- 12. Once a wake-up event occurs, the device will perform a POR Reset sequence. Code execution resumes at the device's Reset vector.

- Determine if the device exited Deep Sleep by reading the Deep Sleep bit, DS (WDTCON<3>). This bit will be set if there was an exit from Deep Sleep mode.

- 14. Clear the Deep Sleep bit, DS (WDTCON<3>).

- 15. Determine the wake-up source by reading the DSWAKEH and DSWAKEL registers.

- Determine if a DSBOR event occurred during Deep Sleep mode by reading the DSBOR bit (DSCONL<1>).

- 17. Read the DSGPR0 and DSGPR1 context save registers (optional).

- 18. Clear the RELEASE bit (DSCONL<0>).

- Note 1: DSWDT and DSBOR are enabled through the devices' Configuration bits. For more information, see Section 28.1 "Configuration Bits".

- 2: The DSWDT and RTCC clock sources are selected through the devices' Configuration bits. For more information, see Section 28.1 "Configuration Bits".

- 3: For more information, see Section 17.0 "Real-Time Clock and Calendar (RTCC)".

- 4: For more information on configuring this peripheral, see Section 4.7 "Ultra Low-Power Wake-up".

# 4.6.8 DEEP SLEEP FAULT DETECTION

If during Deep Sleep, the device is subjected to unusual operating conditions, such as an Electrostatic Discharge (ESD) event, it is possible that internal circuit states used by the Deep Sleep module could become corrupted. If this were to happen, the device may exhibit unexpected behavior, such as a failure to wake back up.

In order to prevent this type of scenario from occurring, the Deep Sleep module includes automatic self-monitoring capability. During Deep Sleep, critical internal nodes are continuously monitored in order to detect possible Fault conditions (which would not ordinarily occur). If a Fault condition is detected, the circuitry will set the DSFLT status bit (DSWAKEL<7>) and automatically wake the microcontroller from Deep Sleep, causing a POR Reset.

During Deep Sleep, the Fault detection circuitry is always enabled and does not require any specific configuration prior to entering Deep Sleep.

### REGISTER 10-14: RPINR12: PERIPHERAL PIN SELECT INPUT REGISTER 12 (BANKED EF2h)

| U-0   | U-0 | U-0 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|-------|-----|-----|-------|-------|-------|-------|-------|

| —     | —   | —   | T1GR4 | T1GR3 | T1GR2 | T1GR1 | T1GR0 |

| bit 7 |     |     |       |       |       |       | bit 0 |

| Legend:           | $R/\overline{W}$ = Readable bit, Writable bit if IOLOCK = 0 |                                    |                    |  |  |

|-------------------|-------------------------------------------------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit                                            | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set                                            | '0' = Bit is cleared               | x = Bit is unknown |  |  |

### bit 7-5 Unimplemented: Read as '0'

bit 4-0 **T1GR<4:0>:** Timer1 Gate Input (T1G) to the Corresponding RPn Pin bits

### REGISTER 10-15: RPINR13: PERIPHERAL PIN SELECT INPUT REGISTER 13 (BANKED EF3h)

| U-0   | U-0 | U-0 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|-------|-----|-----|-------|-------|-------|-------|-------|

| —     | —   | —   | T3GR4 | T3GR3 | T3GR2 | T3GR1 | T3GR0 |

| bit 7 |     |     |       |       |       |       | bit 0 |

| Legend:           | R/W = Readable bit, | $R/\overline{W}$ = Readable bit, Writable bit if IOLOCK = 0 |                                    |  |  |  |

|-------------------|---------------------|-------------------------------------------------------------|------------------------------------|--|--|--|

| R = Readable bit  | W = Writable bit    | U = Unimplemented bit                                       | U = Unimplemented bit, read as '0' |  |  |  |

| -n = Value at POR | '1' = Bit is set    | '0' = Bit is cleared                                        | x = Bit is unknown                 |  |  |  |

bit 4-0 T3GR<4:0>: Timer3 Gate Input (T3G) to the Corresponding RPn Pin bits

### REGISTER 10-16: RPINR14: PERIPHERAL PIN SELECT INPUT REGISTER 14 (BANKED EF4h)

| U-0   | U-0 | U-0 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|-------|-----|-----|-------|-------|-------|-------|-------|

| —     | —   | —   | T5GR4 | T5GR3 | T5GR2 | T5GR1 | T5GR0 |

| bit 7 |     |     |       |       |       |       | bit 0 |

| Legend:           | R/W = Readable bit, Writa | $R/\overline{W}$ = Readable bit, Writable bit if IOLOCK = 0 |                    |  |  |  |

|-------------------|---------------------------|-------------------------------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit          | U = Unimplemented bit, read as '0'                          |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set          | '0' = Bit is cleared                                        | x = Bit is unknown |  |  |  |

bit 7-5 Unimplemented: Read as '0'

bit 4-0 T5GR<4:0>: Timer5 Gate Input (T5G) to the Corresponding RPn Pin bits

### REGISTER 10-21: RPINR22: PERIPHERAL PIN SELECT INPUT REGISTER 22 (BANKED EFDh)

| U-0   | U-0 | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|-------|-----|-----|--------|--------|--------|--------|--------|

| —     | —   |     | SCK2R4 | SCK2R3 | SCK2R2 | SCK2R1 | SCK2R0 |

| bit 7 |     |     |        |        |        |        | bit 0  |

| Legend:           | R/W = Readable bit, Wri | $R/\overline{W}$ = Readable bit, Writable bit if IOLOCK = 0 |                                    |  |  |  |

|-------------------|-------------------------|-------------------------------------------------------------|------------------------------------|--|--|--|

| R = Readable bit  | W = Writable bit        | U = Unimplemented bit                                       | U = Unimplemented bit, read as '0' |  |  |  |

| -n = Value at POR | '1' = Bit is set        | '0' = Bit is cleared                                        | x = Bit is unknown                 |  |  |  |

### bit 7-5 Unimplemented: Read as '0'

bit 4-0 SCK2R<4:0>: Assign SPI2 Clock Input (SCK2) to the Corresponding RPn Pin bits

### REGISTER 10-22: RPINR23: PERIPHERAL PIN SELECT INPUT REGISTER 23 (BANKED EFEh)

| U-0   | U-0 | U-0 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|-------|-----|-----|-------|-------|-------|-------|-------|

| —     | —   | —   | SS2R4 | SS2R3 | SS2R2 | SS2R1 | SS2R0 |

| bit 7 |     |     |       |       |       |       | bit 0 |

| Legend:           | R/W = Readable bit, V | $R/\overline{W}$ = Readable bit, Writable bit if IOLOCK = 0 |                    |  |  |  |

|-------------------|-----------------------|-------------------------------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit      | U = Unimplemented bit,                                      | , read as '0'      |  |  |  |

| -n = Value at POR | '1' = Bit is set      | '0' = Bit is cleared                                        | x = Bit is unknown |  |  |  |

### bit 7-5 Unimplemented: Read as '0'

bit 4-0 SS2R<4:0>: Assign SPI2 Slave Select Input (SS2) to the Corresponding RPn Pin bits

### REGISTER 10-23: RPINR24: PERIPHERAL PIN SELECT INPUT REGISTER 24 (BANKED EFFh)

| U-0   | U-0 | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|-----|--------|--------|--------|--------|--------|

| —     | —   | —   | OCFAR4 | OCFAR3 | OCFAR2 | OCFAR1 | OCFAR0 |

| bit 7 |     |     |        |        |        |        | bit 0  |

| Legend:           | $R/\overline{W}$ = Readable bit, V | $R/\overline{W}$ = Readable bit, Writable bit if IOLOCK = 0 |                                    |  |  |  |

|-------------------|------------------------------------|-------------------------------------------------------------|------------------------------------|--|--|--|

| R = Readable bit  | W = Writable bit                   | U = Unimplemented bit,                                      | U = Unimplemented bit, read as '0' |  |  |  |

| -n = Value at POR | '1' = Bit is set                   | '0' = Bit is cleared                                        | x = Bit is unknown                 |  |  |  |

bit 7-5 Unimplemented: Read as '0'

bit 4-0 OCFAR<4:0>: Assign PWM Fault Input (FLT0) to the Corresponding RPn Pin bits

# 14.0 TIMER2 MODULE

The Timer2 module incorporates the following features:

- 8-bit Timer and Period registers (TMR2 and PR2, respectively)

- Readable and writable (both registers)

- Software programmable prescaler (1:1, 1:4 and 1:16)

- Software programmable postscaler (1:1 through 1:16)

- Interrupt on TMR2 to PR2 match

- Optional use as the shift clock for the MSSP modules

The module is controlled through the T2CON register (Register 14-1) which enables or disables the timer and configures the prescaler and postscaler. Timer2 can be shut off by clearing control bit, TMR2ON (T2CON<2>), to minimize power consumption.

A simplified block diagram of the module is shown in Figure 14-1.

# 14.1 Timer2 Operation

In normal operation, TMR2 is incremented from 00h on each clock (Fosc/4). A 4-bit counter/prescaler on the clock input gives direct input, divide-by-4 and divide-by-16 prescale options. These are selected by the prescaler control bits, T2CKPS<1:0> (T2CON<1:0>). The value of TMR2 is compared to that of the Period register, PR2, on each clock cycle. When the two values match, the comparator generates a match signal as the timer output. This signal also resets the value of TMR2 to 00h on the next cycle and drives the output counter/postscaler (see Section 14.2 "Timer2 Interrupt").

The TMR2 and PR2 registers are both directly readable and writable. The TMR2 register is cleared on any device Reset, while the PR2 register initializes at FFh. Both the prescaler and postscaler counters are cleared on the following events:

- a write to the TMR2 register

- a write to the T2CON register

- any device Reset (Power-on Reset (POR), MCLR Reset, Watchdog Timer Reset (WDTR) or Brown-out Reset (BOR))

TMR2 is not cleared when T2CON is written.

### REGISTER 14-1: T2CON: TIMER2 CONTROL REGISTER (ACCESS FCAh)

| U-0   | R/W-0    | R/W-0    | R/W-0    | R/W-0    | R/W-0  | R/W-0   | R/W-0   |

|-------|----------|----------|----------|----------|--------|---------|---------|

| —     | T2OUTPS3 | T2OUTPS2 | T2OUTPS1 | T2OUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 |

| bit 7 |          |          |          |          |        |         | bit 0   |

| Legend:           |                  |                                                     |                    |  |  |

|-------------------|------------------|-----------------------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | W = Writable bit U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared                                | x = Bit is unknown |  |  |

| bit 7   | Unimplemented: Read as '0'                        |

|---------|---------------------------------------------------|

| bit 6-3 | T2OUTPS<3:0>: Timer2 Output Postscale Select bits |

|         | 0000 = 1:1 Postscale                              |

|         | 0001 = 1:2 Postscale                              |

|         | •                                                 |

|         | •                                                 |

|         | •                                                 |

|         | 1111 = 1:16 Postscale                             |

| bit 2   | TMR2ON: Timer2 On bit                             |

|         | 1 = Timer2 is on                                  |

|         | 0 = Timer2 is off                                 |

| bit 1-0 | T2CKPS<1:0>: Timer2 Clock Prescale Select bits    |

|         | 00 = Prescaler is 1                               |

|         | 01 = Prescaler is 4                               |

|         | 10 = Prescaler is 16                              |

|         |                                                   |

. .. -

# PIC18F47J53

# REGISTER 18-4: CCPRxL: CCP4-10 PERIOD LOW BYTE REGISTER (4, BANKED F13h; 5, F10h; 6, F0Dh; 7, F0Ah; 8, F07h; 9, F04h; 10, F01h)

| R/W-x   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| CCPRxL7 | CCPRxL6 | CCPRxL5 | CCPRxL4 | CCPRxL3 | CCPRxL2 | CCPRxL1 | CCPRxL0 |

| bit 7   |         |         |         |         |         |         | bit 0   |

|         |         |         |         |         |         |         |         |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 7-0 CCPRxL<7:0>: CCPx Period Register Low Byte bits Capture Mode: Capture register low byte Compare Mode: Compare register low byte PWM Mode: PWM Period register low byte

# REGISTER 18-5: CCPRxH: CCP4-10 PERIOD HIGH BYTE REGISTER (4, BANKED F14h; 5, F11h; 6, F0Eh; 7, F0Bh; 8, F08h; 9, F05h; 10, F02h)

| R/W-x   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| CCPRxH7 | CCPRxH6 | CCPRxH5 | CCPRxH4 | CCPRxH3 | CCPRxH2 | CCPRxH1 | CCPRxH0 |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:                                                              |                  |                      |                    |  |

|----------------------------------------------------------------------|------------------|----------------------|--------------------|--|

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                  |                      |                    |  |

| -n = Value at POR                                                    | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |  |

bit 7-0 **CCPRxH<7:0>:** CCPx Period Register High Byte bits Capture Mode: Capture register high byte Compare Mode: Compare register high byte PWM Mode: PWM Period register high byte

#### 20.2 **Control Registers**

Each MSSP module has three associated control registers. These include a status register (SSPxSTAT) and two control registers (SSPxCON1 and SSPxCON2). The use of these registers and their individual Configuration bits differs significantly depending on whether the MSSP module is operated in SPI or I<sup>2</sup>C mode.

Additional details are provided under the individual sections.

Note: In devices with more than one MSSP module, it is very important to pay close attention to the SSPxCON register names. SSP1CON1 and SSP1CON2 control different operational aspects of the same module, while SSP1CON1 and SSP2CON1 control the same features for two different modules.

#### 20.3 **SPI Mode**

The SPI mode allows 8 bits of data to be synchronously transmitted and received simultaneously. All four modes of SPI are supported.

When MSSP2 is used in SPI mode, it can optionally be configured to work with the SPI DMA submodule described in Section 20.4 "SPI DMA Module".

To accomplish communication, typically three pins are used:

- Serial Data Out (SDOx) RC7/CCP10/RX1/DT1/SDO1/RP18 or SDO2/Remappable

- · Serial Data In (SDIx) -RB5/CCP5/KBI1/SDI1/SDA1/RP8 or SDI2/Remappable

- Serial Clock (SCKx) RB4/CCP4/KBI0/SCK1/SCL1/RP7 or SCK2/Remappable

Additionally, a fourth pin may be used when in a Slave mode of operation:

Slave Select (SSx) – RA5/AN4/C1INC/SS1/ HLVDIN/RCV/RP2 or SS2/Remappable

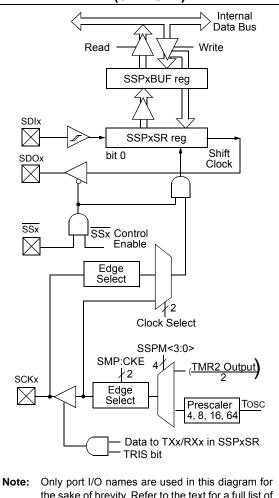

Figure 20-1 depicts the block diagram of the MSSP module when operating in SPI mode.

#### **FIGURE 20-1: MSSPx BLOCK DIAGRAM** (SPI MODE)

the sake of brevity. Refer to the text for a full list of multiplexed functions.

| R/W-0                       | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | R/W-0                                                                                                                                                   | R/W-0                                                                                                | R/W-0                                                                  | R/W-0                                                              | R/W-0                   | R/W-0                |

|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|--------------------------------------------------------------------|-------------------------|----------------------|

| WCOL                        | SSPOV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | SSPEN <sup>(1)</sup>                                                                                                                                    | CKP                                                                                                  | SSPM3 <sup>(2)</sup>                                                   | SSPM2 <sup>(2)</sup>                                               | SSPM1 <sup>(2)</sup>    | SSPM0 <sup>(2)</sup> |

| bit 7                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                         |                                                                                                      |                                                                        |                                                                    |                         | bit                  |

| lagandi                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                         |                                                                                                      |                                                                        |                                                                    |                         |                      |

| <b>Legend:</b><br>R = Reada | able bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | W = Writable b                                                                                                                                          | bit                                                                                                  | U = Unimplem                                                           | ented bit, read                                                    | l as '0'                |                      |

| -n = Value                  | at POR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | '1' = Bit is set                                                                                                                                        |                                                                                                      | '0' = Bit is clea                                                      | ared                                                               | x = Bit is unkr         | iown                 |

| bit 7                       | <u>In Master Tra</u><br>1 = A write                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | e Collision Detec<br>ansmit mode:<br>to the SSPxBUI<br>ssion to be starte<br>sion                                                                       | <sup>=</sup> register wa                                                                             |                                                                        |                                                                    | nditions were i         | not valid for        |

|                             | software<br>0 = No collis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | PxBUF register is<br>e)<br>sion<br><u>10de (Master or S</u>                                                                                             |                                                                                                      |                                                                        | itting the previ                                                   | ous word (mus           | t be cleared         |

| oit 6                       | <b>SSPOV:</b> Rec<br>In Receive m<br>1 = A byte is<br>software                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ceive Overflow In<br>node:<br>s received while t                                                                                                        |                                                                                                      | register is still h                                                    | olding the prev                                                    | <i>r</i> ious byte (mus | t be cleared         |

|                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | <u>node:</u><br>n't care" bit in Tra                                                                                                                    |                                                                                                      |                                                                        |                                                                    |                         |                      |

| oit 5                       | 1 = Enables                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ster Synchronous<br>the serial port ar<br>the serial port a                                                                                             | nd configures                                                                                        | the SDAx and S                                                         |                                                                    | e serial port pi        | าร                   |

| bit 4                       | CKP: SCKx<br>In Slave mod<br>1 = Releases<br>0 = Holds clo<br>In Master mo<br>Unused in th                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Release Control<br><u>de:</u><br>s clock<br>ock low (clock str<br><u>ode:</u><br>is mode.                                                               | bit<br>etch); used to                                                                                | o ensure data se                                                       | tup time                                                           |                         |                      |

| bit 3-0                     | $1111 = I^{2}C \le 1110 = I^{2}C \le 1011 = I^{2}C $ | Master Synchro<br>Slave mode, 10-b<br>Slave mode, 7-bi<br>Firmware Control<br>the SSPxMSK t<br>Master mode, clo<br>Slave mode, 10-b<br>Slave mode, 7-bi | bit address wit<br>t address with<br>led Master m<br>register at the<br>ick = Fosc/(4<br>bit address | th Start and Stop<br>Start and Stop<br>ode (slave Idle)<br>SSPxADD SFR | o bit interrupts<br>bit interrupts e<br>R address <sup>(3,4)</sup> |                         |                      |

| 2:                          | When enabled, t<br>Bit combinations<br>When SSPM<3:0<br>SSPxMSK regist                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | not specifically l<br>0> = 1001, any r<br>ter.                                                                                                          | isted here are<br>eads or write                                                                      | e either reserved<br>s to the SSPxAE                                   | l or implemente<br>DD SFR addres                                   |                         | -                    |

|                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                         |                                                                                                      | Maaking maada ia                                                       | a ala ata al (NACCO                                                |                         |                      |

4: This mode is only available when 7-Bit Address Masking mode is selected (MSSPMSK Configuration bit is '1').

### 20.5.3.4 7-Bit Address Masking Mode

Unlike 5-Bit Address Masking mode, 7-Bit Address Masking mode uses a mask of up to eight bits (in 10-bit addressing) to define a range of addresses than can be Acknowledged, using the lowest bits of the incoming address. This allows the module to Acknowledge up to 127 different addresses with 7-bit addressing, or 255 with 10-bit addressing (see Example 20-4). This mode is the default configuration of the module and is selected when MSSPMSK is unprogrammed ('1').

The address mask for 7-Bit Address Masking mode is stored in the SSPxMSK register, instead of the SSPx-CON2 register. SSPxMSK is a separate, hardware register within the module, but it is not directly addressable. Instead, it shares an address in the SFR space with the SSPxADD register. To access the SSPxMSK register, it is necessary to select MSSP mode, '1001' (SSPCON1<3:0> = 1001), and then read or write to the location of SSPxADD.

To use 7-Bit Address Masking mode, it is necessary to initialize SSPxMSK with a value before selecting the  $I^2C$  Slave Addressing mode. Thus, the required sequence of events is:

- 1. Select SSPxMSK Access mode (SSPx-CON2<3:0> = 1001).

- 2. Write the mask value to the appropriate SSPxADD register address (FC8h for MSSP1, F6Eh for MSSP2).

- Set the appropriate I<sup>2</sup>C Slave mode (SSPx-CON2<3:0> = 0111 for 10-bit addressing, 0110 for 7-bit addressing).

Setting or clearing mask bits in SSPxMSK behaves in the opposite manner of the ADMSK bits in 5-Bit Address Masking mode. That is, clearing a bit in SSPxMSK causes the corresponding address bit to be masked; setting the bit requires a match in that position. SSPxMSK resets to all '1's upon any Reset condition, and therefore, has no effect on the standard MSSP operation until written with a mask value.

With 7-Bit Address Masking mode, the SSPxMSK<7:1> bits mask the corresponding address bits in the SSPxADD register. For any SSPxMSK bits that are active (SSPxMSK<n> = 0), the corresponding SSPxADD address bit is ignored (SSPxADD<n> = x). For the module to issue an address Acknowledge, it is sufficient to match only on addresses that do not have an active address mask.

With 10-Bit Address Masking mode, SSPxMSK<7:0> bits mask the corresponding address bits in the SSPxADD register. For any SSPxMSK bits that are active (= 0), the corresponding SSPxADD address bit is ignored (SSPxADD<n> = x).

Note: The two MSbs of the address are not affected by address masking.

# EXAMPLE 20-4: ADDRESS MASKING EXAMPLES IN 7-BIT MASKING MODE

### 7-Bit Addressing:

SSPxADD<7:1>= 1010 000

SSPxMSK<7:1>= 1111 001

Addresses Acknowledged = A8h, A6h, A4h, A0h

### 10-Bit Addressing:

SSPxADD<7:0> = 1010 0000 (the two MSbs are ignored in this example since they are not affected)

SSPxMSK<5:1> = 1111 0

Addresses Acknowledged = A8h, A6h, A4h, A0h

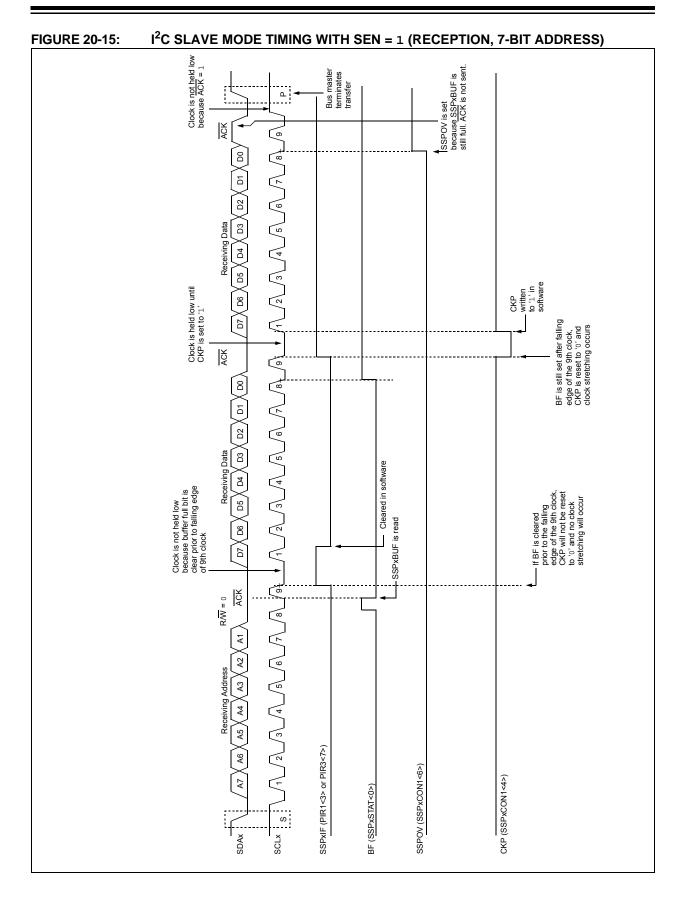

### 20.5.3.5 Reception

When the R/W bit of the address byte is clear and an address match occurs, the R/W bit of the SSPxSTAT register is cleared. The received address is loaded into the SSPxBUF register and the SDAx line is held low (ACK).

When the address byte overflow condition exists, then the no Acknowledge (ACK) pulse is given. An overflow condition is defined as either bit, BF (SSPxSTAT<0>), is set or bit, SSPOV (SSPxCON1<6>), is set.

An MSSP interrupt is generated for each data transfer byte. The interrupt flag bit, SSPxIF, must be cleared in software. The SSPxSTAT register is used to determine the status of the byte.

If SEN is enabled (SSPxCON2<0> = 1), SCLx will be held low (clock stretch) following each data transfer. The clock must be released by setting bit, CKP (SSPx-CON1<4>). See **Section 20.5.4** "**Clock Stretching**" for more details.

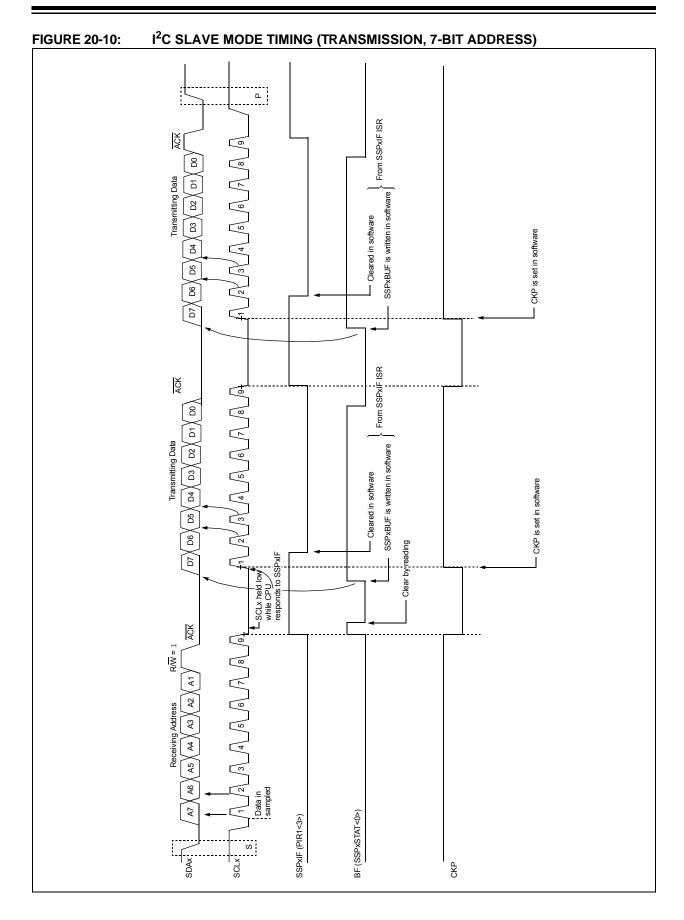

# 20.5.3.6 Transmission

When the R/W bit of the incoming address byte is set and an address match occurs, the R/W bit of the SSPxSTAT register is set. The received address is loaded into the SSPxBUF register. The ACK pulse will be sent on the ninth bit and pin, SCLx, is held low regardless of SEN (see Section 20.5.4 "Clock Stretching" for more details). By stretching the clock, the master will be unable to assert another clock pulse until the slave is done preparing the transmit data. The transmit data must be loaded into the SSPxBUF register, which also loads the SSPxSR register. Then, the SCLx pin should be enabled by setting bit, CKP (SSPxCON1<4>). The eight data bits are shifted out on the falling edge of the SCLx input. This ensures that the SDAx signal is valid during the SCLx high time (Figure 20-10).

The  $\overline{ACK}$  pulse from the master-receiver is latched on the rising edge of the ninth SCLx input pulse. If the SDAx line is high (not  $\overline{ACK}$ ), then the data transfer is complete. In this case, when the  $\overline{ACK}$  is latched by the slave, the slave logic is reset (resets the SSPxSTAT register) and the slave monitors for another occurrence of the Start bit. If the SDAx line was low ( $\overline{ACK}$ ), the next transmit data must be loaded into the SSPxBUF register. Again, the SCLx pin must be enabled by setting bit, CKP.

An MSSP interrupt is generated for each data transfer byte. The SSPxIF bit must be cleared in software and the SSPxSTAT register is used to determine the status of the byte. The SSPxIF bit is set on the falling edge of the ninth clock pulse.