Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 48MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART, USB                             |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 34                                                                         |

| Program Memory Size        | 128KB (64K x 16)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 3.8K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.15V ~ 3.6V                                                               |

| Data Converters            | A/D 13x10b/12b                                                             |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-VQFN Exposed Pad                                                        |

| Supplier Device Package    | 44-QFN (8x8)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f47j53-i-ml |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Input Oscillator<br>Frequency | PLL Division<br>(PLLDIV<2:0>) | Clock Mode<br>(FOSC<2:0>) | MCU Clock Division<br>(CPDIV<1:0>) | Microcontroller<br>Clock Frequency |

|-------------------------------|-------------------------------|---------------------------|------------------------------------|------------------------------------|

|                               |                               |                           | None (11)                          | 48 MHz                             |

| 48 MHz                        | N1/A                          | 50                        | ÷2(10)                             | 24 MHz                             |

|                               | N/A                           | EC                        | ÷3(01)                             | 16 MHz                             |

|                               |                               |                           | ÷6 (00)                            | 8 MHz                              |

|                               |                               |                           | None (11)                          | 48 MHz                             |

|                               | 10 (000)                      | FORM                      | ÷2(10)                             | 24 MHz                             |

| 48 MHz                        | ÷12 (000)                     | ECPLL                     | ÷3(01)                             | 16 MHz                             |

|                               |                               |                           | ÷6 (00)                            | 8 MHz                              |

|                               |                               |                           | None (11)                          | 48 MHz                             |

|                               | 10 (001)                      | FORM                      | ÷2(10)                             | 24 MHz                             |

| 40 MHz                        | ÷10(001)                      | ECPLL                     | ÷3(01)                             | 16 MHz                             |

|                               |                               |                           | ÷6 (00)                            | 8 MHz                              |

|                               |                               |                           | None (11)                          | 48 MHz                             |

|                               | 0 (00.0)                      | FORM                      | ÷2 (10)                            | 24 MHz                             |

| 24 MHz                        | ÷6 (010)                      | ECPLL                     | ÷3(01)                             | 16 MHz                             |

|                               |                               |                           | ÷6 (00)                            | 8 MHz                              |

| 24 MHz                        | N/A                           | EC <sup>(1)</sup>         | None (11)                          | 24 MHz                             |

|                               |                               |                           | ÷2 (10)                            | 12 MHz                             |

|                               |                               |                           | ÷3 (01)                            | 8 MHz                              |

|                               |                               |                           | ÷6 (00)                            | 4 MHz                              |

|                               | ÷5 (011)                      | ECPLL                     | None (11)                          | 48 MHz                             |

|                               |                               |                           | ÷2 (10)                            | 24 MHz                             |

| 20 MHz                        |                               |                           | ÷3(01)                             | 16 MHz                             |

|                               |                               |                           | ÷6 (00)                            | 8 MHz                              |

|                               |                               |                           | None (11)                          | 48 MHz                             |

|                               |                               |                           | ÷2 (10)                            | 24 MHz                             |

| 16 MHz                        | ÷4 (100)                      | HSPLL, ECPLL              | ÷3 (01)                            | 16 MHz                             |

|                               |                               |                           | ÷6 (00)                            | 8 MHz                              |

|                               |                               |                           | None (11)                          | 48 MHz                             |

|                               | 0 (2.22.)                     |                           | ÷2 (10)                            | 24 MHz                             |

| 12 MHz                        | ÷3(101)                       | HSPLL, ECPLL              | ÷3(01)                             | 16 MHz                             |

|                               |                               |                           | ÷6 (00)                            | 8 MHz                              |

|                               |                               |                           | None (11)                          | 48 MHz                             |

| 0.1411-                       | 0 (5 5 5)                     | HSPLL, ECPLL,             | ÷2 (10)                            | 24 MHz                             |

| 8 MHz                         | ÷2 (110)                      | INTOSCPLL/<br>INTOSCPLLO  | ÷3(01)                             | 16 MHz                             |

|                               |                               |                           | ÷6 (00)                            | 8 MHz                              |

|                               |                               |                           | None (11)                          | 48 MHz                             |

| 4.8411                        | 4 ()                          |                           | ÷2 (10)                            | 24 MHz                             |

| 4 MHz                         | ÷ <b>1</b> (111)              | HSPLL, ECPLL              | ÷3(01)                             | 16 MHz                             |

|                               |                               |                           | ÷6 (00)                            | 8 MHz                              |

| <b>TABLE 3-5:</b> | OSCILLATOR CONFIGURATION OPTIONS FOR USB OPERATION |

|-------------------|----------------------------------------------------|

|                   |                                                    |

Note 1: The 24 MHz EC mode (without PLL) is only compatible with low-speed USB. Full-speed USB requires a 48 MHz system clock.

# 5.7 Reset State of Registers

Most registers are unaffected by a Reset. Their status is unknown on POR and unchanged by all other Resets. The other registers are forced to a "Reset state" depending on the type of Reset that occurred.

Most registers are not affected by a WDT wake-up, since this is viewed as the resumption of normal operation. Status bits from the RCON register (CM, RI,

TO, PD, POR and BOR) are set or cleared differently in different Reset situations, as indicated in Table 5-1. These bits are used in software to determine the nature of the Reset.

Table 5-2 describes the Reset states for all of the Special Function Registers. These are categorized by POR and BOR, MCLR and WDT Resets and WDT wake-ups.

| TABLE 5-1: | STATUS BITS, THEIR SIGNIFICANCE AND THE INITIALIZATION CONDITION FOR |

|------------|----------------------------------------------------------------------|

|            | RCON REGISTER                                                        |

|                                                                 | Program                |    |    | RCON | Register |     |     | STKPTR Register |        |

|-----------------------------------------------------------------|------------------------|----|----|------|----------|-----|-----|-----------------|--------|

| Condition                                                       | Counter <sup>(1)</sup> | CM | RI | ТО   | PD       | POR | BOR | STKFUL          | STKUNF |

| Power-on Reset                                                  | 0000h                  | 1  | 1  | 1    | 1        | 0   | 0   | 0               | 0      |

| RESET instruction                                               | 0000h                  | u  | 0  | u    | u        | u   | u   | u               | u      |

| Brown-out Reset                                                 | 0000h                  | 1  | 1  | 1    | 1        | u   | 0   | u               | u      |

| Configuration Mismatch Reset                                    | 0000h                  | 0  | u  | u    | u        | u   | u   | u               | u      |

| MCLR Reset during power-managed Run modes                       | 0000h                  | u  | u  | 1    | u        | u   | u   | u               | u      |

| MCLR Reset during<br>power-managed Idle modes and<br>Sleep mode | 0000h                  | u  | u  | 1    | 0        | u   | u   | u               | u      |

| MCLR Reset during full-power execution                          | 0000h                  | u  | u  | u    | u        | u   | u   | u               | u      |

| Stack Full Reset (STVREN = 1)                                   | 0000h                  | u  | u  | u    | u        | u   | u   | 1               | u      |

| Stack Underflow Reset<br>(STVREN = 1)                           | 0000h                  | u  | u  | u    | u        | u   | u   | u               | 1      |

| Stack Underflow Error (not an actual Reset, STVREN = 0)         | 0000h                  | u  | u  | u    | u        | u   | u   | u               | 1      |

| WDT time-out during full-power<br>or power-managed Run modes    | 0000h                  | u  | u  | 0    | u        | u   | u   | u               | u      |

| WDT time-out during<br>power-managed Idle or Sleep<br>modes     | PC + 2                 | u  | u  | 0    | 0        | u   | u   | u               | u      |

| Interrupt exit from<br>power-managed modes                      | PC + 2                 | u  | u  | u    | 0        | u   | u   | u               | u      |

**Legend:** u = unchanged

**Note 1:** When the wake-up is due to an interrupt and the GIEH or GIEL bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

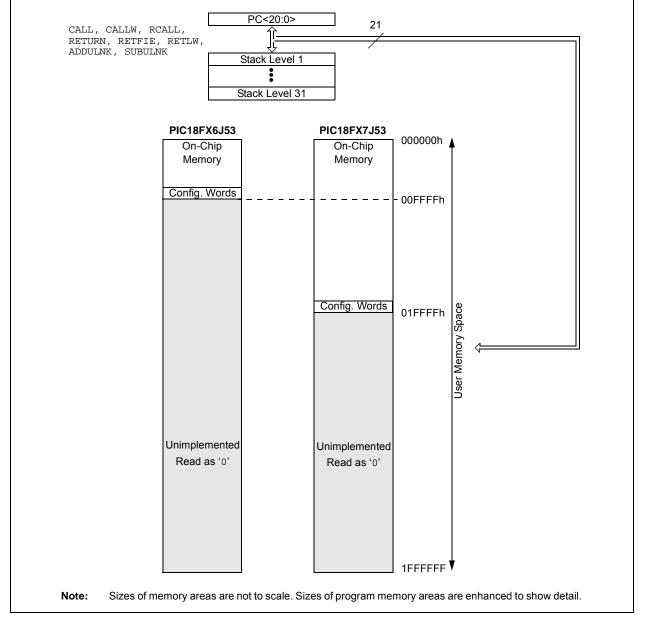

# 6.0 MEMORY ORGANIZATION

There are two types of memory in PIC18 Flash microcontrollers:

- Program Memory

- Data RAM

As Harvard architecture devices, the data and program memories use separate busses; this allows for concurrent access of the two memory spaces.

Section 7.0 "Flash Program Memory" provides additional information on the operation of the Flash program memory.

# 6.1 Program Memory Organization

PIC18 microcontrollers implement a 21-bit program counter, which is capable of addressing a 2-Mbyte program memory space. Accessing a location between the upper boundary of the physically implemented memory and the 2-Mbyte address returns all '0's (a NOP instruction).

The PIC18F47J53 family offers a range of on-chip Flash program memory sizes, from 64 Kbytes (up to 32,768 single-word instructions) to 128 Kbytes (65,536 single-word instructions).

Figure 6-1 provides the program memory maps for individual family devices.

# 7.0 FLASH PROGRAM MEMORY

The Flash program memory is readable, writable and erasable during normal operation over the entire  $V_{\text{DD}}$  range.

A read from program memory is executed on 1 byte at a time. A write to program memory is executed on blocks of 64 bytes at a time or 2 bytes at a time. Program memory is erased in blocks of 1024 bytes at a time. A bulk erase operation may not be issued from user code.

Writing or erasing program memory will cease instruction fetches until the operation is complete. The program memory cannot be accessed during the write or erase, therefore, code cannot execute. An internal programming timer terminates program memory writes and erases.

A value written to program memory does not need to be a valid instruction. Executing a program memory location that forms an invalid instruction results in a NOP.

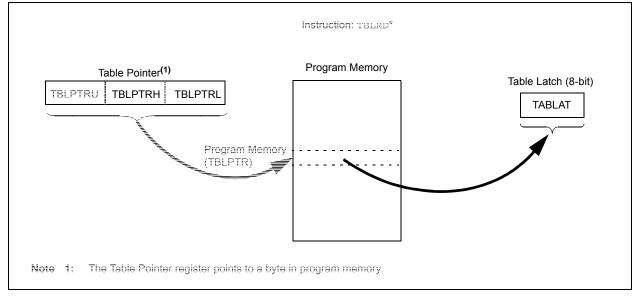

# 7.1 Table Reads and Table Writes

In order to read and write program memory, there are two operations that allow the processor to move bytes between the program memory space and the data RAM:

- Table Read (TBLRD)

- Table Write (TBLWT)

The program memory space is 16 bits wide, while the data RAM space is 8 bits wide. Table reads and table writes move data between these two memory spaces through an 8-bit register (TABLAT).

Table read operations retrieve data from program memory and place it into the data RAM space. Figure 7-1 illustrates the operation of a table read with program memory and data RAM.

Table write operations store data from the data memory space into holding registers in program memory. The procedure to write the contents of the holding registers into program memory is detailed in **Section 7.5** "**Writing to Flash Program Memory**". Figure 7-2 illustrates the operation of a table write with program memory and data RAM.

Table operations work with byte entities. A table block containing data, rather than program instructions, is not required to be word-aligned. Therefore, a table block can start and end at any byte address. If a table write is being used to write executable code into program memory, program instructions will need to be word-aligned.

#### FIGURE 7-1: TABLE READ OPERATION

# 9.6 INTx Pin Interrupts

External interrupts on the INT0, INT1, INT2 and INT3 pins are edge-triggered. If the corresponding INTEDGx bit in the INTCON2 register is set (= 1), the interrupt is triggered by a rising edge; if the bit is clear, the trigger is on the falling edge. When a valid edge appears on the INTx pin, the corresponding flag bit and INTxIF are set. This interrupt can be disabled by clearing the corresponding enable bit, INTxIE. Flag bit, INTxIF, must be cleared in software in the Interrupt Service Routine before re-enabling the interrupt.

All external interrupts (INT0, INT1, INT2 and INT3) can wake up the processor from the Sleep and Idle modes if bit, INTxIE, was set prior to going into the power-managed modes. Deep Sleep mode can wake up from INT0, but the processor will start execution from the power-on reset vector rather than branch to the interrupt vector.

Interrupt priority for INT1, INT2 and INT3 is determined by the value contained in the Interrupt Priority bits, INT1IP (INTCON3<6>), INT2IP (INTCON3<7>) and INT3IP (INTCON2<1>). There is no priority bit associated with INT0; It is always a high-priority interrupt source.

# 9.7 TMR0 Interrupt

In 8-bit mode (which is the default), an overflow in the TMR0 register (FFh  $\rightarrow$  00h) will set flag bit, TMR0IF. In 16-bit mode, an overflow in the TMR0H:TMR0L register

pair (FFFFh  $\rightarrow$  0000h) will set TMR0IF. The interrupt can be enabled/disabled by setting/clearing enable bit, TMR0IE (INTCON<5>). Interrupt priority for Timer0 is determined by the value contained in the interrupt priority bit, TMR0IP (INTCON2<2>). See Section 12.0 "Timer0 Module" for further details on the Timer0 module.

# 9.8 PORTB Interrupt-on-Change

An input change on PORTB<7:4> sets flag bit, RBIF (INTCON<0>). The interrupt can be enabled/disabled by setting/clearing enable bit, RBIE (INTCON<3>). Interrupt priority for PORTB interrupt-on-change is determined by the value contained in the interrupt priority bit, RBIP (INTCON2<0>).

# 9.9 Context Saving During Interrupts

During interrupts, the return PC address is saved on the stack. Additionally, the WREG, STATUS and BSR registers are saved on the Fast Return Stack. If a fast return from interrupt is not used (see **Section 6.3 "Data Memory Organization"**), the user may need to save the WREG, STATUS and BSR registers on entry to the Interrupt Service Routine. Depending on the user's application, other registers may also need to be saved. Example 9-1 saves and restores the WREG, STATUS and BSR registers during an Interrupt Service Routine.

EXAMPLE 9-1: SAVING STATUS, WREG AND BSR REGISTERS IN RAM

| MOVWF<br>MOVFF | W_TEMP<br>STATUS, STATUS_TEMP | ; W_TEMP is in virtual bank<br>; STATUS_TEMP located anywhere |

|----------------|-------------------------------|---------------------------------------------------------------|

| MOVFF          | BSR, BSR_TEMP                 | ; BSR_TMEP located anywhere                                   |

| ;              |                               |                                                               |

| ; USER         | ISR CODE                      |                                                               |

| ;              |                               |                                                               |

| MOVFF          | BSR_TEMP, BSR                 | ; Restore BSR                                                 |

| MOVF           | W_TEMP, W                     | ; Restore WREG                                                |

| MOVFF          | STATUS_TEMP, STATUS           | ; Restore STATUS                                              |

#### 10.7.6 PERIPHERAL PIN SELECT REGISTERS

The PIC18F47J53 family of devices implements a total of 37 registers for remappable peripheral configuration of 44-pin devices. The 28-pin devices have 31 registers for remappable peripheral configuration.

Note: Input and output register values can only be changed if IOLOCK (PPSCON<0>) = 0. See Example 10-7 for a specific command sequence.

# REGISTER 10-5: PPSCON: PERIPHERAL PIN SELECT INPUT REGISTER 0 (BANKED PPSCON)<sup>(1)</sup>

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0  |

|-------|-----|-----|-----|-----|-----|-----|--------|

| —     | _   | —   | —   | —   | —   |     | IOLOCK |

| bit 7 |     |     |     |     |     |     | bit 0  |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

#### bit 7-1 Unimplemented: Read as '0'

- bit 0 IOLOCK: I/O Lock Enable bit

- 1 = I/O lock is active, RPORx and RPINRx registers are write-protected

0 = I/O lock is not active, pin configurations can be changed

**Note 1:** Register values can only be changed if IOLOCK (PPSCON<0>) = 0.

#### **REGISTER 10-6:** RPINR1: PERIPHERAL PIN SELECT INPUT REGISTER 1 (BANKED EE1h)

| U-0   | U-0 | U-0 | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   |

|-------|-----|-----|---------|---------|---------|---------|---------|

| —     | —   | —   | INTR1R4 | INTR1R3 | INTR1R2 | INTR1R1 | INTR1R0 |

| bit 7 |     |     |         |         |         |         | bit 0   |

| Legend:           | $R/\overline{W}$ = Readable bit, Writable bit if IOLOCK = 0 |                                    |                    |  |  |  |

|-------------------|-------------------------------------------------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit                                            | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set                                            | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

#### bit 7-5 Unimplemented: Read as '0'

bit 4-0 **INTR1R<4:0>:** Assign External Interrupt 1 (INT1) to the Corresponding RPn Pin bits

#### REGISTER 10-7: RPINR2: PERIPHERAL PIN SELECT INPUT REGISTER 2 (BANKED EE2h)

| U-0   | U-0 | U-0 | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   |

|-------|-----|-----|---------|---------|---------|---------|---------|

| —     | —   | —   | INTR2R4 | INTR2R3 | INTR2R2 | INTR2R1 | INTR2R0 |

| bit 7 |     |     |         |         |         |         | bit 0   |

| Legend:           | $R/\overline{W}$ = Readable bit, Writable bit if IOLOCK = 0 |                             |                    |  |  |

|-------------------|-------------------------------------------------------------|-----------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit                                            | U = Unimplemented bit, read | l as '0'           |  |  |

| -n = Value at POR | '1' = Bit is set                                            | '0' = Bit is cleared        | x = Bit is unknown |  |  |

bit 7-5 Unimplemented: Read as '0'

bit 4-0 INTR2R<4:0>: Assign External Interrupt 2 (INT2) to the Corresponding RPn Pin bits

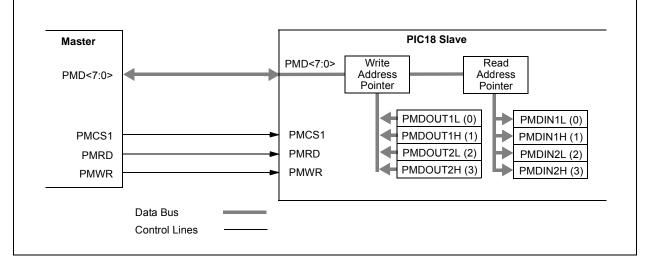

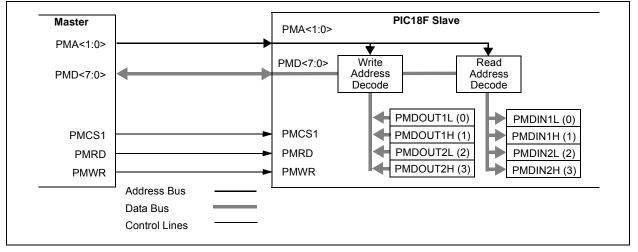

#### 11.2.4 BUFFERED PARALLEL SLAVE PORT MODE

Buffered Parallel Slave Port mode is functionally identical to the legacy PSP mode with one exception, the implementation of 4-level read and write buffers. Buffered PSP mode is enabled by setting the INCM bits in the PMMODEH register. If the INCM<1:0> bits are set to '11', the PMP module will act as the buffered PSP.

When the Buffered PSP mode is active, the PMDIN1L, PMDIN1H, PMDIN2L and PMDIN2H registers become the write buffers and the PMDOUT1L, PMDOUT1H, PMDOUT2L and PMDOUT2H registers become the read buffers. Buffers are numbered, 0 through 3, starting with the lower byte of PMDIN1L to PMDIN2H as the read buffers and PMDOUT1L to PMDOUT2H as the write buffers.

## 11.2.4.1 READ FROM SLAVE PORT

For read operations, the bytes will be sent out sequentially, starting with Buffer 0 (PMDOUT1L<7:0>) and ending with Buffer 3 (PMDOUT2H<7:0>) for every read strobe. The module maintains an internal pointer to keep track of which buffer is to be read. Each buffer has a corresponding read status bit, OBxE, in the PMSTATL register. This bit is cleared when a buffer contains data that has not been written to the bus, and is set when data is written to the bus. If the current buffer location being read from is empty, a buffer underflow is generated and the Buffer Overflow Flag bit, OBUF, is set. If all four OBxE status bits are set, then the Output Buffer Empty flag (OBE) will also be set.

# 11.2.4.2 WRITE TO SLAVE PORT

For write operations, the data has to be stored sequentially, starting with Buffer 0 (PMDIN1L<7:0>) and ending with Buffer 3 (PMDIN2H<7:0>). As with read operations, the module maintains an internal pointer to the buffer that is to be written next.

The input buffers have their own write status bits: IBxF in the PMSTATH register. The bit is set when the buffer contains unread incoming data and cleared when the data has been read. The flag bit is set on the write strobe. If a write occurs on a buffer when its associated IBxF bit is set, the Buffer Overflow flag, IBOV, is set; any incoming data in the buffer will be lost. If all four IBxF flags are set, the Input Buffer Full Flag (IBF) is set.

In Buffered Slave mode, the module can be configured to generate an interrupt on every read or write strobe (IRQM<1:0> = 01). It can be configured to generate an interrupt on a read from Read Buffer 3 or a write to Write Buffer 3, which is essentially an interrupt every fourth read or write strobe (RQM<1:0> = 11). When interrupting every fourth byte for input data, all input buffer registers should be read to clear the IBxF flags. If these flags are not cleared, then there is a risk of hitting an overflow condition.

#### FIGURE 11-5: PARALLEL MASTER/SLAVE CONNECTION BUFFERED EXAMPLE

### 11.2.5 ADDRESSABLE PARALLEL SLAVE PORT MODE

In the Addressable Parallel Slave Port mode (PMMODEH<1:0> = 01), the module is configured with two extra inputs, PMA<1:0>, which are the address lines 1 and 0. This makes the 4-byte buffer space directly addressable as fixed pairs of read and write buffers. As with Legacy Buffered mode, data is output from PMDOUT1L, PMDOUT1H, PMDOUT2L and PMDOUT2H, and is read in PMDIN1L, PMDIN1H, PMDIN2L and PMDIN2L and PMDIN2H. Table 11-1 provides the buffer addressing for the incoming address to the input and output registers.

#### TABLE 11-1: SLAVE MODE BUFFER ADDRESSING

| PMA<1:0> | Output<br>Register<br>(Buffer) | Input Register<br>(Buffer) |

|----------|--------------------------------|----------------------------|

| 00       | PMDOUT1L (0)                   | PMDIN1L (0)                |

| 01       | PMDOUT1H (1)                   | PMDIN1H (1)                |

| 10       | PMDOUT2L (2)                   | PMDIN2L (2)                |

| 11       | PMDOUT2H((3)                   | PMDIN2H (3)                |

#### FIGURE 11-6: PARALLEL MASTER/SLAVE CONNECTION ADDRESSED BUFFER EXAMPLE

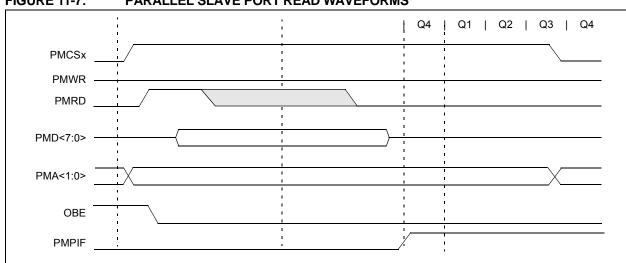

# 11.2.5.1 READ FROM SLAVE PORT

When chip select is active and a read strobe occurs (PMCSx = 1 and PMRD = 1), the data from one of the four output bytes is presented onto PMD<7:0>. Which byte is read depends on the 2-bit address placed on ADDR<1:0>. Table 11-1 provides the corresponding

output registers and their associated address. When an output buffer is read, the corresponding OBxE bit is set. The OBxE flag bit is set when all the buffers are empty. If any buffer is already empty, OBxE = 1, the next read to that buffer will generate an OBUF event.

## FIGURE 11-7: PARALLEL SLAVE PORT READ WAVEFORMS

# PIC18F47J53

| R/W-0                               | R/W-0       | U-0             | R/W-0            | U-0              | R/W-0            | R/W-0           | R/W-0   |

|-------------------------------------|-------------|-----------------|------------------|------------------|------------------|-----------------|---------|

| C7TSEL1                             | C7TSEL0     | —               | C6TSEL0          | —                | C5TSEL0          | C4TSEL1         | C4TSEL0 |

| bit 7                               | ·           |                 |                  |                  | •                |                 | bit C   |

|                                     |             |                 |                  |                  |                  |                 |         |

| Legend:                             |             |                 |                  |                  |                  |                 |         |

| R = Readab                          | le bit      | W = Writable    | bit              | U = Unimpler     | mented bit, read | l as '0'        |         |

| -n = Value at POR '1' = Bit is set  |             |                 | t                | '0' = Bit is cle | ared             | x = Bit is unkr | nown    |

|                                     |             |                 |                  |                  |                  |                 |         |

| bit 7-6                             | C7TSEL<1:0  | >: CCP7 Time    | r Selection bit  |                  |                  |                 |         |

| 00 = CCP7 is based off of TMR1/TMR2 |             |                 |                  |                  |                  |                 |         |

|                                     |             | is based off of |                  |                  |                  |                 |         |

|                                     |             | is based off of |                  |                  |                  |                 |         |

|                                     |             | is based off of |                  |                  |                  |                 |         |

| bit 5                               | •           | ted: Read as    |                  |                  |                  |                 |         |

| bit 4                               |             | CP6 Timer Sel   |                  |                  |                  |                 |         |

|                                     |             | based off of TI |                  |                  |                  |                 |         |

|                                     |             | based off of T  |                  |                  |                  |                 |         |

| bit 3                               | Unimplemen  | ted: Read as    | ʻ0'              |                  |                  |                 |         |

| bit 2                               | C5TSEL0: CO | CP5 Timer Sel   | ection bit       |                  |                  |                 |         |

|                                     |             | based off of T  |                  |                  |                  |                 |         |

|                                     | 1 = CCP5 is | based off of T  | MR5/TMR4         |                  |                  |                 |         |

| bit 1-0                             | C4TSEL<1:0  | >: CCP4 Time    | r Selection bits | 3                |                  |                 |         |

|                                     |             | is based off of |                  |                  |                  |                 |         |

|                                     |             | is based off of | -                |                  |                  |                 |         |

|                                     | 10 = 00P41  | is based off of | I IVIR3/ I IVIR6 |                  |                  |                 |         |

# REGISTER 18-2: CCPTMRS1: CCP4-10 TIMER SELECT 1 REGISTER (BANKED F51h)

11 = Reserved; do not use

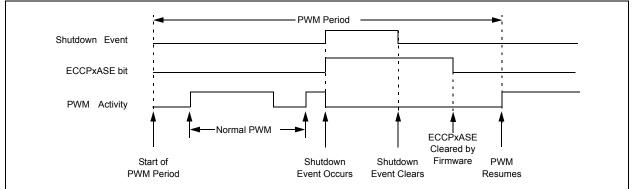

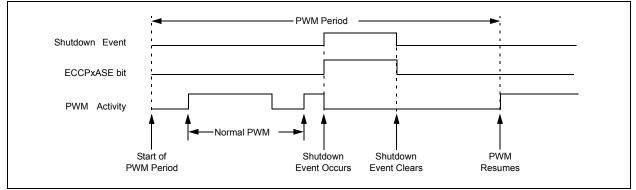

## 19.4.5 AUTO-RESTART MODE

The Enhanced PWM can be configured to automatically restart the PWM signal once the auto-shutdown condition has been removed. Auto-restart is enabled by setting the PxRSEN bit (ECCPxDEL<7>).

If auto-restart is enabled, the ECCPxASE bit will remain set as long as the auto-shutdown condition is active. When the auto-shutdown condition is removed, the ECCPxASE bit will be cleared via hardware and normal operation will resume. The module will wait until the next PWM period begins, however, before re-enabling the output pin. This behavior allows the auto-shutdown with auto-restart features to be used in applications based on the current mode of PWM control.

# FIGURE 19-13: PWM AUTO-SHUTDOWN WITH AUTO-RESTART ENABLED (PxRSEN = 1)

#### 20.5.14 SLEEP OPERATION

While in Sleep mode, the  $I^2C$  module can receive addresses or data and when an address match or complete byte transfer occurs, wake the processor from Sleep (if the MSSP interrupt is enabled).

#### 20.5.15 EFFECTS OF A RESET

A Reset disables the MSSP module and terminates the current transfer.

#### 20.5.16 MULTI-MASTER MODE

In Multi-Master mode, the interrupt generation on the detection of the Start and Stop conditions allows the determination of when the bus is free. The Start and Stop bits are cleared from a Reset or when the MSSP module is disabled. Control of the I<sup>2</sup>C bus may be taken when the P bit (SSPxSTAT<4>) is set, or the bus is Idle, with both the Start and Stop bits clear. When the bus is busy, enabling the MSSP interrupt will generate the interrupt when the Stop condition occurs.

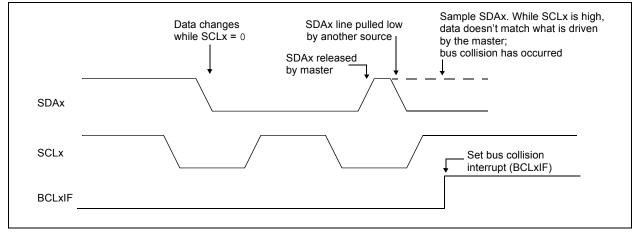

In multi-master operation, the SDAx line must be monitored for arbitration to see if the signal level is the expected output level. This check is performed in hardware with the result placed in the BCLxIF bit.

The states where arbitration can be lost are:

- · Address Transfer

- Data Transfer

- A Start Condition

- A Repeated Start Condition

- An Acknowledge Condition

#### 20.5.17 MULTI -MASTER COMMUNICATION, BUS COLLISION AND BUS ARBITRATION

Multi-Master mode support is achieved by bus arbitration. When the master outputs address/data bits onto the SDAx pin, arbitration takes place when the master outputs a '1' on SDAx, by letting SDAx float high, and another master asserts a '0'. When the SCLx pin floats high, data should be stable. If the expected data on SDAx is a '1' and the data sampled on the SDAx pin = 0, then a bus collision has taken place. The master will set the Bus Collision Interrupt Flag, BCLxIF, and reset the I<sup>2</sup>C port to its Idle state (Figure 20-27).

If a transmit was in progress when the bus collision occurred, the transmission is Halted, the BF flag is cleared, the SDAx and SCLx lines are deasserted and the SSPxBUF can be written to. When the user services the bus collision Interrupt Service Routine, and if the  $I^2C$  bus is free, the user can resume communication by asserting a Start condition.

If a Start, Repeated Start, Stop or Acknowledge condition was in progress when the bus collision occurred, the condition is aborted, the SDAx and SCLx lines are deasserted and the respective control bits in the SSPx-CON2 register are cleared. When the user services the bus collision Interrupt Service Routine (ISR), and if the I<sup>2</sup>C bus is free, the user can resume communication by asserting a Start condition.

The master will continue to monitor the SDAx and SCLx pins. If a Stop condition occurs, the SSPxIF bit will be set.

A write to the SSPxBUF will start the transmission of data at the first data bit regardless of where the transmitter left off when the bus collision occurred.

In Multi-Master mode, the interrupt generation on the detection of Start and Stop conditions allows the determination of when the bus is free. Control of the I<sup>2</sup>C bus can be taken when the Stop bit is set in the SSPxSTAT register, or the bus is Idle and the Start and Stop bits are cleared.

#### FIGURE 20-27: BUS COLLISION TIMING FOR TRANSMIT AND ACKNOWLEDGE

# PIC18F47J53

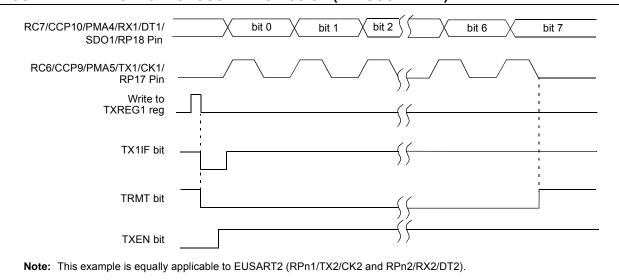

## FIGURE 21-12: SYNCHRONOUS TRANSMISSION (THROUGH TXEN)

| TABLE 21-7: | <b>REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER TRANSMISSION</b> |

|-------------|------------------------------------------------------------------|

|-------------|------------------------------------------------------------------|

| Name     | Bit 7                | Bit 6         | Bit 5         | Bit 4  | Bit 3   | Bit 2  | Bit 1   | Bit 0  |

|----------|----------------------|---------------|---------------|--------|---------|--------|---------|--------|

| INTCON   | GIE/GIEH             | PEIE/GIEL     | TMR0IE        | INT0IE | RBIE    | TMR0IF | INT0IF  | RBIF   |

| PIR1     | PMPIF <sup>(1)</sup> | ADIF          | RC1IF         | TX1IF  | SSP1IF  | CCP1IF | TMR2IF  | TMR1IF |

| PIE1     | PMPIE <sup>(1)</sup> | ADIE          | RC1IE         | TX1IE  | SSP1IE  | CCP1IE | TMR2IE  | TMR1IE |

| IPR1     | PMPIP <sup>(1)</sup> | ADIP          | RC1IP         | TX1IP  | SSP1IP  | CCP1IP | TMR2IP  | TMR1IP |

| PIR3     | SSP2IF               | BCL2IF        | RC2IF         | TX2IF  | TMR4IF  | CTMUIF | TMR3GIF | RTCCIF |

| PIE3     | SSP2IE               | BCL2IE        | RC2IE         | TX2IE  | TMR4IE  | CTMUIE | TMR3GIE | RTCCIE |

| IPR3     | SSP2IP               | BCL2IP        | RC2IP         | TX2IP  | TMR4IP  | CTMUIP | TMR3GIP | RTCCIP |

| RCSTAx   | SPEN                 | RX9           | SREN          | CREN   | ADDEN   | FERR   | OERR    | RX9D   |

| TXREGx   | EUSARTx T            | ransmit Regis | ster          |        |         |        |         |        |

| TXSTAx   | CSRC                 | TX9           | TXEN          | SYNC   | SENDB   | BRGH   | TRMT    | TX9D   |

| BAUDCONx | ABDOVF               | RCIDL         | RXDTP         | TXCKP  | BRG16   | _      | WUE     | ABDEN  |

| SPBRGHx  | EUSARTx B            | aud Rate Ge   | nerator High  | Byte   |         |        |         |        |

| SPBRGx   | EUSARTx B            | aud Rate Ge   | nerator Low I | Byte   |         |        |         |        |

| ODCON2   | _                    | _             | _             | _      | CCP10OD | CCP9OD | U2OD    | U10D   |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used for synchronous master transmission.

Note 1: These pins are only available on 44-pin devices.

#### 21.3.2 EUSART SYNCHRONOUS MASTER RECEPTION

Once Synchronous mode is selected, reception is enabled by setting either the Single Receive Enable bit, SREN (RCSTAx<5>) or the Continuous Receive Enable bit, CREN (RCSTAx<4>). Data is sampled on the RXx pin on the falling edge of the clock.

If enable bit, SREN, is set, only a single word is received. If enable bit, CREN, is set, the reception is continuous until CREN is cleared. If both bits are set, then CREN takes precedence.

To set up a Synchronous Master Reception:

- 1. Initialize the SPBRGHx:SPBRGx registers for the appropriate baud rate. Set or clear the BRG16 bit, as required, to achieve the desired baud rate.

- 2. Enable the synchronous master serial port by setting bits, SYNC, SPEN and CSRC.

- 3. Ensure bits, CREN and SREN, are clear.

- 4. If interrupts are desired, set enable bit, RCxIE.

- 5. If 9-bit reception is desired, set bit, RX9.

- 6. If a single reception is required, set bit, SREN. For continuous reception, set bit, CREN.

- 7. Interrupt flag bit, RCxIF, will be set when reception is complete and an interrupt will be generated if the enable bit, RCxIE, was set.

- 8. Read the RCSTAx register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 9. Read the 8-bit received data by reading the RCREGx register.

- 10. If any error occurred, clear the error by clearing bit, CREN.

- 11. If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set.

|   |          |       | <u>ب</u> ر _ |       | . – |       |               |       |             |                  |   |                  |              |             |     |             |    |             |                   |                                            |

|---|----------|-------|--------------|-------|-----|-------|---------------|-------|-------------|------------------|---|------------------|--------------|-------------|-----|-------------|----|-------------|-------------------|--------------------------------------------|

|   | <u>:</u> | bit 7 | X            | bit 6 | Х   | bit 5 | X <u>''</u>   | bit 4 | X           | bit 3            | Х | bit 2            | $\mathbf{X}$ | bit 1       | _X_ | bit 0       | _X |             |                   | C7/CCP10/PMA4/RX1/<br>DT1/SDO1/RP18        |

|   |          |       |              |       |     |       | <u>ن</u><br>ز |       |             |                  |   |                  |              |             |     |             |    |             |                   | RC6/CCP9/PMA5/TX1/<br>X1/RP17 (TXCKP = 0)  |

|   |          |       |              |       |     |       |               |       |             |                  |   | ;<br>;           |              |             |     |             |    | 1<br>1<br>1 |                   | RC6/CCP9/PMA5/TX1/<br>CK1/RP17 (TXCKP = 1) |

|   |          |       |              |       |     |       |               |       |             | ,<br>,<br>,<br>, |   | ,<br>,<br>,<br>, |              | 1<br>1<br>1 |     | ,<br>,<br>, |    | ų–          |                   | Write to<br>SREN bit                       |

|   | <u>.</u> |       |              |       |     |       |               |       |             |                  |   | I<br>I           |              |             |     |             |    | <u>:</u>    | N bit             | SREN bit                                   |

| 4 | <u> </u> |       |              |       |     |       | ،<br>۱        |       | ۱<br>۱      |                  |   |                  |              | ,<br>       |     | 1<br>1      |    |             | N bit <u>'</u> 0' | CREN bit                                   |

|   |          | ſ     | ו<br>ו<br>ו  |       |     |       |               |       | י<br>י<br>י | 1<br>1<br>1<br>1 |   | ,<br>,<br>,      |              | '           |     | •<br>•<br>• |    | 1<br>1<br>  |                   | RC1IF bit<br>(Interrupt)                   |

|   |          |       |              |       |     |       | <u>.</u>      |       |             | •                |   |                  |              |             |     | 1<br>1      |    | -<br>-      |                   | Read<br>RCREG1                             |

## FIGURE 21-13: SYNCHRONOUS RECEPTION (MASTER MODE, SREN)

| Name     | Bit 7                | Bit 6          | Bit 5        | Bit 4  | Bit 3   | Bit 2  | Bit 1   | Bit 0  |

|----------|----------------------|----------------|--------------|--------|---------|--------|---------|--------|

| INTCON   | GIE/GIEH             | PEIE/GIEL      | TMR0IE       | INT0IE | RBIE    | TMR0IF | INT0IF  | RBIF   |

| PIR1     | PMPIF <sup>(1)</sup> | ADIF           | RC1IF        | TX1IF  | SSP1IF  | CCP1IF | TMR2IF  | TMR1IF |

| PIE1     | PMPIE <sup>(1)</sup> | ADIE           | RC1IE        | TX1IE  | SSP1IE  | CCP1IE | TMR2IE  | TMR1IE |

| IPR1     | PMPIP <sup>(1)</sup> | ADIP           | RC1IP        | TX1IP  | SSP1IP  | CCP1IP | TMR2IP  | TMR1IP |

| PIR3     | SSP2IF               | BCL2IF         | RC2IF        | TX2IF  | TMR4IF  | CTMUIF | TMR3GIF | RTCCIF |

| PIE3     | SSP2IE               | BCL2IE         | RC2IE        | TX2IE  | TMR4IE  | CTMUIE | TMR3GIE | RTCCIE |

| IPR3     | SSP2IP               | BCL2IP         | RC2IP        | TX2IP  | TMR4IP  | CTMUIP | TMR3GIP | RTCCIP |

| RCSTAx   | SPEN                 | RX9            | SREN         | CREN   | ADDEN   | FERR   | OERR    | RX9D   |

| RCREGx   | EUSARTx Re           | eceive Registe | er           |        |         |        |         |        |

| TXSTAx   | CSRC                 | TX9            | TXEN         | SYNC   | SENDB   | BRGH   | TRMT    | TX9D   |

| BAUDCONx | ABDOVF               | RCIDL          | RXDTP        | TXCKP  | BRG16   | _      | WUE     | ABDEN  |

| SPBRGHx  | EUSARTx Ba           | aud Rate Gen   | erator High  | Byte   |         |        |         |        |

| SPBRGx   | EUSARTx Ba           | aud Rate Gen   | erator Low E | Byte   |         |        |         |        |

| ODCON2   | —                    | —              | _            | —      | CCP10OD | CCP9OD | U2OD    | U10D   |

# TABLE 21-8: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER RECEPTION

Legend: — = unimplemented, read as '0'. Shaded cells are not used for synchronous master reception.

**Note 1:** These pins are only available on 44-pin devices.

The ANCON0 and ANCON1 registers are used to configure the operation of the I/O pin associated with each analog channel. Setting any one of the PCFG bits configures the corresponding pin to operate as a digital only I/O. Clearing a bit configures the pin to operate as an analog input for either the A/D Converter or the comparator module. All digital peripherals are disabled and digital inputs read as '0'. As a rule, I/O pins that are multiplexed with analog inputs default to analog operation on device Resets.

In order to correctly perform A/D conversions on the VBG band gap reference (ADCON0<5:2> = 1111), the reference circuit must be powered on first. The VBGEN bit in the ANCON1 register allows the firmware to manually

request that the band gap reference circuit should be enabled. For best accuracy, firmware should allow a settling time of at least 10 ms prior to performing the first acquisition on this channel after enabling the band gap reference.

The reference circuit may already have been turned on if some other hardware module (such as the on-chip voltage regulator, comparators or HLVD) has already requested it. In this case, the initial turn-on settling time may have already elapsed and firmware does not need to wait as long before measuring VBG. Once the acquisition is complete, firmware may clear the VBGEN bit, which will save a small amount of power if no other modules are still requesting the VBG reference.

| REGISTER 22-4: | ANCON0: A/D PORT CONFIGURATION REGISTER 0 ( | (BANKED F48h) |

|----------------|---------------------------------------------|---------------|

|                |                                             |               |

| R/W-0                | R/W-0                | R/W-0                | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|----------------------|----------------------|----------------------|-------|-------|-------|-------|-------|

| PCFG7 <sup>(1)</sup> | PCFG6 <sup>(1)</sup> | PCFG5 <sup>(1)</sup> | PCFG4 | PCFG3 | PCFG2 | PCFG1 | PCFG0 |

| bit 7                |                      |                      |       |       |       |       | bit 0 |

|                      |                      |                      |       |       |       |       |       |

| Legend:              |                      |                      |       |       |       |       |       |

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

|-------------------|------------------|----------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 7-0

PCFG<7:0>: Analog Port Configuration bits (AN7-AN0)

1 = Pin configured as a digital port

0 = Pin configured as an analog channel – digital input disabled and reads '0'

**Note 1:** These bits are only available only on 44-pin devices.

#### REGISTER 22-5: ANCON1: A/D PORT CONFIGURATION REGISTER 1 (BANKED F49h)

| R/W-0 | R | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0 | R/W-0 |

|-------|---|-----|--------|--------|--------|-------|-------|

| VBGEN | r | —   | PCFG12 | PCFG11 | PCFG10 | PCFG9 | PCFG8 |

| bit 7 |   |     |        |        |        |       | bit 0 |

| Legend:           | r = Reserved bit |                       |                    |  |

|-------------------|------------------|-----------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |  |

| VBGEN: 1.2V Band Gap Reference Enable bit                                                                                                                              |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>1 = 1.2V band gap reference is powered on</li> <li>0 = 1.2V band gap reference is turned off to save power (if no other modules are requesting it)</li> </ul> |

| Reserved: Always maintain as '0' for lowest power consumption                                                                                                          |

| Unimplemented: Read as '0'                                                                                                                                             |

| PCFG<12:8>: Analog Port Configuration bits (AN12-AN8)                                                                                                                  |

| <ul> <li>1 = Pin configured as a digital port</li> <li>0 = Pin configured as an analog channel – digital input disabled and reads '0'</li> </ul>                       |

|                                                                                                                                                                        |

# REGISTER 28-1: CONFIG1L: CONFIGURATION REGISTER 1 LOW (BYTE ADDRESS 300000h)

| R/WO-1 | R/WO-1 | R/WO-1 | R/WO-1   | R/WO-1  | R/WO-1  | R/WO-1  | R/WO-1 |

|--------|--------|--------|----------|---------|---------|---------|--------|

| DEBUG  | XINST  | STVREN | CFGPLLEN | PLLDIV2 | PLLDIV1 | PLLDIV0 | WDTEN  |

| bit 7  | •      |        |          |         |         |         | bit 0  |

| Legend:      |                                                   |                                                                                                                                   |                        |                    |  |  |  |  |  |  |  |

|--------------|---------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|------------------------|--------------------|--|--|--|--|--|--|--|

| R = Readab   | ole bit                                           | WO = Write-Once bit                                                                                                               | U = Unimplemented bit, | read as '0'        |  |  |  |  |  |  |  |

| -n = Value a | It POR                                            | '1' = Bit is set                                                                                                                  | '0' = Bit is cleared   | x = Bit is unknown |  |  |  |  |  |  |  |

|              |                                                   |                                                                                                                                   |                        |                    |  |  |  |  |  |  |  |

| bit 7        | DEBUG:                                            | DEBUG: Background Debugger Enable bit                                                                                             |                        |                    |  |  |  |  |  |  |  |

|              |                                                   | ground debugger is disabled;<br>ground debugger is enabled; I                                                                     |                        |                    |  |  |  |  |  |  |  |

| bit 6        | XINST: EX                                         | XINST: Extended Instruction Set Enable bit                                                                                        |                        |                    |  |  |  |  |  |  |  |

|              |                                                   | iction set extension and Index<br>iction set extension and Index                                                                  | •                      |                    |  |  |  |  |  |  |  |

| bit 5        | STVREN:                                           | STVREN: Stack Overflow/Underflow Reset Enable bit                                                                                 |                        |                    |  |  |  |  |  |  |  |

|              |                                                   | 1 = Reset on stack overflow/underflow is enabled                                                                                  |                        |                    |  |  |  |  |  |  |  |

|              | 0 = Reset on stack overflow/underflow is disabled |                                                                                                                                   |                        |                    |  |  |  |  |  |  |  |

| bit 4        |                                                   | CFGPLLEN: PLL Enable bit                                                                                                          |                        |                    |  |  |  |  |  |  |  |

|              |                                                   | 1 = 96 MHz PLL is disabled<br>0 = 96 MHz PLL is enabled                                                                           |                        |                    |  |  |  |  |  |  |  |

| bit 3-1      | PLLDIV<2:0>: Oscillator Selection bits            |                                                                                                                                   |                        |                    |  |  |  |  |  |  |  |

|              |                                                   | Divider must be selected to provide a 4 MHz input into the 96 MHz PLL.                                                            |                        |                    |  |  |  |  |  |  |  |

|              |                                                   | <ul> <li>111 = No divide – oscillator used directly (4 MHz input)</li> <li>110 = Oscillator divided by 2 (8 MHz input)</li> </ul> |                        |                    |  |  |  |  |  |  |  |

|              |                                                   | 101 = Oscillator divided by 3 (12 MHz input)                                                                                      |                        |                    |  |  |  |  |  |  |  |

|              |                                                   | 100 = Oscillator divided by 4 (16 MHz input)                                                                                      |                        |                    |  |  |  |  |  |  |  |

|              |                                                   | 011 = Oscillator divided by 5 (20 MHz input)                                                                                      |                        |                    |  |  |  |  |  |  |  |

|              |                                                   | 010 = Oscillator divided by 6 (24 MHz input)<br>001 = Oscillator divided by 10 (40 MHz input)                                     |                        |                    |  |  |  |  |  |  |  |

|              |                                                   | cillator divided by 12 (48 MHz                                                                                                    | • •                    |                    |  |  |  |  |  |  |  |

| bit 0        | WDTEN:                                            | Watchdog Timer Enable bit                                                                                                         |                        |                    |  |  |  |  |  |  |  |

|              |                                                   | is enabled                                                                                                                        |                        |                    |  |  |  |  |  |  |  |

|              | 0 = WDT                                           | is disabled (control is placed o                                                                                                  | on the SWDTEN bit)     |                    |  |  |  |  |  |  |  |

# PIC18F47J53

| MULLW                                   | Multiply L                  | iteral with W                                                          |                                             | MULWF                     | Multiply W w                                                                                                                                                                                                                                                                                          | rith f                                                                             |                                        |

|-----------------------------------------|-----------------------------|------------------------------------------------------------------------|---------------------------------------------|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|----------------------------------------|

| Syntax:                                 | MULLW                       | k                                                                      |                                             | Syntax:                   | MULWF f{                                                                                                                                                                                                                                                                                              | ,a}                                                                                |                                        |

| Operands:                               | $0 \le k \le 255$           | 5                                                                      |                                             | Operands:                 | $0 \leq f \leq 255$                                                                                                                                                                                                                                                                                   |                                                                                    |                                        |

| Operation:                              | (W) x k $\rightarrow$       | PRODH:PRO                                                              | DL                                          |                           | a ∈ [0,1]                                                                                                                                                                                                                                                                                             |                                                                                    |                                        |

| Status Affected:                        | None                        |                                                                        |                                             | Operation:                | $(W) \mathrel{x} (f) \to P$                                                                                                                                                                                                                                                                           | RODH:PROD                                                                          | L                                      |

| Encoding:                               | 0000                        | 1101 kk                                                                | kk kkkk                                     | Status Affected:          | None                                                                                                                                                                                                                                                                                                  |                                                                                    |                                        |

| Description:                            | out betwee<br>8-bit literal | ed multiplication<br>on the contents<br>'k'. The 16-bit<br>he PRODH:PF | of W and the result is                      | Encoding:<br>Description: | 0000         001a         ffff         ffff           An unsigned multiplication is carried out<br>between the contents of W and the<br>register file location 'f'. The 16-bit result is<br>stored in the PRODH:PRODL register<br>pair. PRODH contains the high byte. Both<br>W and 'f are unchanged. |                                                                                    |                                        |

|                                         | pair. PROE<br>W is uncha    | OH contains th<br>anged.                                               | e high byte.                                |                           |                                                                                                                                                                                                                                                                                                       |                                                                                    |                                        |

|                                         | None of the                 | e Status flags                                                         | are affected.                               |                           | None of the Status flags are affected.                                                                                                                                                                                                                                                                |                                                                                    |                                        |

|                                         | possible in                 | either Overflo<br>this operation<br>but not detect                     | A Zero result                               |                           | Note that neither Overflow nor Carry is possible in this operation. A Zero result is possible but not detected.                                                                                                                                                                                       |                                                                                    |                                        |

| Words:                                  | 1                           |                                                                        |                                             |                           | •                                                                                                                                                                                                                                                                                                     |                                                                                    | k is selected. If                      |

| Cycles:<br>Q Cycle Activity:            | 1                           |                                                                        |                                             |                           | 'a' is '1', the E<br>GPR bank (de                                                                                                                                                                                                                                                                     | BSR is used to                                                                     |                                        |

| Q1<br>Decode                            | Q2<br>Read<br>literal 'k'   | Q3<br>Process<br>Data                                                  | Q4<br>Write<br>registers<br>PRODH:<br>PRODL |                           | If 'a' is '0' and<br>is enabled, th<br>Indexed Liter:<br>whenever f ≤<br>Section 29.2<br>Bit-Oriented<br>Literal Offse                                                                                                                                                                                | is instruction<br>al Offset Addr<br>95 (5Fh). See<br>.3 "Byte-Orie<br>Instructions | essing mode<br>ented and<br>in Indexed |

| Example:                                | MULLW                       | 0C4h                                                                   |                                             | Words:                    | 1                                                                                                                                                                                                                                                                                                     |                                                                                    | elans.                                 |

| Before Instruc                          |                             |                                                                        |                                             |                           | 1                                                                                                                                                                                                                                                                                                     |                                                                                    |                                        |

| W<br>PRODH                              | = E2<br>= ?                 | 2h                                                                     |                                             | Cycles:                   | -                                                                                                                                                                                                                                                                                                     |                                                                                    |                                        |

| PRODL                                   | = ?                         |                                                                        |                                             | Q Cycle Activity:<br>Q1   | Q2                                                                                                                                                                                                                                                                                                    | Q3                                                                                 | Q4                                     |

| After Instructio<br>W<br>PRODH<br>PRODL | = E2                        | Dh                                                                     |                                             | Decode                    | Read<br>register 'f'                                                                                                                                                                                                                                                                                  | Process<br>Data                                                                    | Write<br>registers<br>PRODH:<br>PRODL  |

|                                         |                             |                                                                        |                                             | Example:<br>Before Instri | MULWF                                                                                                                                                                                                                                                                                                 | REG, 1                                                                             |                                        |

Before Instruction

W

=

C4h

REG

=

B5h

PRODH

=

?

PRODL

=

?

After Instruction

W

=

C4h

REG

=

B5h

PRODH

=

24h

PRODH

=

8Ah

PRODH

=

94h

### 29.2.3 BYTE-ORIENTED AND BIT-ORIENTED INSTRUCTIONS IN INDEXED LITERAL OFFSET MODE

| Note: | Enabling the PIC18 instruction set exten- |  |  |  |  |  |  |  |  |

|-------|-------------------------------------------|--|--|--|--|--|--|--|--|

|       | sion may cause legacy applications to     |  |  |  |  |  |  |  |  |

|       | behave erratically or fail entirely.      |  |  |  |  |  |  |  |  |

In addition to eight new commands in the extended set, enabling the extended instruction set also enables Indexed Literal Offset Addressing (Section 6.6.1 "Indexed Addressing with Literal Offset"). This has a significant impact on the way that many commands of the standard PIC18 instruction set are interpreted.

When the extended set is disabled, addresses embedded in opcodes are treated as literal memory locations: either as a location in the Access Bank (a = 0) or in a GPR bank designated by the BSR (a = 1). When the extended instruction set is enabled and a = 0, however, a file register argument of 5Fh or less is interpreted as an offset from the pointer value in FSR2 and not as a literal address. For practical purposes, this means that all instructions that use the Access RAM bit as an argument – that is, all byte-oriented and bit-oriented instructions, or almost half of the core PIC18 instructions – may behave differently when the extended instruction set is enabled.

When the content of FSR2 is 00h, the boundaries of the Access RAM are essentially remapped to their original values. This may be useful in creating backward-compatible code. If this technique is used, it may be necessary to save the value of FSR2 and restore it when moving back and forth between C and assembly routines in order to preserve the Stack Pointer. Users must also keep in mind the syntax requirements of the extended instruction set (see Section 29.2.3.1 "Extended Instruction Syntax with Standard PIC18 Commands").

Although the Indexed Literal Offset mode can be very useful for dynamic stack and pointer manipulation, it can also be very annoying if a simple arithmetic operation is carried out on the wrong register. Users who are accustomed to the PIC18 programming must keep in mind that, when the extended instruction set is enabled, register addresses of 5Fh or less are used for Indexed Literal Offset Addressing.

Representative examples of typical byte-oriented and bit-oriented instructions in the Indexed Literal Offset mode are provided on the following page to show how execution is affected. The operand conditions shown in the examples are applicable to all instructions of these types.

# 29.2.3.1 Extended Instruction Syntax with Standard PIC18 Commands

When the extended instruction set is enabled, the file register argument 'f' in the standard byte-oriented and bit-oriented commands is replaced with the literal offset value 'k'. As already noted, this occurs only when 'f' is less than or equal to 5Fh. When an offset value is used, it must be indicated by square brackets ("[]"). As with the extended instructions, the use of brackets indicates to the compiler that the value is to be interpreted as an index or an offset. Omitting the brackets, or using a value greater than 5Fh within the brackets, will generate an error in the MPASM Assembler.

If the index argument is properly bracketed for Indexed Literal Offset Addressing, the Access RAM argument is never specified; it will automatically be assumed to be '0'. This is in contrast to standard operation (extended instruction set disabled), when 'a' is set on the basis of the target address. Declaring the Access RAM bit in this mode will also generate an error in the MPASM Assembler.

The destination argument 'd' functions as before.

In the latest versions of the MPASM Assembler, language support for the extended instruction set must be explicitly invoked. This is done with either the command line option,  $/_{Y}$ , or the PE directive in the source listing.

## 29.2.4 CONSIDERATIONS WHEN ENABLING THE EXTENDED INSTRUCTION SET

It is important to note that the extensions to the instruction set may not be beneficial to all users. In particular, users who are not writing code that uses a software stack may not benefit from using the extensions to the instruction set.

Additionally, the Indexed Literal Offset Addressing mode may create issues with legacy applications written to the PIC18 assembler. This is because instructions in the legacy code may attempt to address registers in the Access Bank below 5Fh. Since these addresses are interpreted as literal offsets to FSR2 when the instruction set extension is enabled, the application may read or write to the wrong data addresses.

When porting an application to the PIC18F47J53 family, it is very important to consider the type of code. A large, re-entrant application that is written in C and would benefit from efficient compilation will do well when using the instruction set extensions. Legacy applications that heavily use the Access Bank will most likely not benefit from using the extended instruction set.

| PIC18F47J53 Family |         |                                                                  | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial |      |           |       |                                                           |  |

|--------------------|---------|------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|------|-----------|-------|-----------------------------------------------------------|--|

| Param.<br>No.      | Symbol  | Characteristic                                                   | Min.                                                                                                                               | Тур. | Max.      | Units | Conditions                                                |  |