Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 48MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART, USB                              |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 34                                                                          |

| Program Memory Size        | 128KB (64K x 16)                                                            |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 3.8K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.15V ~ 3.6V                                                                |

| Data Converters            | A/D 13x10b/12b                                                              |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 44-TQFP                                                                     |

| Supplier Device Package    | 44-TQFP (10x10)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f47j53t-i-pt |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

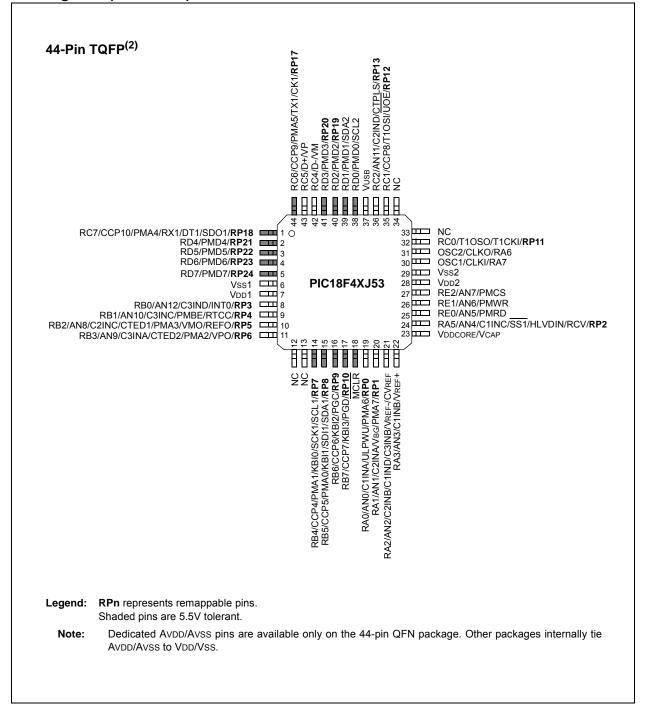

#### **Pin Diagrams (Continued)**

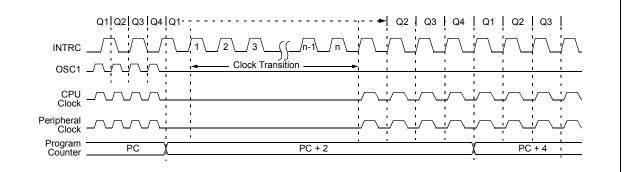

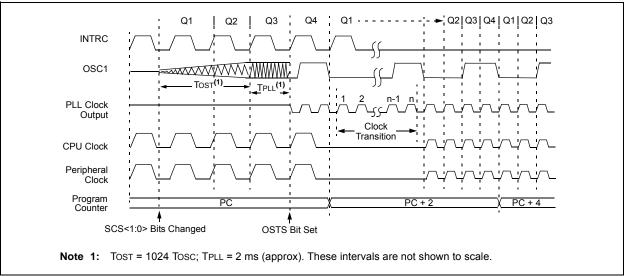

#### 4.2.3 RC\_RUN MODE

In RC\_RUN mode, the CPU and peripherals are clocked from the internal oscillator; the primary clock is shut down. This mode provides the best power conservation of all the Run modes while still executing code. It works well for user applications, which are not highly timing-sensitive or do not require high-speed clocks at all times.

This mode is entered by setting the SCS<1:0> bits (OSCCON<1:0>) to '11'. When the clock source is switched to the internal oscillator block (see Figure 4-3), the primary oscillator is shut down and the OSTS bit is cleared.

On transitions from RC\_RUN mode to PRI\_RUN mode, the device continues to be clocked from the INTOSC block while the primary clock is started. When the primary clock becomes ready, a clock switch to the primary clock occurs (see Figure 4-4). When the clock switch is complete, the OSTS bit is set and the primary clock is providing the device clock. The IDLEN and SCS bits are not affected by the switch. The INTRC clock source will continue to run if either the WDT or the FSCM is enabled.

| TABLE 5-2: | INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED) |             |                                                                |                                                                            |                                 |  |

|------------|---------------------------------------------------------|-------------|----------------------------------------------------------------|----------------------------------------------------------------------------|---------------------------------|--|

| Register   | Applicabl                                               | e Devices   | Power-on Reset,<br>Brown-out Reset,<br>Wake From Deep<br>Sleep | MCLR Resets<br>WDT Reset<br>RESET Instruction<br>Stack Resets<br>CM Resets | Wake-up via WDT<br>or Interrupt |  |

| TMR8       | PIC18F2XJ53                                             | PIC18F4XJ53 | 0000 0000                                                      | _                                                                          | _                               |  |

| PR8        | PIC18F2XJ53                                             | PIC18F4XJ53 | 1111 1111                                                      | _                                                                          | -                               |  |

| T8CON      | PIC18F2XJ53                                             | PIC18F4XJ53 | -000 0000                                                      | -                                                                          | -                               |  |

| PSTR3CON   | PIC18F2XJ53                                             | PIC18F4XJ53 | 00-0 0001                                                      | -                                                                          | -                               |  |

| ECCP3AS    | PIC18F2XJ53                                             | PIC18F4XJ53 | 0000 0000                                                      | —                                                                          | -                               |  |

| ECCP3DEL   | PIC18F2XJ53                                             | PIC18F4XJ53 | 0000 0000                                                      | -                                                                          | -                               |  |

| CCPR3H     | PIC18F2XJ53                                             | PIC18F4XJ53 | xxxx xxxx                                                      | -                                                                          | -                               |  |

| CCPR3L     | PIC18F2XJ53                                             | PIC18F4XJ53 | xxxx xxxx                                                      | —                                                                          | -                               |  |

| CCP3CON    | PIC18F2XJ53                                             | PIC18F4XJ53 | 0000 0000                                                      | -                                                                          | _                               |  |

| CCPR4H     | PIC18F2XJ53                                             | PIC18F4XJ53 | xxxx xxxx                                                      | -                                                                          | -                               |  |

| CCPR4L     | PIC18F2XJ53                                             | PIC18F4XJ53 | xxxx xxxx                                                      | —                                                                          | -                               |  |

| CCP4CON    | PIC18F2XJ53                                             | PIC18F4XJ53 | 00 0000                                                        | _                                                                          | _                               |  |

| CCPR5H     | PIC18F2XJ53                                             | PIC18F4XJ53 | xxxx xxxx                                                      | _                                                                          | _                               |  |

| CCPR5L     | PIC18F2XJ53                                             | PIC18F4XJ53 | xxxx xxxx                                                      | —                                                                          | -                               |  |

| CCP5CON    | PIC18F2XJ53                                             | PIC18F4XJ53 | 00 0000                                                        | _                                                                          | _                               |  |

| CCPR6H     | PIC18F2XJ53                                             | PIC18F4XJ53 | xxxx xxxx                                                      | _                                                                          | -                               |  |

| CCPR6L     | PIC18F2XJ53                                             | PIC18F4XJ53 | xxxx xxxx                                                      | —                                                                          | -                               |  |

| CCP6CON    | PIC18F2XJ53                                             | PIC18F4XJ53 | 00 0000                                                        | -                                                                          | -                               |  |

| CCPR7H     | PIC18F2XJ53                                             | PIC18F4XJ53 | xxxx xxxx                                                      | _                                                                          | -                               |  |

| CCPR7L     | PIC18F2XJ53                                             | PIC18F4XJ53 | xxxx xxxx                                                      | —                                                                          | -                               |  |

| CCP7CON    | PIC18F2XJ53                                             | PIC18F4XJ53 | 00 0000                                                        | _                                                                          | -                               |  |

| CCPR8H     | PIC18F2XJ53                                             | PIC18F4XJ53 | xxxx xxxx                                                      | _                                                                          | _                               |  |

| CCPR8L     | PIC18F2XJ53                                             | PIC18F4XJ53 | xxxx xxxx                                                      | _                                                                          | -                               |  |

| CCP8CON    | PIC18F2XJ53                                             | PIC18F4XJ53 | 00 0000                                                        | _                                                                          | -                               |  |

| CCPR9H     | PIC18F2XJ53                                             | PIC18F4XJ53 | xxxx xxxx                                                      | _                                                                          | -                               |  |

| CCPR9L     | PIC18F2XJ53                                             | PIC18F4XJ53 | xxxx xxxx                                                      | _                                                                          | _                               |  |

| CCP9CON    | PIC18F2XJ53                                             | PIC18F4XJ53 | 00 0000                                                        | —                                                                          | -                               |  |

| CCPR10H    | PIC18F2XJ53                                             | PIC18F4XJ53 | xxxx xxxx                                                      | _                                                                          | -                               |  |

| CCPR10L    | PIC18F2XJ53                                             | PIC18F4XJ53 | xxxx xxxx                                                      | _                                                                          | _                               |  |

| CCP10CON   | PIC18F2XJ53                                             | PIC18F4XJ53 | 00 0000                                                        | —                                                                          | -                               |  |

| RPINR24    | PIC18F2XJ53                                             | PIC18F4XJ53 | 1 1111                                                         | 1 1111                                                                     | u uuuu                          |  |

| RPINR23    | PIC18F2XJ53                                             | PIC18F4XJ53 | 1 1111                                                         | 1 1111                                                                     | u uuuu                          |  |

#### TABLE 5-2: INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED)

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition.

**Note 1:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware stack.

- 2: When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

- 3: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

- **4:** See Table 5-1 for Reset value for specific condition.

- 5: Not implemented for PIC18F2XJ53 devices.

- 6: Not implemented for "LF" devices.

#### 9.5 RCON Register

The RCON register contains bits used to determine the cause of the last Reset or wake-up from Idle or Sleep mode. RCON also contains the bit that enables interrupt priorities (IPEN).

#### REGISTER 9-19: RCON: RESET CONTROL REGISTER (ACCESS FD0h)

| R/W-0 | U-0 | R/W-1 | R/W-1 | R-1 | R-1 | R/W-0 | R/W-0 |

|-------|-----|-------|-------|-----|-----|-------|-------|

| IPEN  | —   | CM    | RI    | TO  | PD  | POR   | BOR   |

| bit 7 |     |       |       |     |     |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7 | <ul> <li>IPEN: Interrupt Priority Enable bit</li> <li>1 = Enable priority levels on interrupts</li> <li>0 = Disable priority levels on interrupts (PIC16CXXX Compatibility mode)</li> </ul> |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6 | Unimplemented: Read as '0'                                                                                                                                                                  |

| bit 5 | CM: Configuration Mismatch Flag bit                                                                                                                                                         |

|       | For details on bit operation, see Register 5-1.                                                                                                                                             |

| bit 4 | RI: RESET Instruction Flag bit                                                                                                                                                              |

|       | For details on bit operation, see Register 5-1.                                                                                                                                             |

| bit 3 | TO: Watchdog Timer Time-out Flag bit                                                                                                                                                        |

|       | For details on bit operation, see Register 5-1.                                                                                                                                             |

| bit 2 | PD: Power-Down Detection Flag bit                                                                                                                                                           |

|       | For details on bit operation, see Register 5-1.                                                                                                                                             |

| bit 1 | POR: Power-on Reset Status bit                                                                                                                                                              |

|       | For details on bit operation, see Register 5-1.                                                                                                                                             |

| bit 0 | BOR: Brown-out Reset Status bit                                                                                                                                                             |

|       | For details on bit operation, see Register 5-1.                                                                                                                                             |

### 10.6 PORTE, TRISE and LATE Registers

| Note:    | PORTE | is | available | only | in | 44-pin |

|----------|-------|----|-----------|------|----|--------|

| devices. |       |    |           |      |    |        |

Depending on the particular PIC18F47J53 family device selected, PORTE is implemented in two different ways.

For 44-pin devices, PORTE is a 3-bit wide port. Three pins (RE0/AN5/PMRD, RE1/AN6/PMWR and RE2/ AN7/PMCS) are individually configurable as inputs or outputs. These pins have Schmitt Trigger input buffers. When selected as analog inputs, these pins will read as '0's.

The corresponding Data Direction register is TRISE. Setting a TRISE bit (= 1) will make the corresponding PORTE pin an input (i.e., put the corresponding output driver in a High-Impedance mode). Clearing a TRISE bit (= 0) will make the corresponding PORTE pin an output (i.e., put the contents of the output latch on the selected pin).

TRISE controls the direction of the RE pins, even when they are being used as analog inputs. The user must make sure to keep the pins configured as inputs when using them as analog inputs.

| Note: | On a POR, RE<2:0> are configured as |

|-------|-------------------------------------|

|       | analog inputs.                      |

The Data Latch register (LATE) is also memory mapped. Read-modify-write operations on the LATE register read and write the latched output value for PORTE.

#### EXAMPLE 10-6: INITIALIZING PORTE

| ; clearing output                                                   |

|---------------------------------------------------------------------|

| ; data latches<br>CLRF LATE ; Alternate method<br>; to clear output |

| ; do clear output<br>; data latches<br>MOVLW 0Ah ; Configure A/D    |

| MOVWF ADCON1 ; for digital inputs                                   |

| MOVLW 03h ; Value used to<br>; initialize data                      |

| ; initialize data<br>; direction                                    |

| MOVWF TRISE ; Set RE<0> as inputs                                   |

| ; RE<1> as outputs<br>; RE<2> as inputs                             |

Each of the PORTE pins has a weak internal pull-up. A single control bit can turn on all the pull-ups. This is performed by setting bit, REPU (TRISE<6>). The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on a POR. The integrated weak pull-ups consist of a semiconductor structure similar to, but somewhat different, from a discrete resistor. On an unloaded I/O pin, the weak pull-ups are intended to provide logic high indication, but will not necessarily pull the pin all the way to VDD levels.

Note that the pull-ups can be used for any set of features, similar to the pull-ups found on PORTB.

### REGISTER 10-45: RPOR24: PERIPHERAL PIN SELECT OUTPUT REGISTER 24 (BANKED ED8h)<sup>(1)</sup>

| U-0   | U-0 | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|-----|--------|--------|--------|--------|--------|

| —     | —   |     | RP24R4 | RP24R3 | RP24R2 | RP24R1 | RP24R0 |

| bit 7 |     |     |        |        |        |        | bit 0  |

| Legend:           | $R/\overline{W}$ = Readable bit, Writable bit if IOLOCK = 0 |                             |                    |

|-------------------|-------------------------------------------------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit                                            | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set                                            | '0' = Bit is cleared        | x = Bit is unknown |

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP24R<4:0>:** Peripheral Output Function is Assigned to RP24 Output Pin bits (see Table 10-14 for peripheral function numbers)

**Note 1:** RP24 pins are not available on 28-pin devices.

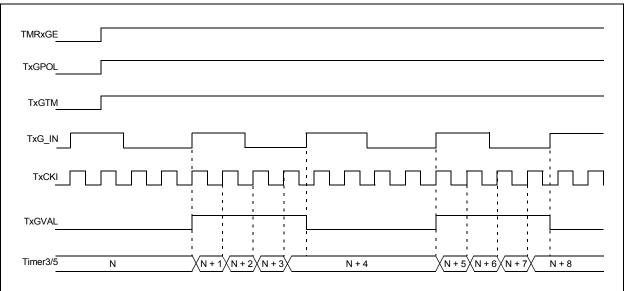

#### 15.5.2 TIMER3/5 GATE SOURCE SELECTION

The Timer3/5 gate source can be selected from one of four different sources. Source selection is controlled by the TxGSS<1:0> bits (TxGCON<1:0>). The polarity for each available source is also selectable and is controlled by the TxGPOL bit (TxGCON<6>).

| TxGSS<1:0> | Timerx Gate Source   |

|------------|----------------------|

| 00         | TxG timer gate pin   |

| 01         | TMR4/6 matches PR4/6 |

| 10         | Comparator 1 output  |

| 11         | Comparator 2 output  |

#### 15.5.2.1 TxG Pin Gate Operation

The TxG pin is one source for Timer3/5 gate control. It can be used to supply an external source to the gate circuitry.

#### 15.5.2.2 Timer4/6 Match Gate Operation

The TMR4/6 register will increment until it matches the value in the PR4/6 register. On the very next increment cycle, TMR4/6 will be reset to 00h. When this Reset occurs, a low-to-high pulse will automatically be generated and internally supplied to the Timer3/5 gate circuitry.

#### 15.5.3 TIMER3/5 GATE-TOGGLE MODE

When Timer3/5 Gate Toggle mode is enabled, it is possible to measure the full cycle length of a Timer3/5 gate signal, as opposed to the duration of a single level pulse.

The Timer1 gate source is routed through a flip-flop that changes state on every incrementing edge of the signal. (For timing details, see Figure 15-3.)

The TxGVAL bit will indicate when the Toggled mode is active and the timer is counting.

Timer3/5 Gate Toggle mode is enabled by setting the TxGTM bit (TxGCON<5>). When the TxGTM bit is cleared, the flip-flop is cleared and held clear. This is necessary in order to control which edge is measured.

#### FIGURE 15-3: TIMER3/5 GATE TOGGLE MODE

NOTES:

#### REGISTER 17-9: DAY: DAY VALUE REGISTER<sup>(1)</sup>

| U-0   | U-0 | R/W-x   | R/W-x   | R/W-x   | R/W-x   | R/W-x   | R/W-x   |

|-------|-----|---------|---------|---------|---------|---------|---------|

| —     | —   | DAYTEN1 | DAYTEN0 | DAYONE3 | DAYONE2 | DAYONE1 | DAYONE0 |

| bit 7 |     |         |         |         |         |         | bit 0   |

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

| bit 7-6 | Unimplemented: Read as '0'                                                                                  |

|---------|-------------------------------------------------------------------------------------------------------------|

| bit 5-4 | <b>DAYTEN&lt;1:0&gt;:</b> Binary Coded Decimal value of Day's Tens Digit bits Contains a value from 0 to 3. |

| bit 3-0 | <b>DAYONE&lt;3:0&gt;:</b> Binary Coded Decimal Value of Day's Ones Digit bits Contains a value from 0 to 9. |

**Note 1:** A write to this register is only allowed when RTCWREN = 1.

#### REGISTER 17-10: WKDY: WEEKDAY VALUE REGISTER<sup>(1)</sup>

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-x | R/W-x | R/W-x |

|-------|-----|-----|-----|-----|-------|-------|-------|

| —     | —   | —   | _   | —   | WDAY2 | WDAY1 | WDAY0 |

| bit 7 |     |     |     |     |       |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 7-3 Unimplemented: Read as '0'

bit 2-0 **WDAY<2:0>:** Binary Coded Decimal Value of Weekday Digit bits Contains a value from 0 to 6.

**Note 1:** A write to this register is only allowed when RTCWREN = 1.

$\ensuremath{\textcircled{}^{\odot}}$  2009-2016 Microchip Technology Inc.

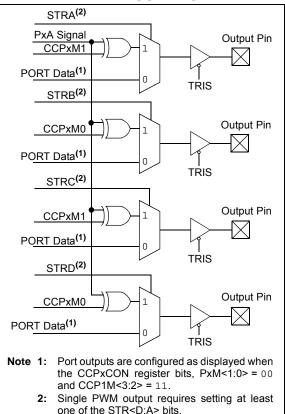

#### 19.4.7.1 Steering Synchronization

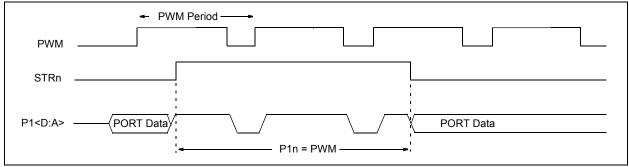

The STRSYNC bit of the PSTRxCON register gives the user two choices for when the steering event will happen. When the STRSYNC bit is '0', the steering event will happen at the end of the instruction that writes to the PSTRxCON register. In this case, the output signal at the Px<D:A> pins may be an incomplete PWM waveform. This operation is useful when the user firmware needs to immediately remove a PWM signal from the pin.

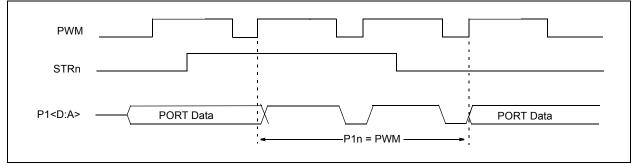

When the STRSYNC bit is '1', the effective steering update will happen at the beginning of the next PWM period. In this case, steering on/off the PWM output will always produce a complete PWM waveform.

Figure 19-17 and Figure 19-18 illustrate the timing diagrams of the PWM steering depending on the STRSYNC setting.

#### FIGURE 19-17: EXAMPLE OF STEERING EVENT AT END OF INSTRUCTION (STRSYNC = 0)

#### FIGURE 19-18: EXAMPLE OF STEERING EVENT AT BEGINNING OF INSTRUCTION (STRSYNC = 1)

#### 20.3.4 ENABLING SPI I/O

To enable the serial port, MSSP Enable bit, SSPEN (SSPxCON1<5>), must be set. To reset or reconfigure SPI mode, clear the SSPEN bit, re-initialize the SSPxCON1 registers and then set the SSPEN bit. This configures the SDIx, SDOx, SCKx and SSx pins as serial port pins. For the pins to behave as the serial port function, the appropriate TRISx bits, PCFGx bits and Peripheral Pin Select registers (if using MSSP2) should be correctly initialized prior to setting the SSPEN bit.

A typical SPI serial port initialization process follows:

- Initialize the ODCON3 register (optional open-drain output control)

- Initialize the remappable pin functions (if using MSSP2, see Section 10.7 "Peripheral Pin Select (PPS)")

- Initialize the SCKx/LAT value to the desired Idle SCKx level (if master device)

- Initialize the SCKx/PCFGx bit (if in Slave mode and multiplexed with the ANx function)

- Initialize the SCKx/TRIS bit as output (Master mode) or input (Slave mode)

- Initialize the SDIx/PCFGx bit (if SDIx is multiplexed with the ANx function)

- · Initialize the SDIx/TRIS bit

- Initialize the SSx/PCFG bit (if in Slave mode and multiplexed the with ANx function)

- Initialize the SSx/TRIS bit (Slave modes)

- · Initialize the SDOx/TRIS bit

- Initialize the SSPxSTAT register

- Initialize the SSPxCON1 register

- · Set the SSPEN bit to enable the module

Any MSSP1 serial port function that is not desired may be overridden by programming the corresponding Data Direction (TRIS) register to the opposite value. If individual MSSP2 serial port functions will not be used, they may be left unmapped.

Note: When MSSP2 is used in SPI Master mode, the SCK2 function must be configured as both an output and an input in the PPS module. SCK2 must be initialized as an output pin (by writing 0x0A to one of the RPORx registers). Additionally, SCK2IN must also be mapped to the same pin by initializing the RPINR22 register. Failure to initialize SCK2/SCK2IN as both output and input will prevent the module from receiving data on the SDI2 pin, as the module uses the SCK2IN signal to latch the received data.

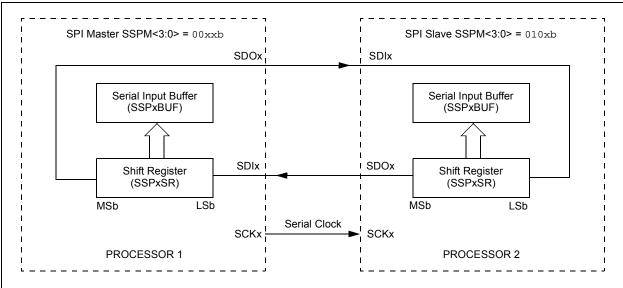

#### 20.3.5 TYPICAL CONNECTION

Figure 20-2 illustrates a typical connection between two microcontrollers. The master controller (Processor 1) initiates the data transfer by sending the SCKx signal. Data is shifted out of both shift registers on their programmed clock edge and latched on the opposite edge of the clock. Both processors should be programmed to the same Clock Polarity (CKP), then both controllers would send and receive data at the same time. Whether the data is meaningful (or dummy data) depends on the application software. This leads to three scenarios for data transmission:

- Master sends valid data Slave sends dummy data

- · Master sends valid data Slave sends valid data

- Master sends dummy data Slave sends valid data

#### FIGURE 20-2: SPI MASTER/SLAVE CONNECTION

| R/W-0                              | R/W-0                              | R/W-0                        | R/W-0             | R/W-0            | R/W-0           | R-1         | R/W-0 |

|------------------------------------|------------------------------------|------------------------------|-------------------|------------------|-----------------|-------------|-------|

| CSRC                               | TX9                                | TXEN <sup>(1)</sup>          | SYNC              | SENDB            | BRGH            | TRMT        | TX9D  |

| bit 7                              |                                    | •                            |                   |                  |                 |             | bit   |

| Legend:                            |                                    |                              |                   |                  |                 |             |       |

| R = Readable bit W = Writable bit  |                                    |                              |                   | U = Unimplem     | nented bit, rea | ıd as '0'   |       |

| -n = Value at POR '1' = Bit is set |                                    |                              | '0' = Bit is clea | ared             | x = Bit is unkr | nown        |       |

|                                    |                                    |                              |                   |                  |                 |             |       |

| bit 7                              | CSRC: Clock                        | Source Select                | bit               |                  |                 |             |       |

|                                    | Asynchronou                        | <u>s mode:</u>               |                   |                  |                 |             |       |

|                                    | Don't care.                        |                              |                   |                  |                 |             |       |

|                                    | <u>Synchronous</u><br>1 = Master m | iode (clock gen              | erated interna    | llv from BRG)    |                 |             |       |

|                                    |                                    | de (clock from               |                   |                  |                 |             |       |

| bit 6                              | <b>TX9:</b> 9-Bit Tr               | ansmit Enable b              | bit               |                  |                 |             |       |

|                                    |                                    | -bit transmissio             |                   |                  |                 |             |       |

|                                    |                                    | -bit transmissio             |                   |                  |                 |             |       |

| bit 5                              |                                    | mit Enable bit <sup>(1</sup> | )                 |                  |                 |             |       |

|                                    | 1 = Transmit<br>0 = Transmit       |                              |                   |                  |                 |             |       |

| bit 4                              | SYNC: EUSA                         | ART Mode Sele                | ct bit            |                  |                 |             |       |

|                                    | 1 = Synchror                       |                              |                   |                  |                 |             |       |

|                                    | 0 = Asynchro                       |                              |                   |                  |                 |             |       |

| bit 3                              |                                    | d Break Charad               | cter bit          |                  |                 |             |       |

|                                    | Asynchronou                        |                              | rt transmission   | n (cleared by ha | rdware upon (   | completion) |       |

|                                    |                                    | ak transmissior              |                   | I (cleared by ha |                 | completion) |       |

|                                    | Synchronous                        |                              | ·                 |                  |                 |             |       |

|                                    | Don't care.                        |                              |                   |                  |                 |             |       |

| bit 2                              | -                                  | Baud Rate Sele               | ect bit           |                  |                 |             |       |

|                                    | Asynchronou                        |                              |                   |                  |                 |             |       |

|                                    | 1 = High spe<br>0 = Low spee       |                              |                   |                  |                 |             |       |

|                                    | Synchronous                        |                              |                   |                  |                 |             |       |

|                                    | Unused in thi                      | is mode.                     |                   |                  |                 |             |       |

| bit 1                              | TRMT: Trans                        | mit Shift Regist             | er Status bit     |                  |                 |             |       |

|                                    | 1 = TSR is ei<br>0 = TSR is fu     |                              |                   |                  |                 |             |       |

| bit 0                              | TX9D: 9 <sup>th</sup> bit          | of Transmit Da               | ta                |                  |                 |             |       |

|                                    | Can be addre                       | ess/data bit or a            | narity hit        |                  |                 |             |       |

#### REGISTER 21-1: TXSTAX: TRANSMIT STATUS AND CONTROL REGISTER (1 ACCESS FADb: 2 FA8b)

Note 1: SREN/CREN overrides TXEN in Sync mode.

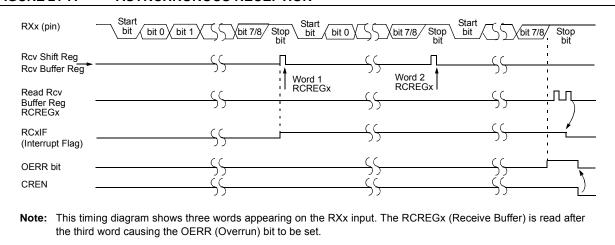

#### FIGURE 21-7: ASYNCHRONOUS RECEPTION

#### TABLE 21-6: REGISTERS ASSOCIATED WITH ASYNCHRONOUS RECEPTION

| Name     | Bit 7                | Bit 6         | Bit 5        | Bit 4  | Bit 3  | Bit 2  | Bit 1   | Bit 0  |

|----------|----------------------|---------------|--------------|--------|--------|--------|---------|--------|

| INTCON   | GIE/GIEH             | PEIE/GIEL     | TMR0IE       | INT0IE | RBIE   | TMR0IF | INT0IF  | RBIF   |

| PIR1     | PMPIF <sup>(1)</sup> | ADIF          | RC1IF        | TX1IF  | SSP1IF | CCP1IF | TMR2IF  | TMR1IF |

| PIE1     | PMPIE <sup>(1)</sup> | ADIE          | RC1IE        | TX1IE  | SSP1IE | CCP1IE | TMR2IE  | TMR1IE |

| IPR1     | PMPIP <sup>(1)</sup> | ADIP          | RC1IP        | TX1IP  | SSP1IP | CCP1IP | TMR2IP  | TMR1IP |

| PIR3     | SSP2IF               | BCL2IF        | RC2IF        | TX2IF  | TMR4IF | CTMUIF | TMR3GIF | RTCCIF |

| PIE3     | SSP2IE               | BCL2IE        | RC2IE        | TX2IE  | TMR4IE | CTMUIE | TMR3GIE | RTCCIE |

| IPR3     | SSP2IP               | BCL2IP        | RC2IP        | TX2IP  | TMR4IP | CTMUIP | TMR3GIP | RTCCIP |

| RCSTAx   | SPEN                 | RX9           | SREN         | CREN   | ADDEN  | FERR   | OERR    | RX9D   |

| RCREGx   | EUSARTx R            | eceive Regist | er           |        |        |        |         |        |

| TXSTAx   | CSRC                 | TX9           | TXEN         | SYNC   | SENDB  | BRGH   | TRMT    | TX9D   |

| BAUDCONx | ABDOVF               | RCIDL         | RXDTP        | TXCKP  | BRG16  | _      | WUE     | ABDEN  |

| SPBRGHx  | EUSARTx B            | aud Rate Ger  | nerator High | Byte   |        |        |         |        |

| SPBRGx   | EUSARTx B            | aud Rate Ger  | erator Low I | Byte   |        |        |         |        |

Legend: — = unimplemented locations read as '0'. Shaded cells are not used for asynchronous reception.

Note 1: These bits are only available on 44-pin devices.

#### 21.2.4 AUTO-WAKE-UP ON SYNC BREAK CHARACTER

During Sleep mode, all clocks to the EUSART are suspended. Because of this, the BRG is inactive and a proper byte reception cannot be performed. The auto-wake-up feature allows the controller to wake-up due to activity on the RXx/DTx line while the EUSART is operating in Asynchronous mode.

The auto-wake-up feature is enabled by setting the WUE bit (BAUDCONx<1>). Once set, the typical receive sequence on RXx/DTx is disabled and the EUSART remains in an Idle state, monitoring for a

wake-up event independent of the CPU mode. A wake-up event consists of a high-to-low transition on the RXx/DTx line. (This coincides with the start of a Sync Break or a Wake-up Signal character for the LIN/J2602 protocol.)

Following a wake-up event, the module generates an RCxIF interrupt. The interrupt is generated synchronously to the Q clocks in normal operating modes (Figure 21-8) and asynchronously if the device is in Sleep mode (Figure 21-9). The interrupt condition is cleared by reading the RCREGx register.

#### REGISTER 22-3: CONFIG3H: CONFIGURATION REGISTER 3 HIGH (BYTE ADDRESS 300005h)

| U-1          | U-1           | U-1                                                                                                                                    | U-1          | R/WO-1            | U-0               | R/WO-1          | R/WO-1  |  |  |  |  |

|--------------|---------------|----------------------------------------------------------------------------------------------------------------------------------------|--------------|-------------------|-------------------|-----------------|---------|--|--|--|--|

| _            | —             | —                                                                                                                                      | _            | MSSPMSK           |                   | ADCSEL          | IOL1WAY |  |  |  |  |

| bit 7        |               |                                                                                                                                        |              |                   |                   |                 | bit 0   |  |  |  |  |

|              |               |                                                                                                                                        |              |                   |                   |                 |         |  |  |  |  |

| Legend:      |               |                                                                                                                                        |              |                   |                   |                 |         |  |  |  |  |

| R = Readab   | le bit        | WO = Write-O                                                                                                                           | nce bit      | U = Unimplen      | nented bit, read  | as '0'          |         |  |  |  |  |

| -n = Value a | t POR         | '1' = Bit is set                                                                                                                       |              | '0' = Bit is clea | ared              | x = Bit is unkr | iown    |  |  |  |  |

|              |               |                                                                                                                                        |              |                   |                   |                 |         |  |  |  |  |

| bit 7-4      | Unimplemen    | <b>ted:</b> Program tl                                                                                                                 | he correspor | nding Flash Con   | figuration bit to | '1'             |         |  |  |  |  |

| bit 3        | MSSPMSK: N    | ISSP 7-Bit Add                                                                                                                         | lress Maskin | g Mode Enable     | bit               |                 |         |  |  |  |  |

|              | 1 = 7-Bit Add | ress Masking r                                                                                                                         | node enable  | d                 |                   |                 |         |  |  |  |  |

|              | 0 = 5-Bit Add | ress Masking r                                                                                                                         | node enable  | d                 |                   |                 |         |  |  |  |  |

| bit 2        | Unimplemen    | ted: Read as 'o                                                                                                                        | )'           |                   |                   |                 |         |  |  |  |  |

| bit 1        | ADCSEL: A/E   | O Converter Mo                                                                                                                         | de bit       |                   |                   |                 |         |  |  |  |  |

|              | 1 = 10-Bit Co | nversion mode                                                                                                                          | enabled      |                   |                   |                 |         |  |  |  |  |

|              | 0 = 12-Bit Co | nversion mode                                                                                                                          | enabled      |                   |                   |                 |         |  |  |  |  |

| bit 0        | IOL1WAY: IO   | LOCK One Wa                                                                                                                            | y Set Enable | e bit             |                   |                 |         |  |  |  |  |

|              |               | 1 = IOLOCK bit (PPSCON<0>) can be set once, provided the unlock sequence has been complete                                             |              |                   |                   |                 |         |  |  |  |  |

|              |               |                                                                                                                                        |              | egisters cannot   |                   |                 |         |  |  |  |  |

|              |               | <ul> <li>IOLOCK bit (PPSCON&lt;0&gt;) can be set and cleared as needed, provided the unlock sequence has<br/>been completed</li> </ul> |              |                   |                   |                 |         |  |  |  |  |

### 23.5.1.1 Bus Activity Detect Interrupt Bit (ACTVIF)

The ACTVIF bit cannot be cleared immediately after the USB module wakes up from Suspend mode or while the USB module is suspended. A few clock cycles are required to synchronize the internal hardware state machine before the ACTVIF bit can be cleared by firmware. Clearing the ACTVIF bit before the internal hardware is synchronized may not have an effect on the value of ACTVIF. Additionally, if the USB module uses the clock from the 96 MHz PLL source, then after clearing the SUSPND bit, the USB module

#### may not be immediately operational while waiting for the 96 MHz PLL to lock. The application code should clear the ACTVIF flag as provided in Example 23-1.

Note: Only one ACTVIF interrupt is generated when resuming from the USB bus Idle condition. If user firmware clears the ACTVIF bit, the bit will not immediately become set again, even when there is continuous bus traffic. Bus traffic must cease long enough to generate another IDLEIF condition before another ACTVIF interrupt can be generated.

#### EXAMPLE 23-1: CLEARING ACTVIF BIT (UIR<2>)

### Assembly:

```

BCF UCON, SUSPND

LOOP:

BTFSS UIR, ACTVIF

BRA DONE

BCF UIR, ACTVIF

BRA LOOP

DONE:

```

#### C:

```

UCONbits.SUSPND = 0;

while (UIRbits.ACTVIF) { UIRbits.ACTVIF = 0; }

```

#### REGISTER 28-2: CONFIG1H: CONFIGURATION REGISTER 1 HIGH (BYTE ADDRESS 300001h)

| U-1     | U-1 | U-1 | U-1 | U-0 | R/WO-1 | R/WO-1 | R/WO-1 |

|---------|-----|-----|-----|-----|--------|--------|--------|

| —       | _   | _   | _   | _   | CP0    | CPDIV1 | CPDIV0 |

| bit 7   |     |     |     |     |        |        | bit 0  |

|         |     |     |     |     |        |        |        |

| Legend: |     |     |     |     |        |        |        |

| R = Readable bit  | WO = Write-Once bit | U = Unimplemented bit, read as '0' |                    |

|-------------------|---------------------|------------------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set    | '0' = Bit is cleared               | x = Bit is unknown |

| bit 7-4 | Unimplemented: Program the corresponding Flash Configuration bit to '1'                                                                                                                          |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 3   | Unimplemented: Maintain as '0'                                                                                                                                                                   |

| bit 2   | CP0: Code Protection bit                                                                                                                                                                         |

|         | <ul><li>1 = Program memory is not code-protected</li><li>0 = Program memory is code-protected</li></ul>                                                                                          |

| bit 1-0 | CPDIV<1:0>: CPU System Clock Selection bits                                                                                                                                                      |

|         | <ul> <li>11 = No CPU system clock divide</li> <li>10 = CPU system clock is divided by 2</li> <li>01 = CPU system clock is divided by 3</li> <li>00 = CPU system clock is divided by 6</li> </ul> |

| ADDWF 1<br>ADDWFC 1<br>ANDWF 1<br>CLRF 1<br>COMF 1<br>CPFSEQ 1 | <b>NTED C</b><br>f, d, a<br>f, d, a<br>f, d, a<br>f, a | Description<br>DPERATIONS<br>Add WREG and f<br>Add WREG and Carry bit to f<br>AND WREG with f<br>Clear f<br>Complement f | Cycles     | <b>MSb</b><br>0010<br>0010 | 01da | ffff    | LSb  | Affected        | Notes      |

|----------------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|------------|----------------------------|------|---------|------|-----------------|------------|

| ADDWF 1<br>ADDWFC 1<br>ANDWF 1<br>CLRF 1<br>COMF 1<br>CPFSEQ 1 | f, d, a<br>f, d, a<br>f, d, a<br>f, a<br>f, d, a       | Add WREG and f<br>Add WREG and Carry bit to f<br>AND WREG with f<br>Clear f                                              | 1          |                            | 01da | fff     |      |                 |            |

| ADDWFC f<br>ANDWF f<br>CLRF f<br>COMF f<br>CPFSEQ f            | f, d, a<br>f, d, a<br>f, a<br>f, d, a                  | Add WREG and Carry bit to f<br>AND WREG with f<br>Clear f                                                                | 1          |                            | 01da | £ £ £ £ |      |                 |            |

| ANDWF f<br>CLRF f<br>COMF f<br>CPFSEQ f                        | f, d, a<br>f, a<br>f, d, a                             | AND WREG with f<br>Clear f                                                                                               |            | 0010                       |      |         | ffff | C, DC, Z, OV, N | 1, 2       |

| CLRF f<br>COMF f<br>CPFSEQ f                                   | f, a<br>f, d, a                                        | Clear f                                                                                                                  | 1          | 0010                       | 00da | ffff    | ffff | C, DC, Z, OV, N | 1, 2       |

| COMF f<br>CPFSEQ f                                             | f, d, a                                                |                                                                                                                          |            | 0001                       | 01da | ffff    | ffff | Z, N            | 1,2        |

| CPFSEQ f                                                       |                                                        | Complement f                                                                                                             | 1          | 0110                       | 101a | ffff    | ffff | Z               | 2          |

|                                                                |                                                        | Complement f                                                                                                             | 1          | 0001                       | 11da | ffff    | ffff | Z, N            | 1, 2       |

| CDESCT 4                                                       |                                                        | Compare f with WREG, Skip =                                                                                              | 1 (2 or 3) | 0110                       | 001a | ffff    | ffff | None            | 4          |

|                                                                | f, a                                                   | Compare f with WREG, Skip >                                                                                              | 1 (2 or 3) | 0110                       | 010a | ffff    | ffff | None            | 4          |

| CPFSLT f                                                       | f, a                                                   | Compare f with WREG, Skip <                                                                                              | 1 (2 or 3) | 0110                       | 000a | ffff    | ffff | None            | 1, 2       |

| DECF f                                                         | f, d, a                                                | Decrement f                                                                                                              | 1          | 0000                       | 01da | ffff    | ffff | C, DC, Z, OV, N | 1, 2, 3, 4 |

| DECFSZ f                                                       | f, d, a                                                | Decrement f, Skip if 0                                                                                                   | 1 (2 or 3) | 0010                       | 11da | ffff    | ffff |                 | 1, 2, 3, 4 |

|                                                                |                                                        | Decrement f, Skip if Not 0                                                                                               | 1 (2 or 3) | 0100                       | 11da | ffff    | ffff | None            | 1, 2       |

| INCF f                                                         | f, d, a                                                | Increment f                                                                                                              | 1          | 0010                       | 10da | ffff    | ffff | C, DC, Z, OV, N | 1, 2, 3, 4 |

|                                                                |                                                        | Increment f, Skip if 0                                                                                                   | 1 (2 or 3) | 0011                       | 11da | ffff    |      | None            | 4          |

|                                                                | f, d, a                                                | Increment f, Skip if Not 0                                                                                               | 1 (2 or 3) | 0100                       | 10da | ffff    | ffff | None            | 1, 2       |

|                                                                | f, d, a                                                | Inclusive OR WREG with f                                                                                                 | 1          | 0001                       | 00da | ffff    | ffff | Z, N            | 1, 2       |

|                                                                |                                                        | Move f                                                                                                                   | 1          | 0101                       | 00da | ffff    |      | Z, N            | 1          |

|                                                                | f <sub>s</sub> , f <sub>d</sub>                        | Move f <sub>s</sub> (source) to 1st word                                                                                 | 2          | 1100                       | ffff | ffff    | ffff |                 |            |

|                                                                | 5. u                                                   | f <sub>d</sub> (destination) 2nd word                                                                                    |            | 1111                       |      | ffff    | ffff |                 |            |

| MOVWF f                                                        | f, a                                                   | Move WREG to f                                                                                                           | 1          | 0110                       | 111a | ffff    | ffff | None            |            |

|                                                                |                                                        | Multiply WREG with f                                                                                                     | 1          | 0000                       | 001a | ffff    | ffff | None            | 1, 2       |

|                                                                |                                                        | Negate f                                                                                                                 | 1          | 0110                       | 110a | ffff    | ffff | C, DC, Z, OV, N |            |

|                                                                |                                                        | Rotate Left f through Carry                                                                                              | 1          | 0011                       | 01da | ffff    |      | C, Z, N         | 1, 2       |

|                                                                |                                                        | Rotate Left f (No Carry)                                                                                                 | 1          | 0100                       | 01da | ffff    | ffff |                 | , ,        |

|                                                                |                                                        | Rotate Right f through Carry                                                                                             | 1          | 0011                       | 00da | ffff    |      | C, Z, N         |            |

|                                                                |                                                        | Rotate Right f (No Carry)                                                                                                | 1          | 0100                       | 00da | ffff    | ffff |                 |            |

|                                                                | f, a                                                   | Set f                                                                                                                    | 1          | 0110                       | 100a | ffff    | ffff | •               | 1, 2       |

|                                                                | f, d, a                                                | Subtract f from WREG with                                                                                                | 1          | 0101                       | 01da | ffff    |      | C, DC, Z, OV, N | , ,        |

|                                                                | , - , -                                                | Borrow                                                                                                                   |            |                            |      |         |      | -, -, , - ,     |            |

| SUBWF f                                                        | f, d, a                                                | Subtract WREG from f                                                                                                     | 1          | 0101                       | 11da | ffff    | ffff | C, DC, Z, OV, N | 1, 2       |

|                                                                | f, d, a                                                | Subtract WREG from f with                                                                                                | 1          | 0101                       | 10da | ffff    |      | C, DC, Z, OV, N |            |

| -                                                              | , -, -:                                                | Borrow                                                                                                                   |            |                            |      |         |      | , -, ,, -       |            |

| SWAPF f                                                        | f, d, a                                                | Swap Nibbles in f                                                                                                        | 1          | 0011                       | 10da | ffff    | ffff | None            | 4          |

|                                                                | f, a                                                   | Test f, Skip if 0                                                                                                        | 1 (2 or 3) | 0110                       | 011a | ffff    |      | None            | 1, 2       |

|                                                                |                                                        | Exclusive OR WREG with f                                                                                                 | 1          |                            | 10da | ffff    | ffff |                 | ,_         |

#### TABLE 29-2: PIC18F47J53 FAMILY INSTRUCTION SET

**Note 1:** When a PORT register is modified as a function of itself (e.g., MOVF PORTB, 1, 0), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared if assigned.

**3:** If Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

4: Some instructions are two-word instructions. The second word of these instructions will be executed as a NOP unless the first word of the instruction retrieves the information embedded in these 16 bits. This ensures that all program memory locations have a valid instruction.

| MOVSS                                              | Move Indexed to Indexed                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                    |  |    |  |  |  |

|----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|----|--|--|--|

| Syntax:                                            | MOVSS                                                                                                                                                                                                                                            | MOVSS [z <sub>s</sub> ], [z <sub>d</sub> ]                                                                                                                                                                                                                                                                                                                         |  |    |  |  |  |

| Operands:                                          | $\begin{array}{l} 0 \leq z_s \leq 127 \\ 0 \leq z_d \leq 127 \end{array}$                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                    |  |    |  |  |  |

| Operation:                                         | ((FSR2) +                                                                                                                                                                                                                                        | $((FSR2) + z_s) \rightarrow ((FSR2) + z_d)$                                                                                                                                                                                                                                                                                                                        |  |    |  |  |  |

| Status Affected:                                   | None                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                    |  |    |  |  |  |

| Encoding:<br>1st word (source)<br>2nd word (dest.) | 1110<br>1111                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                    |  |    |  |  |  |

| Description                                        | moved to a<br>addresses<br>registers a<br>7-bit literal<br>respective<br>registers o<br>the 4096-b                                                                                                                                               | The contents of the source register are<br>moved to the destination register. The<br>addresses of the source and destination<br>registers are determined by adding the<br>7-bit literal offsets, ' $z_s$ ' or ' $z_d$ ',<br>respectively, to the value of FSR2. Both<br>registers can be located anywhere in<br>the 4096-byte data memory space<br>(000h to FFFh). |  |    |  |  |  |

|                                                    | The MOVSS instruction cannot use the PCL, TOSU, TOSH or TOSL as the destination register.                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                    |  |    |  |  |  |

|                                                    | If the resultant source address points to<br>an Indirect Addressing register, the<br>value returned will be 00h. If the<br>resultant destination address points to<br>an Indirect Addressing register, the<br>instruction will execute as a NOP. |                                                                                                                                                                                                                                                                                                                                                                    |  |    |  |  |  |

| Words:                                             | 2                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                    |  |    |  |  |  |

| Cycles:                                            | 2                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                    |  |    |  |  |  |

| Q Cycle Activity:                                  |                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                    |  |    |  |  |  |

|                                                    | 00                                                                                                                                                                                                                                               | ~                                                                                                                                                                                                                                                                                                                                                                  |  | 04 |  |  |  |

| Q1     | Q2          | Q3          | Q4          |

|--------|-------------|-------------|-------------|

| Decode | Determine   | Determine   | Read        |

|        | source addr | source addr | source reg  |

| Decode | Determine   | Determine   | Write       |

|        | dest addr   | dest addr   | to dest reg |

| Before Instruction             |   |     |

|--------------------------------|---|-----|

| FSR2                           | = | 80h |

| Contents<br>of 85h<br>Contents | = | 33h |

| of 86h                         | = | 11h |

| After Instruction              |   |     |

| FSR2                           | = | 80h |

| Contents<br>of 85h<br>Contents | = | 33h |

| of 86h                         | = | 33h |

| PUSHL             | Store Literal at FSR2, Decrement FSR2                                                                                                                          |            |          |                      |  |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|----------|----------------------|--|

| Syntax:           | PUSHL k                                                                                                                                                        |            |          |                      |  |

| Operands:         | $0 \le k \le 255$                                                                                                                                              |            |          |                      |  |

| Operation:        | $k \rightarrow$ (FSR2),<br>FSR2 – 1 $\rightarrow$ FSR2                                                                                                         |            |          |                      |  |

| Status Affected:  | None                                                                                                                                                           |            |          |                      |  |

| Encoding:         | 1111                                                                                                                                                           | 1010       | kkkł     | k kkkk               |  |

|                   | memory address specified by FSR2.<br>FSR2 is decremented by 1 after the<br>operation.<br>This instruction allows users to push<br>values onto a software stack |            |          |                      |  |

| Words:            | 1                                                                                                                                                              | i Sonwa    | ie staer | <b>.</b>             |  |

| Cycles:           | 1                                                                                                                                                              |            |          |                      |  |

| Q Cycle Activity: |                                                                                                                                                                |            |          |                      |  |

| Q1                | Q2                                                                                                                                                             | G          | 3        | Q4                   |  |

| Decode            | Read 'k'                                                                                                                                                       | Proc<br>da |          | Write to destination |  |

| Example:          | PUSHL 08                                                                                                                                                       |            |          |                      |  |

| Before Instruction<br>FSR2H:FSR2L<br>Memory (01ECh) | =<br>= | 01ECh<br>00h |

|-----------------------------------------------------|--------|--------------|

| After Instruction<br>FSR2H:FSR2L<br>Memory (01ECh)  | =<br>= | 01EBh<br>08h |

### 31.2 DC Characteristics: Power-Down and Supply Current PIC18F47J53 Family (Industrial)

| PIC18LF                                                                                                                                                  | 47J53 Family                            | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial |        |       |            |                                                                                             |                                   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|--------|-------|------------|---------------------------------------------------------------------------------------------|-----------------------------------|