Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-XF

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 48MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART, USB                              |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 22                                                                          |

| Program Memory Size        | 64KB (32K x 16)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 3.8K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 2.75V                                                                  |

| Data Converters            | A/D 10x10b/12b                                                              |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-VQFN Exposed Pad                                                         |

| Supplier Device Package    | 28-QFN (6×6)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf26j53-i-ml |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

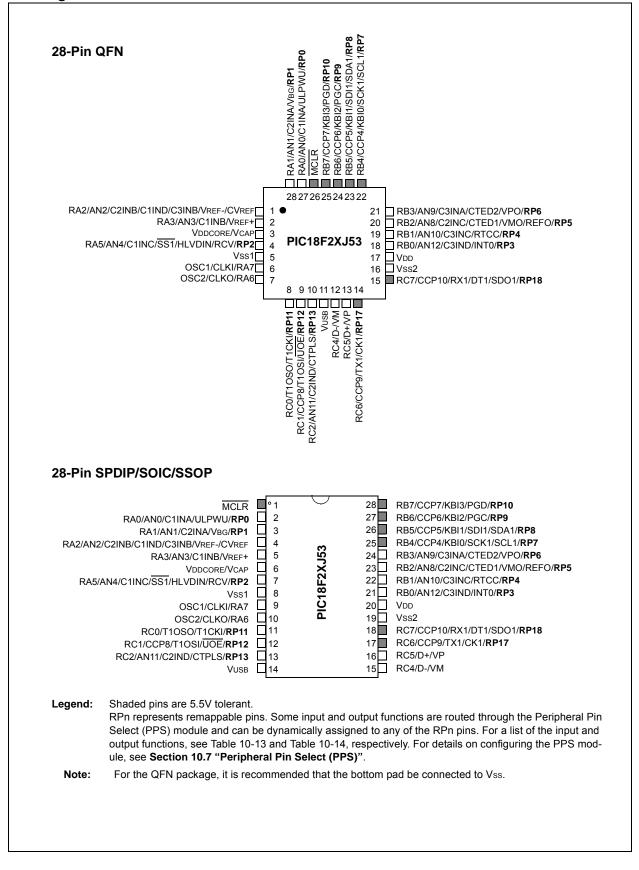

#### **Pin Diagrams**

| Input Oscillator<br>Frequency | PLL Division<br>(PLLDIV<2:0>) | Clock Mode<br>(FOSC<2:0>) | MCU Clock Division<br>(CPDIV<1:0>) | Microcontroller<br>Clock Frequency |

|-------------------------------|-------------------------------|---------------------------|------------------------------------|------------------------------------|

|                               |                               |                           | None (11)                          | 48 MHz                             |

|                               |                               | 50                        | ÷2(10)                             | 24 MHz                             |

| 48 MHz                        | N/A                           | EC                        | ÷3(01)                             | 16 MHz                             |

|                               |                               |                           | ÷6 (00)                            | 8 MHz                              |

|                               |                               |                           | None (11)                          | 48 MHz                             |

|                               | 10 (000)                      | FORM                      | ÷2(10)                             | 24 MHz                             |

| 48 MHz                        | ÷12 (000)                     | ECPLL                     | ÷3(01)                             | 16 MHz                             |

|                               |                               |                           | ÷6 (00)                            | 8 MHz                              |

|                               |                               |                           | None (11)                          | 48 MHz                             |

|                               | 10 (001)                      | FORM                      | ÷2(10)                             | 24 MHz                             |

| 40 MHz                        | ÷10(001)                      | ECPLL                     | ÷3(01)                             | 16 MHz                             |

|                               |                               |                           | ÷6 (00)                            | 8 MHz                              |

|                               |                               |                           | None (11)                          | 48 MHz                             |

|                               | 0 (00.0)                      | FORM                      | ÷2 (10)                            | 24 MHz                             |

| 24 MHz                        | ÷6(010)                       | ECPLL                     | ÷3(01)                             | 16 MHz                             |

|                               |                               |                           | ÷6 (00)                            | 8 MHz                              |

|                               | N/A                           | EC <sup>(1)</sup>         | None (11)                          | 24 MHz                             |

|                               |                               |                           | ÷2 (10)                            | 12 MHz                             |

| 24 MHz                        |                               |                           | ÷3 (01)                            | 8 MHz                              |

|                               |                               |                           | ÷6 (00)                            | 4 MHz                              |

|                               | ÷5 (011)                      | ECPLL                     | None (11)                          | 48 MHz                             |

|                               |                               |                           | ÷2 (10)                            | 24 MHz                             |

| 20 MHz                        |                               |                           | ÷3(01)                             | 16 MHz                             |

|                               |                               |                           | ÷6 (00)                            | 8 MHz                              |

|                               |                               |                           | None (11)                          | 48 MHz                             |

|                               |                               |                           | ÷2 (10)                            | 24 MHz                             |

| 16 MHz                        | ÷4 (100)                      | HSPLL, ECPLL              | ÷3 (01)                            | 16 MHz                             |

|                               |                               |                           | ÷6 (00)                            | 8 MHz                              |

|                               |                               |                           | None (11)                          | 48 MHz                             |

|                               | 0 (2.22.)                     |                           | ÷2 (10)                            | 24 MHz                             |

| 12 MHz                        | ÷3(101)                       | HSPLL, ECPLL              | ÷3(01)                             | 16 MHz                             |

|                               |                               |                           | ÷6 (00)                            | 8 MHz                              |

|                               |                               |                           | None (11)                          | 48 MHz                             |

| 0.1411-                       | 0 (5 5 5)                     | HSPLL, ECPLL,             | ÷2 (10)                            | 24 MHz                             |

| 8 MHz                         | ÷2 (110)                      | INTOSCPLL/<br>INTOSCPLLO  | ÷3(01)                             | 16 MHz                             |

|                               |                               |                           | ÷6 (00)                            | 8 MHz                              |

|                               |                               |                           | None (11)                          | 48 MHz                             |

| 4.8411                        | 4 ()                          |                           | ÷2 (10)                            | 24 MHz                             |

| 4 MHz                         | ÷ <b>1</b> (111)              | HSPLL, ECPLL              | ÷3(01)                             | 16 MHz                             |

|                               |                               |                           | ÷6 (00)                            | 8 MHz                              |

| <b>TABLE 3-5:</b> | OSCILLATOR CONFIGURATION OPTIONS FOR USB OPERATION |

|-------------------|----------------------------------------------------|

|                   |                                                    |

Note 1: The 24 MHz EC mode (without PLL) is only compatible with low-speed USB. Full-speed USB requires a 48 MHz system clock.

#### 6.2.3 INSTRUCTIONS IN PROGRAM MEMORY

The program memory is addressed in bytes. Instructions are stored as 2 bytes or 4 bytes in program memory. The Least Significant Byte (LSB) of an instruction word is always stored in a program memory location with an even address (LSB = 0). To maintain alignment with instruction boundaries, the PC increments in steps of 2 and the LSB will always read '0' (see Section 6.1.3 "Program Counter").

Figure 6-5 provides an example of how instruction words are stored in the program memory.

The CALL and GOTO instructions have the absolute program memory address embedded into the instruction. Since instructions are always stored on word boundaries, the data contained in the instruction is a word address. The word address is written to PC<20:1>, which accesses the desired byte address in program memory. Instruction #2 in Figure 6-5 displays how the instruction, GOTO 0006h, is encoded in the program memory. Program branch instructions, which encode a relative address offset, operate in the same manner. The offset value stored in a branch instruction represents the number of single-word instructions that the PC will be offset by. Section 29.0 "Instruction Set Summary" provides further details of the instruction set.

|                |            |                    | LSB = 1 | LSB = 0 | Word Address $\downarrow$ |

|----------------|------------|--------------------|---------|---------|---------------------------|

|                | Program N  |                    |         |         | 000000h                   |

|                | Byte Locat | ions $\rightarrow$ |         |         | 000002h                   |

|                |            |                    |         |         | 000004h                   |

|                |            |                    |         |         | 000006h                   |

| Instruction 1: | MOVLW      | 055h               | 0Fh     | 55h     | 000008h                   |

| Instruction 2: | GOTO       | 0006h              | EFh     | 03h     | 00000Ah                   |

|                |            |                    | F0h     | 00h     | 00000Ch                   |

| Instruction 3: | MOVFF      | 123h, 456          | h C1h   | 23h     | 00000Eh                   |

|                |            |                    | F4h     | 56h     | 000010h                   |

|                |            |                    |         |         | 000012h                   |

|                |            |                    |         |         | 000014h                   |

#### FIGURE 6-5: INSTRUCTIONS IN PROGRAM MEMORY

#### 6.2.4 TWO-WORD INSTRUCTIONS

The standard PIC18 instruction set has four two-word instructions: CALL, MOVFF, GOTO and LSFR. In all cases, the second word of the instructions always has '1111' as its four Most Significant bits (MSbs); the other 12 bits are literal data, usually a data memory address.

The use of '1111' in the 4 MSbs of an instruction specifies a special form of NOP. If the instruction is executed in proper sequence immediately after the first word, the data in the second word is accessed and

#### EXAMPLE 6-4: TWO-WORD INSTRUCTIONS

used by the instruction sequence. If the first word is skipped for some reason and the second word is executed by itself, a NOP is executed instead. This is necessary for cases when the two-word instruction is preceded by a conditional instruction that changes the PC. Example 6-4 illustrates how this works.

Note: See Section 6.5 "Program Memory and the Extended Instruction Set" for information on two-word instructions in the extended instruction set.

| CASE 1:      |          |             |             |                              |  |  |  |  |

|--------------|----------|-------------|-------------|------------------------------|--|--|--|--|

| Object Code  |          | Source Code | Source Code |                              |  |  |  |  |

| 0110 0110 00 | 0000 000 | TSTFSZ      | REG1        | ; is RAM location 0?         |  |  |  |  |

| 1100 0001 00 | 010 0011 | MOVFF       | REG1, REG2  | ; No, skip this word         |  |  |  |  |

| 1111 0100 01 | LO1 0110 |             |             | ; Execute this word as a NOP |  |  |  |  |

| 0010 0100 00 | 0000 000 | ADDWF       | REG3        | ; continue code              |  |  |  |  |

| CASE 2:      |          |             |             |                              |  |  |  |  |

| Object Code  |          | Source Code | 9           |                              |  |  |  |  |

| 0110 0110 00 | 0000 000 | TSTFSZ      | REG1        | ; is RAM location 0?         |  |  |  |  |

| 1100 0001 00 | 010 0011 | MOVFF       | REG1, REG2  | ; Yes, execute this word     |  |  |  |  |

| 1111 0100 01 | LO1 0110 |             |             | ; 2nd word of instruction    |  |  |  |  |

| 0010 0100 00 | 0000 000 | ADDWF       | REG3        | ; continue code              |  |  |  |  |

| TABLE 6-4: REGISTER FILE SUMMARY (PIC18F47J53 FAMILY) (CONTINUED) |           |                      |                      |                      |               |                |                        |           |                                 |                      |

|-------------------------------------------------------------------|-----------|----------------------|----------------------|----------------------|---------------|----------------|------------------------|-----------|---------------------------------|----------------------|

| Addr.                                                             | File Name | Bit 7                | Bit 6                | Bit 5                | Bit 4         | Bit 3          | Bit 2                  | Bit 1     | Bit 0                           | Value on<br>POR, BOR |

| F53h                                                              | CVRCON    | CVREN                | CVROE                | CVRR                 | CVRSS         | CVR3           | CVR2                   | CVR1      | CVR0                            | 0000 0000            |

| F52h                                                              | CCPTMRS0  | C3TSEL1              | C3TSEL0              | C2TSEL2              | C2TSEL1       | C2TSEL0        | C1TSEL2                | C1TSEL1   | C1TSEL0                         | 0000 0000            |

| F51h                                                              | CCPTMRS1  | C7TSEL1              | C7TSEL0              | _                    | C6TSEL0       | _              | C5TSEL0                | C4TSEL1   | C4TSEL0                         | 00-0 -000            |

| F50h                                                              | CCPTMRS2  | _                    | —                    | _                    | C10TSEL0(3)   | _              | C9TSEL0 <sup>(3)</sup> | C8TSEL1   | C8TSEL0                         | 0 -000               |

| F4Fh                                                              | DSGPR1    | Deep Sleep           | Persistent Ge        | neral Purpose        | Register (con | tents retained | even in deep           | sleep)    |                                 | xxxx xxxx            |

| F4Eh                                                              | DSGPR0    | Deep Sleep           | Persistent Ge        | neral Purpose        | Register (con | tents retained | even in deep           | sleep)    |                                 | xxxx xxxx            |

| F4Dh                                                              | DSCONH    | DSEN                 | _                    | _                    | _             | _              | r                      | DSULPEN   | RTCWDIS                         | 0000                 |

| F4Ch                                                              | DSCONL    | _                    | _                    | _                    | _             | _              | ULPWDIS                | DSBOR     | RELEASE                         | 000                  |

| F4Bh                                                              | DSWAKEH   | _                    | _                    | _                    | _             | _              | _                      | _         | DSINT0                          | 0                    |

| F4Ah                                                              | DSWAKEL   | DSFLT                | _                    | DSULP                | DSWDT         | DSRTC          | DSMCLR                 | _         | DSPOR                           | 0-00 00-1            |

| F49h                                                              | ANCON1    | VBGEN                |                      |                      | PCFG12        | PCFG11         | PCFG10                 | PCFG9     | PCFG8                           | 00 0000              |

| F48h                                                              | ANCON0    | PCFG7 <sup>(1)</sup> | PCFG6 <sup>(1)</sup> | PCFG5 <sup>(1)</sup> | PCFG4         | PCFG3          | PCFG2                  | PCFG1     | PCFG0                           | 0000 0000            |

| F47h                                                              | OEDCON    | ALRMEN               | CHIME                | AMASK3               | AMASK2        | AMASK1         | AMASK0                 | ALRMPTR1  | ALRMPTR0                        | 0000 0000            |

| F46h                                                              | ALRMRPT   | ARPT7                | ARPT6                | ARPT5                | ARPT4         | ARPT3          | ARPT2                  | ARPT1     | ARPT0                           | 0000 0000            |

| F45h                                                              | ALRMVALH  | -                    |                      |                      | ed on ALRMP1  |                |                        | /         | 744.10                          | xxxx xxxx            |

| F44h                                                              | ALRMVALL  | 1                    |                      |                      | d on ALRMPT   |                |                        |           |                                 | xxxx xxxx            |

| F43h                                                              | _         | _                    |                      |                      | _             | _              | _                      |           |                                 |                      |

| F42h                                                              | ODCON1    | CCP8OD               | CCP70D               | CCP6OD               | CCP50D        | CCP4OD         | ECCP3OD                | ECCP2OD   | ECCP10D                         | 0000 0000            |

| F41h                                                              | ODCON2    |                      |                      |                      |               | CCP100D        | CCP90D                 | U2OD      | U10D                            | 0000                 |

| F40h                                                              | ODCON2    | _                    |                      | _                    | _             |                | 001 300                | SPI2OD    | SPI10D                          | 00                   |

| F3Fh                                                              | RTCCFG    | RTCEN                |                      |                      | RTCSYNC       | HALFSEC        | RTCOE                  | RTCPTR1   | RTCPTR0                         | 0-00 0000            |

|                                                                   | RTCCAL    | -                    | -                    |                      |               |                |                        |           |                                 |                      |

| F3Eh                                                              | REFOCON   | CAL7                 | CAL6                 | CAL5                 | CAL4          | CAL3           | CAL2                   | CAL1      | CAL0                            | 0000 0000            |

| F3Dh                                                              |           | ROON                 | —                    | ROSSLP               | ROSEL         | RODIV3         | RODIV2                 | RODIV1    | RODIV0<br>PMPTTL <sup>(1)</sup> |                      |

| F3Ch                                                              | PADCFG1   |                      |                      |                      |               |                | RTSECSEL1              | RTSECSEL0 | PNPTILY                         | 000                  |

| F3Bh                                                              | RTCVALH   |                      |                      |                      | ed on RTCPT   |                |                        |           |                                 | 0xxx xxxx            |

| F3Ah                                                              | RTCVALL   | 1                    |                      | WINDOW Base          |               | 1              | FOEN                   | 0004      | DDDA                            | 0xxx xxxx            |

| F39h                                                              | UCFG      | UTEYE                | UOEMON               | -                    |               | UTRDIS         | FSEN                   | PPB1      | PPB0                            | 00-0 0000            |

| F38h                                                              | UADDR     |                      | ADDR6                | ADDR5                | ADDR4         | ADDR3          | ADDR2                  | ADDR1     | ADDR0                           | -000 0000            |

| F37h                                                              | UEIE      | BTSEE                | -                    | -                    | BTOEE         | DFN8EE         | CRC16EE                | CRC5EE    | PIDEE                           | 00 0000              |

| F36h                                                              | UIE       | —                    | SOFIE                | STALLIE              | IDLEIE        | TRNIE          | ACTVIE                 | UERRIE    | URSTIE                          | -000 0000            |

| F35h                                                              | UEP15     | _                    |                      |                      | EPHSHK        | EPCONDIS       | EPOUTEN                | EPINEN    | EPSTALL                         | 0 0000               |

| F34h                                                              | UEP14     | _                    | _                    | _                    | EPHSHK        | EPCONDIS       | EPOUTEN                | EPINEN    | EPSTALL                         | 0 0000               |

| F33h                                                              | UEP13     | _                    | _                    | _                    | EPHSHK        | EPCONDIS       | EPOUTEN                | EPINEN    | EPSTALL                         | 0 0000               |

| F32h                                                              | UEP12     | _                    | _                    | _                    | EPHSHK        | EPCONDIS       | EPOUTEN                | EPINEN    | EPSTALL                         | 0 0000               |

| F31h                                                              | UEP11     | —                    | _                    | _                    | EPHSHK        | EPCONDIS       | EPOUTEN                | EPINEN    | EPSTALL                         | 0 0000               |

| F30h                                                              | UEP10     | —                    | —                    | —                    | EPHSHK        | EPCONDIS       | EPOUTEN                | EPINEN    | EPSTALL                         | 0 0000               |

| F2Fh                                                              | UEP9      | _                    | _                    | _                    | EPHSHK        | EPCONDIS       | EPOUTEN                | EPINEN    | EPSTALL                         | 0 0000               |

| F2Eh                                                              | UEP8      | —                    | —                    | —                    | EPHSHK        | EPCONDIS       | EPOUTEN                | EPINEN    | EPSTALL                         | 0 0000               |

| F2Dh                                                              | UEP7      | _                    | _                    | _                    | EPHSHK        | EPCONDIS       | EPOUTEN                | EPINEN    | EPSTALL                         | 0 0000               |

| F2Ch                                                              | UEP6      | _                    | _                    | _                    | EPHSHK        | EPCONDIS       | EPOUTEN                | EPINEN    | EPSTALL                         | 0 0000               |

| F2Bh                                                              | UEP5      | —                    | —                    | —                    | EPHSHK        | EPCONDIS       | EPOUTEN                | EPINEN    | EPSTALL                         | 0 0000               |

| F2Ah                                                              | UEP4      | _                    | _                    | _                    | EPHSHK        | EPCONDIS       | EPOUTEN                | EPINEN    | EPSTALL                         | 0 0000               |

| F29h                                                              | UEP3      | —                    | —                    | —                    | EPHSHK        | EPCONDIS       | EPOUTEN                | EPINEN    | EPSTALL                         | 0 0000               |

| F28h                                                              | UEP2      | _                    | —                    | —                    | EPHSHK        | EPCONDIS       | EPOUTEN                | EPINEN    | EPSTALL                         | 0 0000               |

| F27h                                                              | UEP1      | —                    | —                    | —                    | EPHSHK        | EPCONDIS       | EPOUTEN                | EPINEN    | EPSTALL                         | 0 0000               |

| F26h                                                              | UEP0      | —                    | —                    | —                    | EPHSHK        | EPCONDIS       | EPOUTEN                | EPINEN    | EPSTALL                         | 0 0000               |

| F25h                                                              | CM3CON    | CON                  | COE                  | CPOL                 | EVPOL1        | EVPOL0         | CREF                   | CCH1      | CCH0                            | 0001 1111            |

| F24h                                                              | TMR5H     | Timer5 Regis         | ster High Byte       |                      |               |                |                        |           |                                 | xxxx xxxx            |

| TABLE 6-4: | <b>REGISTER FILE SUMMARY (</b> | PIC18F47J53 FAMILY) | (CONTINUED) |

|------------|--------------------------------|---------------------|-------------|

|            |                                |                     |             |

Legend:x = unknown, u = unchanged, - = unimplemented, q = value depends on condition, r = reserved, do not modifyNote1:Implemented only for 44-pin devices (PIC18F46J53, PIC18F47J53, PIC18LF46J53 and PIC18LF47J53).

2: Implemented only for 28-pin devices (PIC18F26J53, PIC18F27J53, PIC18LF26J53 and PIC18LF27J53).

3: Implemented only for devices with 128 Kbyte of program memory (PIC18F27J53, PIC18F47J53, PIC18LF27J53 and PIC18LF47J53).

| TABLI | E 6-4: R  | EGISTER      | FILE SUN       | MMARY (        | PIC18F47     | J53 FAMI         | LY) (CON         | TINUED)        |         |                      |  |  |

|-------|-----------|--------------|----------------|----------------|--------------|------------------|------------------|----------------|---------|----------------------|--|--|

| Addr. | File Name | Bit 7        | Bit 6          | Bit 5          | Bit 4        | Bit 3            | Bit 2            | Bit 1          | Bit 0   | Value on<br>POR, BOR |  |  |

| F23h  | TMR5L     | Timer5 Regis | ster Low Bytes | 6              |              |                  |                  |                |         | xxxx xxxx            |  |  |

| F22h  | T5CON     | TMR5CS1      | TMR5CS0        | T5CKPS1        | T5CKPS0      | T5OSCEN          | T5SYNC           | RD16           | TMR5ON  | 0000 0000            |  |  |

| F21h  | T5GCON    | TMR5GE       | T5GPOL         | T5GTM          | T5GSPM       | T5GGO/<br>T5DONE | T5GVAL           | T5GSS1         | T5GSS0  | 0000 0x00            |  |  |

| F20h  | TMR6      | Timer6 Regis | mer6 Register  |                |              |                  |                  |                |         |                      |  |  |

| F1Fh  | PR6       | Timer6 Perio | d Register     |                |              |                  |                  |                |         | 1111 1111            |  |  |

| F1Eh  | T6CON     | —            | T6OUTPS3       | T6OUTPS2       | T6OUTPS1     | T6OUTPS0         | TMR6ON           | T6CKPS1        | T6CKPS0 | -000 0000            |  |  |

| F1Dh  | TMR8      | Timer8 Regis | ster           |                |              |                  |                  |                |         | 0000 0000            |  |  |

| F1Ch  | PR8       | Timer8 Perio | d Register     |                |              |                  |                  |                |         | 1111 1111            |  |  |

| F1Bh  | T8CON     | _            | T8OUTPS3       | T8OUTPS2       | T8OUTPS1     | T8OUTPS0         | TMR8ON           | T8CKPS1        | T8CKPS0 | -000 0000            |  |  |

| F1Ah  | PSTR3CON  | CMPL1        | CMPL0          | _              | STRSYNC      | STRD             | STRC             | STRB           | STRA    | 00-0 0001            |  |  |

| F19h  | ECCP3AS   | ECCP3ASE     | ECCP3AS2       | ECCP3AS1       | ECCP3AS0     | PSS3AC1          | PSS3AC0          | PSS3BD1        | PSS3BD0 | 0000 0000            |  |  |

| F18h  | ECCP3DEL  | P3RSEN       | P3DC6          | P3DC5          | P3DC4        | P3DC3            | P3DC2            | P3DC1          | P3DC0   | 0000 0000            |  |  |

| F17h  | CCPR3H    | Capture/Com  | npare/PWM R    | egister 3 High | n Byte       |                  |                  |                |         | XXXX XXXX            |  |  |

| F16h  | CCPR3L    | Capture/Com  | npare/PWM R    | egister 3 Low  | Byte         |                  |                  |                |         | XXXX XXXX            |  |  |

| F15h  | CCP3CON   | P3M1         | P3M0           | DC3B1          | DC3B0        | CCP3M3           | CCP3M2           | CCP3M1         | CCP3M0  | 0000 0000            |  |  |

| F14h  | CCPR4H    | Capture/Com  | npare/PWM R    | egister 4 High | n Byte       |                  |                  |                |         | xxxx xxxx            |  |  |

| F13h  | CCPR4L    | Capture/Con  | npare/PWM R    | egister 4 Low  | Byte         |                  |                  |                |         | xxxx xxxx            |  |  |

| F12h  | CCP4CON   | —            | _              | DC4B1          | DC4B0        | CCP4M3           | CCP4M2           | CCP4M1         | CCP4M0  | 00 0000              |  |  |

| F11h  | CCPR5H    | Capture/Com  | npare/PWM R    | egister 5 High | n Byte       | •                | •                |                | •       | xxxx xxxx            |  |  |

| F10h  | CCPR5L    | Capture/Com  | npare/PWM R    | egister 5 Low  | Byte         |                  |                  |                |         | xxxx xxxx            |  |  |

| F0Fh  | CCP5CON   | _            | _              | DC5B1          | DC5B0        | CCP5M3           | CCP5M2           | CCP5M1         | CCP5M0  | 00 0000              |  |  |

| F0Eh  | CCPR6H    | Capture/Com  | pare/PWM R     | egister 6 High | n Byte       |                  |                  |                |         | xxxx xxxx            |  |  |

| F0Dh  | CCPR6L    | Capture/Com  | pare/PWM R     | egister 6 Low  | Byte         |                  |                  |                |         | xxxx xxxx            |  |  |

| F0Ch  | CCP6CON   | _            | —              | DC6B1          | DC6B0        | CCP6M3           | CCP6M2           | CCP6M1         | CCP6M0  | 00 0000              |  |  |

| F0Bh  | CCPR7H    | Capture/Com  | pare/PWM R     | egister 7 High | n Byte       |                  |                  |                |         | xxxx xxxx            |  |  |

| F0Ah  | CCPR7L    | Capture/Com  | pare/PWM R     | egister 7 Low  | Byte         |                  |                  |                |         | xxxx xxxx            |  |  |

| F09h  | CCP7CON   | _            | _              | DC7B1          | DC7B0        | CCP7M3           | CCP7M2           | CCP7M1         | CCP7M0  | 00 0000              |  |  |

| F08h  | CCPR8H    | Capture/Corr | pare/PWM R     | egister 8 High | n Byte       |                  |                  |                |         | xxxx xxxx            |  |  |

| F07h  | CCPR8L    | Capture/Con  | pare/PWM R     | egister 8 Low  | Byte         |                  |                  |                |         | xxxx xxxx            |  |  |

| F06h  | CCP8CON   | _            | _              | DC8B1          | DC8B0        | CCP8M3           | CCP8M2           | CCP8M1         | CCP8M0  | 00 0000              |  |  |

| F05h  | CCPR9H    | Capture/Corr | pare/PWM R     | egister 9 High | n Byte       |                  |                  |                |         | xxxx xxxx            |  |  |

| F04h  | CCPR9L    | Capture/Con  | pare/PWM R     | egister 9 Low  | Byte         |                  |                  |                |         | xxxx xxxx            |  |  |

| F03h  | CCP9CON   | _            | _              | DC9B1          | DC9B0        | CCP9M3           | CCP9M2           | CCP9M1         | CCP9M0  | 00 0000              |  |  |

| F02h  | CCPR10H   | Capture/Corr | pare/PWM R     | egister 10 Hig | gh Byte      |                  |                  |                |         | xxxx xxxx            |  |  |

| F01h  | CCPR10L   | Capture/Corr | pare/PWM R     | egister 10 Lov | w Byte       |                  |                  |                |         | xxxx xxxx            |  |  |

| F00h  | CCP10CON  | _            | _              | DC10B1         | DC10B0       | CCP10M3          | CCP10M2          | CCP10M1        | CCP10M0 | 00 0000              |  |  |

| EFFh  | RPINR24   | _            | _              | _              | PWM Fault In | put (FLT0) to    | Input Pin Map    | ping bits      |         | 1 1111               |  |  |

| EFEh  | RPINR23   | _            | _              | _              | SPI2 Slave S | elect Input (SS  | S2) to Input Pir | n Mapping bits |         | 1 1111               |  |  |

| EFDh  | RPINR22   | _            | _              | _              | -            |                  | Input Pin Map    |                |         | 1 1111               |  |  |

| EFCh  | RPINR21   | _            | _              | _              |              |                  | nput Pin Mapp    | · ·            |         | 1 1111               |  |  |

| EFBh  | _         | _            |                | _              | _            | _                |                  |                |         |                      |  |  |

| EFAh  | _         | _            | _              | _              | _            | _                | _                | _              | _       |                      |  |  |

| EF9h  | _         | _            | _              | _              | _            | _                | _                | _              | _       | 1                    |  |  |

| EF8h  | RPINR17   | _            | _              | _              | EUSART2 CI   | ock Input (CK)   | 2) to Input Pin  | Mapping hits   |         | 1 1111               |  |  |

| EF7h  | RPINR16   |              |                |                | -            |                  | t Pin Mapping    |                |         | 1 1111               |  |  |

| EF6h  |           | _            | _              |                |              |                  |                  |                | _       |                      |  |  |

| EF5h  |           |              |                |                | _            |                  |                  |                |         |                      |  |  |

| - 51  |           |              |                |                |              |                  |                  |                |         | 1                    |  |  |

### TABLE 6-4: REGISTER FILE SUMMARY (PIC18F47J53 FAMILY) (CONTINUED)

$Legend: \quad x = unknown, u = unchanged, - = unimplemented, q = value depends on condition, r = reserved, do not modify a second s$

Note 1: Implemented only for 44-pin devices (PIC18F46J53, PIC18F47J53, PIC18LF46J53 and PIC18LF47J53).

2: Implemented only for 28-pin devices (PIC18F26J53, PIC18F27J53, PIC18LF26J53 and PIC18LF27J53).

3: Implemented only for devices with 128 Kbyte of program memory (PIC18F27J53, PIC18F47J53, PIC18LF27J53 and PIC18LF47J53).

## 6.6 Data Memory and the Extended Instruction Set

Enabling the PIC18 extended instruction set (XINST Configuration bit = 1) significantly changes certain aspects of data memory and its addressing. Specifically, the use of the Access Bank for many of the core PIC18 instructions is different. This is due to the introduction of a new addressing mode for the data memory space. This mode also alters the behavior of Indirect Addressing using FSR2 and its associated operands.

What does not change is just as important. The size of the data memory space is unchanged, as well as its linear addressing. The SFR map remains the same. Core PIC18 instructions can still operate in both Direct and Indirect Addressing mode; inherent and literal instructions do not change at all. Indirect Addressing with FSR0 and FSR1 also remains unchanged.

### 6.6.1 INDEXED ADDRESSING WITH LITERAL OFFSET

Enabling the PIC18 extended instruction set changes the behavior of Indirect Addressing using the FSR2 register pair and its associated file operands. Under proper conditions, instructions that use the Access Bank, that is, most bit and byte-oriented instructions, can invoke a form of Indexed Addressing using an offset specified in the instruction. This special addressing mode is known as Indexed Addressing with Literal Offset or Indexed Literal Offset mode.

When using the extended instruction set, this addressing mode requires the following:

- The use of the Access Bank is forced ('a' = 0); and

- The file address argument is less than or equal to 5Fh.

Under these conditions, the file address of the instruction is not interpreted as the lower byte of an address (used with the BSR in Direct Addressing) or as an 8-bit address in the Access Bank. Instead, the value is interpreted as an offset value to an Address Pointer specified by FSR2. The offset and the contents of FSR2 are added to obtain the target address of the operation.

#### 6.6.2 INSTRUCTIONS AFFECTED BY INDEXED LITERAL OFFSET MODE

Any of the core PIC18 instructions that can use Direct Addressing are potentially affected by the Indexed Literal Offset Addressing mode. This includes all byte and bit-oriented instructions, or almost one-half of the standard PIC18 instruction set. Instructions that only use Inherent or Literal Addressing modes are unaffected.

Additionally, byte and bit-oriented instructions are not affected if they use the Access Bank (Access RAM bit is '1') or include a file address of 60h or above. Instructions meeting these criteria will continue to execute as before. A comparison of the different possible addressing modes when the extended instruction set is enabled is provided in Figure 6-9.

Those who desire to use byte or bit-oriented instructions in the Indexed Literal Offset mode should note the changes to assembler syntax for this mode. This is described in more detail in **Section 29.2.1 "Extended Instruction Syntax"**.

#### 7.5.3 WRITE VERIFY

Depending on the application, good programming practice may dictate that the value written to the memory should be verified against the original value. This should be used in applications where excessive writes can stress bits near the specification limit.

## 7.5.4 UNEXPECTED TERMINATION OF WRITE OPERATION

If a write is terminated by an unplanned event, such as loss of power or an unexpected Reset, the memory location just programmed should be verified and reprogrammed <u>if needed</u>. If the write operation is interrupted by a MCLR Reset, or a WDT time-out Reset during normal operation, the user can check the WRERR bit and rewrite the location(s) as needed.

#### 7.6 Flash Program Operation During Code Protection

See Section 28.6 "Program Verification and Code Protection" for details on code protection of Flash program memory.

#### TABLE 7-2: REGISTERS ASSOCIATED WITH PROGRAM FLASH MEMORY

| Name    | Bit 7                                                             | Bit 6        | Bit 5  | Bit 4                                                   | Bit 3 | Bit 2  | Bit 1  | Bit 0 |  |

|---------|-------------------------------------------------------------------|--------------|--------|---------------------------------------------------------|-------|--------|--------|-------|--|

| TBLPTRU | —                                                                 | —            | bit 21 | Program Memory Table Pointer Upper Byte (TBLPTR<20:16>) |       |        |        |       |  |

| TBPLTRH | Program Memory Table Pointer High Byte (TBLPTR<15:8>)             |              |        |                                                         |       |        |        |       |  |

| TBLPTRL | Program Memory Table Pointer Low Byte (TBLPTR<7:0>)               |              |        |                                                         |       |        |        |       |  |

| TABLAT  | Program Me                                                        | mory Table L | atch   |                                                         |       |        |        |       |  |

| INTCON  | GIE/GIEH                                                          | PEIE/GIEL    | TMR0IE | INT0IE                                                  | RBIE  | TMR0IF | INT0IF | RBIF  |  |

| EECON2  | ECON2 Program Memory Control Register 2 (not a physical register) |              |        |                                                         |       |        |        |       |  |

| EECON1  | _                                                                 | _            | WPROG  | FREE                                                    | WRERR | WREN   | WR     | _     |  |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used during Flash program memory access.

| REGISTER                     | 9-6: PIR3:    | PERIPHERA                      |                  | PT REQUEST          | (FLAG) REC       | SISTER 3 (AC    | CESS FA4h |

|------------------------------|---------------|--------------------------------|------------------|---------------------|------------------|-----------------|-----------|

| R/W-0                        | R/W-0         | R-0                            | R/W-0            | R/W-0               | R/W-0            | R/W-0           | R/W-0     |

| SSP2IF                       | BCL2IF        | RC2IF                          | TX2IF            | TMR4IF              | CTMUIF           | TMR3GIF         | RTCCIF    |

| bit 7                        |               |                                |                  |                     |                  |                 | bit (     |

| Lowende                      |               |                                |                  |                     |                  |                 |           |

| <b>Legend:</b><br>R = Readab | le hit        | W = Writable                   | hit              | II – I Inimplen     | nented bit, read | 1 as 'O'        |           |

| -n = Value a                 |               | '1' = Bit is set               |                  | '0' = Bit is cle    |                  | x = Bit is unkn | 0.000     |

|                              |               |                                | •                |                     | areu             |                 | OWIT      |

| bit 7                        | SSP2IF: Mas   | ter Synchrono                  | us Serial Port 2 | 2 Interrupt Flag    | bit              |                 |           |

|                              |               |                                |                  | te (must be clea    |                  | e)              |           |

|                              | 0 = Waiting t | o transmit/rece                | ive              |                     |                  |                 |           |

| bit 6                        | BCL2IF: Bus   | Collision Inter                | rupt Flag bit (N | ISSP2 module)       |                  |                 |           |

|                              |               |                                | ,                | ared in software    | )                |                 |           |

|                              |               | collision occurre              |                  |                     |                  |                 |           |

| bit 5                        |               | ART2 Receive                   |                  |                     |                  |                 |           |

|                              |               | SAR12 receive                  |                  | G2, is full (cleare | ed when RCRE     | G2 is read)     |           |

| bit 4                        |               | ART2 Transmit                  |                  |                     |                  |                 |           |

|                              |               |                                |                  | G2, is empty (cl    | eared when TX    | REG2 is writter | ר)        |

|                              |               | SART2 transmit                 |                  |                     |                  |                 |           |

| bit 3                        | TMR4IF: TM    | R4 to PR4 Mat                  | ch Interrupt Fla | ag bit              |                  |                 |           |

|                              |               |                                |                  | t be cleared in s   | software)        |                 |           |

|                              |               | 4 to PR4 match                 |                  |                     |                  |                 |           |

| bit 2                        |               | -                              |                  | Interrupt Flag b    |                  |                 |           |

|                              |               | event has occ<br>event has not | · ·              | e cleared in soft   | ware)            |                 |           |

| bit 1                        |               | mer3 Gate Eve                  |                  | aq bit              |                  |                 |           |

|                              |               |                                | •                | be cleared in s     | oftware)         |                 |           |

|                              | 0 = No Time   | r3 gate event c                | ompleted         |                     | ·                |                 |           |

| bit 0                        | RTCCIF: RT    | CC Interrupt Fla               | ag bit           |                     |                  |                 |           |

|                              |               |                                |                  | cleared in softw    | are)             |                 |           |

|                              | 0 = No RTCC   | c interrupt occu               | rred             |                     |                  |                 |           |

|                              |               |                                |                  |                     |                  |                 |           |

#### REGISTER 9-15: IPR2: PERIPHERAL INTERRUPT PRIORITY REGISTER 2 (ACCESS FA2h)

| R/W-1        | R/W-1                        | R/W-1               | R/W-1            | R/W-1             | R/W-1           | R/W-1           | R/W-1  |

|--------------|------------------------------|---------------------|------------------|-------------------|-----------------|-----------------|--------|

| OSCFIP       | CM2IP                        | CM1IP               | USBIP            | BCL1IP            | HLVDIP          | TMR3IP          | CCP2IP |

| bit 7        |                              |                     | ·                |                   |                 | •               | bit C  |

|              |                              |                     |                  |                   |                 |                 |        |

| Legend:      |                              |                     |                  |                   |                 |                 |        |

| R = Readab   | le bit                       | W = Writable        | bit              | U = Unimplem      | ented bit, read | l as '0'        |        |

| -n = Value a | t POR                        | '1' = Bit is set    |                  | '0' = Bit is clea | ared            | x = Bit is unkn | iown   |

|              |                              |                     |                  |                   |                 |                 |        |

| bit 7        |                              | scillator Fail Inte | rrupt Priority b | it                |                 |                 |        |

|              | 1 = High pri<br>0 = Low pri  |                     |                  |                   |                 |                 |        |

| bit 6        | CM2IP: Cor                   | nparator 2 Interr   | upt Priority bit |                   |                 |                 |        |

|              | 1 = High pr                  | iority              |                  |                   |                 |                 |        |

|              | 0 = Low pri                  | ority               |                  |                   |                 |                 |        |

| bit 5        | C12IP: Com                   | parator 1 Interru   | pt Priority bit  |                   |                 |                 |        |

|              | 1 = High prices              |                     |                  |                   |                 |                 |        |

| L:1 1        | 0 = Low prid                 | ,                   |                  |                   |                 |                 |        |

| bit 4        | 1 = High pri                 | B Interrupt Priori  | ly bit           |                   |                 |                 |        |

|              | 1 = High phi<br>0 = Low prie |                     |                  |                   |                 |                 |        |

| bit 3        |                              | is Collision Interi | upt Priority bit | (MSSP1 modul      | e)              |                 |        |

|              | 1 = High pri                 |                     |                  | (                 | - )             |                 |        |

|              | 0 = Low pri                  | •                   |                  |                   |                 |                 |        |

| bit 2        | HLVDIP: Hig                  | gh/Low-Voltage      | Detect Interrup  | ot Priority bit   |                 |                 |        |

|              | 1 = High pr                  |                     |                  |                   |                 |                 |        |

|              | 0 = Low pri                  | •                   |                  |                   |                 |                 |        |

| bit 1        |                              | /IR3 Overflow In    | terrupt Priority | bit               |                 |                 |        |

|              | 1 = High pri<br>0 = Low pri  |                     |                  |                   |                 |                 |        |

| bit 0        | ·                            | CP2 Interrupt P     | riority bit      |                   |                 |                 |        |

|              | 1 = High prior               | •                   | nonty bit        |                   |                 |                 |        |

|              | 0 = Low prie                 | •                   |                  |                   |                 |                 |        |

### 16.0 TIMER4/6/8 MODULE

The Timer4/6/8 timer modules have the following features:

- Eight-bit Timer register (TMRx)

- Eight-bit Period register (PRx)

- · Readable and writable (all registers)

- Software programmable prescaler (1:1, 1:4, 1:16)

- Software programmable postscaler (1:1 to 1:16)

- Interrupt on TMRx match of PRx

| Note: | Throughout this section, generic references      |

|-------|--------------------------------------------------|

|       | are used for register and bit names that are the |

|       | same - except for an 'x' variable that indicates |

|       | the item's association with the Timer4, Timer6   |

|       | or Timer8 module. For example, the control       |

|       | register is named TxCON and refers to            |

|       | T4CON, T6CON and T8CON.                          |

The Timer4/6/8 modules have a control register shown in Register 16-1. Timer4/6/8 can be shut off by clearing control bit, TMRxON (TxCON<2>), to minimize power consumption. The prescaler and postscaler selection of Timer4/6/8 are also controlled by this register. Figure 16-1 is a simplified block diagram of the Timer4/6/8 modules.

#### 16.1 Timer4/6/8 Operation

Timer4/6/8 can be used as the PWM time base for the PWM mode of the ECCP modules. The TMRx registers are readable and writable, and are cleared on any device Reset. The input clock (Fosc/4) has a prescale option of 1:1, 1:4 or 1:16, selected by control bits, TxCKPS<1:0> (TxCON<1:0>). The match output of TMRx goes through a four-bit postscaler (that gives a

1:1 to 1:16 inclusive scaling) to generate a TMRx interrupt, latched in the flag bit, TMRxIF. Table 16-1 gives each module's flag bit.

TABLE 16-1: TIMER4/6/8 FLAG BITS

| Timer Module | Flag Bit |

|--------------|----------|

| 4            | PIR3<3>  |

| 6            | PIR5<3>  |

| 8            | PIR5<4>  |

The interrupt can be enabled or disabled by setting or clearing the Timerx Interrupt Enable bit (TMRxIE), shown in Table 16-2.

#### TABLE 16-2: TIMER4/6/8 INTERRUPT ENABLE BITS

| Timer Module | Flag Bit |

|--------------|----------|

| 4            | PIE3<3>  |

| 6            | PIE5<3>  |

| 8            | PIE5<4>  |

The prescaler and postscaler counters are cleared when any of the following occurs:

- A write to the TMRx register

- · A write to the TxCON register

- Any device Reset (Power-on Reset (POR), MCLR Reset, Watchdog Timer Reset (WDTR) or Brown-out Reset (BOR))

A TMRx is not cleared when a TxCON is written.

Note: The CCP and ECCP modules use Timers 1 through 8 for some modes. The assignment of a particular timer to a CCP/ECCP module is determined by the Timer to CCP enable bits in the CCPTMRSx registers. For more details, see Register 19-2, Register 18-2 and Register 18-3.

#### 17.1.2 RTCVALH AND RTCVALL REGISTER MAPPINGS

### REGISTER 17-6: RESERVED REGISTER

| U-0             | U-0                             | U-0 | U-0 | U-0              | U-0              | U-0             | U-0   |

|-----------------|---------------------------------|-----|-----|------------------|------------------|-----------------|-------|

|                 | —                               | —   | —   | —                | —                | —               |       |

| bit 7           |                                 |     |     |                  |                  |                 | bit 0 |

|                 |                                 |     |     |                  |                  |                 |       |

| Legend:         |                                 |     |     |                  |                  |                 |       |

| R = Readable b  | dable bit W = Writable bit      |     |     | U = Unimpler     | nented bit, read | as '0'          |       |

| -n = Value at P | = Value at POR '1' = Bit is set |     |     | '0' = Bit is cle | ared             | x = Bit is unkn | own   |

bit 7-0 Unimplemented: Read as '0'

#### REGISTER 17-7: YEAR: YEAR VALUE REGISTER<sup>(1)</sup>

| R/W-x  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| YRTEN3 | YRTEN2 | YRTEN1 | YRTEN0 | YRONE3 | YRONE2 | YRONE1 | YRONE0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 7-4YRTEN<3:0>: Binary Coded Decimal Value of Year's Tens Digit bits<br/>Contains a value from 0 to 9.bit 3-0YRONE<3:0>: Binary Coded Decimal Value of Year's Ones Digit bits

Contains a value from 0 to 9.

**Note 1:** A write to the YEAR register is only allowed when RTCWREN = 1.

#### REGISTER 17-8: MONTH: MONTH VALUE REGISTER<sup>(1)</sup>

| U-0   | U-0 | U-0 | R/W-x   | R/W-x   | R/W-x   | R/W-x   | R/W-x   |

|-------|-----|-----|---------|---------|---------|---------|---------|

| —     | —   | —   | MTHTEN0 | MTHONE3 | MTHONE2 | MTHONE1 | MTHONE0 |

| bit 7 |     |     |         |         |         |         | bit 0   |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 7-5 Unimplemented: Read as '0'

bit 4 **MTHTEN0:** Binary Coded Decimal Value of Month's Tens Digit bit Contains a value of 0 or 1.

bit 3-0 MTHONE<3:0>: Binary Coded Decimal Value of Month's Ones Digit bits Contains a value from 0 to 9.

**Note 1:** A write to this register is only allowed when RTCWREN = 1.

### 19.0 ENHANCED CAPTURE/COMPARE/PWM (ECCP) MODULE

PIC18F47J53 family devices have three Enhanced Capture/Compare/PWM (ECCP) modules: ECCP1, ECCP2 and ECCP3. These modules contain a 16-bit register, which can operate as a 16-bit Capture register, a 16-bit Compare register or a PWM Master/Slave Duty Cycle register. These ECCP modules are upwardly compatible with CCP.

Note: Throughout this section, generic references are used for register and bit names that are the same – except for an 'x' variable that indicates the item's association with the ECCP1, ECCP2 or ECCP3 module. For example, the control register is named CCPxCON and refers to CCP1CON, CCP2CON and CCP3CON. The ECCP modules are implemented as standard CCP modules with enhanced PWM capabilities. These include:

- · Provision for two or four output channels

- · Output Steering modes

- · Programmable polarity

- Programmable dead-band control

- Automatic shutdown and restart

The enhanced features are discussed in detail in Section 19.4 "PWM (Enhanced Mode)".

| TABLE 19-3: | EXAMPLE PIN ASSIGNMENTS FOR VARIOUS PWM ENHANCED MODES |

|-------------|--------------------------------------------------------|

| TABLE 19-3: |                                                        |

|             |                                                        |

| ECCP Mode            | PxM<1:0> | PxA                | PxB                | PxC                | PxD                |

|----------------------|----------|--------------------|--------------------|--------------------|--------------------|

| Single               | 00       | Yes <sup>(1)</sup> | Yes <sup>(1)</sup> | Yes <sup>(1)</sup> | Yes <sup>(1)</sup> |

| Half-Bridge          | 10       | Yes                | Yes                | No                 | No                 |

| Full-Bridge, Forward | 01       | Yes                | Yes                | Yes                | Yes                |

| Full-Bridge, Reverse | 11       | Yes                | Yes                | Yes                | Yes                |

Note 1: Outputs are enabled by pulse steering in Single mode (see Register 19-6).

#### PWM (ENHANCED MODE) OUTPUT RELATIONSHIPS **FIGURE 19-4:** (ACTIVE-HIGH STATE) EXAMPLE

| le Output)<br>f-Bridge)                 | PxA Modulated<br>PxA Modulated<br>PxB Modulated<br>PxA Active | <br><br>                                                      | uDelay <sup>(1)</sup>                                                         | Period<br>Delay <sup>(1)</sup> |              |

|-----------------------------------------|---------------------------------------------------------------|---------------------------------------------------------------|-------------------------------------------------------------------------------|--------------------------------|--------------|

| f-Bridge)                               | PxA Modulated<br>PxB Modulated                                |                                                               | · · · · · · · · · · · · · · · · · · ·                                         | Delaÿ <sup>(1)</sup>           |              |

|                                         | PxB Modulated                                                 | <br>                                                          | · · · · · · · · · · · · · · · · · · ·                                         |                                |              |

|                                         |                                                               |                                                               | 1<br>1<br>1                                                                   |                                | i            |

|                                         | PxA Active                                                    |                                                               |                                                                               |                                |              |

|                                         |                                                               |                                                               | <br> <br>                                                                     | <br>                           | <br>!<br>!   |

| (Full-Bridge,<br><sup>01</sup> Forward) | PxB Inactive                                                  |                                                               | 1<br>1<br>1                                                                   | 1<br>1<br>1                    | ¦            |

|                                         | PxC Inactive                                                  |                                                               | ,<br>,<br>,<br>,                                                              |                                |              |

|                                         | PxD Modulated                                                 |                                                               | <br>                                                                          |                                |              |

|                                         | PxA Inactive                                                  |                                                               | 1<br>1<br>1                                                                   | 1<br>1<br>1                    |              |

| 11 (Full-Bridge,<br>Reverse)            | PxB Modulated                                                 | <u> </u>                                                      | '<br>                                                                         |                                |              |

|                                         | PxC Active                                                    |                                                               | <del>.</del>                                                                  |                                | <br><br>!    |

|                                         | PxD Inactive                                                  | <u> </u>                                                      | I                                                                             |                                | 1<br>1<br>1  |

|                                         |                                                               | PxA Inactive<br>Bridge, PxB Modulated<br>verse)<br>PxC Active | PxA Inactive<br>Bridge, PxB Modulated<br>verse)<br>PxC Active<br>PxD Inactive | PxA Inactive                   | PxA Inactive |

Period = 4 \* Tosc \* (PR2 + 1) \* (TMR2 Prescale Value)

Pulse Width = Tosc \* (CCPRxL<7:0>:CCPxCON<5:4>) \* (TMR2 Prescale Value)

Delay = 4 \* Tosc \* (ECCPxDEL<6:0>)

Note 1: Dead-band delay is programmed using the ECCPxDEL register (see Section 19.4.6 "Programmable Dead-Band Delay Mode").

#### 19.4.5 AUTO-RESTART MODE

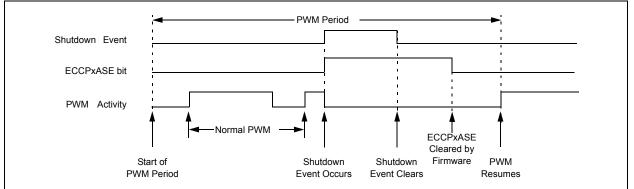

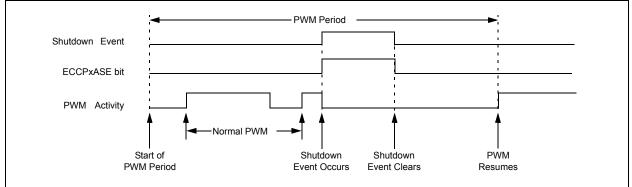

The Enhanced PWM can be configured to automatically restart the PWM signal once the auto-shutdown condition has been removed. Auto-restart is enabled by setting the PxRSEN bit (ECCPxDEL<7>).

If auto-restart is enabled, the ECCPxASE bit will remain set as long as the auto-shutdown condition is active. When the auto-shutdown condition is removed, the ECCPxASE bit will be cleared via hardware and normal operation will resume. The module will wait until the next PWM period begins, however, before re-enabling the output pin. This behavior allows the auto-shutdown with auto-restart features to be used in applications based on the current mode of PWM control.

| Bit 7<br>/GIEH<br>IPIF <sup>(2)</sup><br>PIE <sup>(2)</sup><br>IPIP <sup>(2)</sup> | Bit 6<br>PEIE/GIEL<br>ADIF<br>ADIE                                   | Bit 5<br>TMR0IE<br>RC1IF                                                                      | Bit 4<br>INTOIE<br>TX1IF                                                                                                                      | Bit 3<br>RBIE                                                                                                                                                        | Bit 2<br>TMR0IF                                                                                                                                                                                                       | Bit 1<br>INT0IF                                                                                                                                                                                                                                                   | Bit 0<br>RBIF                                                                                                                                                                                                                                                                                                                         |

|------------------------------------------------------------------------------------|----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIF <sup>(2)</sup>                                                                 | ADIF                                                                 | RC1IF                                                                                         |                                                                                                                                               |                                                                                                                                                                      | -                                                                                                                                                                                                                     | INTOIF                                                                                                                                                                                                                                                            | RBIF                                                                                                                                                                                                                                                                                                                                  |

| PIE <sup>(2)</sup>                                                                 |                                                                      | -                                                                                             | TX1IF                                                                                                                                         |                                                                                                                                                                      |                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                       |

|                                                                                    | ADIE                                                                 |                                                                                               |                                                                                                                                               | SSP1IF                                                                                                                                                               | CCP1IF                                                                                                                                                                                                                | TMR2IF                                                                                                                                                                                                                                                            | TMR1IF                                                                                                                                                                                                                                                                                                                                |