#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 48MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART, USB                              |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 22                                                                          |

| Program Memory Size        | 64KB (32K x 16)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 3.8K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 2.75V                                                                  |

| Data Converters            | A/D 10x10b/12b                                                              |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Through Hole                                                                |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                     |

| Supplier Device Package    | 28-SPDIP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf26j53-i-sp |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

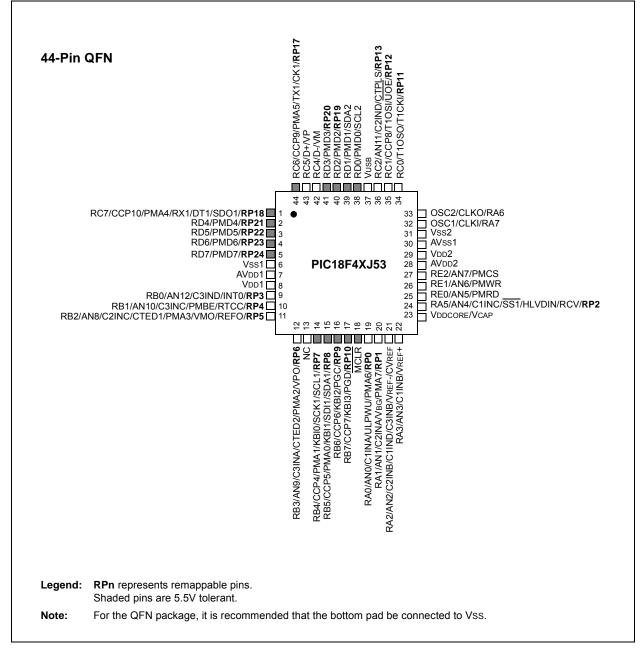

# Pin Diagrams (Continued)

# TABLE 1-1: DEVICE FEATURES FOR THE PIC18F2XJ53 (28-PIN DEVICES)

| Features                             | PIC18F26J53                                                                      | PIC18F27J53       |  |

|--------------------------------------|----------------------------------------------------------------------------------|-------------------|--|

| Operating Frequency                  | DC – 48 MHz                                                                      | DC – 48 MHz       |  |

| Program Memory (Kbytes)              | 64                                                                               | 128               |  |

| Program Memory (Instructions)        | 32,768                                                                           | 65,536            |  |

| Data Memory (Kbytes)                 | 3.8                                                                              | 3.8               |  |

| Interrupt Sources                    | 3                                                                                | 0                 |  |

| I/O Ports                            | Ports A, B, C                                                                    |                   |  |

| Timers                               | 8                                                                                |                   |  |

| Enhanced Capture/Compare/PWM Modules | 3 ECCP and 7 CCP                                                                 |                   |  |

| Serial Communications                | MSSP (2), Enhance                                                                | ed USART (2), USB |  |

| Parallel Communications (PMP/PSP)    | N                                                                                | lo                |  |

| 10/12-Bit Analog-to-Digital Module   | 10 Input                                                                         | Channels          |  |

| Resets (and Delays)                  | POR, BOR, RESET Instruction, Stack Full, Stack Underflow, MCLR, V<br>(PWRT, OST) |                   |  |

| Instruction Set                      | et 75 Instructions, 83 with Extended Instruction Set Enabled                     |                   |  |

| Packages                             | 28-Pin QFN, SOIC, SSOP and SPDIP (300 mil)                                       |                   |  |

# TABLE 1-2:DEVICE FEATURES FOR THE PIC18F4XJ53 (44-PIN DEVICES)

| Features                             | PIC18F46J53                                                                      | PIC18F47J53       |  |

|--------------------------------------|----------------------------------------------------------------------------------|-------------------|--|

| Operating Frequency                  | DC – 48 MHz                                                                      | DC – 48 MHz       |  |

| Program Memory (Kbytes)              | 64                                                                               | 128               |  |

| Program Memory (Instructions)        | 32,768                                                                           | 65,536            |  |

| Data Memory (Kbytes)                 | 3.8                                                                              | 3.8               |  |

| Interrupt Sources                    | 30                                                                               |                   |  |

| I/O Ports                            | Ports A, B, C, D, E                                                              |                   |  |

| Timers                               | 8                                                                                |                   |  |

| Enhanced Capture/Compare/PWM Modules | 3 ECCP a                                                                         | ind 7 CCP         |  |

| Serial Communications                | MSSP (2), Enhance                                                                | ed USART (2), USB |  |

| Parallel Communications (PMP/PSP)    | Yes                                                                              |                   |  |

| 10/12-Bit Analog-to-Digital Module   | 13 Input                                                                         | Channels          |  |

| Resets (and Delays)                  | POR, BOR, RESET Instruction, Stack Full, Stack Underflow, MCLR, \<br>(PWRT, OST) |                   |  |

| Instruction Set                      | 75 Instructions, 83 with Extended Instruction Set Enabled                        |                   |  |

| Packages                             | 44-Pin QFN and TQFP                                                              |                   |  |

# 2.2 Power Supply Pins

## 2.2.1 DECOUPLING CAPACITORS

The use of decoupling capacitors on every pair of power supply pins, such as VDD, VSS, AVDD and AVSS, is required.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: A 0.1  $\mu$ F (100 nF), 10-20V capacitor is recommended. The capacitor should be a low-ESR device, with a resonance frequency in the range of 200 MHz and higher. Ceramic capacitors are recommended.

- Placement on the printed circuit board: The decoupling capacitors should be placed as close to the pins as possible. It is recommended to place the capacitors on the same side of the board as the device. If space is constricted, the capacitor can be placed on another layer on the PCB using a via; however, ensure that the trace length from the pin to the capacitor is no greater than 0.25 inch (6 mm).

- Handling high-frequency noise: If the board is experiencing high-frequency noise (upward of tens of MHz), add a second ceramic type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of 0.01  $\mu$ F to 0.001  $\mu$ F. Place this second capacitor next to each primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible (e.g., 0.1  $\mu$ F in parallel with 0.001  $\mu$ F).

- Maximizing performance: On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum, thereby reducing PCB trace inductance.

### 2.2.2 TANK CAPACITORS

On boards with power traces running longer than six inches in length, it is suggested to use a tank capacitor for integrated circuits, including microcontrollers, to supply a local power source. The value of the tank capacitor should be determined based on the trace resistance that connects the power supply source to the device, and the maximum current drawn by the device in the application. In other words, select the tank capacitor so that it meets the acceptable voltage sag at the device. Typical values range from 4.7  $\mu F$  to 47  $\mu F$ .

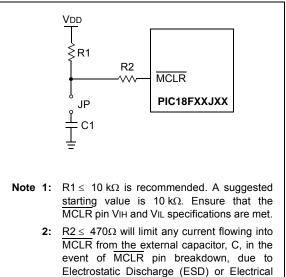

# 2.3 Master Clear (MCLR) Pin

The MCLR pin provides two specific device functions: Device Reset, and Device Programming and Debugging. If programming and debugging are not required in the end application, a direct connection to VDD may be all that is required. The addition of other components, to help increase the application's resistance to spurious Resets from voltage sags, may be beneficial. A typical configuration is shown in Figure 2-1. Other circuit designs may be implemented, depending on the application's requirements.

During programming and debugging, the resistance and capacitance that can be added to the pin must be considered. Device programmers and debuggers drive the  $\overline{\text{MCLR}}$  pin. Consequently, specific voltage levels (VIH and VIL) and fast signal transitions must not be adversely affected. Therefore, specific values of R1 and C1 will need to be adjusted based on the application and PCB requirements. For example, it is recommended that the capacitor, C1, be isolated from the  $\overline{\text{MCLR}}$  pin during programming and debugging operations by using a jumper (Figure 2-2). The jumper is replaced for normal run-time operations.

Any components associated with the  $\overline{\text{MCLR}}$  pin should be placed within 0.25 inch (6 mm) of the pin.

## FIGURE 2-2: EXAMPLE OF MCLR PIN CONNECTIONS

Overstress (EOS). Ensure that the MCLR pin

VIH and VIL specifications are met.

| REGISTER 3-1: | OSCTUNE: OSCILLATOR TUNING REGISTER (ACCESS F9Bh) |

|---------------|---------------------------------------------------|

|               |                                                   |

| R/W-0           | R/W-0                                                                                                                                                                                                                                                                                                                       | R/W-0                             | R/W-0 | R/W-0             | R/W-0            | R/W-0           | R/W-0 |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|-------|-------------------|------------------|-----------------|-------|

| INTSRC          | PLLEN <sup>(1)</sup>                                                                                                                                                                                                                                                                                                        | TUN5                              | TUN4  | TUN3              | TUN2             | TUN1            | TUN0  |

| bit 7           |                                                                                                                                                                                                                                                                                                                             |                                   |       |                   |                  |                 | bit ( |

| Legend:         |                                                                                                                                                                                                                                                                                                                             |                                   |       |                   |                  |                 |       |

| R = Readable b  | oit                                                                                                                                                                                                                                                                                                                         | W = Writable                      | bit   | U = Unimplen      | nented bit, read | l as '0'        |       |

| -n = Value at P | OR                                                                                                                                                                                                                                                                                                                          | '1' = Bit is set                  |       | '0' = Bit is clea | ared             | x = Bit is unkr | nown  |

| bit 7<br>bit 6  | <ul> <li>INTSRC: Internal Oscillator Low-Frequency Source Select bit</li> <li>1 = 31.25 kHz device clock derived from 8 MHz INTOSC source (divide-by-256 enabled)</li> <li>0 = 31 kHz device clock derived directly from INTRC internal oscillator</li> <li>PLLEN: Frequency Multiplier Enable bit<sup>(1)</sup></li> </ul> |                                   |       |                   |                  |                 |       |

|                 | 1 = 96 MHz P                                                                                                                                                                                                                                                                                                                | PLL is enabled<br>PLL is disabled |       |                   |                  |                 |       |

| bit 5-0         |                                                                                                                                                                                                                                                                                                                             | requency Tunir<br>iximum frequer  | •     |                   |                  |                 |       |

**Note 1:** When the CFGPLLEN Configuration bit is used to enable the PLL, clearing OSCTUNE<6> will not disable the PLL.

# 3.3 Oscillator Settings for USB

When the PIC18F47J53 family devices are used for USB connectivity, a 6 MHz or 48 MHz clock must be provided to the USB module for operation in either Low-Speed or Full-Speed modes, respectively. This may require some forethought in selecting an oscillator frequency and programming the device.

The full range of possible oscillator configurations compatible with USB operation is shown in Table 3-5.

# 3.3.1 LOW-SPEED OPERATION

The USB clock for Low-Speed mode is derived from the primary oscillator or from the 96 MHz PLL. In order to operate the USB module in Low-Speed mode, a 6 MHz clock must be provided to the USB module.

See Table 3-4 and Table 3-5 for possible combinations which can be used for low-speed USB operation.

| System Clock | CPDIV<1:0> | Microcontroller Clock | LS48MHZ | USB Clock    |  |  |  |

|--------------|------------|-----------------------|---------|--------------|--|--|--|

| 48           | 11         | 48 MHz                | 1       | 48/8 = 6 MHz |  |  |  |

| 48           | 10         | 48/2 = 24 MHz         | 1       | 48/8 = 6 MHz |  |  |  |

| 48           | 01         | 48/3 = 16 MHz         | 1       | 48/8 = 6 MHz |  |  |  |

| 48           | 00         | 48/6 = 8 MHz          | 1       | 48/8 = 6 MHz |  |  |  |

| 24           | 11         | 24 MHz                | 0       | 24/4 = 6 MHz |  |  |  |

| 24           | 10         | 24/2 = 12 MHz         | 0       | 24/4 = 6 MHz |  |  |  |

| 24           | 01         | 24/3 = 8 MHz          | 0       | 24/4 = 6 MHz |  |  |  |

| 24           | 00         | 24/6 = 4 MHz          | 0       | 24/4 = 6 MHz |  |  |  |

| TABLE 3-4: | CLOCK FOR LOW-SPEED USB |

|------------|-------------------------|

|------------|-------------------------|

# 3.7 Effects of Power-Managed Modes on Various Clock Sources

When the PRI\_IDLE mode is selected, the designated primary oscillator continues to run without interruption. For all other power-managed modes, the oscillator using the OSC1 pin is disabled. Unless the USB module is enabled, the OSC1 pin (and OSC2 pin if used by the oscillator) will stop oscillating.

In secondary clock modes (SEC\_RUN and SEC\_I-DLE), the Timer1 oscillator is operating and providing the device clock. The Timer1 oscillator may also run in all power-managed modes if required to clock Timer1 or Timer3.

In internal oscillator modes (RC\_RUN and RC\_IDLE), the internal oscillator block provides the device clock source. The 31 kHz INTRC output can be used directly to provide the clock and may be enabled to support various special features regardless of the power-managed mode (see Section 28.2 "Watchdog Timer (WDT)", Section 28.4 "Two-Speed Start-up" and Section 28.5 "Fail-Safe Clock Monitor" for more information on WDT, FSCM and Two-Speed Start-up). The INTOSC output at 8 MHz may be used directly to clock the device or may be divided down by the postscaler. The INTOSC output is disabled if the clock is provided directly from the INTRC output.

If Sleep mode is selected, all clock sources which are no longer required are stopped. Since all the transistor switching currents have been stopped, Sleep mode achieves the lowest current consumption of the device (only leakage currents) outside of Deep Sleep. Sleep mode should not be invoked while the USB module is enabled and operating in Full-Power mode. Before Sleep mode is selected, the USB module should be put in the suspend state. This is accomplished by setting the SUSPND bit in the UCON register.

Enabling any on-chip feature that will operate during Sleep mode increases the current consumed during Sleep mode. The INTRC is required to support WDT operation. The Timer1 oscillator may be operating to support an RTC. Other features may be operating that do not require a device clock source (i.e., MSSP slave, PMP, INTx pins, etc.). Peripherals that may add significant current consumption are listed in Section 31.2 "DC Characteristics: Power-Down and Supply Current PIC18F47J53 Family (Industrial)".

# 3.8 Power-up Delays

Power-up delays are controlled by two timers so that no external Reset circuitry is required for most applications. The delays ensure that the device is kept in Reset until the device power supply is stable under normal circumstances and the primary clock is operating and stable. For additional information on power-up delays, see **Section 5.6 "Power-up Timer (PWRT)"**.

The first timer is the Power-up Timer (PWRT), which provides a fixed delay on power-up (parameter 33, Table 31-14).

The second timer is the Oscillator Start-up Timer (OST), intended to keep the chip in Reset until the crystal oscillator is stable (HS mode). The OST does this by counting 1024 oscillator cycles before allowing the oscillator to clock the device.

There is a delay of interval, TCSD (parameter 38, Table 31-14), following POR, while the controller becomes ready to execute instructions. This delay runs concurrently with any other delays. This may be the only delay that occurs when any of the internal oscillator or EC modes are used as the primary clock source.

| TABLE 5-2:             | INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED) |             |                                                                |                                                                            |                                 |  |  |  |

|------------------------|---------------------------------------------------------|-------------|----------------------------------------------------------------|----------------------------------------------------------------------------|---------------------------------|--|--|--|

| Register               | Applicable Devices                                      |             | Power-on Reset,<br>Brown-out Reset,<br>Wake From Deep<br>Sleep | MCLR Resets<br>WDT Reset<br>RESET Instruction<br>Stack Resets<br>CM Resets | Wake-up via WDT<br>or Interrupt |  |  |  |

| PMCONL                 | PIC18F2XJ53                                             | PIC18F4XJ53 | 000- 0000                                                      | 000- 0000                                                                  | uuu- uuuu                       |  |  |  |

| PMMODEH                | PIC18F2XJ53                                             | PIC18F4XJ53 | 0000 0000                                                      | 0000 0000                                                                  | uuuu uuuu                       |  |  |  |

| PMMODEL                | PIC18F2XJ53                                             | PIC18F4XJ53 | 0000 0000                                                      | 0000 0000                                                                  | uuuu uuuu                       |  |  |  |

| PMDOUT2H               | PIC18F2XJ53                                             | PIC18F4XJ53 | 0000 0000                                                      | 0000 0000                                                                  | uuuu uuuu                       |  |  |  |

| PMDOUT2L               | PIC18F2XJ53                                             | PIC18F4XJ53 | 0000 0000                                                      | 0000 0000                                                                  | uuuu uuuu                       |  |  |  |

| PMDIN2H                | PIC18F2XJ53                                             | PIC18F4XJ53 | 0000 0000                                                      | 0000 0000                                                                  | uuuu uuuu                       |  |  |  |

| PMDIN2L                | PIC18F2XJ53                                             | PIC18F4XJ53 | 0000 0000                                                      | 0000 0000                                                                  | uuuu uuuu                       |  |  |  |

| PMEH                   | PIC18F2XJ53                                             | PIC18F4XJ53 | 0000 0000                                                      | 0000 0000                                                                  | uuuu uuuu                       |  |  |  |

| PMEL                   | PIC18F2XJ53                                             | PIC18F4XJ53 | 0000 0000                                                      | 0000 0000                                                                  | uuuu uuuu                       |  |  |  |

| PMSTATH                | PIC18F2XJ53                                             | PIC18F4XJ53 | 00 0000                                                        | 00 0000                                                                    | uu uuuu                         |  |  |  |

| PMSTATL                | PIC18F2XJ53                                             | PIC18F4XJ53 | 10 1111                                                        | 10 1111                                                                    | uu uuuu                         |  |  |  |

| CVRCON                 | PIC18F2XJ53                                             | PIC18F4XJ53 | 0000 0000                                                      | 0000 0000                                                                  | uuuu uuuu                       |  |  |  |

| CCPTMRS0               | PIC18F2XJ53                                             | PIC18F4XJ53 | 0000 0000                                                      | 0000 0000                                                                  | uuuu uuuu                       |  |  |  |

| CCPTMRS1               | PIC18F2XJ53                                             | PIC18F4XJ53 | 0000 0000                                                      | 0000 0000                                                                  | uuuu uuuu                       |  |  |  |

| CCPTMRS2               | PIC18F2XJ53                                             | PIC18F4XJ53 | 0000 0000                                                      | 0000 0000                                                                  | uuuu uuuu                       |  |  |  |

| DSGPR1 <sup>(6)</sup>  | PIC18F2XJ53                                             | PIC18F4XJ53 | uuuu uuuu                                                      | uuuu uuuu                                                                  | uuuu uuuu                       |  |  |  |

| DSGPR0 <sup>(6)</sup>  | PIC18F2XJ53                                             | PIC18F4XJ53 | uuuu uuuu                                                      | uuuu uuuu                                                                  | uuuu uuuu                       |  |  |  |

| DSCONH <sup>(6)</sup>  | PIC18F2XJ53                                             | PIC18F4XJ53 | 000                                                            | 000                                                                        | uuu                             |  |  |  |

| DSCONL <sup>(6)</sup>  | PIC18F2XJ53                                             | PIC18F4XJ53 | 000                                                            | 000                                                                        | uuu                             |  |  |  |

| DSWAKEH <sup>(6)</sup> | PIC18F2XJ53                                             | PIC18F4XJ53 | d                                                              | 0                                                                          | u                               |  |  |  |

| DSWAKEL <sup>(6)</sup> | PIC18F2XJ53                                             | PIC18F4XJ53 | d-dd dd-d                                                      | 0-00 00-0                                                                  | u-uu uu-u                       |  |  |  |

| ANCON1                 | PIC18F2XJ53                                             | PIC18F4XJ53 | 00-0 0000                                                      | uu-u uuuu                                                                  | uu-u uuuu                       |  |  |  |

| ANCON0                 | PIC18F2XJ53                                             | PIC18F4XJ53 | 0000 0000                                                      | uuuu uuuu                                                                  | uuuu uuuu                       |  |  |  |

| ALRMCFG                | PIC18F2XJ53                                             | PIC18F4XJ53 | 0000 0000                                                      | uuuu uuuu                                                                  | uuuu uuuu                       |  |  |  |

| ALRMRPT                | PIC18F2XJ53                                             | PIC18F4XJ53 | 0000 0000                                                      | uuuu uuuu                                                                  | uuuu uuuu                       |  |  |  |

| ALRMVALH               | PIC18F2XJ53                                             | PIC18F4XJ53 | xxxx xxxx                                                      | uuuu uuuu                                                                  | uuuu uuuu                       |  |  |  |

| ALRMVALL               | PIC18F2XJ53                                             | PIC18F4XJ53 | xxxx xxxx                                                      | uuuu uuuu                                                                  | uuuu uuuu                       |  |  |  |

| ODCON1                 | PIC18F2XJ53                                             | PIC18F4XJ53 | 0000                                                           | uuuu                                                                       | uuuu                            |  |  |  |

| ODCON2                 | PIC18F2XJ53                                             | PIC18F4XJ53 | 00                                                             | uu                                                                         | uu                              |  |  |  |

| ODCON3                 | PIC18F2XJ53                                             | PIC18F4XJ53 | 00                                                             | uu                                                                         | uu                              |  |  |  |

| RTCCFG                 | PIC18F2XJ53                                             | PIC18F4XJ53 | 0-00 0000                                                      | u-uu uuuu                                                                  | u-uu uuuu                       |  |  |  |

| RTCCAL                 | PIC18F2XJ53                                             | PIC18F4XJ53 | 0000 0000                                                      | uuuu uuuu                                                                  | uuuu uuuu                       |  |  |  |

| TABLE 5-2: | INITIALIZATION CONDITIONS FOR ALL REGISTERS ( | CONTINUED) | ) |

|------------|-----------------------------------------------|------------|---|

|            |                                               |            |   |

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition.

**Note 1:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware stack.

- 2: When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

- 3: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

- **4:** See Table 5-1 for Reset value for specific condition.

- 5: Not implemented for PIC18F2XJ53 devices.

- 6: Not implemented for "LF" devices.

| R/W-0         | R/W-0                                                                                                   | R/W-0                                 | R/W-0          | R/W-0             | R/W-0            | R/W-0           | R/W-0   |  |  |  |

|---------------|---------------------------------------------------------------------------------------------------------|---------------------------------------|----------------|-------------------|------------------|-----------------|---------|--|--|--|

| CCP8OD        | CCP7OD                                                                                                  | CCP6OD                                | CCP5OD         | CCP4OD            | ECCP3OD          | ECCP2OD         | ECCP10D |  |  |  |

| bit 7         |                                                                                                         |                                       |                |                   |                  |                 | bit 0   |  |  |  |

|               |                                                                                                         |                                       |                |                   |                  |                 |         |  |  |  |

| Legend:       |                                                                                                         |                                       |                |                   |                  |                 |         |  |  |  |

| R = Readabl   |                                                                                                         | W = Writable                          |                | •                 | nented bit, read |                 |         |  |  |  |

| -n = Value at | POR                                                                                                     | '1' = Bit is set                      |                | '0' = Bit is clea | ared             | x = Bit is unkr | nown    |  |  |  |

| bit 7         | <b>ссряор</b> . со                                                                                      | CP8 Open-Drai                         | n Output Enabl | le hit            |                  |                 |         |  |  |  |

|               |                                                                                                         | ain capability is                     | •              |                   |                  |                 |         |  |  |  |

|               |                                                                                                         | ain capability is                     |                |                   |                  |                 |         |  |  |  |

| bit 6         | CCP7OD: CC                                                                                              | CP7 Open-Drai                         | n Output Enabl | le bit            |                  |                 |         |  |  |  |

|               | 1 = Open-dra                                                                                            | 1 = Open-drain capability is enabled  |                |                   |                  |                 |         |  |  |  |

|               | 0 = Open-drain capability is disabled                                                                   |                                       |                |                   |                  |                 |         |  |  |  |

| bit 5         | CCP6OD: CC                                                                                              | CP6 Open-Drai                         | n Output Enabl | le bit            |                  |                 |         |  |  |  |

|               | 1 = Open-drain capability is enabled                                                                    |                                       |                |                   |                  |                 |         |  |  |  |

|               | -                                                                                                       | ain capability is                     |                |                   |                  |                 |         |  |  |  |

| bit 4         |                                                                                                         | CP5 Open-Drai                         |                | le bit            |                  |                 |         |  |  |  |

|               | <ul> <li>1 = Open-drain capability is enabled</li> <li>0 = Open-drain capability is disabled</li> </ul> |                                       |                |                   |                  |                 |         |  |  |  |

| bit 3         | •                                                                                                       |                                       |                | le bit            |                  |                 |         |  |  |  |

|               | <b>CCP4OD:</b> CCP4 Open-Drain Output Enable bit<br>1 = Open-drain capability is enabled                |                                       |                |                   |                  |                 |         |  |  |  |

|               |                                                                                                         | 0 =  Open-drain capability is enabled |                |                   |                  |                 |         |  |  |  |

| bit 2         | ECCP3OD: E                                                                                              | ECCP3 Open-D                          | rain Output En | able bit          |                  |                 |         |  |  |  |

|               | 1 = Open-drain capability is enabled                                                                    |                                       |                |                   |                  |                 |         |  |  |  |

|               | 0 = Open-dra                                                                                            | ain capability is                     | disabled       |                   |                  |                 |         |  |  |  |

| bit 1         | ECCP2OD: E                                                                                              | ECCP2 Open-D                          | rain Output En | able bit          |                  |                 |         |  |  |  |

|               |                                                                                                         | ain capability is                     |                |                   |                  |                 |         |  |  |  |

|               | •                                                                                                       | ain capability is                     |                |                   |                  |                 |         |  |  |  |

| bit 0         |                                                                                                         | ECCP1 Open-D<br>ain capability is     |                | able bit          |                  |                 |         |  |  |  |

|               |                                                                                                         |                                       |                |                   |                  |                 |         |  |  |  |

Choosing the configuration requires the review of all PPSs and their pin assignments, especially those that will not be used in the application. In all cases, unused pin selectable peripherals should be disabled completely. Unused peripherals should have their inputs assigned to an unused RPn pin function. I/O pins with unused RPn functions should be configured with the null peripheral output.

The assignment of a peripheral to a particular pin does not automatically perform any other configuration of the pin's I/O circuitry. In theory, this means adding a pinselectable output to a pin may mean inadvertently driving an existing peripheral input when the output is driven. Users must be familiar with the behavior of other fixed peripherals that share a remappable pin and know when to enable or disable them. To be safe, fixed digital peripherals that share the same pin should be disabled when not in use.

Along these lines, configuring a remappable pin for a specific peripheral does not automatically turn that feature on. The peripheral must be specifically configured for operation and enabled, as if it were tied to a fixed pin. Where this happens in the application code (immediately following device Reset and peripheral configuration or inside the main application routine) depends on the peripheral and its use in the application.

A final consideration is that the PPS functions neither override analog inputs nor reconfigure pins with analog functions for digital I/O. If a pin is configured as an analog input on device Reset, it must be explicitly reconfigured as digital I/O when used with a PPS.

Example 10-7 provides a configuration for bidirectional communication with flow control using EUSART2. The following input and output functions are used:

- Input Function RX2

- Output Function TX2

#### EXAMPLE 10-7: CONFIGURING EUSART2 INPUT AND OUTPUT FUNCTIONS

| ;*****          | ******                                  |

|-----------------|-----------------------------------------|

| ; Unloc         | ck Registers                            |

|                 | *********                               |

| MOVLB           | 0x0E ; PPS registers in BANK 14         |

| BCF             | INTCON, GIE ; Disable interrupts        |

| MOVLW           | 0x55                                    |

| MOVWF           | EECON2, 0                               |

| MOVLW           | 0xAA                                    |

| MOVWF           | EECON2, 0                               |

| ; Turn          | off PPS Write Protect                   |

| BCF             | PPSCON, IOLOCK, BANKED                  |

| ; * * * * * *   | * * * * * * * * * * * * * * * * * * * * |

| ; Confi         | gure Input Functions                    |

|                 | Table 10-13)                            |

|                 | ****                                    |

| ;****           | * * * * * * * * * * * * * * * * * * * * |

| ; Ass           | sign RX2 To Pin RP0                     |

| ; * * * *       | * * * * * * * * * * * * * * * * * * * * |

| MOVLW           | 0x00                                    |

| MOVWF           | RPINR16, BANKED                         |

| ; * * * * * * * | * * * * * * * * * * * * * * * * * * * * |

| ; Confi         | gure Output Functions                   |

|                 | Table 10-14)                            |

| •               |                                         |

| ;****           | * * * * * * * * * * * * * * * * * * * * |

| ; Ass           | sign TX2 To Pin RP1                     |

|                 | _<br>**************                     |

| MOVLW           | 0x06                                    |

| MOVWF           | RPOR1, BANKED                           |

| • * * * * * *   | * * * * * * * * * * * * * * * * * * * * |

|                 | Registers                               |

|                 | ********                                |

| ,<br>BCF        | INTCON, GIE                             |

| MOVLW           |                                         |

| MOVWF           | EECON2, 0                               |

| MOVLW           | 0xAA                                    |

|                 | EECON2, 0                               |

| ; Write         | Protect PPS                             |

|                 | PPSCON, IOLOCK, BANKED                  |

| 201             | TIDEON, TODOCK, DANKED                  |

Note: If the Configuration bit, IOL1WAY = 1, once the IOLOCK bit is set, it cannot be cleared, preventing any future RP register changes. The IOLOCK bit is cleared back to '0' on any device Reset.

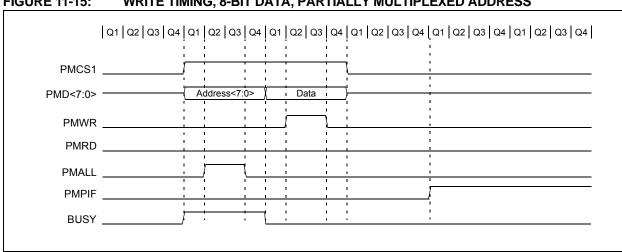

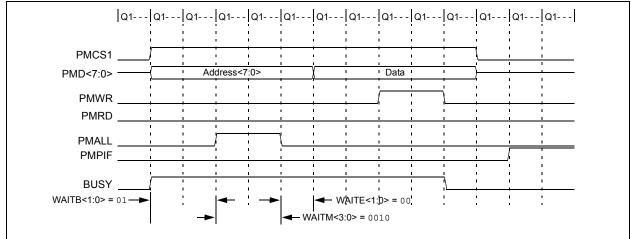

#### WRITE TIMING, 8-BIT DATA, PARTIALLY MULTIPLEXED ADDRESS FIGURE 11-15:

#### FIGURE 11-16: WRITE TIMING, 8-BIT DATA, WAIT STATES ENABLED, PARTIALLY MULTIPLEXED ADDRESS

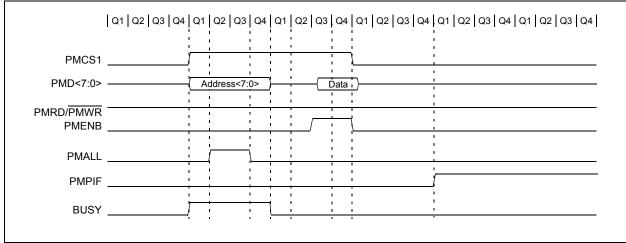

#### FIGURE 11-17: READ TIMING, 8-BIT DATA, PARTIALLY MULTIPLEXED ADDRESS, **ENABLE STROBE**

# REGISTER 15-3: OSCCON2: OSCILLATOR CONTROL REGISTER 2 (ACCESS F87h)

| U-0        | R-0 <sup>(2)</sup>   | U-0                                                                                           | R/W-1            | R/W-0 <sup>(2)</sup>  | R/W-1            | U-0             | U-0   |  |  |

|------------|----------------------|-----------------------------------------------------------------------------------------------|------------------|-----------------------|------------------|-----------------|-------|--|--|

| _          | SOSCRUN              | _                                                                                             | SOSCDRV          | SOSCGO <sup>(3)</sup> | PRISD            | _               | _     |  |  |

| bit 7      |                      |                                                                                               |                  |                       |                  | •               | bit ( |  |  |

|            |                      |                                                                                               |                  |                       |                  |                 |       |  |  |

| Legend:    |                      |                                                                                               |                  |                       |                  |                 |       |  |  |

| R = Reada  | able bit             | W = Writable                                                                                  | bit              | U = Unimpler          | nented bit, read | <b>as</b> `0′   |       |  |  |

| -n = Value | e at POR             | '1' = Bit is set                                                                              |                  | '0' = Bit is cle      | ared             | x = Bit is unkn | nown  |  |  |

|            |                      |                                                                                               |                  |                       |                  |                 |       |  |  |

| bit 7      | Unimplement          | ted: Read as '                                                                                | 0'               |                       |                  |                 |       |  |  |

| bit 6      | SOSCRUN: S           | OSC Run Stat                                                                                  | us bit           |                       |                  |                 |       |  |  |

|            |                      | 1 = System clock comes from secondary SOSC                                                    |                  |                       |                  |                 |       |  |  |

|            | 0 = System c         | lock comes fro                                                                                | m an oscillato   | or other than So      | OSC              |                 |       |  |  |

| bit 5      | Unimplement          | ted: Read as '                                                                                | 0'               |                       |                  |                 |       |  |  |

| bit 4      | SOSCDRV: S           | SOSCDRV: SOSC Drive Control bit                                                               |                  |                       |                  |                 |       |  |  |

|            | 1 = T1OSC/S          | 1 = T1OSC/SOSC circuit oscillator drive circuit selected by Configuration bits, CONFIG2L<4:3> |                  |                       |                  |                 |       |  |  |

|            | 0 = Low-powe         | er T1OSC/SOS                                                                                  | SC circuit is se | elected               |                  |                 |       |  |  |

| bit 3      | SOSCGO: Os           | SOSCGO: Oscillator Start Control bit                                                          |                  |                       |                  |                 |       |  |  |

|            | 1 = Turns on         | 1 = Turns on the oscillator, even if no peripherals are requesting it.                        |                  |                       |                  |                 |       |  |  |

|            | 0 = Oscillator       | is shut off unle                                                                              | ess peripheral   | s are requestir       | ng it            |                 |       |  |  |

| bit 2      | PRISD: Prima         | ry Oscillator D                                                                               | rive Circuit sh  | utdown                |                  |                 |       |  |  |

|            | 1 = Oscillator       | 1 = Oscillator drive circuit on                                                               |                  |                       |                  |                 |       |  |  |

|            | 0 = Oscillator       | drive circuit of                                                                              | f (zero power)   |                       |                  |                 |       |  |  |

| bit 1-0    | Unimplement          | ted: Read as '                                                                                | 0'               |                       |                  |                 |       |  |  |

| Note 1:    | Reset value is '0' v | when Two-Spee                                                                                 | ed Start-up is o | enabled and '1        | ' if disabled.   |                 |       |  |  |

| 2:         | Default output freq  | uency of INTO                                                                                 | SC on Reset      | (4 MHz).              |                  |                 |       |  |  |

|            | • •                  | -                                                                                             |                  |                       |                  |                 |       |  |  |

**3:** When the SOSC is selected to run from a digital clock input, rather than an external crystal, this bit has no effect.

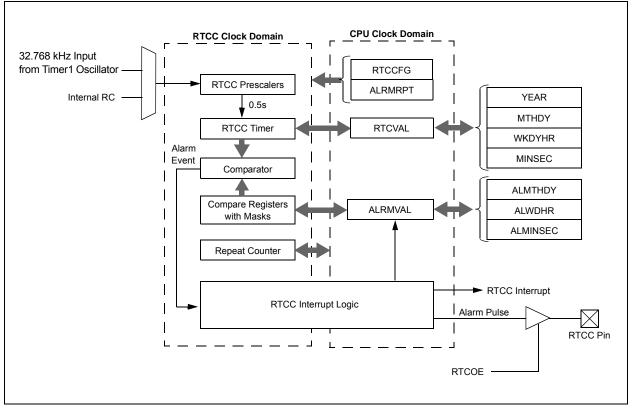

# 17.0 REAL-TIME CLOCK AND CALENDAR (RTCC)

The key features of the Real-Time Clock and Calendar (RTCC) module are:

- · Time: hours, minutes and seconds

- · 24-hour format (military time)

- Calendar: weekday, date, month and year

- Alarm configurable

- Year range: 2000 to 2099

- · Leap year correction

- BCD format for compact firmware

- · Optimized for low-power operation

- · User calibration with auto-adjust

- Calibration range: ±2.64 seconds error per month

- Requirements: external 32.768 kHz clock crystal

- · Alarm pulse or seconds clock output on RTCC pin

The RTCC module is intended for applications where accurate time must be maintained for an extended period with minimum to no intervention from the CPU. The module is optimized for low-power usage in order to provide extended battery life while keeping track of time.

The module is a 100-year clock and calendar with automatic leap year detection. The range of the clock is from 00:00:00 (midnight) on January 1, 2000 to 23:59:59 on December 31, 2099. Hours are measured in 24-hour (military time) format. The clock provides a granularity of one second with half-second visibility to the user.

### FIGURE 17-1: RTCC BLOCK DIAGRAM

**—**

.

# REGISTER 17-11: HOURS: HOURS VALUE REGISTER<sup>(1)</sup>

| U-0   | U-0 | R/W-x  | R/W-x  | R/W-x  | R/W-x  | R/W-x  | R/W-x  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| —     | —   | HRTEN1 | HRTEN0 | HRONE3 | HRONE2 | HRONE1 | HRONE0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7-6 | Unimplemented: Read as '0'                                                                                  |

|---------|-------------------------------------------------------------------------------------------------------------|

| bit 5-4 | <b>HRTEN&lt;1:0&gt;:</b> Binary Coded Decimal Value of Hour's Tens Digit bits Contains a value from 0 to 2. |

| bit 3-0 | <b>HRONE&lt;3:0&gt;:</b> Binary Coded Decimal Value of Hour's Ones Digit bits Contains a value from 0 to 9. |

**Note 1:** A write to this register is only allowed when RTCWREN = 1.

### REGISTER 17-12: MINUTES: MINUTES VALUE REGISTER

| U-0   | R/W-x   |

|-------|---------|---------|---------|---------|---------|---------|---------|

| —     | MINTEN2 | MINTEN1 | MINTEN0 | MINONE3 | MINONE2 | MINONE1 | MINONE0 |

| bit 7 |         |         |         |         |         |         | bit 0   |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7   | Unimplemented: Read as '0'                                                                                     |

|---------|----------------------------------------------------------------------------------------------------------------|

| bit 6-4 | <b>MINTEN&lt;2:0&gt;:</b> Binary Coded Decimal Value of Minute's Tens Digit bits Contains a value from 0 to 5. |

| bit 3-0 | <b>MINONE&lt;3:0&gt;:</b> Binary Coded Decimal Value of Minute's Ones Digit bits Contains a value from 0 to 9. |

## REGISTER 17-13: SECONDS: SECONDS VALUE REGISTER

| U-0   | R/W-x   |

|-------|---------|---------|---------|---------|---------|---------|---------|

| —     | SECTEN2 | SECTEN1 | SECTEN0 | SECONE3 | SECONE2 | SECONE1 | SECONE0 |

| bit 7 |         |         |         |         |         |         | bit 0   |

| Legend:           |  |                  |                        |                    |

|-------------------|--|------------------|------------------------|--------------------|

| R = Readable bit  |  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR |  | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 6-4 | <b>SECTEN&lt;2:0&gt;:</b> Binary Coded Decimal Value of Second's Tens Digit bits Contains a value from 0 to 5. |

|---------|----------------------------------------------------------------------------------------------------------------|

|         |                                                                                                                |

bit 3-0 SECONE<3:0>: Binary Coded Decimal Value of Second's Ones Digit bits Contains a value from 0 to 9.

## 20.3.1 REGISTERS

Each MSSP module has four registers for SPI mode operation. These are:

- MSSPx Control Register 1 (SSPxCON1)

- MSSPx Status Register (SSPxSTAT)

- Serial Receive/Transmit Buffer Register (SSPxBUF)

- MSSPx Shift Register (SSPxSR) Not directly accessible

SSPxCON1 and SSPxSTAT are the control and status registers in SPI mode operation. The SSPxCON1 register is readable and writable. The lower six bits of the SSPxSTAT are read-only. The upper two bits of the SSPxSTAT are read/write.

SSPxSR is the shift register used for shifting data in or out. SSPxBUF is the buffer register to which data bytes are written to or read from.

In receive operations, SSPxSR and SSPxBUF together, create a double-buffered receiver. When SSPxSR receives a complete byte, it is transferred to SSPxBUF and the SSPxIF interrupt is set.

During transmission, the SSPxBUF is not double-buffered. A write to SSPxBUF will write to both SSPxBUF and SSPxSR.

## REGISTER 20-1: SSPxSTAT: MSSPx STATUS REGISTER (SPI MODE) (ACCESS 1, FC7h; 2, F73h)

|                                                                            |                                                     |                                   |                  | •                | , ,            |               |            |

|----------------------------------------------------------------------------|-----------------------------------------------------|-----------------------------------|------------------|------------------|----------------|---------------|------------|

| R/W-1                                                                      | R/W-1                                               | R-1                               | R-1              | R-1              | R-1            | R-1           | R-1        |

| SMP                                                                        | CKE <sup>(1)</sup>                                  | D/Ā                               | Р                | S                | R/W            | UA            | BF         |

| bit 7                                                                      |                                                     |                                   |                  |                  |                |               | bit 0      |

|                                                                            |                                                     |                                   |                  |                  |                |               |            |

| Legend:                                                                    |                                                     |                                   |                  |                  |                |               |            |

| R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'         |                                                     |                                   |                  |                  |                |               |            |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown |                                                     |                                   |                  |                  |                | nown          |            |

|                                                                            |                                                     |                                   |                  |                  |                |               |            |

| bit 7                                                                      | SMP: Sample                                         |                                   |                  |                  |                |               |            |

|                                                                            | SPI Master m                                        |                                   |                  |                  |                |               |            |

|                                                                            |                                                     | a sampled at er<br>a sampled at m |                  |                  |                |               |            |

|                                                                            | SPI Slave mo                                        | •                                 |                  | aiput time       |                |               |            |

|                                                                            | SMP must be cleared when SPI is used in Slave mode. |                                   |                  |                  |                |               |            |

| bit 6                                                                      | CKE: SPI Clo                                        | ock Select bit <sup>(1)</sup>     |                  |                  |                |               |            |

|                                                                            | 1 = Transmit                                        | occurs on trans                   | sition from act  | ve to Idle clock | state          |               |            |

|                                                                            | 0 = Transmit                                        | occurs on trans                   | sition from Idle | to active clock  | state          |               |            |

| bit 5                                                                      | D/A: Data/Ad                                        |                                   |                  |                  |                |               |            |

|                                                                            | Used in I <sup>2</sup> C n                          | node only.                        |                  |                  |                |               |            |

| bit 4                                                                      | P: Stop bit                                         |                                   |                  |                  |                |               |            |

|                                                                            |                                                     | node only; this                   | bit is cleared v | when the MSSP    | module is disa | bled, SSPEN i | s cleared. |

| bit 3                                                                      | S: Start bit                                        |                                   |                  |                  |                |               |            |

|                                                                            | Used in I <sup>2</sup> C n                          | 2                                 |                  |                  |                |               |            |

| bit 2                                                                      |                                                     | /rite Information                 | n bit            |                  |                |               |            |

|                                                                            | Used in I <sup>2</sup> C n                          | node only.                        |                  |                  |                |               |            |

| bit 1                                                                      | UA: Update A                                        |                                   |                  |                  |                |               |            |

|                                                                            | Used in I <sup>2</sup> C n                          | 3                                 |                  |                  |                |               |            |

| bit 0                                                                      | BF: Buffer Fu                                       |                                   |                  |                  |                |               |            |

|                                                                            |                                                     | complete, SSP                     |                  |                  |                |               |            |

|                                                                            | 0 = Receive r                                       | not complete, S                   | SPXBUF is er     | npty             |                |               |            |

| Note 1: F                                                                  | olarity of the clo                                  | ock state is set l                | by the CKP bit   | : (SSPxCON1<4    | >).            |               |            |

|                                                                            |                                                     |                                   |                  |                  |                |               |            |

# REGISTER 20-5: SSPxSTAT: MSSPx STATUS REGISTER (I<sup>2</sup>C MODE) (1, ACCESS FC7h; 2, F73h)

| R/W-1               | R/W-1                            | R-1                                      | R-1                    | R-1              | R-1                  | R-1               | R-1      |

|---------------------|----------------------------------|------------------------------------------|------------------------|------------------|----------------------|-------------------|----------|

| SMP                 | CKE                              | D/A                                      | P <sup>(1)</sup>       | S <sup>(1)</sup> | R/W <sup>(2,3)</sup> | UA                | BF       |

| bit 7               |                                  |                                          |                        |                  |                      |                   | bit C    |

| Logondi             |                                  |                                          |                        |                  |                      |                   |          |

| Legend:<br>R = Read | abla hit                         | M = Mritable                             | h it                   |                  | monted hit rea       | d oo 'O'          |          |

|                     |                                  | W = Writable<br>'1' = Bit is set         |                        | -                | emented bit, rea     | x = Bit is unkr   | 2011/2   |

| -n = Value          | alPOR                            | I = DILIS SEL                            |                        | ʻ0' = Bit is cl  | eareu                |                   | IOWII    |

| bit 7               | SMP: Slew                        | Rate Control bit                         |                        |                  |                      |                   |          |

|                     |                                  | <u>Slave mode:</u>                       |                        |                  |                      |                   |          |

|                     |                                  | ate control disabl                       |                        |                  |                      | 1 MHz)            |          |

| hit C               | 0 = Slew ra                      | ate control enable                       | ed for High-Spe        | ea moae (40      | U KHZ)               |                   |          |

| bit 6               |                                  | Select bit                               |                        |                  |                      |                   |          |

|                     |                                  | <u>SMBus specific i</u>                  | nputs                  |                  |                      |                   |          |

|                     |                                  | SMBus specific                           |                        |                  |                      |                   |          |

| bit 5               | D/A: Data/A                      | ddress bit                               |                        |                  |                      |                   |          |

|                     | In Master m                      | ode:                                     |                        |                  |                      |                   |          |

|                     | Reserved.                        |                                          |                        |                  |                      |                   |          |

|                     | In Slave mo                      |                                          | to received or t       | ranamittad w     | aa data              |                   |          |

|                     |                                  | s that the last by<br>s that the last by |                        |                  |                      |                   |          |

| bit 4               | P: Stop bit <sup>(1</sup>        | •                                        |                        |                  |                      |                   |          |

|                     | 1 = Indicate                     | s that a Stop bit was not detected       |                        | cted last        |                      |                   |          |

| bit 3               | S: Start bit <sup>(1</sup>       |                                          |                        |                  |                      |                   |          |

|                     | 1 = Indicate                     | s that a Start bit                       | has been dete          | cted last        |                      |                   |          |

|                     |                                  | was not detecte                          |                        |                  |                      |                   |          |

| bit 2               | R/W: Read/                       | Write Information                        | n bit <sup>(2,3)</sup> |                  |                      |                   |          |

|                     | In Slave mo                      | de:                                      |                        |                  |                      |                   |          |

|                     | 1 = Read<br>0 = Write            |                                          |                        |                  |                      |                   |          |

|                     | In Master m                      | ode.                                     |                        |                  |                      |                   |          |

|                     |                                  | it is in progress                        |                        |                  |                      |                   |          |

|                     | 0 = Transmi                      | it is not in progre                      | SS                     |                  |                      |                   |          |

| bit 1               | UA: Update                       | Address bit (10-                         | Bit Slave mode         | e only)          |                      |                   |          |

|                     |                                  | s that the user n                        | -                      | the address      | in the SSPxADI       | D register        |          |

|                     |                                  | does not need t                          | to be updated          |                  |                      |                   |          |

| bit 0               |                                  | Full Status bit                          |                        |                  |                      |                   |          |

|                     | <u>In Transmit</u><br>1 = SSPxBL |                                          |                        |                  |                      |                   |          |

|                     | 0 = SSPxBL                       |                                          |                        |                  |                      |                   |          |

|                     | In Receive r                     |                                          |                        |                  |                      |                   |          |

|                     |                                  | JF is full (does n<br>JF is empty (doe   |                        |                  | ,                    |                   |          |

| Note 1:             | This bit is cleare               | ed on Reset and                          | when SSPEN             | is cleared.      |                      |                   |          |

| 2:                  | This bit holds th                | e R/W bit inform                         | ation following        | the last addre   | ess match. This      | bit is only valid | from the |

|                     | address match t                  | to the next Start                        | bit, Stop bit or i     | not ACK bit.     |                      | -                 |          |

3: ORing this bit with SEN, RSEN, PEN, RCEN or ACKEN will indicate if the MSSPx is in Active mode.

# 21.2 EUSART Asynchronous Mode

The Asynchronous mode of operation is selected by clearing the SYNC bit (TXSTAx<4>). In this mode, the EUSART uses standard Non-Return-to-Zero (NRZ) format (one Start bit, eight or nine data bits and one Stop bit). The most common data format is 8 bits. An on-chip dedicated 8-bit/16-bit BRG can be used to derive standard baud rate frequencies from the oscillator.

The EUSART transmits and receives the LSb first. The EUSART's transmitter and receiver are functionally independent but use the same data format and baud rate. The BRG produces a clock, either x16 or x64 of the bit shift rate, depending on the BRGH and BRG16 bits (TXSTAx<2> and BAUDCONx<3>). Parity is not supported by the hardware but can be implemented in software and stored as the ninth data bit.

When operating in Asynchronous mode, the EUSART module consists of the following important elements:

- Baud Rate Generator

- Sampling Circuit

- Asynchronous Transmitter

- · Asynchronous Receiver

- Auto-Wake-up on Sync Break Character

- 12-Bit Break Character Transmit

- Auto-Baud Rate Detection

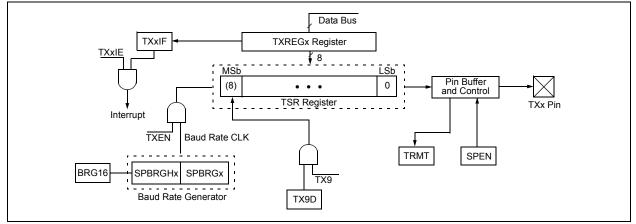

#### 21.2.1 EUSART ASYNCHRONOUS TRANSMITTER

Figure 21-3 displays the EUSART transmitter block diagram.

The heart of the transmitter is the Transmit (Serial) Shift Register (TSR). The shift register obtains its data from the Read/Write Transmit Buffer register, TXREGx. The TXREGx register is loaded with data in software. The TSR register is not loaded until the Stop bit has been transmitted from the previous load. As soon as the Stop bit is transmitted, the TSR is loaded with new data from the TXREGx register (if available). Once the TXREGx register transfers the data to the TSR register (occurs in one TcY), the TXREGx register is empty and the TXxIF flag bit is set. This interrupt can be enabled or disabled by setting or clearing the interrupt enable bit, TXxIE. TXxIF will be set regardless of the state of TXxIE; it cannot be cleared in software. TXxIF is also not cleared immediately upon loading TXREGx, but becomes valid in the second instruction cycle following the load instruction. Polling TXxIF immediately following a load of TXREGx will return invalid results.

While TXxIF indicates the status of the TXREGx register; another bit, TRMT (TXSTAx<1>), shows the status of the TSR register. TRMT is a read-only bit, which is set when the TSR register is empty. No interrupt logic is tied to this bit, so the user has to poll this bit in order to determine if the TSR register is empty.

| Note 1: | The TSR register is not mapped in data memory, so it is not available to the user. |

|---------|------------------------------------------------------------------------------------|

| 2:      | Flag bit, TXxIF, is set when enable bit, TXEN, is set.                             |

To set up an Asynchronous Transmission:

- Initialize the SPBRGHx:SPBRGx registers for the appropriate baud rate. Set or clear the BRGH and BRG16 bits, as required, to achieve the desired baud rate.