Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 48MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART, USB                              |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 22                                                                          |

| Program Memory Size        | 64KB (32K x 16)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 3.8K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 2.75V                                                                  |

| Data Converters            | A/D 10x10b/12b                                                              |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

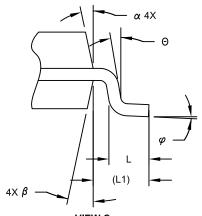

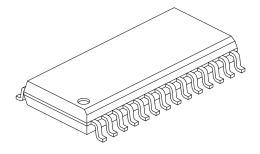

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                              |

| Supplier Device Package    | 28-SSOP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf26j53-i-ss |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### TABLE 1-1: DEVICE FEATURES FOR THE PIC18F2XJ53 (28-PIN DEVICES)

| Features                             | PIC18F26J53                                                                      | PIC18F27J53                  |  |  |

|--------------------------------------|----------------------------------------------------------------------------------|------------------------------|--|--|

| Operating Frequency                  | DC – 48 MHz                                                                      | DC – 48 MHz                  |  |  |

| Program Memory (Kbytes)              | 64                                                                               | 128                          |  |  |

| Program Memory (Instructions)        | 32,768                                                                           | 65,536                       |  |  |

| Data Memory (Kbytes)                 | 3.8                                                                              | 3.8                          |  |  |

| Interrupt Sources                    | 3                                                                                | 0                            |  |  |

| I/O Ports                            | Ports A, B, C                                                                    |                              |  |  |

| Timers                               | 8                                                                                |                              |  |  |

| Enhanced Capture/Compare/PWM Modules | Modules 3 ECCP and 7 CCP                                                         |                              |  |  |

| Serial Communications                | MSSP (2), Enhanced USART (2), USB                                                |                              |  |  |

| Parallel Communications (PMP/PSP)    | No                                                                               |                              |  |  |

| 10/12-Bit Analog-to-Digital Module   | 10 Input Channels                                                                |                              |  |  |

| Resets (and Delays)                  | POR, BOR, RESET Instruction, Stack Full, Stack Underflow, MCLR, W<br>(PWRT, OST) |                              |  |  |

| Instruction Set                      | 75 Instructions, 83 with Exter                                                   | nded Instruction Set Enabled |  |  |

| Packages                             | 28-Pin QFN, SOIC, SSO                                                            | OP and SPDIP (300 mil)       |  |  |

#### TABLE 1-2:DEVICE FEATURES FOR THE PIC18F4XJ53 (44-PIN DEVICES)

| Features                             | PIC18F46J53                                                                        | PIC18F47J53                  |  |

|--------------------------------------|------------------------------------------------------------------------------------|------------------------------|--|

| Operating Frequency                  | DC – 48 MHz                                                                        | DC – 48 MHz                  |  |

| Program Memory (Kbytes)              | 64                                                                                 | 128                          |  |

| Program Memory (Instructions)        | 32,768                                                                             | 65,536                       |  |

| Data Memory (Kbytes)                 | 3.8                                                                                | 3.8                          |  |

| Interrupt Sources                    | 3                                                                                  | 0                            |  |

| I/O Ports                            | Ports A, B, C, D, E                                                                |                              |  |

| Timers                               | 8                                                                                  |                              |  |

| Enhanced Capture/Compare/PWM Modules | 3 ECCP and 7 CCP                                                                   |                              |  |

| Serial Communications                | MSSP (2), Enhanced USART (2), USB                                                  |                              |  |

| Parallel Communications (PMP/PSP)    | Yes                                                                                |                              |  |

| 10/12-Bit Analog-to-Digital Module   | 13 Input Channels                                                                  |                              |  |

| Resets (and Delays)                  | POR, BOR, RESET Instruction, Stack Full, Stack Underflow, MCLR, WDT<br>(PWRT, OST) |                              |  |

| Instruction Set                      | 75 Instructions, 83 with Exter                                                     | nded Instruction Set Enabled |  |

| Packages                             | 44-Pin QFN                                                                         | I and TQFP                   |  |

| 28-SPDIP/<br>SSOP/<br>SOIC | 28-QFN                                | Pin<br>Type                                     | Buffer<br>Type                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Description                                                                                                                                                                                                                                                                                                                                                                                          |

|----------------------------|---------------------------------------|-------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 <sup>(2)</sup>           |                                       |                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                      |

|                            | 26 <sup>(2)</sup>                     | I                                               | ST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Master Clear (Reset) input. This pin is an active-low Reset to the device.                                                                                                                                                                                                                                                                                                                           |

| 9                          | 6                                     | I                                               | ST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Oscillator crystal or external clock input.<br>Oscillator crystal input or external clock source<br>input. ST buffer when configured in RC mode;<br>CMOS otherwise. Main oscillator input<br>connection.                                                                                                                                                                                             |

|                            |                                       | I                                               | CMOS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | External clock source input; always associated with pin function OSC1 (see related OSC1/CLKI pins).                                                                                                                                                                                                                                                                                                  |

|                            |                                       | I/O                                             | TTL/DIG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Digital I/O.                                                                                                                                                                                                                                                                                                                                                                                         |

| 10                         | 7                                     | 0                                               | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Oscillator crystal or clock output.<br>Oscillator crystal output. Connects to crystal or<br>resonator in Crystal Oscillator mode.                                                                                                                                                                                                                                                                    |

|                            |                                       | 0                                               | DIG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Main oscillator feedback output connection.<br>In RC mode, OSC2 pin outputs CLKO, which<br>has 1/4 the frequency of OSC1 and denotes<br>the instruction cycle rate.                                                                                                                                                                                                                                  |

|                            |                                       | I/O                                             | TTL/DIG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                      |

| igger input w              | ith CMOS                              | levels                                          | Ar<br>O<br>Ol                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                      |

| t                          | 10<br>Datible input<br>rigger input w | 10 7<br>batible input<br>rigger input with CMOS | I     I       I     I       I     I/O       I     I       I     I       I     I       I     I       I     I       I     I       I     I       I     I       I     I       I     I       I     I       I     I       I     I       I     I       I     I       I     I       < | I     ST       I     CMOS       I     II/O       I     TTL/DIG       I     I/O       I     I |

TABLE 1-3:

PIC18F2XJ53 PINOUT I/O DESCRIPTIONS

Note 1: RA7 and RA6 will be disabled if OSC1 and OSC2 are used for the clock function.

2: 5.5V tolerant.

| Pin Number |                                          |                                                                                                                                                        | Buffor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                            |  |  |

|------------|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 44-<br>QFN | 44-<br>TQFP                              | Туре                                                                                                                                                   | Туре                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Description                                                                                                                                                                                                                                                                                                                |  |  |

|            |                                          |                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | PORTC is a bidirectional I/O port.                                                                                                                                                                                                                                                                                         |  |  |

| 34         | 32                                       | I/O<br>O<br>I<br>I/O                                                                                                                                   | STDIG<br>Analog<br>ST<br>ST/DIG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Digital I/O.<br>Timer1 oscillator output.<br>Timer1/Timer3 external clock input.<br>Remappable Peripheral Pin 11 input/output.                                                                                                                                                                                             |  |  |

| 35         | 35                                       |                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                            |  |  |

|            |                                          | I/O<br>I/O<br>I<br>O<br>I/O                                                                                                                            | ST/DIG<br>ST/DIG<br>Analog<br>DIG<br>ST/DIG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Digital I/O.<br>Capture/Compare/PWM input/output.<br>Timer1 oscillator input.<br>External USB Transceiver NOE output.<br>Remappable Peripheral Pin 12 input/output.                                                                                                                                                        |  |  |

| 36         | 36                                       |                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                            |  |  |

|            |                                          | I/O<br>I<br>I<br>O<br>I/O                                                                                                                              | ST/DIG<br>Analog<br>DIG<br>ST/DIG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Digital I/O.<br>Analog Input 11.<br>Comparator 2 Input D.<br>CTMU pulse generator output.<br>Remappable Peripheral Pin 13 input/output.                                                                                                                                                                                    |  |  |

| 42         | 42                                       |                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                            |  |  |

|            |                                          | <br> /O<br>                                                                                                                                            | ST<br>—<br>ST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Digital Input.<br>USB bus minus line input/output.<br>External USB Transceiver FM input.                                                                                                                                                                                                                                   |  |  |

| 43         | 43                                       |                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                            |  |  |

|            |                                          | <br> /O<br>                                                                                                                                            | ST<br>—<br>ST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Digital Input.<br>USB bus plus line input/output.<br>External USB Transceiver VP input.                                                                                                                                                                                                                                    |  |  |

| iput wit   |                                          |                                                                                                                                                        | S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | CMOS= CMOS compatible input or outputAnalog= Analog inputO= OutputOD= Open-Drain (no P diode to VDD)I²C= Open-Drain, I²C specific                                                                                                                                                                                          |  |  |

|            | 44-<br>QFN<br>34<br>35<br>36<br>42<br>43 | 44-<br>QFN         44-<br>TQFP           34         32           35         35           36         36           42         42           43         43 | 44-<br>QFN         44-<br>TQFP         Pin<br>Type           34         32         I/O           35         35         I/O           35         35         I/O           36         36         I/O           42         42         I           1/O         I         O           1/O         I         O           1/O         I         O           1/O         I         I/O           1/O         I         I/O           1         I         O           1         I         I/O           1         I/O         I           1         I         I | 44-<br>QFN44-<br>TQFPPin<br>TypeBuffer<br>Type3432I/O<br>O<br>O<br>I<br>I/OSTDIG<br>Analog<br>ST<br>ST/DIG3535I/O<br>I<br>I/OST/DIG<br>ST/DIG3636I/O<br>I<br>I/OST/DIG<br>ST/DIG3636I/O<br>I<br>I/OST/DIG<br>I<br>I/O4242I<br>I<br>I/OST<br>ST/DIG4343I<br>I<br>I/OST<br>ST<br>I/Oapput<br>apputI<br>I<br>IST<br>ST<br>I/O |  |  |

#### **TABLE 1-4:** PIC18F4XJ53 PINOUT I/O DESCRIPTIONS (CONTINUED)

2: Available only on 44-pin devices (PIC18F46J53, PIC18F47J53, PIC18LF46J53 and PIC18LF47J53).

3: 5.5V tolerant.

|                            | Pin N             | Pin Number<br>44- 44- Ty<br>QFN TQFP |        | D ff             | Description                                |  |  |

|----------------------------|-------------------|--------------------------------------|--------|------------------|--------------------------------------------|--|--|

| Pin Name                   |                   |                                      |        | Buffer<br>Type   |                                            |  |  |

|                            |                   |                                      |        |                  | PORTD is a bidirectional I/O port.         |  |  |

| RD0/PMD0/SCL2              | 38 <sup>(3)</sup> | 38(3)                                |        |                  |                                            |  |  |

| RD0                        |                   |                                      | I/O    | ST/DIG           | Digital I/O.                               |  |  |

| PMD0                       |                   |                                      | I/O    | ST/TTL/          | Parallel Master Port data.                 |  |  |

|                            |                   |                                      |        | DIG              | 20.000                                     |  |  |

| SCL2                       | (2)               | (2)                                  | I/O    | l <sup>2</sup> C | l <sup>2</sup> C data input/output.        |  |  |

| RD1/PMD1/SDA2              | 39 <b>(3)</b>     | 39 <b>(3)</b>                        |        |                  |                                            |  |  |

| RD1                        |                   |                                      | I/O    | ST/DIG           |                                            |  |  |

| PMD1                       |                   |                                      | I/O    | ST/TTL/<br>DIG   | Parallel Master Port data.                 |  |  |

| SDA2                       |                   |                                      | I/O    | I <sup>2</sup> C | l <sup>2</sup> C data input/output.        |  |  |

| -                          | 40(3)             | 40 <sup>(3)</sup>                    | ., O   |                  |                                            |  |  |

| RD2/PMD2/RP19<br>RD2       | 40(3)             | 40(3)                                | I/O    | ST/DIG           | Digital I/O.                               |  |  |

| PMD2                       |                   |                                      | 1/O    | ST/TTL/          | •                                          |  |  |

|                            |                   |                                      |        | DIG              |                                            |  |  |

| RP19                       |                   |                                      | I/O    | ST/DIG           | Remappable Peripheral Pin 19 input/output. |  |  |

| RD3/PMD3/RP20              | 41 <sup>(3)</sup> | 41 <sup>(3)</sup>                    |        |                  |                                            |  |  |

| RD3                        |                   |                                      | I/O    | ST/DIG           | Digital I/O.                               |  |  |

| PMD3                       |                   |                                      | I/O    | ST/TTL/          |                                            |  |  |

|                            |                   |                                      |        | DIG              |                                            |  |  |

| RP20                       |                   |                                      | I/O    | ST/DIG           | Remappable Peripheral Pin 20 input/output. |  |  |

| RD4/PMD4/RP21              | 2 <sup>(3)</sup>  | 2 <sup>(3)</sup>                     |        |                  |                                            |  |  |

| RD4                        |                   |                                      | I/O    | ST/DIG           | Digital I/O.                               |  |  |

| PMD4                       |                   |                                      | I/O    | ST/TTL/          | Parallel Master Port data.                 |  |  |

| 8804                       |                   |                                      |        | DIG              | Demonschle Devichenst Die 04 immet/endent  |  |  |

| RP21                       | (0)               | (0)                                  | I/O    | ST/DIG           | Remappable Peripheral Pin 21 input/output. |  |  |

| RD5/PMD5/RP22              | 3 <b>(3)</b>      | ვ <b>(3)</b>                         |        | 07/010           |                                            |  |  |

| RD5                        |                   |                                      | 1/O    | ST/DIG           | Digital I/O.<br>Parallel Master Port data. |  |  |

| PMD5                       |                   |                                      | I/O    | ST/TTL/<br>DIG   | Parallel Master Port data.                 |  |  |

| RP22                       |                   |                                      | I/O    | ST/DIG           | Remappable Peripheral Pin 22 input/output. |  |  |

| RD6/PMD6/RP23              | 4 <sup>(3)</sup>  | 4(3)                                 |        |                  |                                            |  |  |

| RD6/PMD6/RP23              | 4,                | 4."/                                 | I/O    | ST/DIG           | Digital I/O.                               |  |  |

| PMD6                       |                   |                                      | 1/O    | ST/TTL/          |                                            |  |  |

|                            |                   |                                      | -      | DIG              |                                            |  |  |

| RP23                       |                   |                                      | I/O    | ST/DIG           | Remappable Peripheral Pin 23 input/output. |  |  |

| RD7/PMD7/RP24              | 5 <b>(3)</b>      | 5 <b>(3)</b>                         |        |                  |                                            |  |  |

| RD7                        |                   |                                      | I/O    | ST/DIG           |                                            |  |  |

| PMD7                       |                   |                                      | I/O    | ST/TTL/          | Parallel Master Port data.                 |  |  |

|                            |                   |                                      |        | DIG              |                                            |  |  |

| RP24                       |                   |                                      | I/O    | ST/DIG           |                                            |  |  |

| Legend: TTL = TTL compatib |                   |                                      | 0 1    |                  | CMOS = CMOS compatible input or output     |  |  |

| ST = Schmitt Trigge        | er input wit      |                                      | Sievel |                  | Analog = Analog input<br>O = Output        |  |  |

| I = Input<br>P = Power     |                   |                                      |        |                  | OD = Open-Drain (no P diode to VDD)        |  |  |

| DIG = Digital output       |                   |                                      |        |                  | $I^2C$ = Open-Drain, $I^2C$ specific       |  |  |

|                            | disabled if       | OSC1                                 | and O  | SC2 are          | used for the clock function.               |  |  |

PIC18F4XJ53 PINOUT I/O DESCRIPTIONS (CONTINUED) **TABLE 1-4:**

2: Available only on 44-pin devices (PIC18F46J53, PIC18F47J53, PIC18LF46J53 and PIC18LF47J53).

3: 5.5V tolerant.

| TABLE 5-2: INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED) |                          |             |                                                                |                                                                            |                                 |  |  |  |

|--------------------------------------------------------------------|--------------------------|-------------|----------------------------------------------------------------|----------------------------------------------------------------------------|---------------------------------|--|--|--|

| Register                                                           | Register Applicable Devi |             | Power-on Reset,<br>Brown-out Reset,<br>Wake From Deep<br>Sleep | MCLR Resets<br>WDT Reset<br>RESET Instruction<br>Stack Resets<br>CM Resets | Wake-up via WDT<br>or Interrupt |  |  |  |

| IPR1                                                               | PIC18F2XJ53              | PIC18F4XJ53 | 1111 1111                                                      | 1111 1111                                                                  | uuuu uuuu                       |  |  |  |

| PIR1                                                               | PIC18F2XJ53              | PIC18F4XJ53 | 0000 0000                                                      | 0000 0000                                                                  | uuuu uuuu <b>(3)</b>            |  |  |  |

| PIE1                                                               | PIC18F2XJ53              | PIC18F4XJ53 | 0000 0000                                                      | 0000 0000                                                                  | uuuu uuuu                       |  |  |  |

| RCSTA2                                                             | PIC18F2XJ53              | PIC18F4XJ53 | 0000 000x                                                      | 0000 000x                                                                  | uuuu uuuu                       |  |  |  |

| OSCTUNE                                                            | PIC18F2XJ53              | PIC18F4XJ53 | 0000 0000                                                      | 0000 0000                                                                  | uuuu uuuu                       |  |  |  |

| T1GCON                                                             | PIC18F2XJ53              | PIC18F4XJ53 | 00x0 0x00                                                      | 0000 0x00                                                                  | uuuu uuuu                       |  |  |  |

| T3GCON                                                             | PIC18F2XJ53              | PIC18F4XJ53 | 00x0 0x00                                                      | uuuu uxuu                                                                  | uuuu uxuu                       |  |  |  |

| TRISE <sup>(5)</sup>                                               | PIC18F2XJ53              | PIC18F4XJ53 | 00111                                                          | uu111                                                                      | uuuuu                           |  |  |  |

| TRISD <sup>(5)</sup>                                               | PIC18F2XJ53              | PIC18F4XJ53 | 1111 1111                                                      | 1111 1111                                                                  | uuuu uuuu                       |  |  |  |

| TRISC                                                              | PIC18F2XJ53              | PIC18F4XJ53 | 11111                                                          | 11111                                                                      | uuuuu                           |  |  |  |

| TRISB                                                              | PIC18F2XJ53              | PIC18F4XJ53 | 1111 1111                                                      | 1111 1111                                                                  | uuuu uuuu                       |  |  |  |

| TRISA                                                              | PIC18F2XJ53              | PIC18F4XJ53 | 111- 1111                                                      | 111- 1111                                                                  | uuu- uuuu                       |  |  |  |

| LATE <sup>(5)</sup>                                                | PIC18F2XJ53              | PIC18F4XJ53 | xxx                                                            | uuu                                                                        | uuu                             |  |  |  |

| LATD <sup>(5)</sup>                                                | PIC18F2XJ53              | PIC18F4XJ53 | xxxx xxxx                                                      | uuuu uuuu                                                                  | uuuu uuuu                       |  |  |  |

| LATC                                                               | PIC18F2XJ53              | PIC18F4XJ53 | xxxxx                                                          | uuuuu                                                                      | uuuuu                           |  |  |  |

| LATB                                                               | PIC18F2XJ53              | PIC18F4XJ53 | xxxx xxxx                                                      | uuuu uuuu                                                                  | uuuu uuuu                       |  |  |  |

| LATA                                                               | PIC18F2XJ53              | PIC18F4XJ53 | xxx- xxxx                                                      | uuu- uuuu                                                                  | uuu- uuuu                       |  |  |  |

| DMACON1                                                            | PIC18F2XJ53              | PIC18F4XJ53 | 0000 0000                                                      | 0000 0000                                                                  | uuuu uuuu                       |  |  |  |

| OSCCON2                                                            | PIC18F2XJ53              | PIC18F4XJ53 | -0-1 01                                                        | _                                                                          | -                               |  |  |  |

| DMACON2                                                            | PIC18F2XJ53              | PIC18F4XJ53 | 0000 0000                                                      | 0000 0000                                                                  | uuuu uuuu                       |  |  |  |

| HLVDCON                                                            | PIC18F2XJ53              | PIC18F4XJ53 | 0000 0000                                                      | 0000 0000                                                                  | uuuu uuuu                       |  |  |  |

| PORTE <sup>(5)</sup>                                               | PIC18F2XJ53              | PIC18F4XJ53 | xxx                                                            | uuu                                                                        | uuu                             |  |  |  |

| PORTD <sup>(5)</sup>                                               | PIC18F2XJ53              | PIC18F4XJ53 | xxxx xxxx                                                      | uuuu uuuu                                                                  | uuuu uuuu                       |  |  |  |

| PORTC                                                              | PIC18F2XJ53              | PIC18F4XJ53 | xxxx -xxx                                                      | uuuu -uuu                                                                  | uuuu -uuu                       |  |  |  |

| PORTB                                                              | PIC18F2XJ53              | PIC18F4XJ53 | xxxx xxxx                                                      | սսսս սսսս                                                                  | uuuu uuuu                       |  |  |  |

| PORTA                                                              | PIC18F2XJ53              | PIC18F4XJ53 | xxx- xxxx                                                      | uuu- uuuu                                                                  | uuu- uuuu                       |  |  |  |

| SPBRGH1                                                            | PIC18F2XJ53              | PIC18F4XJ53 | 0000 0000                                                      | 0000 0000                                                                  | uuuu uuuu                       |  |  |  |

| BAUDCON1                                                           | PIC18F2XJ53              | PIC18F4XJ53 | 0100 0-00                                                      | 0100 0-00                                                                  | uuuu u-uu                       |  |  |  |

| SPBRGH2                                                            | PIC18F2XJ53              | PIC18F4XJ53 | 0000 0000                                                      | 0000 0000                                                                  | uuuu uuuu                       |  |  |  |

| BAUDCON2                                                           | PIC18F2XJ53              | PIC18F4XJ53 | 0100 0-00                                                      | 0100 0-00                                                                  | uuuu u-uu                       |  |  |  |

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition.

**Note 1:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware stack.

- 2: When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

- 3: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

- 4: See Table 5-1 for Reset value for specific condition.

- **5:** Not implemented for PIC18F2XJ53 devices.

- 6: Not implemented for "LF" devices.

| TABLE 5-2:             | INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED) |             |                                                                |                                                                            |                                 |  |  |  |  |  |

|------------------------|---------------------------------------------------------|-------------|----------------------------------------------------------------|----------------------------------------------------------------------------|---------------------------------|--|--|--|--|--|

| Register               | Applicable Devices                                      |             | Power-on Reset,<br>Brown-out Reset,<br>Wake From Deep<br>Sleep | MCLR Resets<br>WDT Reset<br>RESET Instruction<br>Stack Resets<br>CM Resets | Wake-up via WDT<br>or Interrupt |  |  |  |  |  |

| PMCONL                 | PIC18F2XJ53                                             | PIC18F4XJ53 | 000- 0000                                                      | 000- 0000                                                                  | uuu- uuuu                       |  |  |  |  |  |

| PMMODEH                | PIC18F2XJ53                                             | PIC18F4XJ53 | 0000 0000                                                      | 0000 0000                                                                  | uuuu uuuu                       |  |  |  |  |  |

| PMMODEL                | PIC18F2XJ53                                             | PIC18F4XJ53 | 0000 0000                                                      | 0000 0000                                                                  | uuuu uuuu                       |  |  |  |  |  |

| PMDOUT2H               | PIC18F2XJ53                                             | PIC18F4XJ53 | 0000 0000                                                      | 0000 0000                                                                  | uuuu uuuu                       |  |  |  |  |  |

| PMDOUT2L               | PIC18F2XJ53                                             | PIC18F4XJ53 | 0000 0000                                                      | 0000 0000                                                                  | uuuu uuuu                       |  |  |  |  |  |

| PMDIN2H                | PIC18F2XJ53                                             | PIC18F4XJ53 | 0000 0000                                                      | 0000 0000                                                                  | uuuu uuuu                       |  |  |  |  |  |

| PMDIN2L                | PIC18F2XJ53                                             | PIC18F4XJ53 | 0000 0000                                                      | 0000 0000                                                                  | uuuu uuuu                       |  |  |  |  |  |

| PMEH                   | PIC18F2XJ53                                             | PIC18F4XJ53 | 0000 0000                                                      | 0000 0000                                                                  | uuuu uuuu                       |  |  |  |  |  |

| PMEL                   | PIC18F2XJ53                                             | PIC18F4XJ53 | 0000 0000                                                      | 0000 0000                                                                  | uuuu uuuu                       |  |  |  |  |  |

| PMSTATH                | PIC18F2XJ53                                             | PIC18F4XJ53 | 00 0000                                                        | 00 0000                                                                    | uu uuuu                         |  |  |  |  |  |

| PMSTATL                | PIC18F2XJ53                                             | PIC18F4XJ53 | 10 1111                                                        | 10 1111                                                                    | uu uuuu                         |  |  |  |  |  |

| CVRCON                 | PIC18F2XJ53                                             | PIC18F4XJ53 | 0000 0000                                                      | 0000 0000                                                                  | uuuu uuuu                       |  |  |  |  |  |

| CCPTMRS0               | PIC18F2XJ53                                             | PIC18F4XJ53 | 0000 0000                                                      | 0000 0000                                                                  | uuuu uuuu                       |  |  |  |  |  |

| CCPTMRS1               | PIC18F2XJ53                                             | PIC18F4XJ53 | 0000 0000                                                      | 0000 0000                                                                  | uuuu uuuu                       |  |  |  |  |  |

| CCPTMRS2               | PIC18F2XJ53                                             | PIC18F4XJ53 | 0000 0000                                                      | 0000 0000                                                                  | uuuu uuuu                       |  |  |  |  |  |

| DSGPR1 <sup>(6)</sup>  | PIC18F2XJ53                                             | PIC18F4XJ53 | uuuu uuuu                                                      | uuuu uuuu                                                                  | uuuu uuuu                       |  |  |  |  |  |

| DSGPR0 <sup>(6)</sup>  | PIC18F2XJ53                                             | PIC18F4XJ53 | uuuu uuuu                                                      | uuuu uuuu                                                                  | uuuu uuuu                       |  |  |  |  |  |

| DSCONH <sup>(6)</sup>  | PIC18F2XJ53                                             | PIC18F4XJ53 | 000                                                            | 000                                                                        | uuu                             |  |  |  |  |  |

| DSCONL <sup>(6)</sup>  | PIC18F2XJ53                                             | PIC18F4XJ53 | 000                                                            | 000                                                                        | uuu                             |  |  |  |  |  |

| DSWAKEH <sup>(6)</sup> | PIC18F2XJ53                                             | PIC18F4XJ53 | d                                                              | 0                                                                          | u                               |  |  |  |  |  |

| DSWAKEL <sup>(6)</sup> | PIC18F2XJ53                                             | PIC18F4XJ53 | d-dd dd-d                                                      | 0-00 00-0                                                                  | u-uu uu-u                       |  |  |  |  |  |

| ANCON1                 | PIC18F2XJ53                                             | PIC18F4XJ53 | 00-0 0000                                                      | uu-u uuuu                                                                  | uu-u uuuu                       |  |  |  |  |  |

| ANCON0                 | PIC18F2XJ53                                             | PIC18F4XJ53 | 0000 0000                                                      | uuuu uuuu                                                                  | uuuu uuuu                       |  |  |  |  |  |

| ALRMCFG                | PIC18F2XJ53                                             | PIC18F4XJ53 | 0000 0000                                                      | uuuu uuuu                                                                  | uuuu uuuu                       |  |  |  |  |  |

| ALRMRPT                | PIC18F2XJ53                                             | PIC18F4XJ53 | 0000 0000                                                      | uuuu uuuu                                                                  | uuuu uuuu                       |  |  |  |  |  |

| ALRMVALH               | PIC18F2XJ53                                             | PIC18F4XJ53 | xxxx xxxx                                                      | uuuu uuuu                                                                  | uuuu uuuu                       |  |  |  |  |  |

| ALRMVALL               | PIC18F2XJ53                                             | PIC18F4XJ53 | xxxx xxxx                                                      | uuuu uuuu                                                                  | uuuu uuuu                       |  |  |  |  |  |

| ODCON1                 | PIC18F2XJ53                                             | PIC18F4XJ53 | 0000                                                           | uuuu                                                                       | uuuu                            |  |  |  |  |  |

| ODCON2                 | PIC18F2XJ53                                             | PIC18F4XJ53 | 00                                                             | uu                                                                         | uu                              |  |  |  |  |  |

| ODCON3                 | PIC18F2XJ53                                             | PIC18F4XJ53 | 00                                                             | uu                                                                         | uu                              |  |  |  |  |  |

| RTCCFG                 | PIC18F2XJ53                                             | PIC18F4XJ53 | 0-00 0000                                                      | u-uu uuuu                                                                  | u-uu uuuu                       |  |  |  |  |  |

| RTCCAL                 | PIC18F2XJ53                                             | PIC18F4XJ53 | 0000 0000                                                      | uuuu uuuu                                                                  | uuuu uuuu                       |  |  |  |  |  |

| TABLE 5-2: | INITIALIZATION CONDITIONS FOR ALL REGISTERS ( | CONTINUED) | ) |

|------------|-----------------------------------------------|------------|---|

|            |                                               |            |   |

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition.

**Note 1:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware stack.

- 2: When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

- 3: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

- **4:** See Table 5-1 for Reset value for specific condition.

- 5: Not implemented for PIC18F2XJ53 devices.

- 6: Not implemented for "LF" devices.

# PIC18F47J53

| TABLE 5-2: | INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED) |             |                                                                |                                                                            |                                 |  |  |  |  |  |

|------------|---------------------------------------------------------|-------------|----------------------------------------------------------------|----------------------------------------------------------------------------|---------------------------------|--|--|--|--|--|

| Register   | Applicable Devices                                      |             | Power-on Reset,<br>Brown-out Reset,<br>Wake From Deep<br>Sleep | MCLR Resets<br>WDT Reset<br>RESET Instruction<br>Stack Resets<br>CM Resets | Wake-up via WDT<br>or Interrupt |  |  |  |  |  |

| REFOCON    | PIC18F2XJ53                                             | PIC18F4XJ53 | 0-00 0000                                                      | u-uu uuuu                                                                  | u-uu uuuu                       |  |  |  |  |  |

| PADCFG1    | PIC18F2XJ53                                             | PIC18F4XJ53 | 000                                                            | uuu                                                                        | uuu                             |  |  |  |  |  |

| RTCVALH    | PIC18F2XJ53                                             | PIC18F4XJ53 | 0xxx xxxx                                                      | 0uuu uuuu                                                                  | 0uuu uuuu                       |  |  |  |  |  |

| RTCVALL    | PIC18F2XJ53                                             | PIC18F4XJ53 | 0xxx xxxx                                                      | 0uuu uuuu                                                                  | 0uuu uuuu                       |  |  |  |  |  |

| UCFG       | PIC18F2XJ53                                             | PIC18F4XJ53 | 00-0 0000                                                      | 00-0 0000                                                                  | uu-u uuuu                       |  |  |  |  |  |

| UADDR      | PIC18F2XJ53                                             | PIC18F4XJ53 | -000 0000                                                      | -uuu uuuu                                                                  | -uuu uuuu                       |  |  |  |  |  |

| UEIE       | PIC18F2XJ53                                             | PIC18F4XJ53 | 00 0000                                                        | 00 0000                                                                    | uu uuuu                         |  |  |  |  |  |

| UIE        | PIC18F2XJ53                                             | PIC18F4XJ53 | -000 0000                                                      | -000 0000                                                                  | -uuu uuuu                       |  |  |  |  |  |

| UEP15      | PIC18F2XJ53                                             | PIC18F4XJ53 | 0 0000                                                         | 0 0000                                                                     | u uuuu                          |  |  |  |  |  |

| UEP14      | PIC18F2XJ53                                             | PIC18F4XJ53 | 0 0000                                                         | 0 0000                                                                     | u uuuu                          |  |  |  |  |  |

| UEP13      | PIC18F2XJ53                                             | PIC18F4XJ53 | 0 0000                                                         | 0 0000                                                                     | u uuuu                          |  |  |  |  |  |

| UEP12      | PIC18F2XJ53                                             | PIC18F4XJ53 | 0 0000                                                         | 0 0000                                                                     | u uuuu                          |  |  |  |  |  |

| UEP11      | PIC18F2XJ53                                             | PIC18F4XJ53 | 0 0000                                                         | 0 0000                                                                     | u uuuu                          |  |  |  |  |  |

| UEP10      | PIC18F2XJ53                                             | PIC18F4XJ53 | 0 0000                                                         | 0 0000                                                                     | u uuuu                          |  |  |  |  |  |

| UEP9       | PIC18F2XJ53                                             | PIC18F4XJ53 | 0 0000                                                         | 0 0000                                                                     | u uuuu                          |  |  |  |  |  |