Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 48MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART, USB                              |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 22                                                                          |

| Program Memory Size        | 128KB (64K x 16)                                                            |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 3.8K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 2.75V                                                                  |

| Data Converters            | A/D 10x10b/12b                                                              |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Through Hole                                                                |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                     |

| Supplier Device Package    | 28-SPDIP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf27j53-i-sp |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin Number                                                                                                                                                                                                                                                      |                                          |                                                                                                                                                        | Buffor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 44-<br>QFN                                                                                                                                                                                                                                                      | 44-<br>TQFP                              | Туре                                                                                                                                                   | Туре                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Description                                                                                                                                                                                                                                                                                                                |  |  |  |  |

|                                                                                                                                                                                                                                                                 |                                          |                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | PORTC is a bidirectional I/O port.                                                                                                                                                                                                                                                                                         |  |  |  |  |

| 34                                                                                                                                                                                                                                                              | 32                                       | I/O<br>O<br>I<br>I/O                                                                                                                                   | STDIG<br>Analog<br>ST<br>ST/DIG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Digital I/O.<br>Timer1 oscillator output.<br>Timer1/Timer3 external clock input.<br>Remappable Peripheral Pin 11 input/output.                                                                                                                                                                                             |  |  |  |  |

| 35                                                                                                                                                                                                                                                              | 35                                       |                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

|                                                                                                                                                                                                                                                                 |                                          | I/O<br>I/O<br>I<br>O<br>I/O                                                                                                                            | ST/DIG<br>ST/DIG<br>Analog<br>DIG<br>ST/DIG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Digital I/O.<br>Capture/Compare/PWM input/output.<br>Timer1 oscillator input.<br>External USB Transceiver NOE output.<br>Remappable Peripheral Pin 12 input/output.                                                                                                                                                        |  |  |  |  |

| 36                                                                                                                                                                                                                                                              | 36                                       |                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

|                                                                                                                                                                                                                                                                 |                                          | I/O<br>I<br>I<br>O<br>I/O                                                                                                                              | ST/DIG<br>Analog<br>DIG<br>ST/DIG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Digital I/O.<br>Analog Input 11.<br>Comparator 2 Input D.<br>CTMU pulse generator output.<br>Remappable Peripheral Pin 13 input/output.                                                                                                                                                                                    |  |  |  |  |

| 42                                                                                                                                                                                                                                                              | 42                                       |                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

|                                                                                                                                                                                                                                                                 |                                          | <br> /O<br>                                                                                                                                            | ST<br>—<br>ST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Digital Input.<br>USB bus minus line input/output.<br>External USB Transceiver FM input.                                                                                                                                                                                                                                   |  |  |  |  |

| 43                                                                                                                                                                                                                                                              | 43                                       |                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

|                                                                                                                                                                                                                                                                 |                                          | <br> /O<br>                                                                                                                                            | ST<br>—<br>ST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Digital Input.<br>USB bus plus line input/output.<br>External USB Transceiver VP input.                                                                                                                                                                                                                                    |  |  |  |  |

| VPISTExternal USB Transceiver VP input.Legend:TTL = TTL compatible inputCMOS= CMOS compatible input or outputST = Schmitt Trigger input with CMOS levelsAnalog= Analog inputI= InputO= OutputP= PowerOD= Open-Drain (no P diode to VDD)DIG = Digital outputII2C |                                          |                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

|                                                                                                                                                                                                                                                                 | 44-<br>QFN<br>34<br>35<br>36<br>42<br>43 | 44-<br>QFN         44-<br>TQFP           34         32           35         35           36         36           42         42           43         43 | 44-<br>QFN         44-<br>TQFP         Pin<br>Type           34         32         I/O           35         35         I/O           35         35         I/O           36         36         I/O           42         42         I           1/O         I         O           1/O         I         O           1/O         I         O           1/O         I         I/O           1/O         I         I/O           1         I         O           1         I         I/O           1         I/O         I           1         I         I | 44-<br>QFN44-<br>TQFPPin<br>TypeBuffer<br>Type3432I/O<br>O<br>O<br>I<br>I/OSTDIG<br>Analog<br>ST<br>ST/DIG3535I/O<br>I<br>I/OST/DIG<br>ST/DIG3636I/O<br>I<br>I/OST/DIG<br>ST/DIG3636I/O<br>I<br>I/OST/DIG<br>I<br>I/O4242I<br>I<br>I/OST<br>ST/DIG4343I<br>I<br>I/OST<br>ST<br>I/Oapput<br>apputI<br>I<br>IST<br>ST<br>I/O |  |  |  |  |

#### **TABLE 1-4:** PIC18F4XJ53 PINOUT I/O DESCRIPTIONS (CONTINUED)

2: Available only on 44-pin devices (PIC18F46J53, PIC18F47J53, PIC18LF46J53 and PIC18LF47J53).

3: 5.5V tolerant.

#### 4.2 Run Modes

In the Run modes, clocks to both the core and peripherals are active. The difference between these modes is the clock source.

#### 4.2.1 PRI\_RUN MODE

The PRI\_RUN mode is the normal, full-power execution mode of the microcontroller. This is also the default mode upon a device Reset unless Two-Speed Start-up is enabled (see **Section 28.4 "Two-Speed Start-up"** for details). In this mode, the OSTS bit is set (see **Section 3.5.1 "Oscillator Control Register"**).

#### 4.2.2 SEC\_RUN MODE

The SEC\_RUN mode is the compatible mode to the "clock switching" feature offered in other PIC18 devices. In this mode, the CPU and peripherals are clocked from the Timer1 oscillator. This gives users the option of low-power consumption while still using a high-accuracy clock source.

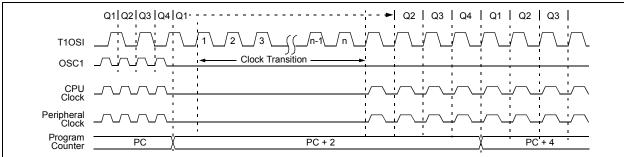

SEC\_RUN mode is entered by setting the SCS<1:0> bits to '01'. The device clock source is switched to the Timer1 oscillator (see Figure 4-1), the primary oscillator is shut down, the SOSCRUN bit (OSC-CON2<6>) is set and the OSTS bit is cleared. Note: The Timer1 oscillator should already be running prior to entering SEC\_RUN mode. If the T1OSCEN bit is not set when the SCS<1:0> bits are set to '01', entry to SEC\_RUN mode will not occur. If the Timer1 oscillator is enabled, but not yet running, device clocks will be delayed until the oscillator has started. In such situations, initial oscillator operation is far from stable and unpredictable operation may result.

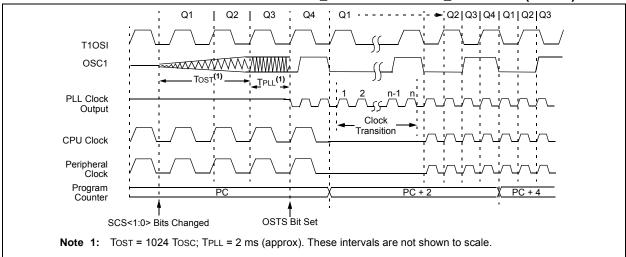

On transitions from SEC\_RUN mode to PRI\_RUN mode, the peripherals and CPU continue to be clocked from the Timer1 oscillator while the primary clock is started. When the primary clock becomes ready, a clock switch back to the primary clock occurs (see Figure 4-2). When the clock switch is complete, the SOSCRUN bit is cleared, the OSTS bit is set and the primary clock would be providing the clock. The IDLEN and SCS bits are not affected by the wake-up; the Timer1 oscillator continues to run.

#### FIGURE 4-1: TRANSITION TIMING FOR ENTRY TO SEC\_RUN MODE

© 2009-2016 Microchip Technology Inc.

#### 6.1.3 PROGRAM COUNTER

The Program Counter (PC) specifies the address of the instruction to fetch for execution. The PC is 21 bits wide and is contained in three separate 8-bit registers. The low byte, known as the PCL register, is both readable and writable. The high byte, or PCH register, contains the PC<15:8> bits; it is not directly readable or writable. Updates to the PCH register are performed through the PCLATH register. The upper byte is called PCU. This register contains the PC<20:16> bits; it is also not directly readable or writable. Updates to the PCH register. Updates to the PCU. This register contains the PC<20:16> bits; it is also not directly readable or writable. Updates to the PCU

The contents of PCLATH and PCLATU are transferred to the program counter by any operation that writes to PCL. Similarly, the upper 2 bytes of the program counter are transferred to PCLATH and PCLATU by an operation that reads PCL. This is useful for computed offsets to the PC (see **Section 6.1.6.1 "Computed GOTO"**).

The PC addresses bytes in the program memory. To prevent the PC from becoming misaligned with word instructions, the Least Significant bit (LSb) of PCL is fixed to a value of '0'. The PC increments by two to address sequential instructions in the program memory.

The CALL, RCALL, GOTO and program branch instructions write to the program counter directly. For these instructions, the contents of PCLATH and PCLATU are not transferred to the program counter.

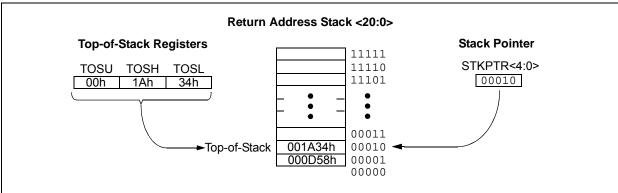

#### 6.1.4 RETURN ADDRESS STACK

The return address stack allows any combination of up to 31 program calls and interrupts to occur. The PC is pushed onto the stack when a CALL or RCALL instruction is executed, or an interrupt is Acknowledged. The PC value is pulled off the stack on a RETURN, RETLW or a RETFIE instruction (and on ADDULNK and SUBULNK instructions if the extended instruction set is enabled). PCLATU and PCLATH are not affected by any of the RETURN or CALL instructions. The stack operates as a 31-word by 21-bit RAM and a 5-bit Stack Pointer (SP), STKPTR. The stack space is not part of either program or data space. The Stack Pointer is readable and writable and the address on the top of the stack is readable and writable through the Top-of-Stack Special Function Registers (SFRs). Data can also be pushed to, or popped from, the stack using these registers.

A CALL type instruction causes a push onto the stack. The Stack Pointer is first incremented and the location pointed to by the Stack Pointer is written with the contents of the PC (already pointing to the instruction following the CALL). A RETURN type instruction causes a pop from the stack. The contents of the location pointed to by the STKPTR are transferred to the PC and then the Stack Pointer is decremented.

The Stack Pointer is initialized to '00000' after all Resets. There is no RAM associated with the location corresponding to a Stack Pointer value of '00000'; this is only a Reset value. Status bits indicate if the stack is full, has overflowed or has underflowed.

#### 6.1.4.1 Top-of-Stack Access

Only the top of the return address stack (TOS) is readable and writable. A set of three registers, TOSU:TOSH:TOSL, holds the contents of the stack location pointed to by the STKPTR register (Figure 6-3). This allows users to implement a software stack if necessary. After a CALL, RCALL or interrupt (and ADDULNK and SUBULNK instructions if the extended instruction set is enabled), the software can read the pushed value by reading the TOSU:TOSH:TOSL registers. These values can be placed on a user-defined software stack. At return time, the software can return these values to TOSU:TOSH:TOSL and do a return.

The user must disable the global interrupt enable bits while accessing the stack to prevent inadvertent stack corruption.

#### FIGURE 6-3: RETURN ADDRESS STACK AND ASSOCIATED REGISTERS

#### 6.2.3 INSTRUCTIONS IN PROGRAM MEMORY

The program memory is addressed in bytes. Instructions are stored as 2 bytes or 4 bytes in program memory. The Least Significant Byte (LSB) of an instruction word is always stored in a program memory location with an even address (LSB = 0). To maintain alignment with instruction boundaries, the PC increments in steps of 2 and the LSB will always read '0' (see Section 6.1.3 "Program Counter").

Figure 6-5 provides an example of how instruction words are stored in the program memory.

The CALL and GOTO instructions have the absolute program memory address embedded into the instruction. Since instructions are always stored on word boundaries, the data contained in the instruction is a word address. The word address is written to PC<20:1>, which accesses the desired byte address in program memory. Instruction #2 in Figure 6-5 displays how the instruction, GOTO 0006h, is encoded in the program memory. Program branch instructions, which encode a relative address offset, operate in the same manner. The offset value stored in a branch instruction represents the number of single-word instructions that the PC will be offset by. Section 29.0 "Instruction Set Summary" provides further details of the instruction set.

|                |            |                    | LSB = 1 | LSB = 0 | Word Address $\downarrow$ |

|----------------|------------|--------------------|---------|---------|---------------------------|

|                | Program N  |                    |         |         | 000000h                   |

|                | Byte Locat | ions $\rightarrow$ |         |         | 000002h                   |

|                |            |                    |         |         | 000004h                   |

|                |            |                    |         |         | 000006h                   |

| Instruction 1: | MOVLW      | 055h               | 0Fh     | 55h     | 000008h                   |

| Instruction 2: | GOTO       | 0006h              | EFh     | 03h     | 00000Ah                   |

|                |            |                    | F0h     | 00h     | 00000Ch                   |

| Instruction 3: | MOVFF      | 123h, 456          | h C1h   | 23h     | 00000Eh                   |

|                |            |                    | F4h     | 56h     | 000010h                   |

|                |            |                    |         |         | 000012h                   |

|                |            |                    |         |         | 000014h                   |

#### FIGURE 6-5: INSTRUCTIONS IN PROGRAM MEMORY

#### 6.2.4 TWO-WORD INSTRUCTIONS

The standard PIC18 instruction set has four two-word instructions: CALL, MOVFF, GOTO and LSFR. In all cases, the second word of the instructions always has '1111' as its four Most Significant bits (MSbs); the other 12 bits are literal data, usually a data memory address.

The use of '1111' in the 4 MSbs of an instruction specifies a special form of NOP. If the instruction is executed in proper sequence immediately after the first word, the data in the second word is accessed and

#### EXAMPLE 6-4: TWO-WORD INSTRUCTIONS

used by the instruction sequence. If the first word is skipped for some reason and the second word is executed by itself, a NOP is executed instead. This is necessary for cases when the two-word instruction is preceded by a conditional instruction that changes the PC. Example 6-4 illustrates how this works.

Note: See Section 6.5 "Program Memory and the Extended Instruction Set" for information on two-word instructions in the extended instruction set.

| CASE 1:      |          |             |            |                              |

|--------------|----------|-------------|------------|------------------------------|

| Object Code  |          | Source Code | 9          |                              |

| 0110 0110 00 | 0000 000 | TSTFSZ      | REG1       | ; is RAM location 0?         |

| 1100 0001 00 | 010 0011 | MOVFF       | REG1, REG2 | ; No, skip this word         |

| 1111 0100 01 | LO1 0110 |             |            | ; Execute this word as a NOP |

| 0010 0100 00 | 0000 000 | ADDWF       | REG3       | ; continue code              |

| CASE 2:      |          |             |            |                              |

| Object Code  |          | Source Code | 9          |                              |

| 0110 0110 00 | 0000 000 | TSTFSZ      | REG1       | ; is RAM location 0?         |

| 1100 0001 00 | 010 0011 | MOVFF       | REG1, REG2 | ; Yes, execute this word     |

| 1111 0100 01 | LO1 0110 |             |            | ; 2nd word of instruction    |

| 0010 0100 00 | 0000 000 | ADDWF       | REG3       | ; continue code              |

#### 6.3.5 SPECIAL FUNCTION REGISTERS

The SFRs are registers used by the CPU and peripheral modules for controlling the desired operation of the device. These registers are implemented as static RAM. SFRs start at the top of data memory (FFFh) and extend downward to occupy more than the top half of Bank 15 (F40h to FFFh). Table 6-2, Table 6-3 and Table 6-4 provide a list of these registers.

The SFRs can be classified into two sets: those associated with the "core" device functionality (ALU, Resets and interrupts) and those related to the peripheral functions. The Reset and Interrupt registers are described in their corresponding chapters, while the ALU's STATUS register is described later in this section. Registers related to the operation of the peripheral features are described in the chapter for that peripheral.

The SFRs are typically distributed among the peripherals whose functions they control. Unused SFR locations are unimplemented and read as '0's

Note: The SFRs located between EB0h and F5Fh are not part of the Access Bank. Either BANKED instructions (using BSR) or the MOVFF instruction should be used to access these locations. When programming in MPLAB<sup>®</sup> C18, the compiler will automatically use the appropriate addressing mode.

#### TABLE 6-2: ACCESS BANK SPECIAL FUNCTION REGISTER MAP

| FFFhTOSUFDFhINDE2 <sup>(1)</sup> FBFhPSTR1CONF9FhIPR1F7FhSPBRGH1FFChTOSLFDDhPOSTIDC2 <sup>(1)</sup> FBEhECCP1ASF9DhPIR1F7EhBAUDCON1FFChSTSKPTRFDChPREINC2 <sup>(1)</sup> FBChCCPR1HF9ChRCSTA2F7ChBAUDCON2FFBhPCLATUFDBhPLUSW2 <sup>(1)</sup> FBBhCCPR1LF9BhOSCTUNEF7BhTMR3HFFAhPCLATHFDAhFSR2LFBAhCCP1CONF9AhF1GCONF7AhTMR3LFF9hPCLFDDhFSR2LFBAhCCP1CONF9AhF1GCONF7AhTMR4LFF7hTBLPTRUFDBhSTATUSF6BhECCP2ASF9AhF1GCONF7AhTMR4LFF7hTBLPTRLFDBhTMR0LF6BhCCP2CHF97hT3GCONF77hPR4FF7hTBLPTRLFDBhTMR0LF6BhCCP2CNF93hTRISEF7AhSSP2BUFFF4hPRODLFD4h <sup>(5)</sup> F64hCCP2CONF93hTRISEF7AhSSP22OT1FF3hPRODLFD2hCM1CONF62hCTMUCONLF93hTRISEF7AhSSP22ON1FF7hINTCONFD2hCM1CONF62hCTMUCONLF93hTRISEF7AhSSP22ON1FF7hINTCONFD2hCM1CONF62hCTMUCONLF93hTRISEF7AhSSP22ON1FF7hINTCONFD2hCM1CONF64h <t< th=""><th>Address</th><th>Name</th><th>Address</th><th>Name</th><th>Address</th><th>Name</th><th>Address</th><th>Name</th><th>Address</th><th>Name</th></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                 | Address | Name                    | Address | Name                    | Address | Name     | Address | Name                   | Address | Name                     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-------------------------|---------|-------------------------|---------|----------|---------|------------------------|---------|--------------------------|

| FFDhTOSLFDDhPOSTDEC2 <sup>(1)</sup> FBDhECCP1DELF9DhPIE1F7DhSPBRGH2FFChSTKPTRFDChPREINC2 <sup>(1)</sup> FBChCCPR1HF9ChRCSTA2F7ChBAUDCON2FFBhPCLATUFDBhPLUSW2 <sup>(1)</sup> FBBhCCPR1LF9BhOSCTUNEF7BhTMR3HFFAhPCLATHFDAhFSR2HFBBhCCP1CONF99hIPRSF78hTMR3LFF8hPCLFD9hFSR2LFB9hPSTR2CONF99hIPRSF78hTMR4FF7hTBLPTRUFD8hSTATUSFB8hECCP2ASF99hIPRSF78hTMR4FF7hTBLPTRLFD6hTMR0HF87hECCP2DELF97hT3GCONF77hPR4FF6hTBLPTRLFD6hTMR0LF86hCCPR2LF99hTRISEF76hT4CONFF8hTABLATFD6hTMR0LF86hCCPR2LF99hTRISEF76hSSP2B/FFF3hPRODLFD3hOSCCONF68hCCPR2LF99hTRISEF77hSSP2D/FFF7hINTCONFD2hCMICONF62hCTMUCONLF92hTRISAF77hSSP2CON1FF7hINTCONFD2hCMICONF62hCTMUCONLF92hTRISAF77hSSP2CON1FF7hINTCONFD2hCMICONF62hCTMUCONLF92hTRISAF77hSSP2CON1FF7hINTCONFD2hCMICONF62hTCMICON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | FFFh    | TOSU                    | FDFh    | INDF2 <sup>(1)</sup>    | FBFh    | PSTR1CON | F9Fh    | IPR1                   | F7Fh    | SPBRGH1                  |

| FFCh         STKPTR         FDCh         PREINC2 <sup>(1)</sup> FBCh         CCPR1H         F9Ch         RCSTA2         F7Ch         BAUDCON2           FFBh         PCLATU         FDBh         PLUSW2 <sup>(1)</sup> FBBh         CCPR1L         F9Bh         OSCTUNE         F7Bh         TMR3H           FF5h         PCL         FDBh         FSR2H         FBBh         CCPR1C         F9Bh         TIGCON         F7Ah         TMR3H           FF5h         FDL         FDBh         STATUS         FBBh         ECCP2AS         F9Bh         PR5         F7bh         TMR4           FF7h         TBLPTRH         FD7h         TMR0H         FB6h         CCPR2H         F96h         TRISE         F76h         SSP2BUF           FF5h         TABLAT         FD6h         TMR0L         FB6h         CCPR2H         F96h         TRISE         F76h         SSP2BUF           FF5h         TABLAT         FD5h         TOCON         F85h         CCPR2H         F96h         TRISE         F76h         SSP2BUF           FF3h         PRODL         FD3h         OSCCON         F83h         CTMUCONH         F93h         TRISE         F73h         SSP2CON1           FF7h         INTCON </td <td>FFEh</td> <td>TOSH</td> <td>FDEh</td> <td>POSTINC2<sup>(1)</sup></td> <td>FBEh</td> <td>ECCP1AS</td> <td>F9Eh</td> <td>PIR1</td> <td>F7Eh</td> <td>BAUDCON1</td> | FFEh    | TOSH                    | FDEh    | POSTINC2 <sup>(1)</sup> | FBEh    | ECCP1AS  | F9Eh    | PIR1                   | F7Eh    | BAUDCON1                 |

| FFBhPCLATUFDBhPLUSW2 <sup>(1)</sup> FBBhCCPR1LF9BhOSCTUNEF7BhTMR3HFFAhPCLATHFDAhFSR2HFBAhCCP1CONF9AhT1GCONF7AhTMR3LFF8hPCLFD9hFSR2LFB9hPSTR2CONF99hIPR5F78hTMR3LFF8hTBLPTRUFD8hSTATUSF88hECCP2ASF99hPIR5F78hTMR44FF7hTBLPTRHFD7hTMR0HFB7hECCP2DELF97hT3GCONF77hTMR44FF6hTBLPTRHFD6hTMR0LFB6hCCPR2HF96hTRISEF76hT4CONFF5hTABLATFD6hT0CONFB6hCCPR2LF96hTRISEF76hSSP2BUFFF7hPRODHFD4h6 <sup>(0)</sup> FB4hCCP2CONF94hTRISEF77hSSP2DU <sup>3</sup> FF3hPRODLFD2hCM1CONFB3hCTMUCONLF93hTRISBF73hSSP2CON2FF7hINTCONFD2hCM1CONFB1hCTMUCONLF93hTRISBF73hSSP2CON2FF7hINTCON2FD1hCM2CONFB1hCTMUCONLF93hTRISBF73hSSP2CON2FF7hINTCON3FD0hRCONFB0hSPBRG1F90hIPR4F70hCMSTATFE7hINTCON1FCChTMR1HFAFhRCREG1F87hPIR4F66hPMADDRI(2.4)FE6hPOSTDEC0 <sup>(1)</sup> FCChTMR2FAChRCST11 <td>FFDh</td> <td>TOSL</td> <td>FDDh</td> <td>POSTDEC2<sup>(1)</sup></td> <td>FBDh</td> <td>ECCP1DEL</td> <td>F9Dh</td> <td>PIE1</td> <td>F7Dh</td> <td>SPBRGH2</td>                                                                                                                                                                                                                                                                                                                                                                                                                                             | FFDh    | TOSL                    | FDDh    | POSTDEC2 <sup>(1)</sup> | FBDh    | ECCP1DEL | F9Dh    | PIE1                   | F7Dh    | SPBRGH2                  |

| FFAh         PCLATH         FDAh         FSR2H         FBAh         CCP1CON         F9Ah         T1GCON         F7Ah         TMR3L           FF9h         PCL         FD9h         FSR2L         FB9h         PSTR2CON         F99h         IPR5         F79h         T3CON           FF8h         TBLPTRU         FD8h         STATUS         FB8h         ECCP2AS         F98h         PIR5         F78h         TMR4           FF7h         TBLPTRU         FD8h         STATUS         FB8h         ECCP2AS         F98h         PIR5         F78h         TMR4           FF7h         TBLPTRL         FD6h         TMR0L         FB7h         CCCP2AS         F98h         TRISE         F76h         T3GCON         F77h         PR4           FF6h         TABLAT         FD6h         TMR0L         F86h         CCP2CON         F94h         TRISE         F76h         SSP2BUF           FF4h         PRODL         FD3h         OSCCON         F83h         CTMUCONL         F92h         TRISA         F72h         SSP2CON1           FF1h         INTCON         FD2h         CM1CON         F81h         CTMUCONL         F91h         PIE5         F71h         SSP2CON2                                                                                                                                                                                           | FFCh    | STKPTR                  | FDCh    | PREINC2 <sup>(1)</sup>  | FBCh    | CCPR1H   | F9Ch    | RCSTA2                 | F7Ch    | BAUDCON2                 |

| FF9hPCLFD9hFSR2LFB9hPSTR2CONF99hIPR5F79hT3CONFF8hTBLPTRUFD8hSTATUSFB8hECCP2ASF98hPIR5F78hTMR4FF7hTBLPTRLFD7hTMR0HFB7hECCP2DELF97hT3GCONF77hPR4FF6hTBLPTRLFD8hTMR0LFB6hCCPR2HF96hTRISEF76hT4CONFF6hTABLATFD5hTOCONFB5hCCPR2LF96hTRISEF76hSSP2AD0 <sup>3</sup> FF7hPRODLFD3hOSCCONFB3hCTMUCONLF93hTRISBF77hSSP2AD0 <sup>3</sup> FF7hINTCONFD2hCM1CONFB2hCTMUCONLF99hIPR4F77hSSP2AD0 <sup>3</sup> FF7hINTCONFD2hCM1CONFB1hCTMUCONLF99hIPR4F77hSSP2AD0 <sup>3</sup> FF7hINTCONFD2hCM1CONFB1hCTMUCONLF99hIPR4F77hSSP2AD0 <sup>4</sup> FF7hINTCON2FD1hCM2CONFB1hCTMUCONLF99hIPR4F77hSSP2CON2FF7hINTCON3FD0hRCONFB0hSPBRG1F99hIPR4F6FhPMADDRH <sup>2,4</sup> FE6hPOSTINC0 <sup>(1)</sup> FCChTMR1LFAEhTXREG1F8FhPIR4F6FhPMADDRH <sup>2,4</sup> FE6hPOSTINC0 <sup>(1)</sup> FCChTMR2FAChRCSTA1F80hLATCF66hPMADDRH <sup>2,4</sup> FE6hPREINC0 <sup>(1)</sup> FCChTMR2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | FFBh    | PCLATU                  | FDBh    | PLUSW2 <sup>(1)</sup>   | FBBh    | CCPR1L   | F9Bh    | OSCTUNE                | F7Bh    | TMR3H                    |

| FF8h         TBLPTRU         FD8h         STATUS         FB8h         ECCP2AS         F98h         PIR5         F78h         TMR4           FF7h         TBLPTRH         FD7h         TMR0H         FB7h         ECCP2DEL         F97h         T3GCON         F77h         PR4           FF6h         TBLPTRL         FD6h         TMR0L         FB6h         CCPR2H         F96h         TRISD         F77h         SP22BUF           FF6h         TABLAT         FD5h         TOCON         FB6h         CCPR2L         F98h         TRISD         F75h         SSP2BUF           FF7h         PRODH         FD4h        6''         FB4h         CCP2CON         F94h         TRISD         F77h         SSP2CON2           FF3h         PRODL         FD3h         OSCCON         FB3h         CTMUCONL         F92h         TRISA         F72h         SSP2CON2           FF7h         INTCON2         FD1h         CM2CON         FB1h         CTMUCONL         F92h         TRISA         F72h         SSP2CON2           FF6h         INTCON3         FD0h         RCON         FB0h         SPBRG1         F90h         IPR4         F6h         PMADDRH <sup>(2,4</sup> )           FEEh         IND                                                                                                                                                                     | FFAh    | PCLATH                  | FDAh    | FSR2H                   | FBAh    | CCP1CON  | F9Ah    | T1GCON                 | F7Ah    | TMR3L                    |

| FF7hTBLPTRHFD7hTMR0HFB7hECCP2DELF97hT3GCONF77hPR4FF6hTBLPTRLFD6hTMR0LFB6hCCPR2HF96hTRISEF76hT4CONFF5hTABLATFD5hT0CONFB5hCCPR2LF95hTRISDF77hSSP2BUFFF4hPRODHFD4h6^0FB4hCCP2CONF94hTRISCF74hSSP2AD0 <sup>3</sup> FF3hPRODLFD3hOSCCONFB3hCTMUCONHF93hTRISBF73hSSP2CON1FF1hINTCONFD2hCM1CONFB2hCTMUCONLF93hTRISAF72hSSP2CON1FF1hINTCON2FD1hCM2CONFB1hCTMUCONLF93hTRISAF72hSSP2CON1FF6hINTCON3FD0hRCONFB1hCTMUCONF91hPIE5F71hSSP2CON2FF6hINTCON3FD0hRCONFB0hSPBRG1F90hIPR4F66hPMADDRH <sup>(2,4)</sup> FEEhINDF0 <sup>(1)</sup> FCFhTMR1LFAEhTXREG1F86hPIE4F66hPMDIN14 <sup>(2,4)</sup> FEEhPOSTINC0 <sup>(1)</sup> FCChTMR2FAChRCSTA1F80hLATCF60hPMDIN14 <sup>(2,4)</sup> FEEhPREINC0 <sup>(1)</sup> FCChTMR2FAChRCSTA1F80hLATCF60hPMDIN14 <sup>(2,4)</sup> FEEhPOSTINC0 <sup>(1)</sup> FCChTMR2FAChRCSTA1F80hLATCF60hPMDIN14 <sup>(2,4)</sup> FEEhPREINC0 <sup>(1)</sup> FCCh </td <td>FF9h</td> <td>PCL</td> <td>FD9h</td> <td>FSR2L</td> <td>FB9h</td> <td>PSTR2CON</td> <td>F99h</td> <td>IPR5</td> <td>F79h</td> <td>T3CON</td>                                                                                                                                                                                                                                                                                                                                                   | FF9h    | PCL                     | FD9h    | FSR2L                   | FB9h    | PSTR2CON | F99h    | IPR5                   | F79h    | T3CON                    |

| FF6hTBLPTRLFD6hTMR0LFB6hCCPR2HF96hTRISEF76hT4CONFF5hTABLATFD5hT0CONFB5hCCPR2LF95hTRISDF75hSSP2BUFFF4hPRODHFD4h(6)FB4hCCP2CONF94hTRISCF74hSSP2ADD(3)FF3hPRODLFD3hOSCCONFB3hCTMUCONHF93hTRISBF73hSSP2STATFF2hINTCONFD2hCM1CONFB2hCTMUCONLF92hTRISAF72hSSP2CON1FF1hINTCON2FD1hCM2CONFB1hCTMUCONLF91hPIE5F71hSSP2CON2FF0hINTCON3FD0hRCONFB0hSPBRG1F90hIPR4F70hCMTATFE6hINDF0f0FCFhTMR1HFAFhRCREG1F8FhPIR4F6fhPMADDRH <sup>(2,4)</sup> FE6hPOSTINC0f0FCChTMR1LFAChTXSTA1F80hLATE <sup>(2)</sup> F6DhPMDIN1H <sup>(2)</sup> FE6hPREINC0f0FCChTMR2FAChRCSTA1F80hLATCF68hPMDIN1H <sup>(2)</sup> FE6hPREINC0f0FCChTMR2FAChRCSTA1F80hLATCF68hTXADDRLFE6hPREINC0f0FCChTMR2FAChRCSTA1F80hLATCF68hTXADDRLFE6hPSR0LFCAhT2CONFAAhRCREG2F88hLATCF68hTXADDRLFE8hPLUSW0 <sup>(1)</sup> FCAhT2CONFAAh<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | FF8h    | TBLPTRU                 | FD8h    | STATUS                  | FB8h    | ECCP2AS  | F98h    | PIR5                   | F78h    | TMR4                     |

| FFshTABLATFDshTOCONFBshCCPR2LF9shTRISDF75hSSP2BUFFF4hPRODHFD4h(5)FB4hCCP2CONF94hTRISCF74hSSP2ADD(3)FF3hPRODLFD3hOSCCONFB3hCTMUCONHF93hTRISBF73hSSP2STATFF2hINTCONFD2hCM1CONFB2hCTMUCONLF92hTRISAF72hSSP2CON1FF1hINTCON2FD1hCM2CONFB1hCTMUICONF91hPIE5F71hSSP2CON2FF0hINTCON3FD0hRCONFB0hSPBRG1F90hIPR4F70hCMSTATFEFhINDF0(1)FCFhTMR1HFAFhRCREG1F8FhPIE4F66hPMADDRI(2.4)FEChPOSTINC0(1)FCEhTMR1LFAEhTXREG1F8EhPIE4F66hPMADDRI(2.4)FEChPREINC0(1)FCChTMR2FAChRCSTA1F8ChLATE(2)F60hPMDIN1L(2)FEBhPLISW0(1)FCChTMR2FAChRCREG2F88hLATCF68hTXADDRLFEAhFSR0LFCAhT2CONFAAhRCREG2F88hLATAF69hRXADDRLFE8hPLISW0(1)FCAhT2CONFAAhRCREG2F88hLATAF69hRXADDRLFE8hPSR0LFCAhT2CONFAAhTXSTA2F88hDMACON1F68hRXADDRLFE8hPSR0LFCAhSSP1ADD(3)FA8h<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | FF7h    | TBLPTRH                 | FD7h    | TMR0H                   | FB7h    | ECCP2DEL | F97h    | T3GCON                 | F77h    | PR4                      |

| FF4hPRODHFD4h(5)FB4hCCP2CONF94hTRISCF74hSSP2ADD(3)FF3hPRODLFD3hOSCCONFB3hCTMUCONHF93hTRISBF73hSSP2STATFF2hINTCONFD2hCM1CONFB2hCTMUCONLF92hTRISAF72hSSP2CON1FF1hINTCON2FD1hCM2CONFB1hCTMUCONLF92hTRISAF72hSSP2CON2FF0hINTCON3FD0hRCONFB0hSPBRG1F90hIPR4F70hCMSTATFEFhINDF0 <sup>(1)</sup> FCFhTMR1HFAFhRCREG1F8FhPIR4F6FhPMADDRI <sup>(2,4)</sup> FEChPOSTIDC0 <sup>(1)</sup> FCChTMR1LFAChTXREG1F8EhPIE4F66hPMADDRI <sup>(2,4)</sup> FEChPREINC0 <sup>(1)</sup> FCChTMR2FAChRCSTA1F8ChLATE <sup>(2)</sup> F60hPMDIN14 <sup>(2)</sup> FEChPREINC0 <sup>(1)</sup> FCChTMR2FAChRCSTA1F8chLATCF68hTXADDRLFEAhFSR0HFCAhT2CONFAAhRCREG2F88hLATAF68hTXADDRLFEAhFSR0LFCAhSSP1ADD <sup>(3)</sup> FA8hTXSTA2F88hDMACON1F68hRXADDRLFE8hPOSTIDC1 <sup>(1)</sup> FCAhSSP1ADD <sup>(3)</sup> FA8hTXSTA2F88hDMACON1F68hRXADDRLFE8hPOSTIDC1 <sup>(1)</sup> FCAhSSP1ADD <sup>(3)</sup> FA8hTXSTA2F88hDMACON1F68hRXADDRLFE8hP                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | FF6h    | TBLPTRL                 | FD6h    | TMR0L                   | FB6h    | CCPR2H   | F96h    | TRISE                  | F76h    | T4CON                    |

| Fr3hPRODLFD3hOSCCONFB3hCTMUCONHF93hTRISBF73hSSP2STATFF3hNTCONFD2hCM1CONFB3hCTMUCONHF93hTRISBF73hSSP2STATFF1hINTCON2FD1hCM2CONFB1hCTMUCONLF92hTRISAF72hSSP2CON1FF1hINTCON3FD0hRCONFB1hCTMUCONF91hPIE5F71hSSP2CON1FF6hINTCON3FD0hRCONFB0hSPBRG1F90hIPR4F70hCMSTATFEFhINDF0 <sup>(1)</sup> FCFhTMR1HFAFhRCREG1F8FhPIR4F6FhPMADDRH <sup>(2,4)</sup> FE6hPOSTDEC0 <sup>(1)</sup> FCChTMR2FAChRCSTA1F80hLATE <sup>(2)</sup> F60hPMDIN1H <sup>(2)</sup> FE6hPOSTDEC0 <sup>(1)</sup> FCChTMR2FAChRCSTA1F8chLATE <sup>(2)</sup> F6ChPMDIN1L <sup>(2)</sup> FE6hPEINC0 <sup>(1)</sup> FCChTMR2FAAhRCREG2F88hLATCF68hTXADDRLFEAhFSR0HFCAhT2CONFAAhRCREG2F88hLATAF69hRXADDRLFE8hVREGFC8hSSP18UFFA9hTXREG2F88hLATAF69hRXADDRLFE8hWREGFC8hSSP13TTFA7hEECON2F87hOSCCON2 <sup>(6)</sup> F67hDMABCLFE8hWREGFC8hSSP1CON1FA8hTXSTA2F88hDMACON1F68hRXADDRLFE8hPOSTDEC1 <sup>(1)</sup> FC7h <td< td=""><td>FF5h</td><td>TABLAT</td><td>FD5h</td><td>TOCON</td><td>FB5h</td><td>CCPR2L</td><td>F95h</td><td>TRISD</td><td>F75h</td><td>SSP2BUF</td></td<>                                                                                                                                                                                                                                                                                                                                                | FF5h    | TABLAT                  | FD5h    | TOCON                   | FB5h    | CCPR2L   | F95h    | TRISD                  | F75h    | SSP2BUF                  |

| FF2hINTCONFD2hCM1CONFB2hCTMUCONLF92hTRISAF72hSSP2CON1FF1hINTCON2FD1hCM2CONFB1hCTMUICONF91hPIE5F71hSSP2CON2FF0hINTCON3FD0hRCONFB0hSPBRG1F90hIPR4F70hCMSTATFEFhINDF0 <sup>(1)</sup> FCFhTMR1HFAFhRCREG1F8FhPIR4F6FhPMADDRH <sup>(2,4)</sup> FEbhPOSTDEC0 <sup>(1)</sup> FCChTMR1LFAEhTXREG1F8EhPIE4F6EhPMADDRL <sup>(2,4)</sup> FEbhPOSTDEC0 <sup>(1)</sup> FCChT1CONFADhTXSTA1F8DhLATE <sup>(2)</sup> F6ChPMDIN1H <sup>(2)</sup> FEChPREINC0 <sup>(1)</sup> FCChTMR2FAChRCSTA1F8ChLATD <sup>(2)</sup> F6ChPMDIN1L <sup>(2)</sup> FEBhPLUSW0 <sup>(1)</sup> FCBhPR2FABhSPBRG2F8BhLATCF6BhTXADDRLFEAhFSR0LFC9hSSP1BUFFA9hTXREG2F89hLATAF69hRXADDRLFE8hWREGFC8hSSP1AD0 <sup>(3)</sup> FA8hTXSTA2F88hDMACON1F68hRXADDRLFE6hPOSTIDC1 <sup>(1)</sup> FC7hSSP1CON2FA5hIPR3F86hDMACON2F66hDMABCLFE6hPOSTIDC1 <sup>(1)</sup> FC6hSSP1CON2FA5hIPR3F86hDMACON2F66hDMABCLFE6hPOSTIDC1 <sup>(1)</sup> FC6hSSP1CON2FA5hIPR3F86hDMACON2F66hDMABCLFE6h <t< td=""><td>FF4h</td><td>PRODH</td><td>FD4h</td><td>(5)</td><td>FB4h</td><td>CCP2CON</td><td>F94h</td><td>TRISC</td><td>F74h</td><td>SSP2ADD<sup>(3)</sup></td></t<>                                                                                                                                                                                                                                                                       | FF4h    | PRODH                   | FD4h    | (5)                     | FB4h    | CCP2CON  | F94h    | TRISC                  | F74h    | SSP2ADD <sup>(3)</sup>   |

| FF1hINTCON2FD1hCM2CONFB1hCTMUICONF91hPIE5F71hSSP2CON2FF0hINTCON3FD0hRCONFB0hSPBRG1F90hIPR4F70hCMSTATFEFhINDF0 <sup>(1)</sup> FCFhTMR1HFAFhRCREG1F8FhPIR4F6FhPMADDRH <sup>(2,4)</sup> FEEhPOSTDEC0 <sup>(1)</sup> FCChTMR1LFAFhRCREG1F8FhPIR4F6EhPMADDRL <sup>(2,4)</sup> FEChPOSTDEC0 <sup>(1)</sup> FCChTMR1LFAChTXSTA1F8DhLATE <sup>(2)</sup> F6ChPMDIN1H <sup>(2)</sup> FEChPREINC0 <sup>(1)</sup> FCChTMR2FAChRCSTA1F8ChLATD <sup>(2)</sup> F6ChPMDIN1L <sup>(2)</sup> FEChPREINC0 <sup>(1)</sup> FCChTMR2FAChRCSTA1F8ChLATCF6BhPMDIN1L <sup>(2)</sup> FEBhPLUSW0 <sup>(1)</sup> FCBhPR2FABhSPBRG2F8BhLATCF6BhTXADDRLFEAhFSR0LFCAhT2CONFAAhRCREG2F8AhLATBF6AhTXADDRLFE8hWREGFC8hSSP1ADD <sup>(3)</sup> FA8hTXSTA2F88hDMACON1F68hRXADDRLFE8hPOSTINC1 <sup>(1)</sup> FC7hSSP1STATFA7hEECON2F87hOSCCON2 <sup>(6)</sup> F67hDMABCLFE6hPOSTINC1 <sup>(1)</sup> FC6hSSP1CON1FA6hEECON1F86hDMACON2F66hDMABCHFE6hPOSTINC1 <sup>(1)</sup> FC6hSSP1CON2FA5hIPR3F85hHLVDCONF65hUCONF                                                                                                                                                                                                                                                                                                                                                                                                      | FF3h    | PRODL                   | FD3h    | OSCCON                  | FB3h    | CTMUCONH | F93h    | TRISB                  | F73h    | SSP2STAT                 |

| FF0hINTCON3FD0hRCONFB0hSPBRG1F90hIPR4F70hCMSTATFEFhINDF0 <sup>(1)</sup> FCFhTMR1HFAFhRCREG1F8FhPIR4F6FhPMADDRH <sup>(2,4)</sup> FEEhPOSTINC0 <sup>(1)</sup> FCChTMR1LFAEhTXREG1F8EhPIE4F6EhPMADDRL <sup>(2,4)</sup> FEDhPOSTDEC0 <sup>(1)</sup> FCChT1CONFADhTXSTA1F8DhLATE <sup>(2)</sup> F6ChPMDIN1H <sup>(2)</sup> FEChPREINC0 <sup>(1)</sup> FCChTMR2FAChRCSTA1F8ChLATD <sup>(2)</sup> F6ChPMDIN1L <sup>(2)</sup> FEBhPLUSW0 <sup>(1)</sup> FCBhPR2FABhSPBRG2F8BhLATCF6BhTXADDRLFEAhFSR0HFCAhT2CONFAAhRCREG2F8AhLATBF6AhTXADDRLFE8hWREGFC8hSSP18UFFA9hTXREG2F89hLATAF69hRXADDRHFE7hINDF1 <sup>(1)</sup> FC7hSSP18TATFA7hEECON2F87hOSCCON2 <sup>(5)</sup> F67hDMABCLFE6hPOSTINC1 <sup>(1)</sup> FC6hSSP1CON1FA6hEECON1F86hDMACON2F66hDMABCHFE6hPOSTDEC1 <sup>(1)</sup> FC6hSSP1CON2FA5hIPR3F65hHLVDCONF65hUCONFE6hPOSTDEC1 <sup>(1)</sup> FC6hSSP1CON2FA5hIPR3F65hHLVDCONF65hUCONFE6hPOSTDEC1 <sup>(1)</sup> FC6hSSP1CON2FA5hIPR3F65hHLVDCONF65hUCONFE6h <t< td=""><td>FF2h</td><td>INTCON</td><td>FD2h</td><td>CM1CON</td><td>FB2h</td><td>CTMUCONL</td><td>F92h</td><td>TRISA</td><td>F72h</td><td>SSP2CON1</td></t<>                                                                                                                                                                                                                                                         | FF2h    | INTCON                  | FD2h    | CM1CON                  | FB2h    | CTMUCONL | F92h    | TRISA                  | F72h    | SSP2CON1                 |

| FEFhINDF0 <sup>(1)</sup> FCFhTMR1HFAFhRCREG1F8FhPIR4F6FhPMADDRH <sup>(2,4)</sup> FEEhPOSTINC0 <sup>(1)</sup> FCEhTMR1LFAEhTXREG1F8EhPIE4F6EhPMADDRL <sup>(2,4)</sup> FEDhPOSTDEC0 <sup>(1)</sup> FCDhT1CONFADhTXSTA1F8DhLATE <sup>(2)</sup> F6DhPMDIN1H <sup>(2)</sup> FEChPREINC0 <sup>(1)</sup> FCChTMR2FAChRCSTA1F8ChLATD <sup>(2)</sup> F6ChPMDIN1L <sup>(2)</sup> FEBhPLUSW0 <sup>(1)</sup> FCBhPR2FABhSPBRG2F8BhLATCF6BhTXADDRLFEAhFSR0HFCAhT2CONFAAhRCREG2F8AhLATBF6AhTXADDRLFE9hFSR0LFC9hSSP18UFFA9hTXREG2F89hLATAF69hRXADDRHFE8hWREGFC8hSSP1ADD <sup>(3)</sup> FA8hTXSTA2F88hDMACON1F68hRXADDRHFE7hINDF1 <sup>(1)</sup> FC7hSSP1STATFA7hEECON2F87hOSCCON2 <sup>(5)</sup> F67hDMABCLFE6hPOSTINC1 <sup>(1)</sup> FC6hSSP1CON1FA6hEECON1F86hDMACON2F66hDMABCHFE4hPREINC1 <sup>(1)</sup> FC6hSSP1CON2FA5hIPR3F85hHLVDCONF66hUCONFE4hPREINC1 <sup>(1)</sup> FC6hADRESHFA4hPIR3F84hPORTE <sup>(2)</sup> F64hUSTATFE3hPLUSW1 <sup>(1)</sup> FC3hADRESLFA3hPIE3F83hPORTCF63hUEIRFE3h <td>FF1h</td> <td>INTCON2</td> <td>FD1h</td> <td>CM2CON</td> <td>FB1h</td> <td>CTMUICON</td> <td>F91h</td> <td>PIE5</td> <td>F71h</td> <td>SSP2CON2</td>                                                                                                                                                                                                                                     | FF1h    | INTCON2                 | FD1h    | CM2CON                  | FB1h    | CTMUICON | F91h    | PIE5                   | F71h    | SSP2CON2                 |

| FEEhPOSTINCO <sup>(1)</sup> FCEhTMR1LFAEhTXREG1F8EhPIE4F6EhPMADDRL <sup>(2,4)</sup> FEDhPOSTDECO <sup>(1)</sup> FCDhT1CONFADhTXSTA1F8DhLATE <sup>(2)</sup> F6DhPMDIN1H <sup>(2)</sup> FEChPREINCO <sup>(1)</sup> FCChTMR2FAChRCSTA1F8ChLATD <sup>(2)</sup> F6ChPMDIN1L <sup>(2)</sup> FEBhPLUSW0 <sup>(1)</sup> FCBhPR2FABhSPBRG2F8BhLATCF6BhTXADDRLFEAhFSR0HFCAhT2CONFAAhRCREG2F8AhLATBF6AhTXADDRLFE9hFSR0LFC9hSSP1BUFFA9hTXREG2F89hLATAF69hRXADDRLFE8hWREGFC8hSSP1ADD <sup>(3)</sup> FA8hTXSTA2F88hDMACON1F68hRXADDRLFE7hINDF1 <sup>(1)</sup> FC7hSSP1STATFA7hEECON2F87hOSCCON2 <sup>(5)</sup> F67hDMABCLFE6hPOSTDEC1 <sup>(1)</sup> FC6hSSP1CON1FA6hEECON1F86hDMACON2F66hDMABCHFE3hPOSTDEC1 <sup>(1)</sup> FC3hADRESLFA3hPIE3F83hPORTE <sup>(2)</sup> F63hUEIRFE2hFSR1HFC2hADCON0FA2hIPR2F81hPORTEF61hUFRMH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | FF0h    | INTCON3                 | FD0h    | RCON                    | FB0h    | SPBRG1   | F90h    | IPR4                   | F70h    | CMSTAT                   |

| FEDhPOSTDEC0 <sup>(1)</sup> FCDhT1CONFADhTXSTA1F8DhLATE <sup>(2)</sup> F6DhPMDIN1H <sup>(2)</sup> FEChPREINC0 <sup>(1)</sup> FCChTMR2FAChRCSTA1F8ChLATD <sup>(2)</sup> F6ChPMDIN1L <sup>(2)</sup> FEBhPLUSW0 <sup>(1)</sup> FCBhPR2FABhSPBRG2F8BhLATCF6BhTXADDRLFEAhFSR0HFCAhT2CONFAAhRCREG2F8AhLATBF6AhTXADDRHFE9hFSR0LFC9hSSP1BUFFA9hTXREG2F89hLATAF69hRXADDRHFE8hWREGFC8hSSP1ADD <sup>(3)</sup> FA8hTXSTA2F88hDMACON1F68hRXADDRHFE7hINDF1 <sup>(1)</sup> FC7hSSP1STATFA7hEECON2F87hOSCCON2 <sup>(5)</sup> F67hDMABCLFE6hPOSTDEC1 <sup>(1)</sup> FC6hSSP1CON1FA6hEECON1F86hDMACON2F66hDMABCHFE5hPOSTDEC1 <sup>(1)</sup> FC3hSSP1CON2FA3hIPR3F83hHLVDCONF65hUCONFE4hPREINC1 <sup>(1)</sup> FC4hADRESHFA4hPIR3F83hPORTD <sup>(2)</sup> F64hUSTATFE2hFSR1HFC2hADCON0FA2hIPR2F81hPORTCF62hUIRFE1hFSR1LFC1hADCON1FA1hPIR2F81hPORTBF61hUFRMH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | FEFh    | INDF0 <sup>(1)</sup>    | FCFh    | TMR1H                   | FAFh    | RCREG1   | F8Fh    | PIR4                   | F6Fh    | PMADDRH <sup>(2,4)</sup> |

| FEChPREINCO(1)FCChTMR2FAChRCSTA1F8ChLATD(2)F6ChPMDIN1L(2)FEBhPLUSW0(1)FCBhPR2FABhSPBRG2F8BhLATCF6BhTXADDRLFEAhFSR0HFCAhT2CONFAAhRCREG2F8AhLATBF6AhTXADDRHFE9hFSR0LFC9hSSP1BUFFA9hTXREG2F89hLATAF69hRXADDRLFE8hWREGFC8hSSP1ADD(3)FA8hTXSTA2F88hDMACON1F68hRXADDRHFE7hINDF1(1)FC7hSSP1STATFA7hEECON2F87hOSCCON2(5)F67hDMABCLFE6hPOSTINC1(1)FC6hSSP1CON1FA6hEECON1F86hDMACON2F66hDMABCHFE5hPOSTDEC1(1)FC5hSSP1CON2FA5hIPR3F85hHLVDCONF65hUCONFE4hPREINC1(1)FC3hADRESLFA3hPIE3F83hPORTD(2)F63hUEIRFE2hFSR1HFC2hADCON0FA2hIPR2F81hPORTBF61hUFRMHFE1hFSR1LFC1hADCON1FA1hPIR2F81hPORTBF61hUFRMH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | FEEh    | POSTINC0 <sup>(1)</sup> | FCEh    | TMR1L                   | FAEh    | TXREG1   | F8Eh    | PIE4                   | F6Eh    | PMADDRL <sup>(2,4)</sup> |

| FEBhPLUSW0 <sup>(1)</sup> FCBhPR2FABhSPBRG2F8BhLATCF6BhTXADDRLFEAhFSR0HFCAhT2CONFAAhRCREG2F8AhLATBF6AhTXADDRHFE9hFSR0LFC9hSSP1BUFFA9hTXREG2F89hLATAF69hRXADDRLFE8hWREGFC8hSSP1ADD <sup>(3)</sup> FA8hTXSTA2F88hDMACON1F68hRXADDRHFE7hINDF1 <sup>(1)</sup> FC7hSSP1STATFA7hEECON2F87hOSCCON2 <sup>(5)</sup> F67hDMABCLFE6hPOSTINC1 <sup>(1)</sup> FC6hSSP1CON1FA6hEECON1F86hDMACON2F66hDMABCHFE5hPOSTDEC1 <sup>(1)</sup> FC5hSSP1CON2FA5hIPR3F85hHLVDCONF65hUCONFE4hPREINC1 <sup>(1)</sup> FC3hADRESHFA3hPIE3F83hPORTD <sup>(2)</sup> F63hUEIRFE2hFSR1HFC2hADCON0FA2hIPR2F81hPORTBF61hUFRMHFE1hFSR1LFC1hADCON1FA1hPIR2F81hPORTBF61hUFRMH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | FEDh    | POSTDEC0 <sup>(1)</sup> | FCDh    | T1CON                   | FADh    | TXSTA1   | F8Dh    | LATE <sup>(2)</sup>    | F6Dh    | PMDIN1H <sup>(2)</sup>   |

| FEAhFSR0HFCAhT2CONFAAhRCREG2F8AhLATBF6AhTXADDRHFE9hFSR0LFC9hSSP1BUFFA9hTXREG2F89hLATAF69hRXADDRLFE8hWREGFC8hSSP1ADD <sup>(3)</sup> FA8hTXSTA2F88hDMACON1F68hRXADDRHFE7hINDF1 <sup>(1)</sup> FC7hSSP1STATFA7hEECON2F87hOSCCON2 <sup>(5)</sup> F67hDMABCLFE6hPOSTINC1 <sup>(1)</sup> FC6hSSP1CON1FA6hEECON1F86hDMACON2F66hDMABCHFE5hPOSTDEC1 <sup>(1)</sup> FC5hSSP1CON2FA5hIPR3F85hHLVDCONF65hUCONFE4hPREINC1 <sup>(1)</sup> FC4hADRESHFA4hPIR3F84hPORTE <sup>(2)</sup> F64hUSTATFE3hPLUSW1 <sup>(1)</sup> FC3hADRESLFA3hPIE3F83hPORTD <sup>(2)</sup> F63hUEIRFE2hFSR1HFC2hADCON0FA2hIPR2F82hPORTCF62hUIRFE1hFSR1LFC1hADCON1FA1hPIR2F81hPORTBF61hUFRMH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | FECh    | PREINC0 <sup>(1)</sup>  | FCCh    | TMR2                    | FACh    | RCSTA1   | F8Ch    | LATD <sup>(2)</sup>    | F6Ch    | PMDIN1L <sup>(2)</sup>   |

| FE9hFSR0LFC9hSSP1BUFFA9hTXREG2F89hLATAF69hRXADDRLFE8hWREGFC8hSSP1ADD <sup>(3)</sup> FA8hTXSTA2F88hDMACON1F68hRXADDRHFE7hINDF1 <sup>(1)</sup> FC7hSSP1STATFA7hEECON2F87hOSCCON2 <sup>(5)</sup> F67hDMABCLFE6hPOSTINC1 <sup>(1)</sup> FC6hSSP1CON1FA6hEECON1F86hDMACON2F66hDMABCHFE5hPOSTDEC1 <sup>(1)</sup> FC5hSSP1CON2FA5hIPR3F85hHLVDCONF65hUCONFE4hPREINC1 <sup>(1)</sup> FC4hADRESHFA4hPIR3F84hPORTE <sup>(2)</sup> F64hUSTATFE3hPLUSW1 <sup>(1)</sup> FC3hADRESLFA3hPIE3F83hPORTD <sup>(2)</sup> F63hUEIRFE2hFSR1HFC2hADCON0FA2hIPR2F82hPORTCF62hUIRFE1hFSR1LFC1hADCON1FA1hPIR2F81hPORTBF61hUFRMH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | FEBh    | PLUSW0 <sup>(1)</sup>   | FCBh    | PR2                     | FABh    | SPBRG2   | F8Bh    | LATC                   | F6Bh    | TXADDRL                  |

| FE8hWREGFC8hSSP1ADD(3)FA8hTXSTA2F88hDMACON1F68hRXADDRHFE7hINDF1(1)FC7hSSP1STATFA7hEECON2F87hOSCCON2(5)F67hDMABCLFE6hPOSTINC1(1)FC6hSSP1CON1FA6hEECON1F86hDMACON2F66hDMABCHFE5hPOSTDEC1(1)FC5hSSP1CON2FA5hIPR3F85hHLVDCONF65hUCONFE4hPREINC1(1)FC4hADRESHFA4hPIR3F84hPORTE(2)F64hUSTATFE3hPLUSW1(1)FC3hADRESLFA3hPIE3F83hPORTD(2)F63hUEIRFE2hFSR1HFC2hADCON0FA2hIPR2F82hPORTCF62hUIRFE1hFSR1LFC1hADCON1FA1hPIR2F81hPORTBF61hUFRMH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | FEAh    | FSR0H                   | FCAh    | T2CON                   | FAAh    | RCREG2   | F8Ah    | LATB                   | F6Ah    | TXADDRH                  |

| FE7hINDF1(1)FC7hSSP1STATFA7hEECON2F87hOSCCON2(5)F67hDMABCLFE6hPOSTINC1(1)FC6hSSP1CON1FA6hEECON1F86hDMACON2F66hDMABCHFE5hPOSTDEC1(1)FC5hSSP1CON2FA5hIPR3F85hHLVDCONF65hUCONFE4hPREINC1(1)FC4hADRESHFA4hPIR3F84hPORTE(2)F64hUSTATFE3hPLUSW1(1)FC3hADRESLFA3hPIE3F83hPORTD(2)F63hUEIRFE2hFSR1HFC2hADCON0FA2hIPR2F82hPORTCF62hUIRFE1hFSR1LFC1hADCON1FA1hPIR2F81hPORTBF61hUFRMH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | FE9h    | FSR0L                   | FC9h    | SSP1BUF                 | FA9h    | TXREG2   | F89h    | LATA                   | F69h    | RXADDRL                  |