#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2000                       |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 48MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART, USB                              |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 22                                                                          |

| Program Memory Size        | 128KB (64K x 16)                                                            |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 3.8K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 2.75V                                                                  |

| Data Converters            | A/D 10x10b/12b                                                              |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                              |

| Supplier Device Package    | 28-SSOP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf27j53-i-ss |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 2.4 Voltage Regulator Pins (VCAP/VDDCORE)

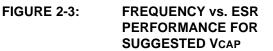

On "F" devices, a low-ESR (< 5 $\Omega$ ) capacitor is required on the VCAP/VDDCORE pin to stabilize the voltage regulator output voltage. The VCAP/VDDCORE pin must not be connected to VDD and must use a capacitor of 10  $\mu$ F connected to ground. The type can be ceramic or tantalum. A suitable example is the Murata GRM21BF50J106ZE01 (10  $\mu$ F, 6.3V) or equivalent. Designers may use Figure 2-3 to evaluate ESR equivalence of candidate devices.

It is recommended that the trace length not exceed 0.25 inch (6 mm). Refer to **Section 31.0** "**Electrical Characteristics**" for additional information.

On "LF" devices, the VCAP/VDDCORE pin must be tied to a voltage supply at the VDDCORE level. Refer to **Section 31.0** "**Electrical Characteristics**" for information on VDD and VDDCORE.

Note that the "LF" versions of these devices are provided with the voltage regulator permanently disabled; they must always be provided with a supply voltage on the VDDCORE pin.

## 2.5 ICSP Pins

The PGC and PGD pins are used for In-Circuit Serial Programming<sup>TM</sup> (ICSP<sup>TM</sup>) and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of ohms, not to exceed 100 $\Omega$ .

Pull-up resistors, series diodes, and capacitors on the PGC and PGD pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits, and pin input voltage high (VIH) and input low (VIL) requirements.

For device emulation, ensure that the "Communication Channel Select" (i.e., PGCx/PGDx pins) programmed into the device matches the physical connections for the ICSP to the Microchip debugger/emulator tool.

For more information on available Microchip development tools connection requirements, refer to **Section 30.0 "Development Support"**.

## 2.6 External Oscillator Pins

Many microcontrollers have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator (refer to **Section 3.0 "Oscillator Configurations"** for details).

The oscillator circuit should be placed on the same side of the board as the device. Place the oscillator circuit close to the respective oscillator pins with no more than 0.5 inch (12 mm) between the circuit components and the pins. The load capacitors should be placed next to the oscillator itself, on the same side of the board.

Use a grounded copper pour around the oscillator circuit to isolate it from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed.

Layout suggestions are shown in Figure 2-4. In-line packages may be handled with a single-sided layout that completely encompasses the oscillator pins. With fine-pitch packages, it is not always possible to completely surround the pins and components. A suitable solution is to tie the broken guard sections to a mirrored ground layer. In all cases, the guard trace(s) must be returned to ground.

In planning the application's routing and I/O assignments, ensure that adjacent port pins and other signals in close proximity to the oscillator are benign (i.e., free of high frequencies, short rise and fall times, and other similar noise).

For additional information and design guidance on oscillator circuits, please refer to these Microchip Application Notes, available at the corporate website (www.microchip.com):

- AN826, Crystal Oscillator Basics and Crystal Selection for rfPIC<sup>™</sup> and PICmicro<sup>®</sup> Devices

- AN849, Basic PICmicro<sup>®</sup> Oscillator Design

- AN943, Practical PICmicro<sup>®</sup> Oscillator Analysis and Design

- AN949, Making Your Oscillator Work

## 2.7 Unused I/Os

Unused I/O pins should be configured as outputs and driven to a logic low state. Alternatively, connect a 1 k $\Omega$  to 10 k $\Omega$  resistor to Vss on unused pins and drive the output to logic low.

#### FIGURE 2-4: SUGGESTED PLACEMENT OF THE OSCILLATOR CIRCUIT

#### 3.2.5.1 OSCTUNE Register

The internal oscillator's output has been calibrated at the factory but can be adjusted in the user's application. This is done by writing to the OSCTUNE register (Register 3-1). The tuning sensitivity is constant throughout the tuning range.

When the OSCTUNE register is modified, the INTOSC frequency will begin shifting to the new frequency. The INTOSC clock will stabilize typically within 1  $\mu$ s. Code execution continues during this shift. There is no indication that the shift has occurred.

The OSCTUNE register also contains the INTSRC bit. The INTSRC bit allows users to select which internal oscillator provides the clock source when the 31 kHz frequency option is selected. This is covered in larger detail in **Section 3.5.1 "Oscillator Control Register"**.

The PLLEN bit, contained in the OSCTUNE register, can be used to enable or disable the internal 96 MHz PLL when running in one of the PLL type oscillator modes (e.g., INTOSCPLL). Oscillator modes that do not contain "PLL" in their name cannot be used with the PLL. In these modes, the PLL is always disabled regardless of the setting of the PLLEN bit.

When configured for one of the PLL enabled modes, setting the PLLEN bit does not immediately switch the device clock to the PLL output. The PLL requires up to electrical parameter,  $t_{rc}$ , to start-up and lock, during which time, the device continues to be clocked. Once the PLL output is ready, the microcontroller core will automatically switch to the PLL derived frequency.

#### 3.2.5.2 Internal Oscillator Output Frequency and Drift

The internal oscillator block is calibrated at the factory to produce an INTOSC output frequency of 8.0 MHz. However, this frequency may drift as VDD or temperature changes, which can affect the controller operation in a variety of ways.

The low-frequency INTRC oscillator operates independently of the INTOSC source. Any changes in INTOSC across voltage and temperature are not necessarily reflected by changes in INTRC and vice versa.

#### 3.2.5.3 Compensating for INTOSC Drift

It is possible to adjust the INTOSC frequency by modifying the value in the OSCTUNE register. This has no effect on the INTRC clock source frequency.

Tuning the INTOSC source requires knowing when to make the adjustment, in which direction it should be made and in some cases, how large a change is needed. When using the EUSART, for example, an adjustment may be required when it begins to generate framing errors or receives data with errors while in Asynchronous mode. Framing errors indicate that the device clock frequency is too high; to adjust for this, decrement the value in OSCTUNE to reduce the clock frequency. On the other hand, errors in data may suggest that the clock speed is too low; to compensate, increment OSCTUNE to increase the clock frequency.

It is also possible to verify device clock speed against a reference clock. Two timers may be used: one timer is clocked by the peripheral clock, while the other is clocked by a fixed reference source, such as the Timer1 oscillator. Both timers are cleared, but the timer clocked by the reference generates interrupts. When an interrupt occurs, the internally clocked timer is read and both timers are cleared. If the internally clocked timer value is greater than expected, then the internal oscillator block is running too fast. To adjust for this, decrement the OSCTUNE register.

Finally, an ECCP module can use free-running Timer1 (or Timer3), clocked by the internal oscillator block and an external event with a known period (i.e., AC power frequency). The time of the first event is captured in the CCPRxH:CCPRxL registers and is recorded for use later. When the second event causes a capture, the time of the first event is subtracted from the time of the second event. Since the period of the external event is known, the time difference between events can be calculated.

If the measured time is greater than the calculated time, the internal oscillator block is running too fast; to compensate, decrement the OSCTUNE register. If the measured time is less than the calculated time, the internal oscillator block is running too slow; to compensate, increment the OSCTUNE register.

| TABLE 5-2:          | INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED) |             |                                                                |                                                                            |                                 |  |  |  |  |

|---------------------|---------------------------------------------------------|-------------|----------------------------------------------------------------|----------------------------------------------------------------------------|---------------------------------|--|--|--|--|

| Register            | Applicable Devices                                      |             | Power-on Reset,<br>Brown-out Reset,<br>Wake From Deep<br>Sleep | MCLR Resets<br>WDT Reset<br>RESET Instruction<br>Stack Resets<br>CM Resets | Wake-up via WDT<br>or Interrupt |  |  |  |  |

| INDF2               | PIC18F2XJ53                                             | PIC18F4XJ53 | N/A                                                            | N/A                                                                        | N/A                             |  |  |  |  |

| POSTINC2            | PIC18F2XJ53                                             | PIC18F4XJ53 | N/A                                                            | N/A                                                                        | N/A                             |  |  |  |  |

| POSTDEC2            | PIC18F2XJ53                                             | PIC18F4XJ53 | N/A                                                            | N/A                                                                        | N/A                             |  |  |  |  |

| PREINC2             | PIC18F2XJ53                                             | PIC18F4XJ53 | N/A                                                            | N/A                                                                        | N/A                             |  |  |  |  |

| PLUSW2              | PIC18F2XJ53                                             | PIC18F4XJ53 | N/A                                                            | N/A                                                                        | N/A                             |  |  |  |  |

| FSR2H               | PIC18F2XJ53                                             | PIC18F4XJ53 | 0000                                                           | 0000                                                                       | uuuu                            |  |  |  |  |

| FSR2L               | PIC18F2XJ53                                             | PIC18F4XJ53 | xxxx xxxx                                                      | uuuu uuuu                                                                  | uuuu uuuu                       |  |  |  |  |

| STATUS              | PIC18F2XJ53                                             | PIC18F4XJ53 | x xxxx                                                         | u uuuu                                                                     | u uuuu                          |  |  |  |  |

| TMR0H               | PIC18F2XJ53                                             | PIC18F4XJ53 | 0000 0000                                                      | 0000 0000                                                                  | uuuu uuuu                       |  |  |  |  |

| TMR0L               | PIC18F2XJ53                                             | PIC18F4XJ53 | xxxx xxxx                                                      | uuuu uuuu                                                                  | uuuu uuuu                       |  |  |  |  |

| TOCON               | PIC18F2XJ53                                             | PIC18F4XJ53 | 1111 1111                                                      | 1111 1111                                                                  | uuuu uuuu                       |  |  |  |  |

| OSCCON              | PIC18F2XJ53                                             | PIC18F4XJ53 | 0110 qq00                                                      | 0110 qq00                                                                  | 0110 qq0u                       |  |  |  |  |

| CM1CON              | PIC18F2XJ53                                             | PIC18F4XJ53 | 0001 1111                                                      | uuuu uuuu                                                                  | uuuu uuuu                       |  |  |  |  |

| CM2CON              | PIC18F2XJ53                                             | PIC18F4XJ53 | 0001 1111                                                      | uuuu uuuu                                                                  | uuuu uuuu                       |  |  |  |  |

| RCON <sup>(4)</sup> | PIC18F2XJ53                                             | PIC18F4XJ53 | 0-11 11qq                                                      | 0-qq qquu                                                                  | u-qq qquu                       |  |  |  |  |

| TMR1H               | PIC18F2XJ53                                             | PIC18F4XJ53 | xxxx xxxx                                                      | uuuu uuuu                                                                  | uuuu uuuu                       |  |  |  |  |

| TMR1L               | PIC18F2XJ53                                             | PIC18F4XJ53 | xxxx xxxx                                                      | uuuu uuuu                                                                  | uuuu uuuu                       |  |  |  |  |

| T1CON               | PIC18F2XJ53                                             | PIC18F4XJ53 | 0000 0000                                                      | u0uu uuuu                                                                  | uuuu uuuu                       |  |  |  |  |

| TMR2                | PIC18F2XJ53                                             | PIC18F4XJ53 | 0000 0000                                                      | 0000 0000                                                                  | uuuu uuuu                       |  |  |  |  |

| PR2                 | PIC18F2XJ53                                             | PIC18F4XJ53 | 1111 1111                                                      | 1111 1111                                                                  | uuuu uuuu                       |  |  |  |  |

| T2CON               | PIC18F2XJ53                                             | PIC18F4XJ53 | -000 0000                                                      | -000 0000                                                                  | -uuu uuuu                       |  |  |  |  |

| SSP1BUF             | PIC18F2XJ53                                             | PIC18F4XJ53 | xxxx xxxx                                                      | uuuu uuuu                                                                  | uuuu uuuu                       |  |  |  |  |

| SSP1ADD             | PIC18F2XJ53                                             | PIC18F4XJ53 | 0000 0000                                                      | 0000 0000                                                                  | uuuu uuuu                       |  |  |  |  |

| SSP1MSK             | PIC18F2XJ53                                             | PIC18F4XJ53 |                                                                | uuuu uuuu                                                                  | uuuu uuuu                       |  |  |  |  |

| SSP1STAT            | PIC18F2XJ53                                             | PIC18F4XJ53 | 0000 0000                                                      | 0000 0000                                                                  | uuuu uuuu                       |  |  |  |  |

| SSP1CON1            | PIC18F2XJ53                                             | PIC18F4XJ53 | 0000 0000                                                      | 0000 0000                                                                  | uuuu uuuu                       |  |  |  |  |

| SSP1CON2            | PIC18F2XJ53                                             | PIC18F4XJ53 | 0000 0000                                                      | 0000 0000                                                                  | uuuu uuuu                       |  |  |  |  |

| ADRESH              | PIC18F2XJ53                                             | PIC18F4XJ53 | xxxx xxxx                                                      | uuuu uuuu                                                                  | uuuu uuuu                       |  |  |  |  |

| ADRESL              | PIC18F2XJ53                                             | PIC18F4XJ53 | xxxx xxxx                                                      | uuuu uuuu                                                                  | uuuu uuuu                       |  |  |  |  |

| ADCON0              | PIC18F2XJ53                                             | PIC18F4XJ53 | 0000 0000                                                      | 0000 0000                                                                  | uuuu uuuu                       |  |  |  |  |

| ADCON1              | PIC18F2XJ53                                             | PIC18F4XJ53 | 0000 0000                                                      | 0000 0000                                                                  | uuuu uuuu                       |  |  |  |  |

| WDTCON              | PIC18F2XJ53                                             | PIC18F4XJ53 | 1qq0 0000                                                      | 0qq0 0000                                                                  | uqqu uuuu                       |  |  |  |  |

| TABLE 5-2: | INITIALIZATION CONDITIONS FOR ALL REGISTERS ( | CONTINUED) | ) |

|------------|-----------------------------------------------|------------|---|

|            |                                               |            |   |

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition.

- 2: When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

- 3: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

- 4: See Table 5-1 for Reset value for specific condition.

- 5: Not implemented for PIC18F2XJ53 devices.

- 6: Not implemented for "LF" devices.

**Note 1:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware stack.

| TADLE J-2. | INTRALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED) |             |                                                                |                                                                            |                                 |  |  |  |  |

|------------|--------------------------------------------------------|-------------|----------------------------------------------------------------|----------------------------------------------------------------------------|---------------------------------|--|--|--|--|

| Register   | Applicable Devices                                     |             | Power-on Reset,<br>Brown-out Reset,<br>Wake From Deep<br>Sleep | MCLR Resets<br>WDT Reset<br>RESET Instruction<br>Stack Resets<br>CM Resets | Wake-up via WDT<br>or Interrupt |  |  |  |  |

| RPOR5      | PIC18F2XJ53                                            | PIC18F4XJ53 | 0 0000                                                         | 0 0000                                                                     | u uuuu                          |  |  |  |  |

| RPOR4      | PIC18F2XJ53                                            | PIC18F4XJ53 | 0 0000                                                         | 0 0000                                                                     | u uuuu                          |  |  |  |  |

| RPOR3      | PIC18F2XJ53                                            | PIC18F4XJ53 | 0 0000                                                         | 0 0000                                                                     | u uuuu                          |  |  |  |  |

| RPOR2      | PIC18F2XJ53                                            | PIC18F4XJ53 | 0 0000                                                         | 0 0000                                                                     | u uuuu                          |  |  |  |  |

| RPOR1      | PIC18F2XJ53                                            | PIC18F4XJ53 | 0 0000                                                         | 0 0000                                                                     | u uuuu                          |  |  |  |  |

| RPOR0      | PIC18F2XJ53                                            | PIC18F4XJ53 | 0 0000                                                         | 0 0000                                                                     | u uuuu                          |  |  |  |  |

#### TABLE 5-2: INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED)

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition.

**Note 1:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware stack.

2: When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

3: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

4: See Table 5-1 for Reset value for specific condition.

5: Not implemented for PIC18F2XJ53 devices.

6: Not implemented for "LF" devices.

## 7.4 Erasing Flash Program Memory

The minimum erase block is 512 words or 1024 bytes. Only through the use of an external programmer, or through ICSP control, can larger blocks of program memory be bulk erased. Word erase in the Flash array is not supported.

When initiating an erase sequence from the microcontroller itself, a block of 1024 bytes of program memory is erased. The Most Significant 12 bits of the TBLPTR<21:10> point to the block being erased; TBLPTR<9:0> are ignored.

The EECON1 register commands the erase operation. The WREN bit must be set to enable write operations. The FREE bit is set to select an erase operation. For protection, the write initiate sequence for EECON2 must be used.

A long write is necessary for erasing the internal Flash. Instruction execution is halted while in a long write cycle. The long write will be terminated by the internal programming timer.

#### 7.4.1 FLASH PROGRAM MEMORY ERASE SEQUENCE

The sequence of events for erasing a block of internal program memory location is:

- 1. Load Table Pointer register with address of row being erased.

- 2. Set the WREN and FREE bits (EECON1<2,4>) to enable the erase operation.

- 3. Disable interrupts.

- 4. Write 55h to EECON2.

- 5. Write 0AAh to EECON2.

- 6. Set the WR bit; this will begin the erase cycle.

- The CPU will stall for the duration of the erase for TIE (see parameter D133B).

- 8. Re-enable interrupts.

#### EXAMPLE 7-2: ERASING FLASH PROGRAM MEMORY

|           | MOVLW | CODE_ADDR_UPPER | ; load TBLPTR with the base   |

|-----------|-------|-----------------|-------------------------------|

|           | MOVWF | TBLPTRU         | ; address of the memory block |

|           | MOVLW | CODE_ADDR_HIGH  |                               |

|           | MOVWF | TBLPTRH         |                               |

|           | MOVLW | CODE_ADDR_LOW   |                               |

|           | MOVWF | TBLPTRL         |                               |

| ERASE_ROW |       |                 |                               |

|           | BSF   | EECON1, WREN    | ; enable write to memory      |

|           | BSF   | EECON1, FREE    | ; enable Erase operation      |

|           | BCF   | INTCON, GIE     | ; disable interrupts          |

| Required  | MOVLW | 55h             |                               |

| Sequence  | MOVWF | EECON2          | ; write 55h                   |

|           | MOVLW | 0AAh            |                               |

|           | MOVWF | EECON2          | ; write OAAh                  |

|           | BSF   | EECON1, WR      | ; start erase (CPU stall)     |

|           | BSF   | INTCON, GIE     | ; re-enable interrupts        |

|           |       |                 |                               |

| Pin       | Function            | TRIS<br>Setting | I/O | l/O<br>Type | Description                          |

|-----------|---------------------|-----------------|-----|-------------|--------------------------------------|

| RD6/PMD6/ | RD6                 | 1               | I   | ST          | PORTD<6> data input.                 |

| RP23      |                     | 0               | 0   | DIG         | LATD<6> data output.                 |

|           | PMD6 <sup>(1)</sup> | 1               | Ι   | ST/TTL      | Parallel Master Port data in.        |

|           |                     | 0               | 0   | DIG         | Parallel Master Port data out.       |

|           | RP23                | 1               | Ι   | ST          | Remappable Peripheral Pin 23 input.  |

|           |                     |                 | 0   | DIG         | Remappable Peripheral Pin 23 output. |

| RD7/PMD7/ | RD7                 | 1               | Ι   | ST          | PORTD<7> data input.                 |

| RP24      |                     | 0               | 0   | DIG         | LATD<7> data output.                 |

|           | PMD7 <sup>(1)</sup> | 1               | Ι   | ST/TTL      | Parallel Master Port data in.        |

|           |                     | 0               | 0   | DIG         | Parallel Master Port data out.       |

|           | RP24                | 1               | Ι   | ST          | Remappable Peripheral Pin 24 input.  |

|           |                     | 0               | 0   | DIG         | Remappable Peripheral Pin 24 output. |

#### TABLE 10-9: PORTD I/O SUMMARY (CONTINUED)

**Legend:** DIG = Digital level output; TTL = TTL input buffer; ST = Schmitt Trigger input buffer;  $I^2C/SMB = I^2C/SMB$ us input buffer; x = Don't care (TRIS bit does not affect port direction or is overridden for this option).

Note 1: This bit is only available on 44-pin devices (PIC18F46J53, PIC18F47J53, PIC18LF46J53 and PIC18LF47J53).

#### TABLE 10-10: SUMMARY OF REGISTERS ASSOCIATED WITH PORTD

| Name                 | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  |

|----------------------|--------|--------|--------|--------|--------|--------|--------|--------|

| PORTD <sup>(1)</sup> | RD7    | RD6    | RD5    | RD4    | RD3    | RD2    | RD1    | RD0    |

| LATD <sup>(1)</sup>  | LATD7  | LATD6  | LATD5  | LATD4  | LATD3  | LATD2  | LATD1  | LATD0  |

| TRISD <sup>(1)</sup> | TRISD7 | TRISD6 | TRISD5 | TRISD4 | TRISD3 | TRISD2 | TRISD1 | TRISD0 |

Legend: — = unimplemented, read as '0'. Shaded cells are not used by PORTD.

Note 1: These registers are not available in 28-pin devices (PIC18F26J53, PIC18F27J53, PIC18LF26J53 and PIC18LF26J53).

## PIC18F47J53

| REGISTER 17-2: | <b>RTCCAL: RTCC CALIBRATION REGISTER (</b> | BANKED F3Eh) |

|----------------|--------------------------------------------|--------------|

|                |                                            |              |

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| CAL7  | CAL6  | CAL5  | CAL4  | CAL3  | CAL2  | CAL1  | CAL0  |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                                                                      |                      |                    |  |  |

|-------------------|----------------------------------------------------------------------|----------------------|--------------------|--|--|

| R = Readable bit  | R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                      |                    |  |  |

| -n = Value at POR | '1' = Bit is set                                                     | '0' = Bit is cleared | x = Bit is unknown |  |  |

| bit 7-0 | CAL<7:0>: RTCC Drift Calibration bits<br>01111111 = Maximum positive adjustment; adds 508 RTC clock pulses every minute                                                                               |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         |                                                                                                                                                                                                       |

|         | •                                                                                                                                                                                                     |

|         | 00000001 = Minimum positive adjustment; adds four RTCC clock pulses every minute<br>00000000 = No adjustment<br>11111111 = Minimum negative adjustment; subtracts four RTCC clock pulses every minute |

|         |                                                                                                                                                                                                       |

|         | •                                                                                                                                                                                                     |

|         | 10000000 = Maximum negative adjustment; subtracts 512 RTCC clock pulses every minute                                                                                                                  |

## REGISTER 17-3: PADCFG1: PAD CONFIGURATION REGISTER (BANKED F3Ch)

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-0                    | R/W-0                    | R/W-0                 |

|-------|-----|-----|-----|-----|--------------------------|--------------------------|-----------------------|

|       | _   | _   | _   | _   | RTSECSEL1 <sup>(1)</sup> | RTSECSEL0 <sup>(1)</sup> | PMPTTL <sup>(2)</sup> |

| bit 7 |     |     |     |     |                          |                          | bit 0                 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 7-3       | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                            |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 2-1       | RTSECSEL<1:0>: RTCC Seconds Clock Output Select bits <sup>(1)</sup>                                                                                                                                                                                                                                                   |

|               | <ul> <li>11 = Reserved; do not use</li> <li>10 = RTCC source clock is selected for the RTCC pin (pin can be INTRC or T1OSC, depending on the RTCOSC (CONFIG3L&lt;1&gt;) setting)</li> <li>01 = RTCC seconds clock is selected for the RTCC pin</li> <li>00 = RTCC alarm pulse is selected for the RTCC pin</li> </ul> |

| bit 0         | <ul> <li>PMPTTL: PMP Module TTL Input Buffer Select bit<sup>(2)</sup></li> <li>1 = PMP module uses TTL input buffers</li> <li>0 = PMP module uses Schmitt input buffers</li> </ul>                                                                                                                                    |

| Note 1:<br>2: | To enable the actual RTCC output, the RTCOE (RTCCFG<2>) bit must be set.<br>Available only on 44-pin devices (PIC18F46J53, PIC18F47J53, PIC18LF46J53 and PIC18LF47J53). For<br>28-pin devices, the bit is U-0.                                                                                                        |

| R/W-0         | R/W-0                                          | R/W-0            | R/W-0          | R/W-0            | R/W-0                       | R/W-0                      | R/W-0       |  |  |

|---------------|------------------------------------------------|------------------|----------------|------------------|-----------------------------|----------------------------|-------------|--|--|

| ALRMEN        | CHIME                                          | AMASK3           | AMASK2         | AMASK1           | AMASK0                      | ALRMPTR1                   | ALRMPTR0    |  |  |

| bit 7         |                                                |                  |                |                  |                             |                            | bit (       |  |  |

| Legend:       |                                                |                  |                |                  |                             |                            |             |  |  |

| R = Readable  | e bit                                          | W = Writable     | bit            | U = Unimpler     | mented bit, rea             | d as '0'                   |             |  |  |

| -n = Value at | POR                                            | '1' = Bit is set |                | '0' = Bit is cle | ared                        | x = Bit is unki            | nown        |  |  |

|               |                                                |                  |                |                  |                             |                            |             |  |  |

| bit 7         |                                                | arm Enable bit   |                |                  |                             |                            |             |  |  |

|               |                                                |                  | ed automatical | y after an alarr | n event whene               | ver ARPT<7:0>              | = 0000 0000 |  |  |

|               | and CHII<br>0 = Alarm is                       | ,                |                |                  |                             |                            |             |  |  |

| bit 6         | CHIME: Chim                                    |                  |                |                  |                             |                            |             |  |  |

|               |                                                |                  | T<7:0> bits ar | e allowed to ro  | oll over from 00            | h to FFh                   |             |  |  |

|               |                                                | disabled; ARF    |                |                  |                             |                            |             |  |  |

| bit 5-2       | AMASK<3:0                                      | >: Alarm Mask    | Configuration  | bits             |                             |                            |             |  |  |

|               |                                                | y half second    |                |                  |                             |                            |             |  |  |

|               | 0001 = Every second<br>0010 = Every 10 seconds |                  |                |                  |                             |                            |             |  |  |

|               | 0010 = Ever                                    |                  |                |                  |                             |                            |             |  |  |

|               | 0100 = Ever                                    |                  |                |                  |                             |                            |             |  |  |

|               | 0101 = Ever                                    |                  |                |                  |                             |                            |             |  |  |

|               | 0110 = Once<br>0111 = Once                     |                  |                |                  |                             |                            |             |  |  |

|               | 1000 = Once                                    |                  |                |                  |                             |                            |             |  |  |

|               |                                                |                  | t when config  | ured for Febru   | ary 29 <sup>th</sup> , once | every four years           | 5)          |  |  |

|               |                                                | erved - do not   | -              |                  | •                           |                            |             |  |  |

|               |                                                | erved – do not   |                |                  |                             |                            |             |  |  |

| bit 1-0       |                                                | :0>: Alarm Val   | -              |                  |                             |                            |             |  |  |

|               |                                                |                  |                |                  |                             | ALRMVALH ar<br>of ALRMVALH |             |  |  |

|               | '00'.                                          |                  |                |                  | ry lead of white            |                            |             |  |  |

|               | ALRMVAL<1                                      | <u>5:8&gt;:</u>  |                |                  |                             |                            |             |  |  |

|               | 00 <b>= ALRMM</b>                              |                  |                |                  |                             |                            |             |  |  |

|               | 01 = ALRMW                                     |                  |                |                  |                             |                            |             |  |  |

|               | 10 = ALRMM<br>11 = Unimple                     |                  |                |                  |                             |                            |             |  |  |

|               | <u>ALRMVAL&lt;7</u>                            |                  |                |                  |                             |                            |             |  |  |

|               | 00 = ALRMS                                     |                  |                |                  |                             |                            |             |  |  |

|               | 01 = ALRMH                                     |                  |                |                  |                             |                            |             |  |  |

|               | 10 = ALRMD                                     |                  |                |                  |                             |                            |             |  |  |

|               | 11 = Unimple                                   | emented          |                |                  |                             |                            |             |  |  |

## REGISTER 17-4: ALRMCFG: ALARM CONFIGURATION REGISTER (ACCESS F47h)

When a shutdown event occurs, two things happen:

- The ECCPxASE bit is set to '1'. The ECCPxASE will remain set until cleared in firmware or an auto-restart occurs. (See Section 19.4.5 "Auto-Restart Mode".)

- The enabled PWM pins are asynchronously placed in their shutdown states. The PWM output pins are grouped into pairs (PxA/PxC) and

(PxB/PxD). The state of each pin pair is determined by the PSSxAC and PSSxBD bits (ECCPxAS<3:0>).

Each pin pair may be placed into one of three states:

- Drive logic '1'

- Drive logic '0'

- Tri-state (high-impedance)

## REGISTER 19-4: ECCPxAS: ECCP1/2/3 AUTO-SHUTDOWN CONTROL REGISTER (1, ACCESS FBEh; 2, FB8h; 3, BANKED F19h)

| R/W-0    | R/W-0    | R/W-0    | R/W-0    | R/W-0   | R/W-0   | R/W-0   | R/W-0   |

|----------|----------|----------|----------|---------|---------|---------|---------|

| ECCPxASE | ECCPxAS2 | ECCPxAS1 | ECCPxAS0 | PSSxAC1 | PSSxAC0 | PSSxBD1 | PSSxBD0 |

| bit 7    |          |          |          |         |         |         | bit 0   |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7   | ECCPxASE: ECCP Auto-Shutdown Event Status bit                                                                                                                                                                                                                                                                                                                                          |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 1 = A shutdown event has occurred; ECCP outputs are in a shutdown state                                                                                                                                                                                                                                                                                                                |

|         | 0 = ECCP outputs are operating                                                                                                                                                                                                                                                                                                                                                         |

| bit 6-4 | ECCPxAS<2:0>: ECCP Auto-Shutdown Source Select bits                                                                                                                                                                                                                                                                                                                                    |

|         | <ul> <li>000 = Auto-shutdown is disabled</li> <li>001 = Comparator, C1OUT, output is high</li> <li>010 = Comparator, C2OUT, output is high</li> <li>011 = Either comparator, C1OUT or C2OUT, is high</li> <li>100 = VIL on FLT0 pin</li> <li>101 = VIL on FLT0 pin or comparator, C1OUT, output is high</li> <li>110 = VIL on FLT0 pin or comparator, C2OUT, output is high</li> </ul> |

|         | 111 = VIL on FLT0 pin or comparator, C1OUT, or comparator, C2OUT, is high                                                                                                                                                                                                                                                                                                              |

| bit 3-2 | PSSxAC<1:0>: PxA and PxC Pins Shutdown State Control bits                                                                                                                                                                                                                                                                                                                              |

|         | 00 = Drive pins, PxA and PxC, to '0'<br>01 = Drive pins, PxA and PxC, to '1'<br>1x = PxA and PxC pins tri-state                                                                                                                                                                                                                                                                        |

| bit 1-0 | PSSxBD<1:0>: PxB and PxD Pins Shutdown State Control bits                                                                                                                                                                                                                                                                                                                              |

|         | 00 = Drive pins, PxB and PxD, to '0'<br>01 = Drive pins, PxB and PxD, to '1'<br>1x = PxB and PxD pins tri-state                                                                                                                                                                                                                                                                        |

| Note 1: | The auto-shutdown condition is a level-based signal, not an edge-based signal. As long as the level is present, the auto-shutdown will persist.                                                                                                                                                                                                                                        |

| 2:      | Writing to the ECCPxASE bit is disabled while an auto-shutdown condition persists.                                                                                                                                                                                                                                                                                                     |

| -       |                                                                                                                                                                                                                                                                                                                                                                                        |

3: Once the auto-shutdown condition has been removed and the PWM restarted (either through firmware or auto-restart), the PWM signal will always restart at the beginning of the next PWM period.

# REGISTER 19-6: PSTRxCON: PULSE STEERING CONTROL (1, ACCESS FBFh; 2, FB9h; 3, BANKED F1Ah)<sup>(1)</sup>

| R/W-0            | R/W-0          | U-0                           | R/W-0                                                | R/W-0            | R/W-0            | R/W-0           | R/W-1         |

|------------------|----------------|-------------------------------|------------------------------------------------------|------------------|------------------|-----------------|---------------|

| CMPL1            | CMPL0          | —                             | STRSYNC                                              | STRD             | STRC             | STRB            | STRA          |

| bit 7            |                |                               |                                                      |                  |                  |                 | bit (         |

|                  |                |                               |                                                      |                  |                  |                 |               |

| Legend:          |                |                               |                                                      |                  |                  |                 |               |

| R = Readable bit |                | W = Writable                  | e bit                                                | U = Unimpler     | mented bit, read | d as '0'        |               |

| -n = Value at    | POR            | '1' = Bit is se               | et                                                   | '0' = Bit is cle | ared             | x = Bit is unkr | nown          |

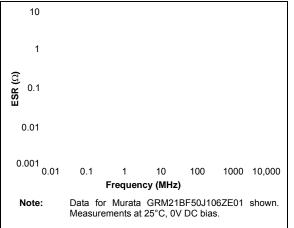

| bit 7-6          | 1 = Modulate   | ed output pin t               | ary Mode Outpu<br>oggles between<br>: assignment dis | PxA and PxB      | for each period  | ł               | rmine Steerin |

| bit 5            | Unimplemen     | ted: Read as                  | <b>'</b> 0 <b>'</b>                                  |                  |                  |                 |               |

| bit 4            | STRSYNC: S     | Steering Sync I               | bit                                                  |                  |                  |                 |               |

|                  |                |                               | e occurs on next                                     |                  |                  |                 |               |

|                  | 0 = Output s   | teering update                | e occurs at the b                                    | eginning of the  | e instruction cy | cle boundary    |               |

| bit 3            | STRD: Steeri   | ng Enable D b                 | bit                                                  |                  |                  |                 |               |

|                  |                | has the PWM is assigned to    | waveform with port pin                               | polarity control | I from CCPxM<    | 1:0>            |               |

| bit 2            | STRC: Steeri   | ng Enable C t                 | bit                                                  |                  |                  |                 |               |

|                  |                | has the PWM is assigned to    | waveform with port pin                               | polarity control | I from CCPxM<    | 1:0>            |               |

| bit 1            | STRB: Steeri   | ng Enable B b                 | bit                                                  |                  |                  |                 |               |

|                  | •              | has the PWM<br>is assigned to | waveform with p<br>port pin                          | oolarity control | from CCPxM<      | 1:0>            |               |

| bit 0            | STRA: Steeri   | ng Enable A b                 | bit                                                  |                  |                  |                 |               |

|                  |                | has the PWM is assigned to    | waveform with p<br>port pin                          | oolarity control | from CCPxM<      | 1:0>            |               |

|                  | e PWM Steering | g mode is ava                 | ilable only wher                                     | the CCPxCO       | N register bits, | CCPxM<3:2>      | = 11 and      |

PxM<1:0> = 00.

# PIC18F47J53

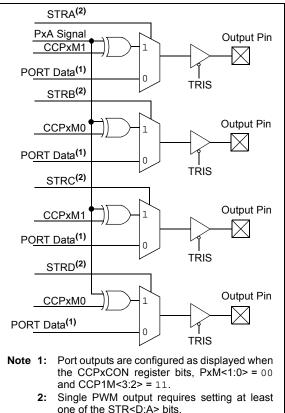

### 19.4.7.1 Steering Synchronization

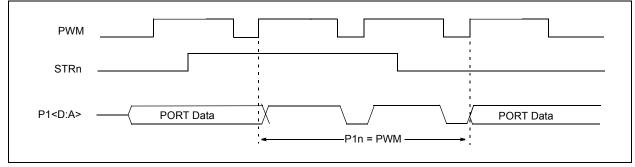

The STRSYNC bit of the PSTRxCON register gives the user two choices for when the steering event will happen. When the STRSYNC bit is '0', the steering event will happen at the end of the instruction that writes to the PSTRxCON register. In this case, the output signal at the Px<D:A> pins may be an incomplete PWM waveform. This operation is useful when the user firmware needs to immediately remove a PWM signal from the pin.

When the STRSYNC bit is '1', the effective steering update will happen at the beginning of the next PWM period. In this case, steering on/off the PWM output will always produce a complete PWM waveform.

Figure 19-17 and Figure 19-18 illustrate the timing diagrams of the PWM steering depending on the STRSYNC setting.

### FIGURE 19-17: EXAMPLE OF STEERING EVENT AT END OF INSTRUCTION (STRSYNC = 0)

#### FIGURE 19-18: EXAMPLE OF STEERING EVENT AT BEGINNING OF INSTRUCTION (STRSYNC = 1)

## 20.4 SPI DMA MODULE

The SPI DMA module contains control logic to allow the MSSP2 module to perform SPI direct memory access transfers. This enables the module to quickly transmit or receive large amounts of data with relatively little CPU intervention. When the SPI DMA module is used, MSSP2 can directly read and write to general purpose SRAM. When the SPI DMA module is not enabled, MSSP2 functions normally, but without DMA capability.

The SPI DMA module is composed of control logic, a Destination Receive Address Pointer, a Transmit Source Address Pointer, an interrupt manager and a Byte Count register for setting the size of each DMA transfer. The DMA module may be used with all SPI Master and Slave modes, and supports both half-duplex and full-duplex transfers.

#### 20.4.1 I/O PIN CONSIDERATIONS

When enabled, the SPI DMA module uses the MSSP2 module. All SPI input and output signals, related to MSSP2, are routed through the Peripheral Pin Select module. The appropriate initialization procedure, as described in **Section 20.4.6** "**Using the SPI DMA Module**", will need to be followed prior to using the SPI DMA module. The output pins assigned to the SDO2 and SCK2 functions can optionally be configured as open-drain outputs, such as for level shifting operations mentioned in the same section.

### 20.4.2 RAM TO RAM COPY OPERATIONS

Although the SPI DMA module is primarily intended to be used for SPI communication purposes, the module can also be used to perform RAM to RAM copy operations. To do this, configure the module for Full-Duplex Master mode operation, but assign the SDO2 output and SDI2 input functions onto the same RPn pin in the PPS module. Also assign SCK2 out and SCK2 in onto the same RPn pin (a different pin than used for SDO2 and SDI2). This will allow the module to operate in Loopback mode, providing RAM copy capability.

#### 20.4.3 IDLE AND SLEEP CONSIDERATIONS

The SPI DMA module remains fully functional when the microcontroller is in Idle mode.

During normal Sleep, the SPI DMA module is not functional and should not be used. To avoid corrupting a transfer, user firmware should be careful to make certain that pending DMA operations are complete by polling the DMAEN bit in the DMACON1 register prior to putting the microcontroller into Sleep.

In SPI Slave modes, the MSSP2 module is capable of transmitting and/or receiving one byte of data while in Sleep mode. This allows the SSP2IF flag in the PIR3 register to be used as a wake-up source. When the DMAEN bit is cleared, the SPI DMA module is effectively disabled, and the MSSP2 module functions normally, but without DMA capabilities. If the DMAEN bit is clear prior to entering Sleep, it is still possible to use the SSP2IF as a wake-up source without any data loss.

Neither MSSP2 nor the SPI DMA module will provide any functionality in Deep Sleep. Upon exiting from Deep Sleep, all of the I/O pins, MSSP2 and SPI DMA related registers will need to be fully re-initialized before the SPI DMA module can be used again.

### 20.4.4 REGISTERS

The SPI DMA engine is enabled and controlled by the following Special Function Registers:

- DMACON1

DMACON2

- TXADDRL

- TXADDRHRXADDRH

- RXADDRL

- DMABCH

- DMABCL

## PIC18F47J53

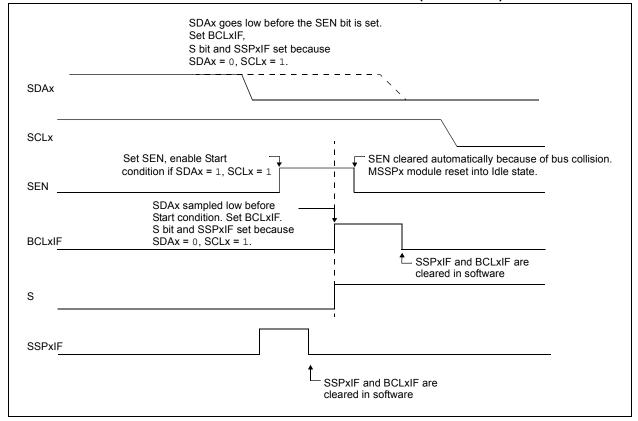

#### 20.5.17.1 Bus Collision During a Start Condition

During a Start condition, a bus collision occurs if:

- a) SDAx or SCLx is sampled low at the beginning of the Start condition (Figure 20-28).

- b) SCLx is sampled low before SDAx is asserted low (Figure 20-29).

During a Start condition, both the SDAx and the SCLx pins are monitored.

If the SDAx pin is already low, or the SCLx pin is already low, then all of the following occur:

- The Start condition is aborted

- · The BCLxIF flag is set

- The MSSP module is reset to its inactive state (Figure 20-28)

The Start condition begins with the SDAx and SCLx pins deasserted. When the SDAx pin is sampled high, the BRG is loaded from SSPxADD<6:0> and counts down to 0. If the SCLx pin is sampled low while SDAx is high, a bus collision occurs because it is assumed that another master is attempting to drive a data '1' during the Start condition.

If the SDAx pin is sampled low during this count, the BRG is reset and the SDAx line is asserted early (Figure 20-30). If, however, a '1' is sampled on the SDAx pin, the SDAx pin is asserted low at the end of the BRG count. The BRG is then reloaded and counts down to 0. If the SCLx pin is sampled as '0' during this time, a bus collision does not occur. At the end of the BRG count, the SCLx pin is asserted low.

Note: The reason that a bus collision is not a factor during a Start condition is that no two bus masters can assert a Start condition at the exact same time. Therefore, one master will always assert SDAx before the other. This condition does not cause a bus collision because the two masters must be allowed to arbitrate the first address following the Start condition. If the address is the same, arbitration must be allowed to continue into the data portion, Repeated Start or Stop conditions.

#### FIGURE 20-28: BUS COLLISION DURING START CONDITION (SDAx ONLY)

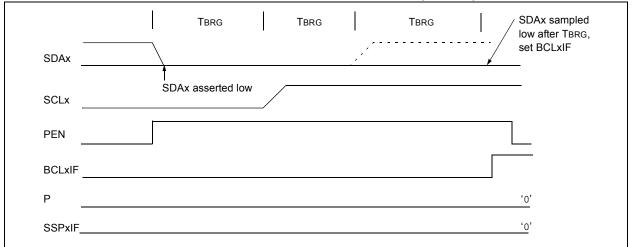

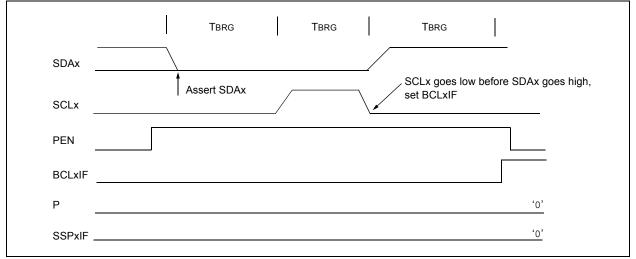

#### 20.5.17.3 Bus Collision During a Stop Condition

Bus collision occurs during a Stop condition if:

- a) After the SDAx pin has been deasserted and allowed to float high, SDAx is sampled low after the BRG has timed out.

- b) After the SCLx pin is deasserted, SCLx is sampled low before SDAx goes high.

The Stop condition begins with SDAx asserted low. When SDAx is sampled low, the SCLx pin is allowed to float. When the pin is sampled high (clock arbitration), the BRG is loaded with SSPxADD<6:0> and counts down to 0. After the BRG times out, SDAx is sampled. If SDAx is sampled low, a bus collision has occurred. This is due to another master attempting to drive a data '0' (Figure 20-33). If the SCLx pin is sampled low before SDAx is allowed to float high, a bus collision occurs. This is another case of another master attempting to drive a data '0' (Figure 20-34).

#### FIGURE 20-33: BUS COLLISION DURING A STOP CONDITION (CASE 1)

### FIGURE 20-34: BUS COLLISION DURING A STOP CONDITION (CASE 2)

## 21.2 EUSART Asynchronous Mode

The Asynchronous mode of operation is selected by clearing the SYNC bit (TXSTAx<4>). In this mode, the EUSART uses standard Non-Return-to-Zero (NRZ) format (one Start bit, eight or nine data bits and one Stop bit). The most common data format is 8 bits. An on-chip dedicated 8-bit/16-bit BRG can be used to derive standard baud rate frequencies from the oscillator.

The EUSART transmits and receives the LSb first. The EUSART's transmitter and receiver are functionally independent but use the same data format and baud rate. The BRG produces a clock, either x16 or x64 of the bit shift rate, depending on the BRGH and BRG16 bits (TXSTAx<2> and BAUDCONx<3>). Parity is not supported by the hardware but can be implemented in software and stored as the ninth data bit.

When operating in Asynchronous mode, the EUSART module consists of the following important elements:

- Baud Rate Generator

- Sampling Circuit

- Asynchronous Transmitter

- · Asynchronous Receiver

- Auto-Wake-up on Sync Break Character

- 12-Bit Break Character Transmit

- Auto-Baud Rate Detection

#### 21.2.1 EUSART ASYNCHRONOUS TRANSMITTER

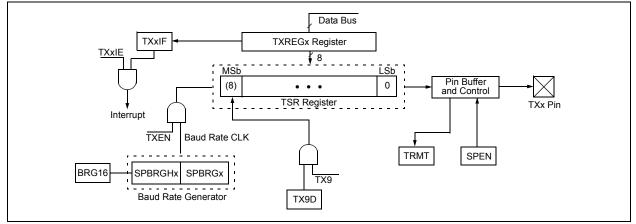

Figure 21-3 displays the EUSART transmitter block diagram.

The heart of the transmitter is the Transmit (Serial) Shift Register (TSR). The shift register obtains its data from the Read/Write Transmit Buffer register, TXREGx. The TXREGx register is loaded with data in software. The TSR register is not loaded until the Stop bit has been transmitted from the previous load. As soon as the Stop bit is transmitted, the TSR is loaded with new data from the TXREGx register (if available). Once the TXREGx register transfers the data to the TSR register (occurs in one TcY), the TXREGx register is empty and the TXxIF flag bit is set. This interrupt can be enabled or disabled by setting or clearing the interrupt enable bit, TXxIE. TXxIF will be set regardless of the state of TXxIE; it cannot be cleared in software. TXxIF is also not cleared immediately upon loading TXREGx, but becomes valid in the second instruction cycle following the load instruction. Polling TXxIF immediately following a load of TXREGx will return invalid results.

While TXxIF indicates the status of the TXREGx register; another bit, TRMT (TXSTAx<1>), shows the status of the TSR register. TRMT is a read-only bit, which is set when the TSR register is empty. No interrupt logic is tied to this bit, so the user has to poll this bit in order to determine if the TSR register is empty.

| Note 1: | The TSR register is not mapped in data memory, so it is not available to the user. |

|---------|------------------------------------------------------------------------------------|

| 2:      | Flag bit, TXxIF, is set when enable bit, TXEN, is set.                             |

To set up an Asynchronous Transmission:

- Initialize the SPBRGHx:SPBRGx registers for the appropriate baud rate. Set or clear the BRGH and BRG16 bits, as required, to achieve the desired baud rate.

- 2. Enable the asynchronous serial port by clearing bit, SYNC, and setting bit, SPEN.

- 3. If interrupts are desired, set enable bit, TXxIE.

- 4. If 9-bit transmission is desired, set transmit bit, TX9; can be used as an address/data bit.

- 5. Enable the transmission by setting bit, TXEN, which will also set bit, TXxIF.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit, TX9D.

- 7. Load data to the TXREGx register (starts transmission).

- If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set.

#### FIGURE 21-3: EUSART TRANSMIT BLOCK DIAGRAM

© 2009-2016 Microchip Technology Inc.

#### 22.8 Operation in Power-Managed Modes

The selection of the automatic acquisition time and A/D conversion clock is determined in part by the clock source and frequency while in a power-managed mode.

If the A/D is expected to operate while the device is in a power-managed mode, the ACQT<2:0> and ADCS<2:0> bits in ADCON1 should be updated in accordance with the power-managed mode clock that will be used. After the power-managed mode is entered (either of the power-managed Run modes), an A/D acquisition or conversion may be started. Once an acquisition or conversion is started, the device should continue to be clocked by the same power-managed mode clock source until the conversion has been completed. If desired, the device may be placed into the corresponding power-managed Idle mode during the conversion.

If the power-managed mode clock frequency is less than 1 MHz, the A/D RC clock source should be selected.

Operation in the Sleep mode requires the A/D RC clock to be selected. If bits, ACQT<2:0>, are set to '000' and a conversion is started, the conversion will be delayed one instruction cycle to allow execution of the SLEEP instruction and entry to Sleep mode. The IDLEN and SCS bits in the OSCCON register must have already been cleared prior to starting the conversion.

### EXAMPLE 22-1: SAMPLE A/D CALIBRATION ROUTINE

| BCF         | ANCON0, PCFG0 | ;Make Channel 0 analog                         |

|-------------|---------------|------------------------------------------------|

| BSF         | ADCON0, ADON  | ;Enable A/D module                             |

| BSF         | ADCON1, ADCAL | ;Enable Calibration                            |

| BSF         | ADCON0,GO     | ;Start a dummy A/D conversion                  |

| CALIBRATION |               | ;                                              |

| BTFSC       | ADCON0,GO     | ;Wait for the dummy conversion to finish       |

| BRA         | CALIBRATION   | i                                              |

| BCF         | ADCON1, ADCAL | ;Calibration done, turn off calibration enable |

|             |               | ;Proceed with the actual A/D conversion        |

|             |               |                                                |

#### TABLE 22-2: SUMMARY OF A/D REGISTERS

| Name    | Bit 7                | Bit 6                | Bit 5                | Bit 4  | Bit 3  | Bit 2  | Bit 1    | Bit 0    |

|---------|----------------------|----------------------|----------------------|--------|--------|--------|----------|----------|

| INTCON  | GIE/GIEH             | PEIE/GIEL            | TMR0IE               | INT0IE | RBIE   | TMR0IF | INT0IF   | RBIF     |

| PIR1    | PMPIF <sup>(1)</sup> | ADIF                 | RC1IF                | TX1IF  | SSP1IF | CCP1IF | TMR2IF   | TMR1IF   |

| PIE1    | PMPIE <sup>(1)</sup> | ADIE                 | RC1IE                | TX1IE  | SSP1IE | CCP1IE | TMR2IE   | TMR1IE   |

| IPR1    | PMPIP <sup>(1)</sup> | ADIP                 | RC1IP                | TX1IP  | SSP1IP | CCP1IP | TMR2IP   | TMR1IP   |

| PIR2    | OSCFIF               | CM2IF                | CM1IF                | USBIF  | BCL1IF | HLVDIF | TMR3IF   | CCP2IF   |

| PIE2    | OSCFIE               | CM2IE                | CM1IE                | USBIE  | BCL1IE | HLVDIE | TMR3IE   | CCP2IE   |

| IPR2    | OSCFIP               | CM2IP                | CM1IP                | USBIP  | BCL1IP | HLVDIP | TMR3IP   | CCP2IP   |

| ADCTRIG | —                    | _                    | _                    | _      | _      | _      | TRIGSEL1 | TRIGSEL0 |

| ADRESH  | A/D Result           | Register High        | i Byte               |        |        |        |          |          |

| ADRESL  | A/D Result           | Register Low         | Byte                 |        |        |        |          |          |

| ADCON0  | VCFG1                | VCFG0                | CHS3                 | CHS3   | CHS1   | CHS0   | GO/DONE  | ADON     |

| ANCON0  | PCFG7 <sup>(1)</sup> | PCFG6 <sup>(1)</sup> | PCFG5 <sup>(1)</sup> | PCFG4  | PCFG3  | PCFG2  | PCFG1    | PCFG0    |

| ADCON1  | ADFM                 | ADCAL                | ACQT2                | ACQT1  | ACQT0  | ADCS2  | ADCS1    | ADCS0    |

| ANCON1  | VBGEN                | r                    | _                    | PCFG12 | PCFG11 | PCFG10 | PCFG9    | PCFG8    |

| CCP2CON | P2M1                 | P2M0                 | DC2B1                | DC2B0  | CCP2M3 | CCP2M2 | CCP2M1   | CCP2M0   |

| PORTA   | RA7                  | RA6                  | RA5                  |        | RA3    | RA2    | RA1      | RA0      |

| TRISA   | TRISA7               | TRISA6               | TRISA5               |        | TRISA3 | TRISA2 | TRISA1   | TRISA0   |

**Legend:** — = unimplemented, read as '0', r = reserved. Shaded cells are not used for A/D conversion.

Note 1: These bits are only available on 44-pin devices.

## 27.3.2 CAPACITANCE CALIBRATION

There is a small amount of capacitance from the internal A/D Converter sample capacitor as well as stray capacitance from the circuit board traces and pads that affect the precision of capacitance measurements. A measurement of the stray capacitance can be taken by making sure the desired capacitance to be measured has been removed. The measurement is then performed using the following steps:

- 1. Initialize the A/D Converter and the CTMU.

- 2. Set EDG1STAT (= 1).

- 3. Wait for a fixed delay of time, *t*.

- 4. Clear EDG1STAT.

- 5. Perform an A/D conversion.

- 6. Calculate the stray and A/D sample capacitances:

$$C_{\text{OFFSET}} = C_{\text{STRAY}} + C_{\text{AD}} = (I \cdot t) / V$$

where *I* is known from the current source measurement step, *t* is a fixed delay and *V* is measured by performing an A/D conversion.

This measured value is then stored and used for calculations of time measurement or subtracted for capacitance measurement. For calibration, it is expected that the capacitance of CSTRAY + CAD is approximately known. CAD is approximately 4 pF.

An iterative process may need to be used to adjust the time, t, that the circuit is charged to obtain a reasonable voltage reading from the A/D Converter. The value of t may be determined by setting COFFSET to a theoretical value, then solving for t. For example, if CSTRAY is theoretically calculated to be 11 pF, and V is expected to be 70% of VDD or 2.31V, then t would be:

$$(4 \text{ pF} + 11 \text{ pF}) \bullet 2.31 \text{V}/0.55 \ \mu\text{A}$$

or 63 µs.

See Example 27-3 for a typical routine for CTMU capacitance calibration.

# PIC18F47J53

| SLEEP                             | Enter Sle                                                                                                                                                     | ep Mode                                                         |                | SUBFWB                         |

|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|----------------|--------------------------------|

| Syntax:                           | SLEEP                                                                                                                                                         |                                                                 |                | Syntax:                        |

| Operands:                         | None                                                                                                                                                          |                                                                 |                | Operands:                      |

| Operation:                        | $\begin{array}{l} \text{O0h} \rightarrow \text{WI} \\ 0 \rightarrow \text{WDT} \\ 1 \rightarrow \overline{\text{TO}}, \\ 0 \rightarrow \text{PD} \end{array}$ | DT,<br>postscaler,                                              |                | Operation:<br>Status Affected: |

| Status Affected:                  | TO, PD                                                                                                                                                        |                                                                 |                | Encoding:                      |

| Encoding:                         | 0000                                                                                                                                                          | 0000 000                                                        | 00 0011        | Description:                   |

| Description:                      | cleared. T<br>is set. The                                                                                                                                     | r-Down status<br>he Time-out st<br>Watchdog Tir<br>are cleared. | atus bit (TO)  | Description.                   |

|                                   | •                                                                                                                                                             | ssor is put into<br>scillator stoppe                            | •              |                                |

| Words:                            | 1                                                                                                                                                             |                                                                 |                |                                |

| Cycles:                           | 1                                                                                                                                                             |                                                                 |                |                                |

| Q Cycle Activity:                 |                                                                                                                                                               |                                                                 |                |                                |