Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 48MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART, USB                               |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                        |

| Number of I/O              | 22                                                                           |

| Program Memory Size        | 128KB (64K x 16)                                                             |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 3.8K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 2.75V                                                                   |

| Data Converters            | A/D 10x10b/12b                                                               |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                               |

| Supplier Device Package    | 28-SOIC                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf27j53t-i-so |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 3.0 OSCILLATOR CONFIGURATIONS

#### 3.1 Overview

Devices in the PIC18F47J53 family incorporate a different oscillator and microcontroller clock system than general purpose PIC18F devices. Besides the USB module, with its unique requirements for a stable clock source, make it is necessary to provide a separate clock source that is compliant with both USB low-speed and full-speed specifications.

The PIC18F47J53 family has additional prescalers and postscalers, which have been added to accommodate a wide range of oscillator frequencies. Figure 3-1 provides an overview of the oscillator structure.

Other oscillator features used in PIC18 enhanced microcontrollers, such as the internal oscillator block and clock switching, remain the same. They are discussed later in this chapter.

## 3.1.1 OSCILLATOR CONTROL

The operation of the oscillator in PIC18F47J53 family devices is controlled through three Configuration registers, and two control registers. Configuration registers, CONFIG1L, CONFIG1H and CONFIG2L, select the oscillator mode, PLL prescaler and CPU divider options. As Configuration bits, these are set when the device is programmed and left in that configuration until the device is reprogrammed.

The OSCCON register (Register 3-2) selects the Active Clock mode; it is primarily used in controlling clock switching in power-managed modes. Its use is discussed in **Section 3.5.1** "**Oscillator Control Register**".

The OSCTUNE register (Register 3-1) is used to trim the INTOSC frequency source and select the low-frequency clock source that drives several special features. The OSCTUNE register is also used to activate or disable the Phase Locked Loop (PLL). Its use is described in **Section 3.2.5.1 "OSCTUNE Register"**.

## 3.2 Oscillator Types

PIC18F47J53 family devices can be operated in eight distinct oscillator modes. Users can program the FOSC<2:0> Configuration bits to select one of the modes listed in Table 3-1. For oscillator modes which produce a clock output (CLKO) on pin RA6, the output frequency will be one fourth of the peripheral clock frequency. The clock output stops when in Sleep mode, but will continue during Idle mode (see Figure 3-1).

## TABLE 3-1: OSCILLATOR MODES

| TABLE 3-1: | OSCILLATOR MODES                                                                                                                                                                                                                         |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Mode       | Description                                                                                                                                                                                                                              |

| ECPLL      | External Clock Input mode, the PLL can<br>be enabled or disabled in software,<br>CLKO on RA6, apply external clock<br>signal to RA7.                                                                                                     |

| EC         | External Clock Input mode, the PLL is always disabled, CLKO on RA6, apply external clock signal to RA7.                                                                                                                                  |

| HSPLL      | High-Speed Crystal/Resonator mode,<br>PLL can be enabled or disabled in<br>software, crystal/resonator connected<br>between RA6 and RA7.                                                                                                 |

| HS         | High-Speed Crystal/Resonator mode,<br>PLL always disabled, crystal/resonator<br>connected between RA6 and RA7.                                                                                                                           |

| INTOSCPLLO | Internal Oscillator mode, PLL can be<br>enabled or disabled in software, CLKO<br>on RA6, port function on RA7, the<br>internal oscillator block is used to derive<br>both the primary clock source and the<br>postscaled internal clock. |

| INTOSCPLL  | Internal Oscillator mode, PLL can be<br>enabled or disabled in software, port<br>function on RA6 and RA7, the internal<br>oscillator block is used to derive both the<br>primary clock source and the postscaled<br>internal clock.      |

| INTOSCO    | Internal Oscillator mode, PLL is always<br>disabled, CLKO on RA6, port function on<br>RA7, the output of the INTOSC<br>postscaler serves as both the postscaled<br>internal clock and the primary clock<br>source.                       |

| INTOSC     | Internal Oscillator mode, PLL is always<br>disabled, port function on RA6 and RA7,<br>the output of the INTOSC postscaler<br>serves as both the postscaled internal<br>clock and the primary clock source.                               |

# 3.2.1 OSCILLATOR MODES AND USB OPERATION

Because of the unique requirements of the USB module, a different approach to clock operation is necessary. In order to use the USB module, a fixed 6 MHz or 48 MHz clock must be internally provided to the USB module for operation in either Low-Speed or Full-Speed mode, respectively. The microcontroller core need not be clocked at the same frequency as the USB module.

A network of MUXes, clock dividers and a fixed 96 MHz output PLL have been provided, which can be used to derive various microcontroller core and USB module frequencies. Figure 3-1 helps in understanding the oscillator structure of the PIC18F47J53 family of devices.

| Input Oscillator<br>Frequency | PLL Division<br>(PLLDIV<2:0>) | Clock Mode<br>(FOSC<2:0>) | MCU Clock Division<br>(CPDIV<1:0>) | Microcontroller<br>Clock Frequency |

|-------------------------------|-------------------------------|---------------------------|------------------------------------|------------------------------------|

|                               |                               |                           | None (11)                          | 48 MHz                             |

|                               |                               | 50                        | ÷2(10)                             | 24 MHz                             |

| 48 MHz                        | N/A                           | EC                        | ÷3(01)                             | 16 MHz                             |

|                               |                               |                           | ÷6 (00)                            | 8 MHz                              |

|                               |                               |                           | None (11)                          | 48 MHz                             |

|                               | 10 (000)                      | FORM                      | ÷2(10)                             | 24 MHz                             |

| 48 MHz                        | ÷12 (000)                     | ECPLL                     | ÷3(01)                             | 16 MHz                             |

|                               |                               |                           | ÷6 (00)                            | 8 MHz                              |

|                               |                               |                           | None (11)                          | 48 MHz                             |

|                               | 10 (001)                      | FORM                      | ÷2(10)                             | 24 MHz                             |

| 40 MHz                        | ÷10(001)                      | ECPLL                     | ÷3(01)                             | 16 MHz                             |

|                               |                               |                           | ÷6 (00)                            | 8 MHz                              |

|                               |                               |                           | None (11)                          | 48 MHz                             |

|                               | ÷6 (010)                      | FORM                      | ÷2 (10)                            | 24 MHz                             |

| 24 MHz                        |                               | ECPLL                     | ÷3(01)                             | 16 MHz                             |

|                               |                               |                           | ÷6 (00)                            | 8 MHz                              |

|                               |                               | EC <sup>(1)</sup>         | None (11)                          | 24 MHz                             |

|                               | N/A                           |                           | ÷2 (10)                            | 12 MHz                             |

| 24 MHz                        |                               |                           | ÷3 (01)                            | 8 MHz                              |

|                               |                               |                           | ÷6 (00)                            | 4 MHz                              |

|                               | ÷5 (011)                      | ECPLL                     | None (11)                          | 48 MHz                             |

|                               |                               |                           | ÷2 (10)                            | 24 MHz                             |

| 20 MHz                        |                               |                           | ÷3(01)                             | 16 MHz                             |

|                               |                               |                           | ÷6 (00)                            | 8 MHz                              |

|                               |                               |                           | None (11)                          | 48 MHz                             |

|                               |                               |                           | ÷2 (10)                            | 24 MHz                             |

| 16 MHz                        | ÷4 (100)                      | HSPLL, ECPLL              | ÷3 (01)                            | 16 MHz                             |

|                               |                               |                           | ÷6 (00)                            | 8 MHz                              |

|                               |                               |                           | None (11)                          | 48 MHz                             |

|                               | 0 (2.22.)                     |                           | ÷2 (10)                            | 24 MHz                             |

| 12 MHz                        | ÷3(101)                       | HSPLL, ECPLL              | ÷3(01)                             | 16 MHz                             |

|                               |                               |                           | ÷6 (00)                            | 8 MHz                              |

|                               |                               |                           | None (11)                          | 48 MHz                             |

| 0.1411-                       | 0 (5 5 5)                     | HSPLL, ECPLL,             | ÷2 (10)                            | 24 MHz                             |

| 8 MHz                         | ÷2 (110)                      | INTOSCPLL/<br>INTOSCPLLO  | ÷3(01)                             | 16 MHz                             |

|                               |                               |                           | ÷6 (00)                            | 8 MHz                              |

|                               |                               |                           | None (11)                          | 48 MHz                             |

| 4.8411                        | 4 ()                          |                           | ÷2 (10)                            | 24 MHz                             |

| 4 MHz                         | ÷ <b>1</b> (111)              | HSPLL, ECPLL              | ÷3(01)                             | 16 MHz                             |

|                               |                               |                           | ÷6 (00)                            | 8 MHz                              |

| <b>TABLE 3-5:</b> | OSCILLATOR CONFIGURATION OPTIONS FOR USB OPERATION |

|-------------------|----------------------------------------------------|

|                   |                                                    |

Note 1: The 24 MHz EC mode (without PLL) is only compatible with low-speed USB. Full-speed USB requires a 48 MHz system clock.

## REGISTER 9-10: PIE2: PERIPHERAL INTERRUPT ENABLE REGISTER 2 (ACCESS FA0h)

| R/W-0        | R/W-0                      | R/W-0                 | R/W-0           | R/W-0             | R/W-0            | R/W-0           | R/W-0  |

|--------------|----------------------------|-----------------------|-----------------|-------------------|------------------|-----------------|--------|

| OSCFIE       | CM2IE                      | CM1IE                 | USBIE           | BCL1IE            | HLVDIE           | TMR3IE          | CCP2IE |

| bit 7        |                            |                       |                 |                   |                  |                 | bit 0  |

|              |                            |                       |                 |                   |                  |                 |        |

| Legend:      |                            |                       |                 |                   |                  |                 |        |

| R = Readab   | le bit                     | W = Writable          | bit             | U = Unimplem      | nented bit, read | d as '0'        |        |

| -n = Value a | t POR                      | '1' = Bit is set      |                 | '0' = Bit is clea | ared             | x = Bit is unkr | nown   |

|              |                            |                       | _               | -                 |                  |                 |        |

| bit 7        |                            | scillator Fail Inte   | rrupt Enable b  | it                |                  |                 |        |

|              | 1 = Enableo<br>0 = Disable |                       |                 |                   |                  |                 |        |

| bit 6        |                            | nparator 2 Interr     | upt Enable bit  |                   |                  |                 |        |

|              | 1 = Enabled                | -                     |                 |                   |                  |                 |        |

|              | 0 = Disable                | d                     |                 |                   |                  |                 |        |

| bit 5        | CM1IE: Con                 | nparator 1 Interr     | upt Enable bit  |                   |                  |                 |        |

|              | 1 = Enabled                |                       |                 |                   |                  |                 |        |

|              | 0 = Disable                |                       |                 |                   |                  |                 |        |

| bit 4        |                            | 3 Interrupt Enab      | le bit          |                   |                  |                 |        |

|              | 1 = Enableo<br>0 = Disable |                       |                 |                   |                  |                 |        |

| bit 3        |                            | s Collision Interi    | unt Enable bit  | (MSSP1 modul      | e)               |                 |        |

|              | 1 = Enableo                |                       |                 |                   | 0)               |                 |        |

|              | 0 = Disable                | d                     |                 |                   |                  |                 |        |

| bit 2        | HLVDIE: Hig                | gh/Low-Voltage        | Detect Interrup | ot Enable bit     |                  |                 |        |

|              | 1 = Enabled                |                       |                 |                   |                  |                 |        |

|              | 0 = Disable                |                       | –               |                   |                  |                 |        |

| bit 1        |                            | /IR3 Overflow In      | terrupt Enable  | bit               |                  |                 |        |

|              | 1 = Enableo<br>0 = Disable |                       |                 |                   |                  |                 |        |

| bit 0        |                            | ~<br>CCP2 Interrupt E | nable bit       |                   |                  |                 |        |

| <b>-</b>     | 1 = Enableo                | •                     |                 |                   |                  |                 |        |

|              | 0 = Disable                | d                     |                 |                   |                  |                 |        |

#### 9.6 INTx Pin Interrupts

External interrupts on the INT0, INT1, INT2 and INT3 pins are edge-triggered. If the corresponding INTEDGx bit in the INTCON2 register is set (= 1), the interrupt is triggered by a rising edge; if the bit is clear, the trigger is on the falling edge. When a valid edge appears on the INTx pin, the corresponding flag bit and INTxIF are set. This interrupt can be disabled by clearing the corresponding enable bit, INTxIE. Flag bit, INTxIF, must be cleared in software in the Interrupt Service Routine before re-enabling the interrupt.

All external interrupts (INT0, INT1, INT2 and INT3) can wake up the processor from the Sleep and Idle modes if bit, INTxIE, was set prior to going into the power-managed modes. Deep Sleep mode can wake up from INT0, but the processor will start execution from the power-on reset vector rather than branch to the interrupt vector.

Interrupt priority for INT1, INT2 and INT3 is determined by the value contained in the Interrupt Priority bits, INT1IP (INTCON3<6>), INT2IP (INTCON3<7>) and INT3IP (INTCON2<1>). There is no priority bit associated with INT0; It is always a high-priority interrupt source.

## 9.7 TMR0 Interrupt

In 8-bit mode (which is the default), an overflow in the TMR0 register (FFh  $\rightarrow$  00h) will set flag bit, TMR0IF. In 16-bit mode, an overflow in the TMR0H:TMR0L register

pair (FFFFh  $\rightarrow$  0000h) will set TMR0IF. The interrupt can be enabled/disabled by setting/clearing enable bit, TMR0IE (INTCON<5>). Interrupt priority for Timer0 is determined by the value contained in the interrupt priority bit, TMR0IP (INTCON2<2>). See Section 12.0 "Timer0 Module" for further details on the Timer0 module.

## 9.8 PORTB Interrupt-on-Change

An input change on PORTB<7:4> sets flag bit, RBIF (INTCON<0>). The interrupt can be enabled/disabled by setting/clearing enable bit, RBIE (INTCON<3>). Interrupt priority for PORTB interrupt-on-change is determined by the value contained in the interrupt priority bit, RBIP (INTCON2<0>).

## 9.9 Context Saving During Interrupts

During interrupts, the return PC address is saved on the stack. Additionally, the WREG, STATUS and BSR registers are saved on the Fast Return Stack. If a fast return from interrupt is not used (see **Section 6.3 "Data Memory Organization"**), the user may need to save the WREG, STATUS and BSR registers on entry to the Interrupt Service Routine. Depending on the user's application, other registers may also need to be saved. Example 9-1 saves and restores the WREG, STATUS and BSR registers during an Interrupt Service Routine.

EXAMPLE 9-1: SAVING STATUS, WREG AND BSR REGISTERS IN RAM

| MOVWF<br>MOVFF | W_TEMP<br>STATUS, STATUS_TEMP | ; W_TEMP is in virtual bank<br>; STATUS_TEMP located anywhere |

|----------------|-------------------------------|---------------------------------------------------------------|

| MOVFF          | BSR, BSR_TEMP                 | ; BSR_TMEP located anywhere                                   |

| ;              |                               |                                                               |

| ; USER         | ISR CODE                      |                                                               |

| ;              |                               |                                                               |

| MOVFF          | BSR_TEMP, BSR                 | ; Restore BSR                                                 |

| MOVF           | W_TEMP, W                     | ; Restore WREG                                                |

| MOVFF          | STATUS_TEMP, STATUS           | ; Restore STATUS                                              |

| IABLE 10-7:  |          |                 |     |             |                                                                                            |  |  |  |

|--------------|----------|-----------------|-----|-------------|--------------------------------------------------------------------------------------------|--|--|--|

| Pin          | Function | TRIS<br>Setting | I/O | I/О<br>Туре | Description                                                                                |  |  |  |

| RC0/T1OSO/   | RC0      | 1               | Ι   | ST          | PORTC<0> data input.                                                                       |  |  |  |

| T1CKI/RP11   |          | 0               | 0   | DIG         | LATC<0> data output.                                                                       |  |  |  |

|              | T10S0    | х               | 0   | ANA         | Timer1 oscillator output; enabled when Timer1 oscillator is enabled. Disables digital I/O. |  |  |  |

|              | T1CKI    | 1               | I   | ST          | Timer1 digital clock input.                                                                |  |  |  |

|              | RP11     | 1               | Ι   | ST          | Remappable Peripheral Pin 11 input.                                                        |  |  |  |

|              |          | 0               | 0   | DIG         | Remappable Peripheral Pin 11 output.                                                       |  |  |  |

| RC1/CCP8/    | RC1      | 1               | I   | ST          | PORTC<1> data input.                                                                       |  |  |  |

| T1OSI/UOE/   |          | 0               | 0   | DIG         | LATC<1> data output.                                                                       |  |  |  |

| RP12         | CCP8     | 1               | I   | ST          | Capture input.                                                                             |  |  |  |

|              |          | 0               | 0   | DIG         | Compare/PWM output.                                                                        |  |  |  |

|              | T1OSI    | SI x I ANA      |     | ANA         | Timer1 oscillator input; enabled when Timer1 oscillator is enabled. Disables digital I/O.  |  |  |  |

|              | UOE      | 0               | 0   | DIG         | External USB transceiver NOE output.                                                       |  |  |  |

|              | RP12     | 1               | Ι   | ST          | Remappable Peripheral Pin 12 input.                                                        |  |  |  |

|              |          | 0               | 0   | DIG         | Remappable Peripheral Pin 12 output.                                                       |  |  |  |

| RC2/AN11/    | RC2      | 1               | I   | ST          | PORTC<2> data input.                                                                       |  |  |  |

| C2IND/CTPLS/ |          | 0               | 0   | DIG         | PORTC<2> data output.                                                                      |  |  |  |

| RP13         | AN11     | 1               | I   | ANA         | A/D Input Channel 11.                                                                      |  |  |  |

|              | C2IND    | 1               | I   | ANA         | Comparator 2 Input D.                                                                      |  |  |  |

|              | CTPLS    | 0               | 0   | DIG         | CTMU pulse generator output.                                                               |  |  |  |

|              | RP13     | 1               | Ι   | ST          | Remappable Peripheral Pin 13 input.                                                        |  |  |  |

|              |          | 0               | 0   | DIG         | Remappable Peripheral Pin 13 output.                                                       |  |  |  |

| RC4/D-/VM    | RC4      | 1               | Ι   | ST          | PORTC<4> data input.                                                                       |  |  |  |

|              | D-       | x               | Ι   | XCVR        | USB bus minus line output.                                                                 |  |  |  |

|              |          | х               | 0   | XCVR        | USB bus minus line input.                                                                  |  |  |  |

|              | VM       | 1               | I   | ST          | External USB transceiver VP input.                                                         |  |  |  |

| RC5/D+/VP    | RC5      | 1               | I   | ST          | PORTC<5> data input.                                                                       |  |  |  |

|              | D+       | х               | I   | XCVR        | USB bus plus line input.                                                                   |  |  |  |

|              |          | х               | 0   | XCVR        | USB bus plus line output.                                                                  |  |  |  |

|              | VP       | 1               | I   | ST          | External USB transceiver VP input.                                                         |  |  |  |

# TABLE 10-7: PORTC I/O SUMMARY<sup>(1)</sup>

**Legend:** DIG = Digital level output; TTL = TTL input buffer; ST = Schmitt Trigger input buffer; ANA = Analog level input/output; I<sup>2</sup>C/SMB = I<sup>2</sup>C/SMBus input buffer; x = Don't care (TRIS bit does not affect port direction or is overridden for this option)

**Note 1:** Enhanced PWM output is available only on PIC18F4XJ53 devices.

2: This bit is only available on 44-pin devices (PIC18F46J53, PIC18F47J53, PIC18LF46J53 and PIC18LF47J53).

#### 10.7.3.2 Output Mapping

In contrast to inputs, the outputs of the PPS options are mapped on the basis of the pin. In this case, a control register associated with a particular pin dictates the peripheral output to be mapped. The RPORx registers are used to control output mapping. The value of the bit field corresponds to one of the peripherals and that peripheral's output is mapped to the pin (see Table 10-14). Because of the mapping technique, the list of peripherals for output mapping also includes a null value of '00000'. This permits any given pin to remain disconnected from the output of any of the pin-selectable peripherals.

## TABLE 10-14: SELECTABLE OUTPUT SOURCES (MAPS FUNCTION TO OUTPUT)

| Function | Output Function<br>Number <sup>(1)</sup> | Output Name                                             |

|----------|------------------------------------------|---------------------------------------------------------|

| NULL     | 0                                        | NULL <sup>(2)</sup>                                     |

| C1OUT    | 1                                        | Comparator 1 Output                                     |

| C2OUT    | 2                                        | Comparator 2 Output                                     |

| C3OUT    | 3                                        | Comparator 3 Output                                     |

| TX2/CK2  | 6                                        | EUSART2 Asynchronous Transmit/Asynchronous Clock Output |

| DT2      | 7                                        | EUSART2 Synchronous Transmit                            |

| SDO2     | 10                                       | SPI2 Data Output                                        |

| SCK2     | 11                                       | SPI2 Clock Output                                       |

| SSDMA    | 12                                       | SPI DMA Slave Select                                    |

| ULPOUT   | 13                                       | Ultra Low-Power Wake-up Event                           |

| CCP1/P1A | 14                                       | ECCP1 Compare or PWM Output Channel A                   |

| P1B      | 15                                       | ECCP1 Enhanced PWM Output, Channel B                    |

| P1C      | 16                                       | ECCP1 Enhanced PWM Output, Channel C                    |

| P1D      | 17                                       | ECCP1 Enhanced PWM Output, Channel D                    |

| CCP2/P2A | 18                                       | ECCP2 Compare or PWM Output                             |

| P2B      | 19                                       | ECCP2 Enhanced PWM Output, Channel B                    |

| P2C      | 20                                       | ECCP2 Enhanced PWM Output, Channel C                    |

| P2D      | 21                                       | ECCP2 Enhanced PWM Output, Channel D                    |

| CCP3/P3A | 22                                       | ECCP3 Compare or PWM Output                             |

| P3B      | 23                                       | ECCP3 Enhanced PWM Output, Channel B                    |

| P3C      | 24                                       | ECCP3 Enhanced PWM Output, Channel C                    |

| P3D      | 25                                       | ECCP3 Enhanced PWM Output, Channel D                    |

**Note 1:** Value assigned to the RP<4:0> pins corresponds to the peripheral output function number.

2: The NULL function is assigned to all RPn outputs at device Reset and disables the RPn output function.

#### **11.2 Slave Port Modes**

The primary mode of operation for the module is configured using the MODE<1:0> bits in the PMMODEH register. The setting affects whether the module acts as a slave or a master, and it determines the usage of the control pins.

#### 11.2.1 LEGACY MODE (PSP)

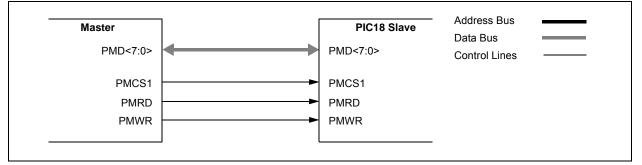

In Legacy mode (PMMODEH<1:0> = 00 and PMPEN = 1), the module is configured as a Parallel Slave Port (PSP) with the associated enabled module

pins dedicated to the module. In this mode, an external device, such as another microcontroller or microprocessor, can asynchronously read and write data using the 8-bit data bus (PMD<7:0>), the read (PMRD), write (PMWR) and chip select (PMCS1) inputs. It acts as a slave on the bus and responds to the read/write-control signals.

Figure 11-2 displays the connection of the PSP. When chip select is active and a write strobe occurs (PMCSx = 1 and PMWR = 1), the data from PMD<7:0> is captured into the PMDIN1L register.

#### FIGURE 11-2: LEGACY PARALLEL SLAVE PORT EXAMPLE

| TADLE 11-2.                |                      |                                             |              |               |               |           |           |        |  |  |  |

|----------------------------|----------------------|---------------------------------------------|--------------|---------------|---------------|-----------|-----------|--------|--|--|--|

| Name                       | Bit 7                | Bit 6                                       | Bit 5        | Bit 4         | Bit 3         | Bit 2     | Bit 1     | Bit 0  |  |  |  |

| INTCON                     | GIE/GIEH             | PEIE/GIEL                                   | TMR0IE       | INT0IE        | RBIE          | TMR0IF    | INT0IF    | RBIF   |  |  |  |

| PIR1                       | PMPIF <sup>(2)</sup> | ADIF                                        | RC1IF        | TX1IF         | SSP1IF        | CCP1IF    | TMR2IF    | TMR1IF |  |  |  |

| PIE1                       | PMPIE <sup>(2)</sup> | ADIE                                        | RC1IE        | TX1IE         | SSP1IE        | CCP1IE    | TMR2IE    | TMR1IE |  |  |  |

| IPR1                       | PMPIP <sup>(2)</sup> | ADIP                                        | RC1IP        | TX1IP         | SSP1IP        | CCP1IP    | TMR2IP    | TMR1IP |  |  |  |

| PMCONH <sup>(2)</sup>      | PMPEN                | -                                           | PSIDL        | ADRMUX1       | ADRMUX0       | PTBEEN    | PTWREN    | PTRDEN |  |  |  |

| PMCONL <sup>(2)</sup>      | CSF1                 | CSF0                                        | ALP          | —             | CS1P          | BEP       | WRSP      | RDSP   |  |  |  |

| PMADDRH <sup>(1,2)</sup> / | —                    | CS1                                         | Parallel M   | aster Port Ad | dress High By | rte       |           |        |  |  |  |

| PMDOUT1H <sup>(1,2)</sup>  | Parallel Port        | Parallel Port Out Data High Byte (Buffer 1) |              |               |               |           |           |        |  |  |  |

| PMADDRL <sup>(1,2)</sup> / | Parallel Mas         | Parallel Master Port Address Low Byte       |              |               |               |           |           |        |  |  |  |

| PMDOUT1L <sup>(1,2)</sup>  | Parallel Port        | Parallel Port Out Data Low Byte (Buffer 0)  |              |               |               |           |           |        |  |  |  |

| PMDOUT2H <sup>(2)</sup>    | Parallel Port        | : Out Data Hi                               | gh Byte (Βι  | uffer 3)      |               |           |           |        |  |  |  |

| PMDOUT2L <sup>(2)</sup>    | Parallel Port        | Out Data Lo                                 | w Byte (Bu   | ffer 2)       |               |           |           |        |  |  |  |

| PMDIN1H <sup>(2)</sup>     | Parallel Port        | In Data High                                | n Byte (Buff | er 1)         |               |           |           |        |  |  |  |

| PMDIN1L <sup>(2)</sup>     | Parallel Port        | In Data Low                                 | Byte (Buffe  | er 0)         |               |           |           |        |  |  |  |

| PMDIN2H <sup>(2)</sup>     | Parallel Port        | In Data High                                | n Byte (Buff | er 3)         |               |           |           |        |  |  |  |

| PMDIN2L <sup>(2)</sup>     | Parallel Port        | In Data Low                                 | Byte (Buffe  | er 2)         |               |           |           |        |  |  |  |

| PMMODEH <sup>(2)</sup>     | BUSY                 | IRQM1                                       | IRQM0        | INCM1         | INCM0         | MODE16    | MODE1     | MODE0  |  |  |  |

| PMMODEL <sup>(2)</sup>     | WAITB1               | WAITB0                                      | WAITM3       | WAITM2        | WAITM1        | WAITM0    | WAITE1    | WAITE0 |  |  |  |

| PMEH <sup>(2)</sup>        | PTEN15               | PTEN14                                      | PTEN13       | PTEN12        | PTEN11        | PTEN10    | PTEN9     | PTEN8  |  |  |  |

| PMEL <sup>(2)</sup>        | PTEN7                | PTEN6                                       | PTEN5        | PTEN4         | PTEN3         | PTEN2     | PTEN1     | PTEN0  |  |  |  |

| PMSTATH <sup>(2)</sup>     | IBF                  | IBOV                                        | —            | —             | IB3F          | IB2F      | IB1F      | IB0F   |  |  |  |

| PMSTATL <sup>(2)</sup>     | OBE                  | OBUF                                        | _            | _             | OB3E          | OB2E      | OB1E      | OB0E   |  |  |  |

| PADCFG1                    | —                    | —                                           | —            | —             | _             | RTSECSEL1 | RTSECSEL0 | PMPTTL |  |  |  |

#### TABLE 11-2: REGISTERS ASSOCIATED WITH PMP MODULE

Legend: — = unimplemented, read as '0'. Shaded cells are not used during PMP operation.

**Note 1:** The PMADDRH/PMDOUT1H and PMADDRL/PMDOUT1L register pairs share the physical registers and addresses, but have different functions determined by the module's operating mode.

2: These bits and/or registers are only available in 44-pin devices.

#### 13.5.1 USING TIMER1 AS A CLOCK SOURCE

The Timer1 oscillator is also available as a clock source in power-managed modes. By setting the clock select bits, SCS<1:0> (OSCCON<1:0>), to '01', the device switches to SEC\_RUN mode; both the CPU and peripherals are clocked from the Timer1 oscillator. If the IDLEN bit (OSCCON<7>) is cleared and a SLEEP instruction is executed, the device enters SEC\_IDLE mode. Additional details are available in **Section 4.0** "Low-Power Modes".

Whenever the Timer1 oscillator is providing the clock source, the Timer1 system clock status flag, SOSCRUN (OSCCON2<6>), is set. This can be used to determine the controller's current clocking mode. It can also indicate the clock source currently being used by the Fail-Safe Clock Monitor. If the Clock Monitor is enabled and the Timer1 oscillator fails while providing the clock, polling the SOSCRUN bit will indicate whether the clock is being provided by the Timer1 oscillator or another source.

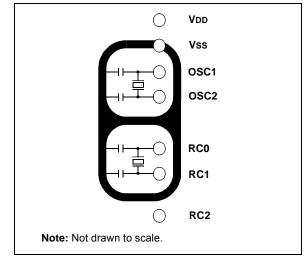

#### 13.5.2 TIMER1 OSCILLATOR LAYOUT CONSIDERATIONS

The Timer1 oscillator circuit draws very little power during operation. Due to the low-power nature of the oscillator, it may also be sensitive to rapidly changing signals in close proximity. This is especially true when the oscillator is configured for extremely Low-Power mode (SOSCSEL<1:0> = 01).

The oscillator circuit, displayed in Figure 13-2, should be located as close as possible to the microcontroller. There should be no circuits passing within the oscillator circuit boundaries other than VSS or VDD.

If a high-speed circuit must be located near the oscillator (such as the ECCP1 pin in Output Compare or PWM mode, or the primary oscillator using the OSC2 pin), a grounded guard ring around the oscillator circuit, as displayed in Figure 13-3, may be helpful when used on a single-sided PCB or in addition to a ground plane.

#### FIGURE 13-3: OSCILLATOR CIRCUIT WITH GROUNDED GUARD RING

In the Low Drive Level mode (SOSCSEL<1:0> = 01), it is critical that the RC2 I/O pin signals be kept away from the oscillator circuit. Configuring RC2 as a digital output, and toggling it, can potentially disturb the oscillator circuit, even with relatively good PCB layout. If possible, it is recommended to either leave RC2 unused, or use it as an input pin with a slew rate limited signal source. If RC2 must be used as a digital output, it may be necessary to use the Higher Drive Level Oscillator mode (SOSCSEL<1:0> = 11) with many PCB layouts. Even in the High Drive Level mode, careful layout procedures should still be followed when designing the oscillator circuit.

In addition to dV/dt induced noise considerations, it is also important to ensure that the circuit board is clean. Even a very small amount of conductive soldering flux residue can cause PCB leakage currents which can overwhelm the oscillator circuit.

## 13.6 Timer1 Interrupt

The TMR1 register pair (TMR1H:TMR1L) increments from 0000h to FFFFh and rolls over to 0000h. The Timer1 interrupt, if enabled, is generated on overflow which is latched in interrupt flag bit, TMR1IF (PIR1<0>). This interrupt can be enabled or disabled by setting or clearing the Timer1 Interrupt Enable bit, TMR1IE (PIE1<0>).

#### 13.8.2 TIMER1 GATE SOURCE SELECTION

The Timer1 gate source can be selected from one of four different sources. Source selection is controlled by the T1GSSx bits of the T1GCON register. The polarity for each available source is also selectable. Polarity selection is controlled by the T1GPOL bit of the T1GCON register.

TABLE 13-4: TIMER1 GATE SOURCES

| T1GSS<1:0> | Timer1 Gate Source  |

|------------|---------------------|

| 00         | Timer1 Gate Pin     |

| 01         | TMR2 matches PR2    |

| 10         | Comparator 1 output |

| 11         | Comparator 2 output |

13.8.2.1 T1G Pin Gate Operation

The T1G pin is one source for Timer1 gate control. It can be used to supply an external source to the Timer1 gate circuitry.

#### 13.8.2.2 Timer2 Match Gate Operation

The TMR2 register will increment until it matches the value in the PR2 register. On the very next increment cycle, TMR2 will be reset to 00h. When this Reset occurs, a low-to-high pulse will automatically be generated and internally supplied to the Timer1 gate circuitry.

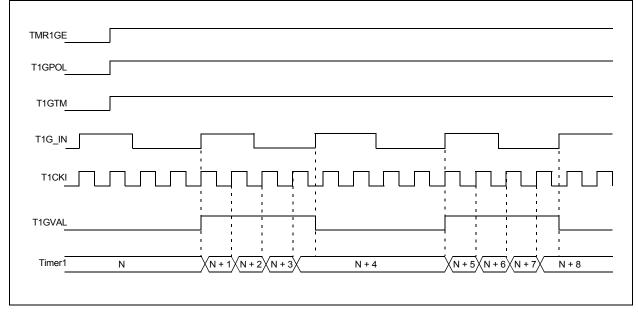

#### 13.8.3 TIMER1 GATE TOGGLE MODE

When Timer1 Gate Toggle mode is enabled, it is possible to measure the full cycle length of a Timer1 gate signal, as opposed to the duration of a single level pulse.

The Timer1 gate source is routed through a flip-flop that changes state on every incrementing edge of the signal. See Figure 13-5 for timing details.

The T1GVAL bit will indicate when the Toggled mode is active and the timer is counting.

The Timer1 Gate Toggle mode is enabled by setting the T1GTM bit of the T1GCON register. When the T1GTM bit is cleared, the flip-flop is cleared and held clear. This is necessary in order to control which edge is measured.

#### FIGURE 13-5: TIMER1 GATE TOGGLE MODE

| R/W-0         | R/W-0                                                                                                                    | R/W-0            | R/W-0          | R/W-0            | R/W-0            | R/W-0           | R/W-0       |  |  |  |  |

|---------------|--------------------------------------------------------------------------------------------------------------------------|------------------|----------------|------------------|------------------|-----------------|-------------|--|--|--|--|

| ALRMEN        | CHIME                                                                                                                    | AMASK3           | AMASK2         | AMASK1           | AMASK0           | ALRMPTR1        | ALRMPTR0    |  |  |  |  |

| bit 7         |                                                                                                                          |                  |                |                  |                  |                 | bit (       |  |  |  |  |

| Legend:       |                                                                                                                          |                  |                |                  |                  |                 |             |  |  |  |  |

| R = Readable  | e bit                                                                                                                    | W = Writable     | bit            | U = Unimpler     | mented bit, rea  | d as '0'        |             |  |  |  |  |

| -n = Value at | POR                                                                                                                      | '1' = Bit is set |                | '0' = Bit is cle | ared             | x = Bit is unki | nown        |  |  |  |  |

|               |                                                                                                                          |                  |                |                  |                  |                 |             |  |  |  |  |

| bit 7         |                                                                                                                          | arm Enable bit   |                |                  |                  |                 |             |  |  |  |  |

|               |                                                                                                                          |                  | ed automatical | y after an alarr | n event whene    | ver ARPT<7:0>   | = 0000 0000 |  |  |  |  |

|               | and CHII<br>0 = Alarm is                                                                                                 | ,                |                |                  |                  |                 |             |  |  |  |  |

| bit 6         | CHIME: Chim                                                                                                              |                  |                |                  |                  |                 |             |  |  |  |  |

|               |                                                                                                                          |                  | T<7:0> bits ar | e allowed to ro  | oll over from 00 | h to FFh        |             |  |  |  |  |

|               |                                                                                                                          | disabled; ARF    |                |                  |                  |                 |             |  |  |  |  |

| bit 5-2       | AMASK<3:0                                                                                                                | >: Alarm Mask    | Configuration  | bits             |                  |                 |             |  |  |  |  |

|               | 0000 = Every half second                                                                                                 |                  |                |                  |                  |                 |             |  |  |  |  |

|               | 0001 = Every second                                                                                                      |                  |                |                  |                  |                 |             |  |  |  |  |

|               | 0010 = Every 10 seconds<br>0011 = Every minute                                                                           |                  |                |                  |                  |                 |             |  |  |  |  |

|               | 0100 = Ever                                                                                                              |                  |                |                  |                  |                 |             |  |  |  |  |

|               | 0101 = Ever                                                                                                              |                  |                |                  |                  |                 |             |  |  |  |  |

|               | 0110 = Once<br>0111 = Once                                                                                               |                  |                |                  |                  |                 |             |  |  |  |  |

|               |                                                                                                                          |                  |                |                  |                  |                 |             |  |  |  |  |

|               | 1000 = Once a month<br>1001 = Once a year (except when configured for February 29 <sup>th</sup> , once every four years) |                  |                |                  |                  |                 |             |  |  |  |  |

|               | 101x = Reserved - do not use                                                                                             |                  |                |                  |                  |                 |             |  |  |  |  |

|               |                                                                                                                          | erved – do not   |                |                  |                  |                 |             |  |  |  |  |

| bit 1-0       |                                                                                                                          | :0>: Alarm Val   | -              |                  |                  |                 |             |  |  |  |  |

|               | Points to the corresponding Alarm Value registers when reading the ALRMVALH and ALRMVALL                                 |                  |                |                  |                  |                 |             |  |  |  |  |

|               | registers. The ALRMPTR<1:0> value decrements on every read or write of ALRMVALH until it reaches<br>'00'.                |                  |                |                  |                  |                 |             |  |  |  |  |

|               | 00.<br>ALRMVAL<15:8>:                                                                                                    |                  |                |                  |                  |                 |             |  |  |  |  |

|               | 00 = ALRMMIN                                                                                                             |                  |                |                  |                  |                 |             |  |  |  |  |

|               | 01 = ALRMWD                                                                                                              |                  |                |                  |                  |                 |             |  |  |  |  |

|               | 10 = ALRMM<br>11 = Unimple                                                                                               |                  |                |                  |                  |                 |             |  |  |  |  |

|               | <u>ALRMVAL&lt;7</u>                                                                                                      |                  |                |                  |                  |                 |             |  |  |  |  |

|               | 00 = ALRMS                                                                                                               |                  |                |                  |                  |                 |             |  |  |  |  |

|               | 01 = ALRMH                                                                                                               |                  |                |                  |                  |                 |             |  |  |  |  |

|               | 10 = ALRMD                                                                                                               |                  |                |                  |                  |                 |             |  |  |  |  |

|               | 11 = Unimple                                                                                                             | emented          |                |                  |                  |                 |             |  |  |  |  |

## REGISTER 17-4: ALRMCFG: ALARM CONFIGURATION REGISTER (ACCESS F47h)

# 19.0 ENHANCED CAPTURE/COMPARE/PWM (ECCP) MODULE

PIC18F47J53 family devices have three Enhanced Capture/Compare/PWM (ECCP) modules: ECCP1, ECCP2 and ECCP3. These modules contain a 16-bit register, which can operate as a 16-bit Capture register, a 16-bit Compare register or a PWM Master/Slave Duty Cycle register. These ECCP modules are upwardly compatible with CCP.

Note: Throughout this section, generic references are used for register and bit names that are the same – except for an 'x' variable that indicates the item's association with the ECCP1, ECCP2 or ECCP3 module. For example, the control register is named CCPxCON and refers to CCP1CON, CCP2CON and CCP3CON. The ECCP modules are implemented as standard CCP modules with enhanced PWM capabilities. These include:

- · Provision for two or four output channels

- · Output Steering modes

- · Programmable polarity

- Programmable dead-band control

- Automatic shutdown and restart

The enhanced features are discussed in detail in Section 19.4 "PWM (Enhanced Mode)".

| R/W-0        | R/W-0                                                                                                                                                         | R/W-0                                                    | R/W-0           | R/W-0             | R/W-0            | R/W-0             | R/W-0          |  |  |  |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|-----------------|-------------------|------------------|-------------------|----------------|--|--|--|

| PxM1         | PxM0                                                                                                                                                          | DCxB1                                                    | DCxB0           | CCPxM3            | CCPxM2           | CCPxM1            | CCPxM0         |  |  |  |

| bit 7        |                                                                                                                                                               |                                                          |                 |                   |                  |                   | bit (          |  |  |  |

| Legend:      |                                                                                                                                                               |                                                          |                 |                   |                  |                   |                |  |  |  |

| R = Readab   | le bit                                                                                                                                                        | W = Writable                                             | bit             | U = Unimplen      | nented bit, read | d as '0'          |                |  |  |  |

| -n = Value a | t POR                                                                                                                                                         | '1' = Bit is set                                         |                 | '0' = Bit is cle  | ared             | x = Bit is unkr   | nown           |  |  |  |

| bit 7-6      | <u>lf CCPxM&lt;3:</u><br>xx =  PxA as                                                                                                                         | Enhanced PWM<br>2> = 00, 01, 10<br>ssigned as capt       | <u>):</u>       | -                 | B, PxC and Px    | D assigned as     | port pins      |  |  |  |

|              | Steeri                                                                                                                                                        | output: PxA, P<br>n <b>g Mode</b> ")<br>idge output forv |                 |                   | -                |                   | 19.4.7 "Pulse  |  |  |  |

|              | port pi                                                                                                                                                       |                                                          |                 |                   |                  |                   | D assigned a   |  |  |  |

| bit 5-4      | <ul> <li>11 = Full-bridge output reverse: PxB modulated; PxC active; PxA and PxD inactive</li> <li>DCxB&lt;1:0&gt;: PWM Duty Cycle bit 1 and bit 0</li> </ul> |                                                          |                 |                   |                  |                   |                |  |  |  |

|              | <u>Capture mode:</u><br>Unused.                                                                                                                               |                                                          |                 |                   |                  |                   |                |  |  |  |

|              | Compare mode:                                                                                                                                                 |                                                          |                 |                   |                  |                   |                |  |  |  |

|              | Unused.                                                                                                                                                       |                                                          |                 |                   |                  |                   |                |  |  |  |

|              | PWM mode:<br>These bits ar<br>in ECCPRxL                                                                                                                      | e the two LSbs                                           | of the 10-bit F | WM duty cycle     | . The eight MS   | bs of the duty c  | ycle are found |  |  |  |

| bit 3-0      | CCPxM<3:0>: ECCPx Mode Select bits                                                                                                                            |                                                          |                 |                   |                  |                   |                |  |  |  |

|              | 0000 = Capture/Compare/PWM off (resets ECCPx module)<br>0001 = Reserved                                                                                       |                                                          |                 |                   |                  |                   |                |  |  |  |

|              | 0010 = Compare mode, toggle output on match<br>0011 = Capture mode                                                                                            |                                                          |                 |                   |                  |                   |                |  |  |  |

|              | 0100 = Capture mode; every falling edge                                                                                                                       |                                                          |                 |                   |                  |                   |                |  |  |  |

|              | 0101 = Capture mode; every rising edge<br>0110 = Capture mode; every fourth rising edge                                                                       |                                                          |                 |                   |                  |                   |                |  |  |  |

|              |                                                                                                                                                               | oture mode; eve<br>oture mode; eve                       |                 |                   |                  |                   |                |  |  |  |

|              |                                                                                                                                                               | npare mode; ini                                          | , ,             | 0                 | tout on compa    | re match (set C   | CPxIF)         |  |  |  |

|              |                                                                                                                                                               | npare mode; ini                                          |                 |                   |                  |                   |                |  |  |  |

|              | 1010 = Cor                                                                                                                                                    | npare mode; ge                                           | nerate softwa   | re interrupt only | y, ECCPx pin r   | everts to I/O sta | ite            |  |  |  |

|              | sets                                                                                                                                                          | mpare mode; trig<br>s CCPxIF bit)                        |                 | -                 |                  |                   | /D conversior  |  |  |  |

|              |                                                                                                                                                               | M mode; PxA a                                            |                 |                   |                  |                   |                |  |  |  |

|              |                                                                                                                                                               | M mode; PxA a                                            |                 | <b>U</b> .        |                  |                   |                |  |  |  |

|              | 1110 = PW                                                                                                                                                     | M mode; PxA a                                            | nd PxC active   | e-low; PxB and    | PxD active-hig   | n                 |                |  |  |  |

1111 = PWM mode; PxA and PxC active-low; PxB and PxD active-low

#### 20.3.1 REGISTERS

Each MSSP module has four registers for SPI mode operation. These are:

- MSSPx Control Register 1 (SSPxCON1)

- MSSPx Status Register (SSPxSTAT)

- Serial Receive/Transmit Buffer Register (SSPxBUF)

- MSSPx Shift Register (SSPxSR) Not directly accessible

SSPxCON1 and SSPxSTAT are the control and status registers in SPI mode operation. The SSPxCON1 register is readable and writable. The lower six bits of the SSPxSTAT are read-only. The upper two bits of the SSPxSTAT are read/write.

SSPxSR is the shift register used for shifting data in or out. SSPxBUF is the buffer register to which data bytes are written to or read from.

In receive operations, SSPxSR and SSPxBUF together, create a double-buffered receiver. When SSPxSR receives a complete byte, it is transferred to SSPxBUF and the SSPxIF interrupt is set.

During transmission, the SSPxBUF is not double-buffered. A write to SSPxBUF will write to both SSPxBUF and SSPxSR.

#### REGISTER 20-1: SSPxSTAT: MSSPx STATUS REGISTER (SPI MODE) (ACCESS 1, FC7h; 2, F73h)

|                                                                      |                            |                                   |                  | •                 | , ,            |                 |            |

|----------------------------------------------------------------------|----------------------------|-----------------------------------|------------------|-------------------|----------------|-----------------|------------|

| R/W-1                                                                | R/W-1                      | R-1                               | R-1              | R-1               | R-1            | R-1             | R-1        |

| SMP                                                                  | CKE <sup>(1)</sup>         | D/Ā                               | Р                | S                 | R/W            | UA              | BF         |

| bit 7                                                                |                            |                                   |                  |                   |                |                 | bit 0      |

|                                                                      |                            |                                   |                  |                   |                |                 |            |

| Legend:                                                              |                            |                                   |                  |                   |                |                 |            |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                            |                                   |                  |                   |                |                 |            |

| -n = Value a                                                         | It POR                     | '1' = Bit is set                  |                  | '0' = Bit is clea | ared           | x = Bit is unkr | nown       |

|                                                                      |                            |                                   |                  |                   |                |                 |            |

| bit 7                                                                | SMP: Sample                |                                   |                  |                   |                |                 |            |

|                                                                      | SPI Master m               |                                   | 1.5.1.1.         |                   |                |                 |            |

|                                                                      |                            | a sampled at er<br>a sampled at m |                  |                   |                |                 |            |

|                                                                      | SPI Slave mo               | •                                 |                  |                   |                |                 |            |

|                                                                      |                            | e cleared when                    | SPI is used in   | Slave mode.       |                |                 |            |

| bit 6                                                                | CKE: SPI Clo               | ock Select bit <sup>(1)</sup>     |                  |                   |                |                 |            |

|                                                                      | 1 = Transmit               | occurs on trans                   | sition from act  | ve to Idle clock  | state          |                 |            |

|                                                                      | 0 = Transmit               | occurs on trans                   | sition from Idle | to active clock   | state          |                 |            |

| bit 5                                                                | D/A: Data/Ad               |                                   |                  |                   |                |                 |            |

|                                                                      | Used in I <sup>2</sup> C n | node only.                        |                  |                   |                |                 |            |

| bit 4                                                                | P: Stop bit                |                                   |                  |                   |                |                 |            |

|                                                                      |                            | node only; this                   | bit is cleared v | when the MSSP     | module is disa | bled, SSPEN i   | s cleared. |

| bit 3                                                                | S: Start bit               |                                   |                  |                   |                |                 |            |

|                                                                      | Used in I <sup>2</sup> C n | ,                                 |                  |                   |                |                 |            |

| bit 2                                                                |                            | /rite Information                 | n bit            |                   |                |                 |            |

|                                                                      | Used in I <sup>2</sup> C n | node only.                        |                  |                   |                |                 |            |

| bit 1                                                                | UA: Update A               |                                   |                  |                   |                |                 |            |

|                                                                      | Used in I <sup>2</sup> C n | node only.                        |                  |                   |                |                 |            |

| bit 0                                                                | BF: Buffer Fu              |                                   |                  |                   |                |                 |            |

|                                                                      |                            | complete, SSP                     |                  |                   |                |                 |            |

|                                                                      | 0 = Receive r              | not complete, S                   | SPXBUF is er     | npty              |                |                 |            |

| Note 1: F                                                            | Polarity of the clo        | ock state is set l                | by the CKP bit   | (SSPxCON1<4       | >).            |                 |            |

|                                                                      |                            |                                   |                  |                   |                |                 |            |

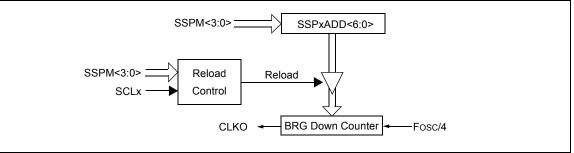

#### 20.5.7.1 Baud Rate and Module Interdependence

Because MSSP1 and MSSP2 are independent, they can operate simultaneously in  $I^2C$  Master mode at different baud rates. This is done by using different BRG reload values for each module.

Because this mode derives its basic clock source from the system clock, any changes to the clock will affect both modules in the same proportion. It may be possible to change one or both baud rates back to a previous value by changing the BRG reload value.

## FIGURE 20-19: BAUD RATE GENERATOR BLOCK DIAGRAM

## TABLE 20-3: I<sup>2</sup>C CLOCK RATE w/BRG

| Fosc   | Fcy    | Fcy * 2 | BRG Value | FscL<br>(2 Rollovers of BRG) |

|--------|--------|---------|-----------|------------------------------|

| 40 MHz | 10 MHz | 20 MHz  | 18h       | 400 kHz <sup>(1)</sup>       |

| 40 MHz | 10 MHz | 20 MHz  | 1Fh       | 312.5 kHz                    |

| 40 MHz | 10 MHz | 20 MHz  | 63h       | 100 kHz                      |

| 16 MHz | 4 MHz  | 8 MHz   | 09h       | 400 kHz <sup>(1)</sup>       |

| 16 MHz | 4 MHz  | 8 MHz   | 0Ch       | 308 kHz                      |

| 16 MHz | 4 MHz  | 8 MHz   | 27h       | 100 kHz                      |

| 4 MHz  | 1 MHz  | 2 MHz   | 02h       | 333 kHz <sup>(1)</sup>       |

| 4 MHz  | 1 MHz  | 2 MHz   | 09h       | 100 kHz                      |

| 4 MHz  | 1 MHz  | 2 MHz   | 00h       | 1 MHz <sup>(1)</sup>         |

**Note 1:** The I<sup>2</sup>C interface does not conform to the 400 kHz I<sup>2</sup>C specification (which applies to rates greater than 100 kHz) in all details, but may be used with care where higher rates are required by the application.

| Name                   | Bit 7                                                                                                                | Bit 6           | Bit 5                    | Bit 4                 | Bit 3                 | Bit 2                       | Bit 1        | Bit 0  |

|------------------------|----------------------------------------------------------------------------------------------------------------------|-----------------|--------------------------|-----------------------|-----------------------|-----------------------------|--------------|--------|

| INTCON                 | GIE/GIEH                                                                                                             | PEIE/GIEL       | TMR0IE                   | INT0IE                | RBIE                  | TMR0IF                      | INT0IF       | RBIF   |

| PIR1                   | PMPIF <sup>(3)</sup>                                                                                                 | ADIF            | RC1IF                    | TX1IF                 | SSP1IF                | CCP1IF                      | TMR2IF       | TMR1IF |

| PIE1                   | PMPIE <sup>(3)</sup>                                                                                                 | ADIE            | RC1IE                    | TX1IE                 | SSP1IE                | CCP1IE                      | TMR2IE       | TMR1IE |