Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 48MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART, USB                               |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                        |

| Number of I/O              | 22                                                                           |

| Program Memory Size        | 128KB (64K x 16)                                                             |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 3.8K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 2.75V                                                                   |

| Data Converters            | A/D 10x10b/12b                                                               |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                               |

| Supplier Device Package    | 28-SSOP                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf27j53t-i-ss |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TABLE 1-1: DEVICE FEATURES FOR THE PIC18F2XJ53 (28-PIN DEVICES)

| Features                             | PIC18F26J53                                                                      | PIC18F27J53            |  |  |

|--------------------------------------|----------------------------------------------------------------------------------|------------------------|--|--|

| Operating Frequency                  | DC – 48 MHz                                                                      | DC – 48 MHz            |  |  |

| Program Memory (Kbytes)              | 64                                                                               | 128                    |  |  |

| Program Memory (Instructions)        | 32,768                                                                           | 65,536                 |  |  |

| Data Memory (Kbytes)                 | 3.8                                                                              | 3.8                    |  |  |

| Interrupt Sources                    | 3                                                                                | 0                      |  |  |

| I/O Ports                            | Ports A, B, C                                                                    |                        |  |  |

| Timers                               | 8                                                                                |                        |  |  |

| Enhanced Capture/Compare/PWM Modules | 3 ECCP a                                                                         | Ind 7 CCP              |  |  |

| Serial Communications                | MSSP (2), Enhance                                                                | ed USART (2), USB      |  |  |

| Parallel Communications (PMP/PSP)    | N                                                                                | lo                     |  |  |

| 10/12-Bit Analog-to-Digital Module   | 10 Input                                                                         | Channels               |  |  |

| Resets (and Delays)                  | POR, BOR, RESET Instruction, Stack Full, Stack Underflow, MCLR, W<br>(PWRT, OST) |                        |  |  |

| Instruction Set                      | 75 Instructions, 83 with Extended Instruction Set Enabled                        |                        |  |  |

| Packages                             | 28-Pin QFN, SOIC, SSO                                                            | OP and SPDIP (300 mil) |  |  |

## TABLE 1-2:DEVICE FEATURES FOR THE PIC18F4XJ53 (44-PIN DEVICES)

| Features                             | PIC18F46J53                                               | PIC18F47J53       |  |  |

|--------------------------------------|-----------------------------------------------------------|-------------------|--|--|

| Operating Frequency                  | DC – 48 MHz                                               | DC – 48 MHz       |  |  |

| Program Memory (Kbytes)              | 64                                                        | 128               |  |  |

| Program Memory (Instructions)        | 32,768                                                    | 65,536            |  |  |

| Data Memory (Kbytes)                 | 3.8                                                       | 3.8               |  |  |

| Interrupt Sources                    | 3                                                         | 0                 |  |  |

| I/O Ports                            | Ports A, B, C, D, E                                       |                   |  |  |

| Timers                               | 8                                                         |                   |  |  |

| Enhanced Capture/Compare/PWM Modules | 3 ECCP and 7 CCP                                          |                   |  |  |

| Serial Communications                | MSSP (2), Enhance                                         | ed USART (2), USB |  |  |

| Parallel Communications (PMP/PSP)    | Yes                                                       |                   |  |  |

| 10/12-Bit Analog-to-Digital Module   | 13 Input Channels                                         |                   |  |  |

| Resets (and Delays)                  | < Full, Stack Underflow, MCLR, WDT<br>T, OST)             |                   |  |  |

| Instruction Set                      | 75 Instructions, 83 with Extended Instruction Set Enabled |                   |  |  |

| Packages                             | 44-Pin QFN and TQFP                                       |                   |  |  |

| 28-SPDIP/<br>SSOP/<br>SOIC | 28-QFN                                | Pin<br>Type                                     | Buffer<br>Type                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Description                                                                                                                                                                                                                                                                                                                                                                                          |  |

|----------------------------|---------------------------------------|-------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1 <sup>(2)</sup>           |                                       |                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Description                                                                                                                                                                                                                                                                                                                                                                                          |  |

|                            | 26 <sup>(2)</sup>                     | I                                               | ST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Master Clear (Reset) input. This pin is an active-low Reset to the device.                                                                                                                                                                                                                                                                                                                           |  |

| 9                          | 6                                     | I                                               | ST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Oscillator crystal or external clock input.<br>Oscillator crystal input or external clock source<br>input. ST buffer when configured in RC mode;<br>CMOS otherwise. Main oscillator input<br>connection.                                                                                                                                                                                             |  |

|                            |                                       | I                                               | CMOS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | External clock source input; always associated with pin function OSC1 (see related OSC1/CLKI pins).                                                                                                                                                                                                                                                                                                  |  |

|                            |                                       | I/O                                             | TTL/DIG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Digital I/O.                                                                                                                                                                                                                                                                                                                                                                                         |  |

| 10                         | 7                                     | 0                                               | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Oscillator crystal or clock output.<br>Oscillator crystal output. Connects to crystal or<br>resonator in Crystal Oscillator mode.                                                                                                                                                                                                                                                                    |  |

|                            |                                       | 0                                               | DIG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Main oscillator feedback output connection.<br>In RC mode, OSC2 pin outputs CLKO, which<br>has 1/4 the frequency of OSC1 and denotes<br>the instruction cycle rate.                                                                                                                                                                                                                                  |  |

|                            |                                       | I/O                                             | TTL/DIG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| igger input w              | ith CMOS                              | levels                                          | Ar<br>O<br>Ol                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| t                          | 10<br>Datible input<br>rigger input w | 10 7<br>batible input<br>rigger input with CMOS | I     I       I     I       I     I/O       I     I       I     I       I     I       I     I       I     I       I     I       I     I       I     I       I     I       I     I       I     I       I     I       I     I       I     I       I     I       I     I       < | I     ST       I     CMOS       I     II/O       I     TTL/DIG       I     I/O       I     I |  |

TABLE 1-3:

PIC18F2XJ53 PINOUT I/O DESCRIPTIONS

Note 1: RA7 and RA6 will be disabled if OSC1 and OSC2 are used for the clock function.

2: 5.5V tolerant.

| Mada                         | DSCONH<7>           | oscco                | OSCCON<7,1:0> |                               | Clocking    | Ausilable Clask and Ossillator Source                                              |  |  |  |  |

|------------------------------|---------------------|----------------------|---------------|-------------------------------|-------------|------------------------------------------------------------------------------------|--|--|--|--|

| Mode                         | DSEN <sup>(1)</sup> | IDLEN <sup>(1)</sup> | SCS<1:0>      | CPU                           | Peripherals | Available Clock and Oscillator Source                                              |  |  |  |  |

| Sleep                        | 0                   | 0                    | N/A           | Off                           | Off         | Timer1 oscillator and/or RTCC may optionally be enabled                            |  |  |  |  |

| Deep<br>Sleep <sup>(3)</sup> | 1                   | 0                    | N/A           | Powered<br>off <sup>(2)</sup> | Powered off | RTCC can run uninterrupted using the Timer1 or<br>internal low-power RC oscillator |  |  |  |  |

| PRI_RUN                      | 0                   | N/A                  | 00            | Clocked                       | Clocked     | The normal, full-power execution mode; primary clock source (defined by FOSC<2:0>) |  |  |  |  |

| SEC_RUN                      | 0                   | N/A                  | 01            | Clocked                       | Clocked     | Secondary – Timer1 oscillator                                                      |  |  |  |  |

| RC_RUN                       | 0                   | N/A                  | 11            | Clocked                       | Clocked     | Postscaled internal clock                                                          |  |  |  |  |

| PRI_IDLE                     | 0                   | 1                    | 00            | Off                           | Clocked     | Primary clock source (defined by FOSC<2:0>)                                        |  |  |  |  |

| SEC_IDLE                     | 0                   | 1                    | 01            | Off                           | Clocked     | Secondary – Timer1 oscillator                                                      |  |  |  |  |

| RC_IDLE                      | 0                   | 1                    | 11            | Off                           | Clocked     | Postscaled internal clock                                                          |  |  |  |  |

### TABLE 4-1:LOW-POWER MODES

Note 1: IDLEN and DSEN reflect their values when the SLEEP instruction is executed.

2: Deep Sleep turns off the internal core voltage regulator to power down core logic. See Section 4.6 "Deep Sleep Mode" for more information.

3: Deep Sleep mode is only available on "F" devices, not "LF" devices.

## 4.1.3 CLOCK TRANSITIONS AND STATUS INDICATORS

The length of the transition between clock sources is the sum of two cycles of the old clock source and three to four cycles of the new clock source. This formula assumes that the new clock source is stable.

Two bits indicate the current clock source and its status: OSTS (OSCCON<3>) and SOSCRUN (OSC-CON2<6>). In general, only one of these bits will be set in a given power-managed mode. When the OSTS bit is set, the primary clock would be providing the device clock. When the SOSCRUN bit is set, the Timer1 oscillator would be providing the clock. If neither of these bits is set, INTRC would be clocking the device.

| Note: | Executing a SLEEP instruction does not     |

|-------|--------------------------------------------|

|       | necessarily place the device into Sleep    |

|       | mode. It acts as the trigger to place the  |

|       | controller into either the Sleep or Deep   |

|       | Sleep mode, or one of the Idle modes,      |

|       | depending on the setting of the IDLEN bit. |

### 4.1.4 MULTIPLE SLEEP COMMANDS

The power-managed mode that is invoked with the SLEEP instruction is determined by the setting of the IDLEN and DSEN bits at the time the instruction is executed. If another SLEEP instruction is executed, the device will enter the power-managed mode specified by IDLEN and DSEN at that time. If IDLEN or DSEN have changed, the device will enter the new power-managed mode specified by the new setting.

## REGISTER 10-42: RPOR21: PERIPHERAL PIN SELECT OUTPUT REGISTER 21 (BANKED ED5h)<sup>(1)</sup>

| U-0   | U-0 | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|-----|--------|--------|--------|--------|--------|

| —     | —   |     | RP21R4 | RP21R3 | RP21R2 | RP21R1 | RP21R0 |

| bit 7 |     |     |        |        |        |        | bit 0  |

| Legend:           | $R/\overline{W}$ = Readable bit, Writable bit if IOLOCK = 0 |                                    |                    |  |  |

|-------------------|-------------------------------------------------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit                                            | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set                                            | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP21R<4:0>:** Peripheral Output Function is Assigned to RP21 Output Pin bits (see Table 10-14 for peripheral function numbers)

Note 1: RP21 pins are not available on 28-pin devices.

## REGISTER 10-43: RPOR22: PERIPHERAL PIN SELECT OUTPUT REGISTER 22 (BANKED ED6h)<sup>(1)</sup>

| U-0   | U-0 | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|-----|--------|--------|--------|--------|--------|

| —     | —   | —   | RP22R4 | RP22R3 | RP22R2 | RP22R1 | RP22R0 |

| bit 7 |     |     |        |        |        |        | bit 0  |

| Legend:           | $R/\overline{W}$ = Readable bit, Writable bit if IOLOCK = 0 |                                    |                    |  |  |

|-------------------|-------------------------------------------------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit                                            | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set                                            | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP22R<4:0>:** Peripheral Output Function is Assigned to RP22 Output Pin bits (see Table 10-14 for peripheral function numbers)

Note 1: RP22 pins are not available on 28-pin devices.

### REGISTER 10-44: RPOR23: PERIPHERAL PIN SELECT OUTPUT REGISTER 23 (BANKED ED7h)<sup>(1)</sup>

| U-0   | U-0 | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|-----|--------|--------|--------|--------|--------|

| —     | —   | —   | RP23R4 | RP23R3 | RP23R2 | RP23R1 | RP23R0 |

| bit 7 |     |     |        |        |        |        | bit 0  |

| Legend:           | $R/\overline{W}$ = Readable bit, Writable bit if IOLOCK = 0 |                                    |                    |  |  |

|-------------------|-------------------------------------------------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit                                            | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set                                            | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP23R<4:0>:** Peripheral Output Function is Assigned to RP23 Output Pin bits (see Table 10-14 for peripheral function numbers)

Note 1: RP23 pins are not available on 28-pin devices.

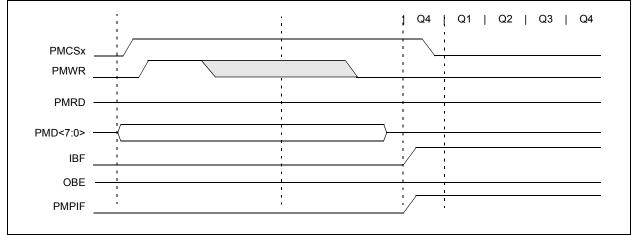

### 11.2.2 WRITE TO SLAVE PORT

When chip select is active and a write strobe occurs (PMCSx = 1 and PMWR = 1), the data from PMD<7:0> is captured into the lower PMDIN1L register. The PMPIF and IBF flag bits are set when the write ends. The timing for the control signals in Write mode is displayed in Figure 11-3. The polarity of the control signals are configurable.

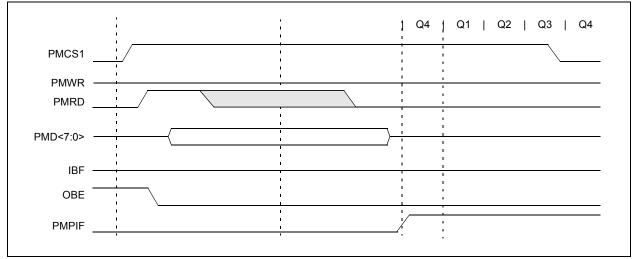

## 11.2.3 READ FROM SLAVE PORT

When chip select is active and a read strobe occurs (PMCSx = 1 and PMRD = 1), the data from the PMD-OUT1L register (PMDOUT1L<7:0>) is presented on to PMD<7:0>. Figure 11-4 provides the timing for the control signals in Read mode.

### FIGURE 11-4: PARALLEL SLAVE PORT READ WAVEFORMS

### 13.8.2 TIMER1 GATE SOURCE SELECTION

The Timer1 gate source can be selected from one of four different sources. Source selection is controlled by the T1GSSx bits of the T1GCON register. The polarity for each available source is also selectable. Polarity selection is controlled by the T1GPOL bit of the T1GCON register.

TABLE 13-4: TIMER1 GATE SOURCES

| T1GSS<1:0> | Timer1 Gate Source  |

|------------|---------------------|

| 00         | Timer1 Gate Pin     |

| 01         | TMR2 matches PR2    |

| 10         | Comparator 1 output |

| 11         | Comparator 2 output |

13.8.2.1 T1G Pin Gate Operation

The T1G pin is one source for Timer1 gate control. It can be used to supply an external source to the Timer1 gate circuitry.

### 13.8.2.2 Timer2 Match Gate Operation

The TMR2 register will increment until it matches the value in the PR2 register. On the very next increment cycle, TMR2 will be reset to 00h. When this Reset occurs, a low-to-high pulse will automatically be generated and internally supplied to the Timer1 gate circuitry.

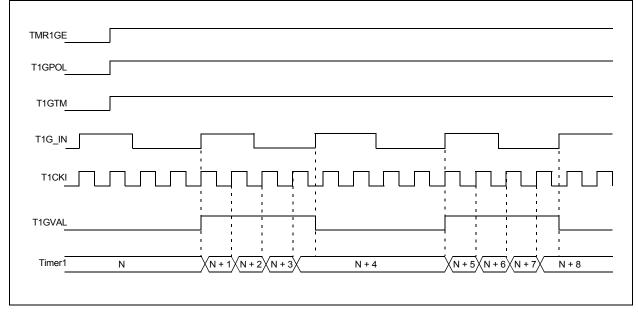

### 13.8.3 TIMER1 GATE TOGGLE MODE

When Timer1 Gate Toggle mode is enabled, it is possible to measure the full cycle length of a Timer1 gate signal, as opposed to the duration of a single level pulse.

The Timer1 gate source is routed through a flip-flop that changes state on every incrementing edge of the signal. See Figure 13-5 for timing details.

The T1GVAL bit will indicate when the Toggled mode is active and the timer is counting.

The Timer1 Gate Toggle mode is enabled by setting the T1GTM bit of the T1GCON register. When the T1GTM bit is cleared, the flip-flop is cleared and held clear. This is necessary in order to control which edge is measured.

### FIGURE 13-5: TIMER1 GATE TOGGLE MODE

## 18.0 CAPTURE/COMPARE/PWM (CCP) MODULES

PIC18F47J53 family devices have seven CCP (Capture/Compare/PWM) modules, designated CCP4 through CCP10. All the modules implement standard Capture, Compare and Pulse-Width Modulation (PWM) modes.

Note: Throughout this section, generic references are used for register and bit names that are the same – except for an 'x' variable that indicates the item's association with the specific CCP module. For example, the control register is named CCPxCON and refers to CCP4CON through CCP10CON. Each CCP module contains a 16-bit register that can operate as a 16-bit Capture register, a 16-bit Compare register or a PWM Master/Slave Duty Cycle register. For the sake of clarity, all CCP module operation in the following sections is described with respect to CCP4, but is equally applicable to CCP5 through CCP10.

# REGISTER 18-1: CCPxCON: CCP4-10 CONTROL REGISTER (4, BANKED F12h; 5, F0Fh; 6, F0Ch; 7, F09h; 8, F06h; 9, F03h; 10, F00h)

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|-------|-------|--------|--------|--------|--------|

| —     | —   | DCxB1 | DCxB0 | CCPxM3 | CCPxM2 | CCPxM1 | CCPxM0 |

| bit 7 |     |       |       |        |        |        | bit 0  |

### Legend:

| U                 |                  |                                    |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

### bit 7-6 Unimplemented: Read as '0'

bit 5-4 DCxB<1:0>: PWM Duty Cycle bit 1 and bit 0 for CCPx Module Capture mode: Unused. Compare mode: Unused. PWM mode: These bits are the two Least Significant bits (bit 1 and bit 0) of the 10-bit PWM duty cycle. The eight Most Significant bits (DCxB<9:2>) of the duty cycle are found in CCPRxL. bit 3-0 CCPxM<3:0>: CCPx Module Mode Select bits 0000 = Capture/Compare/PWM disabled (resets CCPx module) 0001 = Reserved 0010 = Compare mode, toggle output on match (CCPxIF bit is set) 0011 = Reserved 0100 = Capture mode: every falling edge 0101 = Capture mode: every rising edge 0110 = Capture mode: every 4th rising edge 0111 = Capture mode: every 16th rising edge 1000 = Compare mode: initialize CCPx pin low; on compare match, force CCPx pin high (CCPxIF bit is set) 1001 = Compare mode: initialize CCPx pin high; on compare match, force CCPx pin low (CCPxIF bit is set) 1010 = Compare mode: generate software interrupt on compare match (CCPxIF bit is set, CCPx pin reflects I/O state) 1011 = Compare mode: Special Event Trigger; reset timer on CCPx match (CCPxIF bit is set)

11xx = PWM mode

**Note 1:** CCPxM<3:0> = 1011 will only reset timer and not start A/D conversion on CCPx match.

## 20.0 MASTER SYNCHRONOUS SERIAL PORT (MSSP) MODULE

The Master Synchronous Serial Port (MSSP) module is a serial interface, useful for communicating with other peripheral or microcontroller devices. These peripheral devices include serial EEPROMs, shift registers, display drivers and A/D Converters.

## 20.1 Master SSP (MSSP) Module Overview

The MSSP module can operate in one of two modes:

- Serial Peripheral Interface (SPI)

- Inter-Integrated Circuit (I<sup>2</sup>C)

- Full Master mode

- Slave mode (with general address call)

The  $I^2C$  interface supports the following modes in hardware:

- Master mode

- Multi-Master mode

- Slave mode with 5-bit and 7-bit address masking (with address masking for both 10-bit and 7-bit addressing)

All members of the PIC18F47J53 family have two MSSP modules, designated as MSSP1 and MSSP2. The modules operate independently:

- PIC18F4XJ53 devices Both modules can be configured for either I<sup>2</sup>C or SPI communication

- PIC18F2XJ53 devices:

- MSSP1 can be used for either I<sup>2</sup>C or SPI communication

- MSSP2 can be used only for SPI communication

All of the MSSP1 module related SPI and  $I^2C$  I/O functions are hard-mapped to specific I/O pins.

For MSSP2 functions:

SPI I/O functions (SDO2, SDI2, SCK2 and SS2) are all routed through the Peripheral Pin Select (PPS) module.

These functions may be configured to use any of the RPn remappable pins, as described in **Section 10.7** "**Peripheral Pin Select (PPS)**".

• I<sup>2</sup>C functions (SCL2 and SDA2) have fixed pin locations.

On all PIC18F47J53 family devices, the SPI DMA capability can only be used in conjunction with MSSP2. The SPI DMA feature is described in **Section 20.4 "SPI DMA Module"**.

| Note: | Throughout this section, generic references to an MSSP module in any of its operating modes may be interpreted as being equally applicable to MSSP1 or MSSP2. Register names and module I/O signals use the generic designator 'x' to indicate the use of a numeral to distinguish a particular module when required. Control bit names are not individuated. |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

### 20.5.2 OPERATION

The MSSP module functions are enabled by setting the MSSP Enable bit, SSPEN (SSPxCON1<5>).

The SSPxCON1 register allows control of the  $I^2C$  operation. Four mode selection bits (SSPxCON1<3:0>) allow one of the following  $I^2C$  modes to be selected:

- I<sup>2</sup>C Master mode, clock

- I<sup>2</sup>C Slave mode (7-bit address)

- I<sup>2</sup>C Slave mode (10-bit address)

- I<sup>2</sup>C Slave mode (7-bit address) with Start and Stop bit interrupts enabled

- I<sup>2</sup>C Slave mode (10-bit address) with Start and Stop bit interrupts enabled

- I<sup>2</sup>C Firmware Controlled Master mode, slave is Idle

Selection of any I<sup>2</sup>C mode, with the SSPEN bit set, forces the SCLx and SDAx pins to be open-drain, provided these pins are programmed as inputs by setting the appropriate TRISB or TRISD bits. To ensure proper operation of the module, pull-up resistors must be provided externally to the SCLx and SDAx pins.

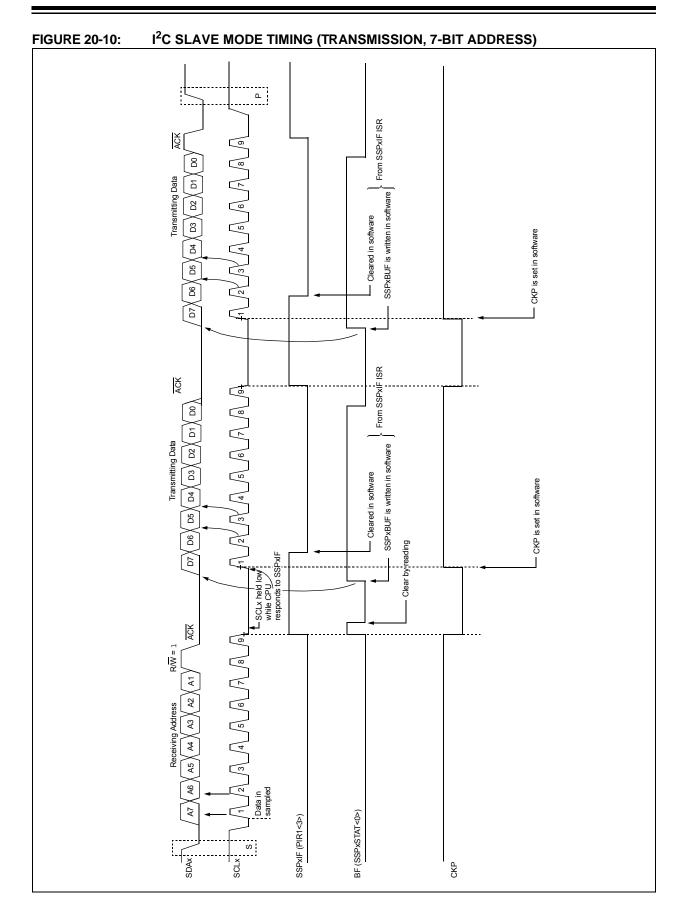

### 20.5.3 SLAVE MODE

In Slave mode, the SCLx and SDAx pins must be configured as inputs (TRISB<5:4> set). The MSSP module will override the input state with the output data when required (slave-transmitter).

The  $I^2C$  Slave mode hardware will always generate an interrupt on an address match. Address masking will allow the hardware to generate an interrupt for more than one address (up to 31 in 7-bit addressing and up to 63 in 10-bit addressing). Through the mode select bits, the user can also choose to interrupt on Start and Stop bits.

When an address is matched, or the data transfer after an address match is received, the hardware will automatically generate the Acknowledge ( $\overline{ACK}$ ) pulse and load the SSPxBUF register with the received value currently in the SSPxSR register.

Any combination of the following conditions will cause the MSSP module not to give this ACK pulse:

- The Buffer Full bit, BF (SSPxSTAT<0>), was set before the transfer was received.

- The overflow bit, SSPOV (SSPxCON1<6>), was set before the transfer was received.

In this case, the SSPxSR register value is not loaded into the SSPxBUF, but bit, SSPxIF, is set. The BF bit is cleared by reading the SSPxBUF register, while bit, SSPOV, is cleared through software. The SCLx clock input must have a minimum high and low for proper operation. The high and low times of the  $I^2C$  specification, as well as the requirement of the MSSP module, are shown in timing parameter 100 and parameter 101.

### 20.5.3.1 Addressing

Once the MSSP module has been enabled, it waits for a Start condition to occur. Following the Start condition, the 8 bits are shifted into the SSPxSR register. All incoming bits are sampled with the rising edge of the clock (SCLx) line. The value of register, SSPxSR<7:1>, is compared to the value of the SSPxADD register. The address is compared on the falling edge of the eighth clock (SCLx) pulse. If the addresses match and the BF and SSPOV bits are clear, the following events occur:

- 1. The SSPxSR register value is loaded into the SSPxBUF register.

- 2. The Buffer Full bit, BF, is set.

- 3. An ACK pulse is generated.

- 4. The MSSPx Interrupt Flag bit, SSPxIF, is set (and an interrupt is generated, if enabled) on the falling edge of the ninth SCLx pulse.

In 10-Bit Addressing mode, two address bytes need to be received by the slave. The five Most Significant bits (MSbs) of the first address byte specify if this is a 10-bit address. Bit,  $R/\overline{W}$  (SSPxSTAT<2>), must specify a write so the slave device will receive the second address byte. For a 10-bit address, the first byte would equal '11110 A9 A8 0', where 'A9' and 'A8' are the two MSbs of the address. The sequence of events for 10-bit addressing is as follows, with steps 7 through 9 for the slave-transmitter:

- 1. Receive the first (high) byte of address (bits, SSPxIF, BF and UA, are set on an address match).

- 2. Update the SSPxADD register with the second (low) byte of the address (clears bit, UA, and releases the SCLx line).

- 3. Read the SSPxBUF register (clears bit, BF) and clear flag bit, SSPxIF.

- 4. Receive the second (low) byte of address (bits, SSPxIF, BF and UA, are set).

- 5. Update the SSPxADD register with the first (high) byte of the address. If a match releases the SCLx line, this will clear bit, UA.

- 6. Read the SSPxBUF register (clears bit, BF) and clear flag bit, SSPxIF.

- 7. Receive Repeated Start condition.

- 8. Receive the first (high) byte of address (bits, SSPxIF and BF, are set).

- 9. Read the SSPxBUF register (clears bit, BF) and clear flag bit, SSPxIF.

# PIC18F47J53

SSPOV is set because SSPxBUF is still full. ACK is not sent. Bus master terminates transfer ٩ ACK 6 8 D3 Receiving Data 4 D5 D6 6 Note 1: In this example, an address equal to A7, A6, A5, X, A3, X, X will be Acknowledged and cause an interrupt. ACK 8 5 D2 D3 Receiving Data  $^{D4}$ Cleared in software SSPxBUF is read D5 D6 2 ACK R/W = 0 (CKP does not reset to '0' when SEN = 0) A3 eivina Addr × 45 A SSPxIF (PIR1<3> or PIR3<7>) A6 SSPOV (SSPxCON1<6>) CKP (SSPxCON1<4>) Å BF (SSPxSTAT<0>) s SDAX SCLX

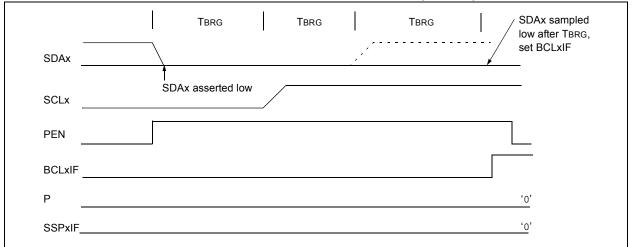

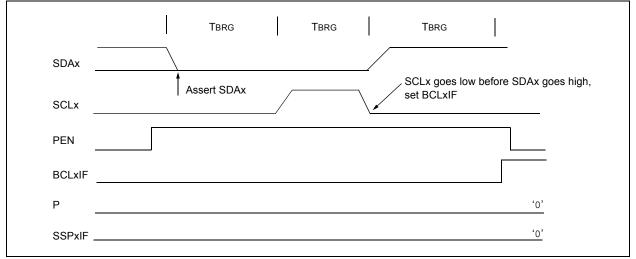

### 20.5.17.3 Bus Collision During a Stop Condition

Bus collision occurs during a Stop condition if:

- a) After the SDAx pin has been deasserted and allowed to float high, SDAx is sampled low after the BRG has timed out.

- b) After the SCLx pin is deasserted, SCLx is sampled low before SDAx goes high.

The Stop condition begins with SDAx asserted low. When SDAx is sampled low, the SCLx pin is allowed to float. When the pin is sampled high (clock arbitration), the BRG is loaded with SSPxADD<6:0> and counts down to 0. After the BRG times out, SDAx is sampled. If SDAx is sampled low, a bus collision has occurred. This is due to another master attempting to drive a data '0' (Figure 20-33). If the SCLx pin is sampled low before SDAx is allowed to float high, a bus collision occurs. This is another case of another master attempting to drive a data '0' (Figure 20-34).

### FIGURE 20-33: BUS COLLISION DURING A STOP CONDITION (CASE 1)

### FIGURE 20-34: BUS COLLISION DURING A STOP CONDITION (CASE 2)

### EXAMPLE 21-1: CALCULATING BAUD RATE ERROR

```

For a device with Fosc of 16 MHz, desired baud rate of 9600, Asynchronous mode, and

8-bit BRG:

Desired Baud Rate = Fosc/(64 ([SPBRGHx:SPBRGx] + 1))

Solving for SPBRGHx:SPBRGx:

X = ((Fosc/Desired Baud Rate)/64) - 1

= ((16000000/9600)/64) - 1

= [25.042] = 25

Calculated Baud Rate=16000000/(64 (25 + 1))

= 9615

Error = (Calculated Baud Rate - Desired Baud Rate)/Desired Baud Rate

= (9615 - 9600)/9600 = 0.16%

```

### TABLE 21-2: REGISTERS ASSOCIATED WITH BAUD RATE GENERATOR

| Name     | Bit 7                                    | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |  |

|----------|------------------------------------------|-------|-------|-------|-------|-------|-------|-------|--|

| TXSTAx   | CSRC                                     | TX9   | TXEN  | SYNC  | SENDB | BRGH  | TRMT  | TX9D  |  |

| RCSTAx   | SPEN                                     | RX9   | SREN  | CREN  | ADDEN | FERR  | OERR  | RX9D  |  |

| BAUDCONx | ABDOVF                                   | RCIDL | RXDTP | TXCKP | BRG16 | _     | WUE   | ABDEN |  |

| SPBRGHx  | Ix EUSARTx Baud Rate Generator High Byte |       |       |       |       |       |       |       |  |

| SPBRGx   | Gx EUSARTx Baud Rate Generator Low Byte  |       |       |       |       |       |       |       |  |

Legend: — = unimplemented, read as '0'. Shaded cells are not used by the BRG.

### 23.2.5 USB ADDRESS REGISTER (UADDR)

The USB Address register contains the unique USB address that the peripheral will decode when active. UADDR is reset to 00h when a USB Reset is received, indicated by URSTIF, or when a Reset is received from the microcontroller. The USB address must be written by the microcontroller during the USB setup phase (enumeration) as part of the Microchip USB firmware support.

### 23.2.6 USB FRAME NUMBER REGISTERS (UFRMH:UFRML)

The Frame Number registers contain the 11-bit frame number. The low-order byte is contained in UFRML, while the three high-order bits are contained in UFRMH. The register pair is updated with the current frame number whenever a SOF token is received. For the microcontroller, these registers are read-only. The Frame Number registers are primarily used for isochronous transfers. The contents of the UFRMH and UFRML registers are only valid when the 48 MHz SIE clock is active (i.e., contents are inaccurate when SUSPND (UCON<1>) bit = 1).

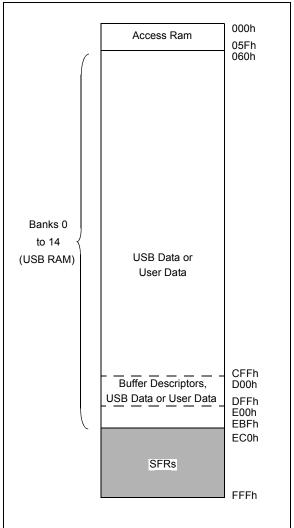

## 23.3 USB RAM

USB data moves between the microcontroller core and the SIE through a memory space known as the USB RAM. This is a special dual access memory that is mapped into the normal data memory space in Banks, 0 through 14 (00h to EBFh), for a total of 3.8 Kbytes (Figure 23-4).

Bank 13 (D00h through DFFh) is used specifically for endpoint buffer control, while Banks 0 through 12 and Bank 14 are available for USB data. Depending on the type of buffering being used, all but 8 bytes of Bank 13 may also be available for use as USB buffer space.

Although USB RAM is available to the microcontroller as data memory, the sections that are being accessed by the SIE should not be accessed by the microcontroller. A semaphore mechanism is used to determine the access to a particular buffer at any given time. This is discussed in **Section 23.4.1.1 "Buffer Ownership**".

### FIGURE 23-4:

### IMPLEMENTATION OF USB RAM IN DATA MEMORY SPACE

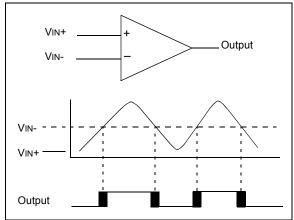

## 24.2 Comparator Operation

A single comparator is shown in Figure 24-2, along with the relationship between the analog input levels and the digital output. When the analog input at VIN+ is less than the analog input, VIN-, the output of the comparator is a digital low level. When the analog input at VIN+ is greater than the analog input, VIN-, the output of the comparator is a digital high level. The shaded areas of the output of the comparator in Figure 24-2 represent the uncertainty due to input offsets and response time.

FIGURE 24-2: SINGLE COMPARATOR

### 24.3 Comparator Response Time

Response time is the minimum time, after selecting a new reference voltage or input source, before the comparator output has a valid level. The response time of the comparator differs from the settling time of the voltage reference. Therefore, both of these times must be considered when determining the total response to a comparator input change. Otherwise, the maximum delay of the comparators should be used (see **Section 31.0 "Electrical Characteristics"**).

## 24.4 Analog Input Connection Considerations

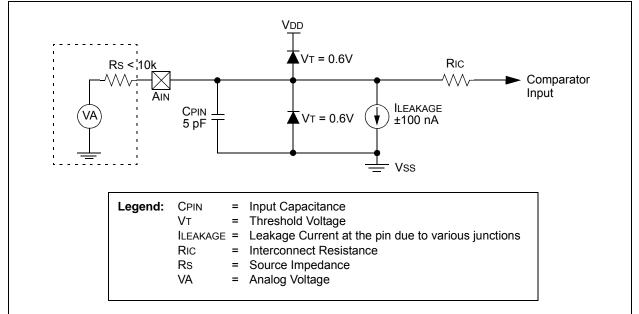

Figure 24-3 provides a simplified circuit for an analog input. Since the analog pins are connected to a digital output, they have reverse biased diodes to VDD and Vss. The analog input, therefore, must be between Vss and VDD. If the input voltage deviates from this range by more than 0.6V in either direction, one of the diodes is forward biased and a latch-up condition may occur. A maximum source impedance of 10 k $\Omega$  is recommended for the analog sources. Any external component connected to an analog input pin, such as a capacitor or a Zener diode, should have very little leakage current.

## REGISTER 27-2: CTMUCONL: CTMU CONTROL REGISTER LOW (ACCESS FB2h)

| R/W-0                             | R/W-0                                                  | R/W-0                     | R/W-0           | R/W-0             | R/W-0            | R/W-x           | R/W-x    |  |  |  |

|-----------------------------------|--------------------------------------------------------|---------------------------|-----------------|-------------------|------------------|-----------------|----------|--|--|--|

| EDG2POL                           | EDG2SEL1                                               | EDG2SEL0                  | EDG1POL         | EDG1SEL1          | EDG1SEL0         | EDG2STAT        | EDG1STAT |  |  |  |

| bit 7                             |                                                        |                           |                 |                   |                  |                 | bit 0    |  |  |  |

|                                   |                                                        |                           |                 |                   |                  |                 |          |  |  |  |

| Legend:                           |                                                        |                           |                 |                   |                  |                 |          |  |  |  |

| R = Readable                      | e bit                                                  | W = Writable I            | pit             | U = Unimplem      | nented bit, read | l as '0'        |          |  |  |  |

| -n = Value at                     | POR                                                    | '1' = Bit is set          |                 | '0' = Bit is clea | ared             | x = Bit is unkr | nown     |  |  |  |

|                                   |                                                        |                           |                 |                   |                  |                 |          |  |  |  |

| bit 7                             | EDG2POL: E                                             | dge 2 Polarity            | Select bit      |                   |                  |                 |          |  |  |  |

|                                   |                                                        | programmed f              |                 |                   |                  |                 |          |  |  |  |

|                                   | -                                                      | s programmed f            | -               |                   |                  |                 |          |  |  |  |

| bit 6-5                           |                                                        | :0>: Edge 2 Sou           | arce Select bit | S                 |                  |                 |          |  |  |  |

|                                   | 11 = CTED1<br>10 = CTED2                               |                           |                 |                   |                  |                 |          |  |  |  |

|                                   |                                                        | CP1 output compare module |                 |                   |                  |                 |          |  |  |  |

|                                   | 00 <b>= Timer1</b> r                                   |                           |                 |                   |                  |                 |          |  |  |  |

| bit 4                             | EDG1POL: E                                             | dge 1 Polarity            | Select bit      |                   |                  |                 |          |  |  |  |

|                                   | <b>U</b> 1                                             | rogrammed for             |                 |                   |                  |                 |          |  |  |  |

|                                   | • •                                                    | rogrammed for             | •               |                   |                  |                 |          |  |  |  |

| bit 3-2                           | EDG1SEL<1:                                             | :0>: Edge 1 So            | urce Select bit | S                 |                  |                 |          |  |  |  |

|                                   | 11 = CTED1 pin                                         |                           |                 |                   |                  |                 |          |  |  |  |

|                                   | 10 = CTED2 pin                                         |                           |                 |                   |                  |                 |          |  |  |  |

|                                   | 01 = ECCP1 output compare module<br>00 = Timer1 module |                           |                 |                   |                  |                 |          |  |  |  |

| bit 1                             | EDG2STAT:                                              | Edge 2 Status b           | it              |                   |                  |                 |          |  |  |  |

|                                   | 1 = Edge 2 event has occurred                          |                           |                 |                   |                  |                 |          |  |  |  |

|                                   | 0 = Edge 2 e                                           | vent has not oc           | curred          |                   |                  |                 |          |  |  |  |

| bit 0 EDG1STAT: Edge 1 Status bit |                                                        |                           |                 |                   |                  |                 |          |  |  |  |

|                                   |                                                        | vent has occurr           |                 |                   |                  |                 |          |  |  |  |

|                                   | 0 = Edge 1 e                                           | vent has not oc           | curred          |                   |                  |                 |          |  |  |  |

## 31.2 DC Characteristics: Power-Down and Supply Current PIC18F47J53 Family (Industrial) (Continued)

| PIC18LF       | 47J53 Family                                                      | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial |      |                       |       |                                              |                                                         |  |  |  |

|---------------|-------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|------|-----------------------|-------|----------------------------------------------|---------------------------------------------------------|--|--|--|

| PIC18F4       | 7J53 Family                                                       | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial |      |                       |       |                                              |                                                         |  |  |  |

| Param.<br>No. | Device                                                            | Тур.                                                                                                                               | Max. | lax. Units Conditions |       |                                              |                                                         |  |  |  |

|               | Module Differential Currents (AlwDT, AlHLVD, AlOSCB, AlAD, AlUSB) |                                                                                                                                    |      |                       |       |                                              |                                                         |  |  |  |

| (∆IOSCB)      | Real-Time Clock/Calendar                                          | 0.5                                                                                                                                | 4.0  | μA                    | -40°C |                                              |                                                         |  |  |  |

|               | with Low-Power Timer1                                             | 0.7                                                                                                                                | 4.5  | μA                    | +25°C | VDD = 2.15V,<br>VDDCORE = 10 μF<br>Capacitor |                                                         |  |  |  |

|               | Oscillator                                                        | 0.8                                                                                                                                | 4.5  | μA                    | +60°C |                                              |                                                         |  |  |  |

|               |                                                                   | 0.9                                                                                                                                | 4.5  | μA                    | +85°C |                                              |                                                         |  |  |  |

|               |                                                                   | 0.6                                                                                                                                | 4.5  | μA                    | -40°C |                                              |                                                         |  |  |  |

|               |                                                                   | 0.8                                                                                                                                | 5.0  | μA                    | +25°C | VDD = $2.5V$ ,<br>VDDCORE = $10 \mu$ F       | PIC18FXXJ53<br>32.768 kHz <sup>(3)</sup> , T1OSCEN = 1, |  |  |  |

|               |                                                                   | 0.9                                                                                                                                | 5.0  | μA                    | +60°C | Capacitor                                    | (SOSCSEL<1:0> = 01)                                     |  |  |  |

|               |                                                                   | 1.0                                                                                                                                | 5.0  | μA                    | +85°C | ·                                            | , , , , , , , , , , , , , , , , , , ,                   |  |  |  |

|               |                                                                   | 0.8                                                                                                                                | 6.5  | μA                    | -40°C |                                              |                                                         |  |  |  |

|               |                                                                   | 1.0                                                                                                                                | 6.5  | μA                    | +25°C | VDD = $3.3V$ ,<br>VDDCORE = $10 \mu F$       |                                                         |  |  |  |

|               |                                                                   | 1.1                                                                                                                                | 8.0  | μA                    | +60°C | Capacitor                                    |                                                         |  |  |  |

|               |                                                                   | 1.3                                                                                                                                | 8.0  | μA                    | +85°C | •                                            |                                                         |  |  |  |

**Note 1:** The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD or VSS and all features that add delta current disabled (such as WDT, Timer1 oscillator, BOR, etc.).

2: The supply current is mainly a function of operating voltage, frequency and mode. Other factors, such as I/O pin loading and switching rate, oscillator type and circuit, internal code execution pattern and temperature, also have an impact on the current consumption. All features that add delta current are disabled (USB module, WDT, etc.). The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD/Vss;

$\overline{MCLR}$  = VDD; WDT disabled unless otherwise specified.

- **3:** Low-power Timer1 with standard, low-cost 32 kHz crystals have an operating temperature range of -10°C to +70°C. Extended temperature crystals are available at a much higher cost.

- 4: This is the module differential current when the USB module is enabled and clocked at 48 MHz, but with no USB cable attached. When the USB cable is attached or data is being transmitted, the current consumption may be much higher (see Section 23.6.4 "USB Transceiver Current Consumption"). During USB Suspend mode (USBEN = 1, SUSPND = 1, bus in Idle state), the USB module current will be dominated by the D+ or D- pull-up resistor. The integrated pull-up resistor use "resistor switching" according to the resistor\_ecn supplement to the USB 2.0 Specifications, and therefore, may be as low as 900Ω during Idle conditions.

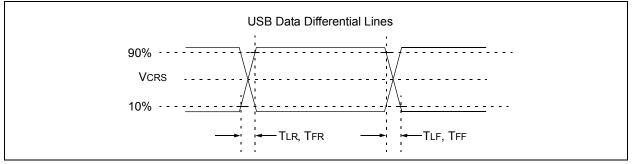

### FIGURE 31-23: USB SIGNAL TIMING

### TABLE 31-33: USB LOW-SPEED TIMING REQUIREMENTS

| Param.<br>No. | Symbol | Characteristic          | Min. | Тур. | Max. | Units | Conditions         |

|---------------|--------|-------------------------|------|------|------|-------|--------------------|

|               | Tlr    | Transition Rise Time    | 75   | _    | 300  | ns    | CL = 200 to 600 pF |

|               | Tlf    | Transition Fall Time    | 75   | —    | 300  | ns    | CL = 200 to 600 pF |

|               | TLRFM  | Rise/Fall Time Matching | 80   |      | 125  | %     |                    |

### TABLE 31-34: USB FULL-SPEED REQUIREMENTS

| Param.<br>No. | Symbol | Characteristic          | Min. | Тур. | Max.  | Units | Conditions |

|---------------|--------|-------------------------|------|------|-------|-------|------------|

|               | Tfr    | Transition Rise Time    | 4    | _    | 20    | ns    | CL = 50 pF |

|               | Tff    | Transition Fall Time    | 4    |      | 20    | ns    | CL = 50 pF |

|               | TFRFM  | Rise/Fall Time Matching | 90   |      | 111.1 | %     |            |

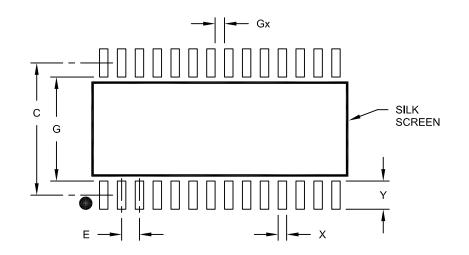

28-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

## RECOMMENDED LAND PATTERN

|                          | Units            | MILLIMETERS |      |      |  |

|--------------------------|------------------|-------------|------|------|--|

| Dimension                | Dimension Limits |             |      | MAX  |  |

| Contact Pitch            | E                | 1.27 BSC    |      |      |  |

| Contact Pad Spacing      | С                |             | 9.40 |      |  |

| Contact Pad Width (X28)  | Х                |             |      | 0.60 |  |

| Contact Pad Length (X28) | Y                |             |      | 2.00 |  |

| Distance Between Pads    | Gx               | 0.67        |      |      |  |

| Distance Between Pads    | G                | 7.40        |      |      |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2052A

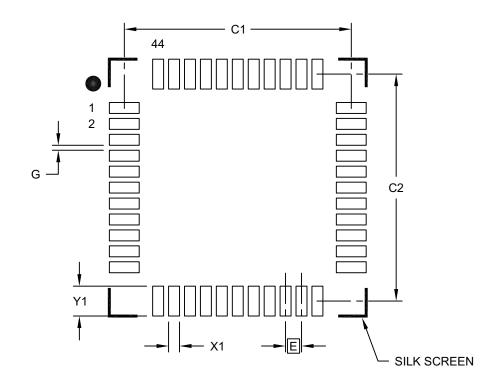

## 44-Lead Plastic Thin Quad Flatpack (PT) - 10X10X1 mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

## RECOMMENDED LAND PATTERN

|                          | Units |          |       | S    |

|--------------------------|-------|----------|-------|------|

| Dimensior                | MIN   | NOM      | MAX   |      |

| Contact Pitch            | Е     | 0.80 BSC |       |      |

| Contact Pad Spacing      | C1    |          | 11.40 |      |

| Contact Pad Spacing      | C2    |          | 11.40 |      |

| Contact Pad Width (X44)  | X1    |          |       | 0.55 |

| Contact Pad Length (X44) | Y1    |          |       | 1.50 |

| Distance Between Pads    | G     | 0.25     |       |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2076B