Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 48MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART, USB                              |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 34                                                                          |

| Program Memory Size        | 64KB (32K x 16)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 3.8K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 2.75V                                                                  |

| Data Converters            | A/D 13x10b/12b                                                              |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 44-TQFP                                                                     |

| Supplier Device Package    | 44-TQFP (10x10)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf46j53-i-pt |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1.0 DEVICE OVERVIEW

This document contains device-specific information for the following devices:

- PIC18F26J53 PIC18LF26J53

- PIC18F27J53 PIC18LF27J53

- PIC18F46J53 PIC18LF46J53

- PIC18F47J53 PIC18LF47J53

This family introduces a new line of low-voltage Universal Serial Bus (USB) microcontrollers with the main traditional advantage of all PIC18 microcontrollers, namely, high computational performance and a rich feature set at an extremely competitive price point. These features make the PIC18F47J53 family a logical choice for many high-performance applications, where cost is a primary consideration.

# 1.1 Core Features

### 1.1.1 XLP TECHNOLOGY

All of the devices in the PIC18F47J53 family incorporate a range of features that can significantly reduce power consumption during operation. Key features are:

- Alternate Run Modes: By clocking the controller from the Timer1 source or the internal RC oscillator, power consumption during code execution can be reduced by as much as 90%.

- **Multiple Idle Modes:** The controller can also run with its CPU core disabled but the peripherals still active. In these states, power consumption can be reduced even further, to as little as 4% of normal operational requirements.

- On-the-Fly Mode Switching: The power-managed modes are invoked by user code during operation, allowing the users to incorporate power-saving ideas into their application's software design.

- **Deep Sleep:** The 2.5V internal core voltage regulator on F parts can be shutdown to cut power consumption to as low as 15 nA (typical). Certain features can remain operating during Deep Sleep, such as the Real-Time Clock Calendar.

- Ultra Low Power Wake-Up: Waking from Sleep or Deep Sleep modes after a period of time can be done without an oscillator/clock source, saving power for applications requiring periodic activity.

## 1.1.2 UNIVERSAL SERIAL BUS (USB)

Devices in the PIC18F47J53 family incorporate a fully-featured USB communications module with a built-in transceiver that is compliant with the USB Specification Revision 2.0. The module supports both low-speed and full-speed communication for all supported data transfer types.

# 1.1.3 OSCILLATOR OPTIONS AND FEATURES

All of the devices in the PIC18F47J53 family offer five different oscillator options, allowing users a range of choices in developing application hardware. These include:

- Two Crystal modes, using crystals or ceramic resonators.

- Two External Clock modes, offering the option of a divide-by-4 clock output.

- An internal oscillator block, which provides an 8 MHz clock and an INTRC source (approximately 31 kHz, stable over temperature and VDD), as well as a range of six user-selectable clock frequencies, between 125 kHz to 4 MHz, for a total of eight clock frequencies. This option frees an oscillator pin for use as an additional general purpose I/O.

- A Phase Lock Loop (PLL) frequency multiplier available to the high-speed crystal, and external and internal oscillators, providing a clock speed up to 48 MHz.

- Dual clock operation, allowing the USB module to run from a high-frequency oscillator while the rest of the microcontroller is clocked at a different frequency.

The internal oscillator block provides a stable reference source that gives the PIC18F47J53 family additional features for robust operation:

- Fail-Safe Clock Monitor: This option constantly monitors the main clock source against a reference signal provided by the internal oscillator. If a clock failure occurs, the controller is switched to the internal oscillator, allowing for continued low-speed operation or a safe application shutdown.

- **Two-Speed Start-up:** This option allows the internal oscillator to serve as the clock source from Power-on Reset (POR), or wake-up from Sleep mode, until the primary clock source is available.

# 1.1.4 EXPANDED MEMORY

The PIC18F47J53 family provides ample room for application code, from 64 Kbytes to 128 Kbytes of code space. The Flash cells for program memory are rated to last in excess of 10000 erase/write cycles. Data retention without refresh is conservatively estimated to be greater than 20 years.

The Flash program memory is readable and writable during normal operation. The PIC18F47J53 family also provides plenty of room for dynamic application data with up to 3.8 Kbytes of data RAM.

| 28-SPDIP/<br>SSOP/<br>SOIC | 28-QFN                                | Pin<br>Type                                     | Buffer<br>Type                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Description                                                                                                                                                                                                                                                                                                                                                                                                       |

|----------------------------|---------------------------------------|-------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 <sup>(2)</sup>           |                                       |                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                            | 26 <sup>(2)</sup>                     | I                                               | ST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Master Clear (Reset) input. This pin is an active-low Reset to the device.                                                                                                                                                                                                                                                                                                                                        |

| 9                          | 6                                     | I                                               | ST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Oscillator crystal or external clock input.<br>Oscillator crystal input or external clock source<br>input. ST buffer when configured in RC mode;<br>CMOS otherwise. Main oscillator input<br>connection.                                                                                                                                                                                                          |

|                            |                                       | I                                               | CMOS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | External clock source input; always associated with pin function OSC1 (see related OSC1/CLKI pins).                                                                                                                                                                                                                                                                                                               |

|                            |                                       | I/O                                             | TTL/DIG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Digital I/O.                                                                                                                                                                                                                                                                                                                                                                                                      |

| 10                         | 7                                     | 0                                               | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Oscillator crystal or clock output.<br>Oscillator crystal output. Connects to crystal or<br>resonator in Crystal Oscillator mode.                                                                                                                                                                                                                                                                                 |

|                            |                                       | 0                                               | DIG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Main oscillator feedback output connection.<br>In RC mode, OSC2 pin outputs CLKO, which<br>has 1/4 the frequency of OSC1 and denotes<br>the instruction cycle rate.                                                                                                                                                                                                                                               |

|                            |                                       | I/O                                             | TTL/DIG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                   |

| igger input w              | ith CMOS                              | levels                                          | Ar<br>O<br>Ol                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                   |

| t                          | 10<br>Datible input<br>rigger input w | 10 7<br>batible input<br>rigger input with CMOS | I     I       I     I       I     I/O       I     I       I     I       I     I       I     I       I     I       I     I       I     I       I     I       I     I       I     I       I     I       I     I       I     I       I     I       I     I       I     I       < | I     ST       I     CMOS       I     II/O       I     TTL/DIG       I     I/O       I/O     TTL/DIG       I/O     I/O       I/O     TTL/DIG       I/O     TTL/DIG       I/O     TTL/DIG       I/O     TTL/DIG       I/O     Ar       O     O       O     O       I     O |

TABLE 1-3:

PIC18F2XJ53 PINOUT I/O DESCRIPTIONS

Note 1: RA7 and RA6 will be disabled if OSC1 and OSC2 are used for the clock function.

2: 5.5V tolerant.

|                                                                                                | Pin Nu                     | ımber  |                             |                                                                               |                                                                                                                                                                                                           |  |  |

|------------------------------------------------------------------------------------------------|----------------------------|--------|-----------------------------|-------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Pin Name                                                                                       | 28-SPDIP/<br>SSOP/<br>SOIC | 28-QFN | Pin<br>Type                 | Buffer<br>Type                                                                | Description                                                                                                                                                                                               |  |  |

|                                                                                                |                            |        |                             |                                                                               | PORTA is a bidirectional I/O port.                                                                                                                                                                        |  |  |

| RA0/AN0/C1INA/ULPWU/RP0<br>RA0<br>AN0<br>C1INA<br>ULPWU<br>RP0                                 | 2                          | 27     | I/O<br>I<br>I<br>I/O        | TTL/DIG<br>Analog<br>Analog<br>Analog<br>ST/DIG                               | Digital I/O.<br>Analog Input 0.<br>Comparator 1 Input A.<br>Ultra low-power wake-up input.<br>Remappable Peripheral Pin 0 input/output.                                                                   |  |  |

|                                                                                                | 2                          | 20     |                             | 011010                                                                        |                                                                                                                                                                                                           |  |  |

| RA1/AN1/C2INA/VBG/RP1<br>RA1<br>AN1<br>C2INA<br>VBG<br>RP1                                     | 3                          | 28     | I/O<br>O<br>I<br>O<br>I/O   | TTL/DIG<br>Analog<br>Analog<br>Analog<br>ST/DIG                               | Digital I/O.<br>Analog Input 1.<br>Comparator 2 Input A.<br>Band Gap Reference Voltage (VBG) output.<br>Remappable Peripheral Pin 1 input/output.                                                         |  |  |

| RA2/AN2/C2INB/C1IND/                                                                           | 4                          | 1      |                             |                                                                               |                                                                                                                                                                                                           |  |  |

| C3INB/VREF-/CVREF<br>RA2<br>AN2<br>C2INB<br>C1IND<br>C3INB<br>VREF-<br>CVREF                   |                            |        | I/O<br> <br> <br> <br>0<br> | TTL/DIG<br>Analog<br>Analog<br>Analog<br>Analog<br>Analog<br>Analog<br>Analog | Digital I/O.<br>Analog Input 2.<br>Comparator 2 Input B.<br>Comparator 1 Input D.<br>Comparator 3 Input B.<br>A/D reference voltage (low) input.<br>Comparator reference voltage output.                  |  |  |

| RA3/AN3/C1INB/VREF+                                                                            | 5                          | 2      |                             |                                                                               |                                                                                                                                                                                                           |  |  |

| RA3<br>AN3<br>C1INB<br>VREF+                                                                   |                            |        | I/O<br>I<br>I<br>I          | TTL/DIG<br>Analog<br>Analog<br>Analog                                         | Digital I/O.<br>Analog Input 3.<br>Comparator 1 Input B.<br>A/D reference voltage (high) input.                                                                                                           |  |  |

| RA5/AN4/C1INC/SS1/                                                                             | 7                          | 4      |                             |                                                                               |                                                                                                                                                                                                           |  |  |

| HLVDIN/RCV/RP2<br>RA5<br>AN4<br><u>C1INC</u><br>SS1<br>HLVDIN<br>RCV<br>RP2                    |                            |        | I/O<br>I<br>I<br>I<br>I/O   | TTL/DIG<br>Analog<br>Analog<br>TTL<br>Analog<br>Analog<br>ST/DIG              | Digital I/O.<br>Analog Input 4.<br>Comparator 1 Input C.<br>SPI slave select input.<br>High/Low-Voltage Detect input.<br>External USB transceiver RCV input.<br>Remappable Peripheral Pin 2 input/output. |  |  |

| RA6 <sup>(1)</sup><br>RA7 <sup>(1)</sup>                                                       |                            |        |                             |                                                                               | See the OSC2/CLKO/RA6 pin.<br>See the OSC1/CLKI/RA7 pin.                                                                                                                                                  |  |  |

| Legend: TTL = TTL compat<br>ST = Schmitt Trig<br>I = Input<br>P = Power<br>DIG = Digital outpu | ger input wi<br>ıt         |        |                             | Ar<br>O<br>OI<br>I <sup>2</sup> (                                             | MOS = CMOS compatible input or output<br>alog = Analog input<br>= Output<br>D = Open-Drain (no P diode to VDD)                                                                                            |  |  |

#### PIC18F2XJ53 PINOUT I/O DESCRIPTIONS (CONTINUED) **TABLE 1-3:**

2: 5.5V tolerant.

# 4.0 LOW-POWER MODES

The PIC18F47J53 family devices can manage power consumption through clocking to the CPU and the peripherals. In general, reducing the clock frequency and number of circuits being clocked reduces power consumption.

For managing power in an application, the primary modes of operation are:

- Run Mode

- Idle Mode

- Sleep Mode

- · Deep Sleep Mode

Additionally, there is an Ultra Low-Power Wake-up (ULPWU) mode for generating an interrupt-on-change on RA0.

These modes define which portions of the device are clocked and at what speed.

- The Run and Idle modes can use any of the three available clock sources (primary, secondary or internal oscillator blocks).

- The Sleep mode does not use a clock source.

The ULPWU mode on RA0 allows a slow falling voltage to generate an interrupt-on-change on RA0 without excess current consumption. See **Section 4.7** "**Ultra Low-Power Wake-up**".

The power-managed modes include several power-saving features offered on previous PIC<sup>®</sup> devices, such as clock switching, ULPWU and Sleep mode. In addition, the PIC18F47J53 family devices add a new power-managed Deep Sleep mode.

## 4.1 Selecting Power-Managed Modes

Selecting a power-managed mode requires these decisions:

- Will the CPU be clocked?

- If so, which clock source will be used?

The IDLEN bit (OSCCON<7>) controls CPU clocking and the SCS<1:0> bits (OSCCON<1:0>) select the clock source. The individual modes, bit settings, clock sources and affected modules are summarized in Table 4-1.

# 4.1.1 CLOCK SOURCES

The SCS<1:0> bits allow the selection of one of three clock sources for power-managed modes. They are:

- Primary clock source Defined by the FOSC<2:0> Configuration bits

- Timer1 clock Provided by the secondary oscillator

- Postscaled internal clock Derived from the internal oscillator block

#### 4.1.2 ENTERING POWER-MANAGED MODES

Switching from one clock source to another begins by loading the OSCCON register. The SCS<1:0> bits select the clock source.

Changing these bits causes an immediate switch to the new clock source, assuming that it is running. The switch also may be subject to clock transition delays. These delays are discussed in **Section 4.1.3 "Clock Transitions and Status Indicators"** and subsequent sections.

Entry to the power-managed Idle or Sleep modes is triggered by the execution of a SLEEP instruction. The actual mode that results depends on the status of the IDLEN bit.

Depending on the current mode and the mode being switched to, a change to a power-managed mode does not always require setting all of these bits. Many transitions may be done by changing the oscillator select bits, the IDLEN bit, or the DSEN bit prior to issuing a SLEEP instruction.

If the IDLEN and DSEN bits are already configured correctly, it may only be necessary to perform a SLEEP instruction to switch to the desired mode.

# 6.6.3 MAPPING THE ACCESS BANK IN INDEXED LITERAL OFFSET MODE

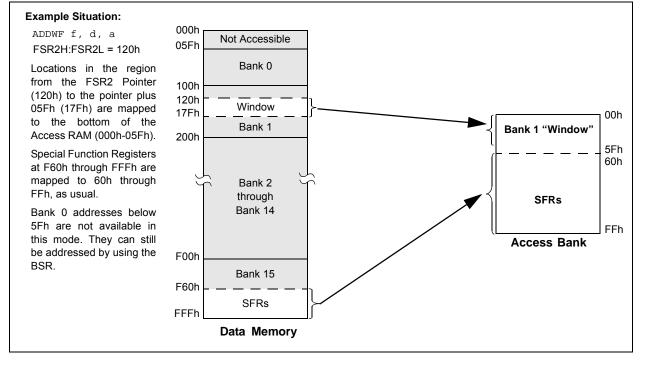

The use of Indexed Literal Offset Addressing mode effectively changes how the lower part of Access RAM (00h to 5Fh) is mapped. Rather than containing just the contents of the bottom part of Bank 0, this mode maps the contents from Bank 0 and a user-defined "window" that can be located anywhere in the data memory space. The value of FSR2 establishes the lower boundary of the addresses mapped to the window, while the upper boundary is defined by FSR2 plus 95 (5Fh). Addresses in the Access RAM above 5Fh are mapped as previously described (see **Section 6.3.3** "**Access Bank**"). Figure 6-10 provides an example of Access Bank remapping in this addressing mode.

Remapping of the Access Bank applies *only* to operations using the Indexed Literal Offset mode. Operations that use the BSR (Access RAM bit is '1') will continue to use Direct Addressing as before. Any Indirect or Indexed Addressing operation that explicitly uses any of the indirect file operands (including FSR2) will continue to operate as standard Indirect Addressing. Any instruction that uses the Access Bank, but includes a register address of greater than 05Fh, will use Direct Addressing and the normal Access Bank map.

#### 6.6.4 BSR IN INDEXED LITERAL OFFSET MODE

Although the Access Bank is remapped when the extended instruction set is enabled, the operation of the BSR remains unchanged. Direct Addressing, using the BSR to select the data memory bank, operates in the same manner as previously described.

#### FIGURE 6-10: REMAPPING THE ACCESS BANK WITH INDEXED LITERAL OFFSET ADDRESSING

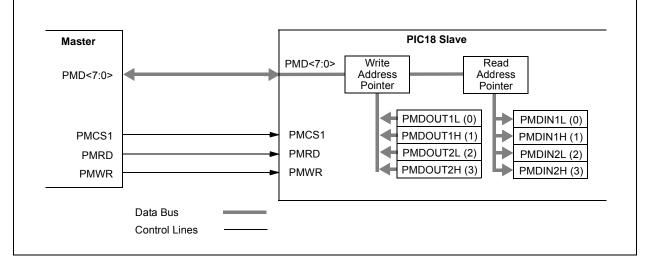

### 11.1.2 DATA REGISTERS

The PMP module uses eight registers for transferring data into and out of the microcontroller. They are arranged as four pairs to allow the option of 16-bit data operations:

- PMDIN1H and PMDIN1L

- PMDIN2H and PMDIN2L

- PMADDRH/PMDOUT1H and PMADDRL/PMDOUT1L

- PMDOUT2H and PMDOUT2L

The PMDIN1 registers are used for incoming data in Slave modes, and both input and output data in Master modes. The PMDIN2 registers are used for buffering input data in select Slave modes.

The PMADDR/PMDOUT1 registers are actually a single register pair; the name and function are dictated by the module's operating mode. In Master modes, the registers function as the PMADDRH and PMADDRL registers, and contain the address of any incoming or outgoing data. In Slave modes, the registers function as PMDOUT1H and PMDOUT1L, and are used for outgoing data.

PMADDRH differs from PMADDRL in that it can also have limited PMP control functions. When the module is operating in select Master mode configurations, the upper two bits of the register can be used to determine the operation of chip select signals. If these are not used, PMADDR simply functions to hold the upper 8 bits of the address. Register 11-9 provides the function of the individual bits in PMADDRH.

The PMDOUT2H and PMDOUT2L registers are only used in Buffered Slave modes and serve as a buffer for outgoing data.

#### 11.1.3 PAD CONFIGURATION CONTROL REGISTER

In addition to the module level configuration options, the PMP module can also be configured at the I/O pin for electrical operation. This option allows users to select either the normal Schmitt Trigger input buffer on digital I/O pins shared with the PMP, or use TTL level compatible buffers instead. Buffer configuration is controlled by the PMPTTL bit in the PADCFG1 register.

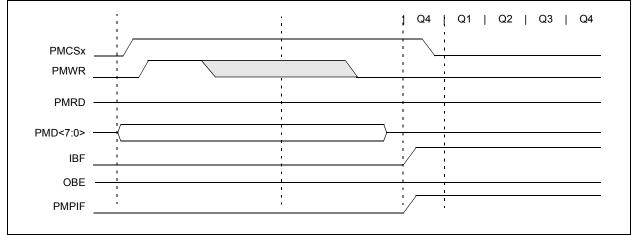

## 11.2.2 WRITE TO SLAVE PORT

When chip select is active and a write strobe occurs (PMCSx = 1 and PMWR = 1), the data from PMD<7:0> is captured into the lower PMDIN1L register. The PMPIF and IBF flag bits are set when the write ends. The timing for the control signals in Write mode is displayed in Figure 11-3. The polarity of the control signals are configurable.

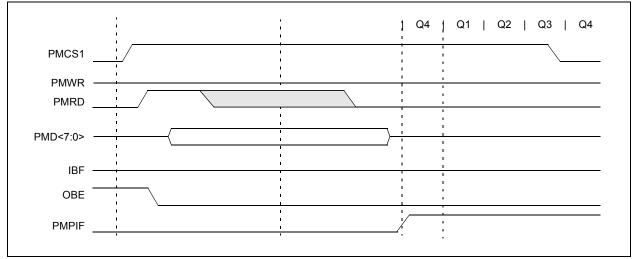

# 11.2.3 READ FROM SLAVE PORT

When chip select is active and a read strobe occurs (PMCSx = 1 and PMRD = 1), the data from the PMD-OUT1L register (PMDOUT1L<7:0>) is presented on to PMD<7:0>. Figure 11-4 provides the timing for the control signals in Read mode.

#### FIGURE 11-4: PARALLEL SLAVE PORT READ WAVEFORMS

#### 11.2.4 BUFFERED PARALLEL SLAVE PORT MODE

Buffered Parallel Slave Port mode is functionally identical to the legacy PSP mode with one exception, the implementation of 4-level read and write buffers. Buffered PSP mode is enabled by setting the INCM bits in the PMMODEH register. If the INCM<1:0> bits are set to '11', the PMP module will act as the buffered PSP.

When the Buffered PSP mode is active, the PMDIN1L, PMDIN1H, PMDIN2L and PMDIN2H registers become the write buffers and the PMDOUT1L, PMDOUT1H, PMDOUT2L and PMDOUT2H registers become the read buffers. Buffers are numbered, 0 through 3, starting with the lower byte of PMDIN1L to PMDIN2H as the read buffers and PMDOUT1L to PMDOUT2H as the write buffers.

## 11.2.4.1 READ FROM SLAVE PORT

For read operations, the bytes will be sent out sequentially, starting with Buffer 0 (PMDOUT1L<7:0>) and ending with Buffer 3 (PMDOUT2H<7:0>) for every read strobe. The module maintains an internal pointer to keep track of which buffer is to be read. Each buffer has a corresponding read status bit, OBxE, in the PMSTATL register. This bit is cleared when a buffer contains data that has not been written to the bus, and is set when data is written to the bus. If the current buffer location being read from is empty, a buffer underflow is generated and the Buffer Overflow Flag bit, OBUF, is set. If all four OBxE status bits are set, then the Output Buffer Empty flag (OBE) will also be set.

# 11.2.4.2 WRITE TO SLAVE PORT

For write operations, the data has to be stored sequentially, starting with Buffer 0 (PMDIN1L<7:0>) and ending with Buffer 3 (PMDIN2H<7:0>). As with read operations, the module maintains an internal pointer to the buffer that is to be written next.

The input buffers have their own write status bits: IBxF in the PMSTATH register. The bit is set when the buffer contains unread incoming data and cleared when the data has been read. The flag bit is set on the write strobe. If a write occurs on a buffer when its associated IBxF bit is set, the Buffer Overflow flag, IBOV, is set; any incoming data in the buffer will be lost. If all four IBxF flags are set, the Input Buffer Full Flag (IBF) is set.

In Buffered Slave mode, the module can be configured to generate an interrupt on every read or write strobe (IRQM<1:0> = 01). It can be configured to generate an interrupt on a read from Read Buffer 3 or a write to Write Buffer 3, which is essentially an interrupt every fourth read or write strobe (RQM<1:0> = 11). When interrupting every fourth byte for input data, all input buffer registers should be read to clear the IBxF flags. If these flags are not cleared, then there is a risk of hitting an overflow condition.

#### FIGURE 11-5: PARALLEL MASTER/SLAVE CONNECTION BUFFERED EXAMPLE

# 12.3 Prescaler

An 8-bit counter is available as a prescaler for the Timer0 module. The prescaler is not directly readable or writable. Its value is set by the PSA and T0PS<2:0> bits (T0CON<3:0>), which determine the prescaler assignment and prescale ratio.

Clearing the PSA bit assigns the prescaler to the Timer0 module. When it is assigned, prescale values from 1:2 through 1:256, in power-of-2 increments, are selectable.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g., CLRF TMR0, MOVWF TMR0, BSF TMR0, etc.) clear the prescaler count.

| Note: | Writing to TMR0 when the prescaler is       |

|-------|---------------------------------------------|

|       | assigned to Timer0 will clear the prescaler |

|       | count but will not change the prescaler     |

|       | assignment.                                 |

#### 12.3.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control and can be changed "on-the-fly" during program execution.

# 12.4 Timer0 Interrupt

The TMR0 interrupt is generated when the TMR0 register overflows from FFh to 00h in 8-bit mode, or from FFFFh to 0000h in 16-bit mode. This overflow sets the TMR0IF flag bit. The interrupt can be masked by clearing the TMR0IE bit (INTCON<5>). Before re-enabling the interrupt, the TMR0IF bit must be cleared in software by the Interrupt Service Routine (ISR).

Since Timer0 is shut down in Sleep mode, the TMR0 interrupt cannot awaken the processor from Sleep.

| TABLE 12-1: | REGISTERS ASSOCIATED WITH TIMER0 |

|-------------|----------------------------------|

|             |                                  |

| Name   | Bit 7                    | Bit 6                     | Bit 5  | Bit 4         | Bit 3 | Bit 2  | Bit 1  | Bit 0 |  |

|--------|--------------------------|---------------------------|--------|---------------|-------|--------|--------|-------|--|

| TMR0L  | Timer0 Register Low Byte |                           |        |               |       |        |        |       |  |

| TMR0H  | Timer0 Regis             | Timer0 Register High Byte |        |               |       |        |        |       |  |

| INTCON | GIE/GIEH                 | PEIE/GIEL                 | TMR0IE | <b>INTOIE</b> | RBIE  | TMR0IF | INT0IF | RBIF  |  |

| TOCON  | TMR0ON                   | T08BIT                    | TOCS   | TOSE          | PSA   | T0PS2  | T0PS1  | T0PS0 |  |

|        |                          |                           | T      |               |       |        |        |       |  |

**Legend:** Shaded cells are not used by Timer0.

# REGISTER 17-18: ALRMMIN: ALARM MINUTES VALUE REGISTER

| U-0   | R/W-x   |

|-------|---------|---------|---------|---------|---------|---------|---------|

| —     | MINTEN2 | MINTEN1 | MINTEN0 | MINONE3 | MINONE2 | MINONE1 | MINONE0 |

| bit 7 |         |         |         |         |         |         | bit 0   |

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

| bit 7   | Unimplemented: Read as '0'                                                                                     |

|---------|----------------------------------------------------------------------------------------------------------------|

| bit 6-4 | <b>MINTEN&lt;2:0&gt;:</b> Binary Coded Decimal Value of Minute's Tens Digit bits Contains a value from 0 to 5. |

| bit 3-0 | <b>MINONE&lt;3:0&gt;:</b> Binary Coded Decimal Value of Minute's Ones Digit bits Contains a value from 0 to 9. |

### REGISTER 17-19: ALRMSEC: ALARM SECONDS VALUE REGISTER

| U-0   | R/W-x   |

|-------|---------|---------|---------|---------|---------|---------|---------|

| —     | SECTEN2 | SECTEN1 | SECTEN0 | SECONE3 | SECONE2 | SECONE1 | SECONE0 |

| bit 7 |         |         |         |         |         |         | bit 0   |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

#### bit 7 Unimplemented: Read as '0'

bit 6-4 SECTEN<2:0>: Binary Coded Decimal Value of Second's Tens Digit bits Contains a value from 0 to 5.

bit 3-0 SECONE<3:0>: Binary Coded Decimal Value of Second's Ones Digit bits Contains a value from 0 to 9. When a shutdown event occurs, two things happen:

- The ECCPxASE bit is set to '1'. The ECCPxASE will remain set until cleared in firmware or an auto-restart occurs. (See Section 19.4.5 "Auto-Restart Mode".)

- The enabled PWM pins are asynchronously placed in their shutdown states. The PWM output pins are grouped into pairs (PxA/PxC) and

(PxB/PxD). The state of each pin pair is determined by the PSSxAC and PSSxBD bits (ECCPxAS<3:0>).

Each pin pair may be placed into one of three states:

- Drive logic '1'

- Drive logic '0'

- Tri-state (high-impedance)

# REGISTER 19-4: ECCPxAS: ECCP1/2/3 AUTO-SHUTDOWN CONTROL REGISTER (1, ACCESS FBEh; 2, FB8h; 3, BANKED F19h)

| R/W-0    | R/W-0    | R/W-0    | R/W-0    | R/W-0   | R/W-0   | R/W-0   | R/W-0   |

|----------|----------|----------|----------|---------|---------|---------|---------|

| ECCPxASE | ECCPxAS2 | ECCPxAS1 | ECCPxAS0 | PSSxAC1 | PSSxAC0 | PSSxBD1 | PSSxBD0 |

| bit 7    |          |          |          |         |         |         | bit 0   |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7   | ECCPxASE: ECCP Auto-Shutdown Event Status bit                                                                                                                                                                                                                                                                                                                                          |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 1 = A shutdown event has occurred; ECCP outputs are in a shutdown state                                                                                                                                                                                                                                                                                                                |

|         | 0 = ECCP outputs are operating                                                                                                                                                                                                                                                                                                                                                         |

| bit 6-4 | ECCPxAS<2:0>: ECCP Auto-Shutdown Source Select bits                                                                                                                                                                                                                                                                                                                                    |

|         | <ul> <li>000 = Auto-shutdown is disabled</li> <li>001 = Comparator, C1OUT, output is high</li> <li>010 = Comparator, C2OUT, output is high</li> <li>011 = Either comparator, C1OUT or C2OUT, is high</li> <li>100 = VIL on FLT0 pin</li> <li>101 = VIL on FLT0 pin or comparator, C1OUT, output is high</li> <li>110 = VIL on FLT0 pin or comparator, C2OUT, output is high</li> </ul> |

|         | 111 = VIL on FLT0 pin or comparator, C1OUT, or comparator, C2OUT, is high                                                                                                                                                                                                                                                                                                              |

| bit 3-2 | PSSxAC<1:0>: PxA and PxC Pins Shutdown State Control bits                                                                                                                                                                                                                                                                                                                              |

|         | 00 = Drive pins, PxA and PxC, to '0'<br>01 = Drive pins, PxA and PxC, to '1'<br>1x = PxA and PxC pins tri-state                                                                                                                                                                                                                                                                        |

| bit 1-0 | PSSxBD<1:0>: PxB and PxD Pins Shutdown State Control bits                                                                                                                                                                                                                                                                                                                              |

|         | 00 = Drive pins, PxB and PxD, to '0'<br>01 = Drive pins, PxB and PxD, to '1'<br>1x = PxB and PxD pins tri-state                                                                                                                                                                                                                                                                        |

| Note 1: | The auto-shutdown condition is a level-based signal, not an edge-based signal. As long as the level is present, the auto-shutdown will persist.                                                                                                                                                                                                                                        |

| 2:      | Writing to the ECCPxASE bit is disabled while an auto-shutdown condition persists.                                                                                                                                                                                                                                                                                                     |

| -       |                                                                                                                                                                                                                                                                                                                                                                                        |

3: Once the auto-shutdown condition has been removed and the PWM restarted (either through firmware or auto-restart), the PWM signal will always restart at the beginning of the next PWM period.

#### 20.2 **Control Registers**

Each MSSP module has three associated control registers. These include a status register (SSPxSTAT) and two control registers (SSPxCON1 and SSPxCON2). The use of these registers and their individual Configuration bits differs significantly depending on whether the MSSP module is operated in SPI or I<sup>2</sup>C mode.

Additional details are provided under the individual sections.

Note: In devices with more than one MSSP module, it is very important to pay close attention to the SSPxCON register names. SSP1CON1 and SSP1CON2 control different operational aspects of the same module, while SSP1CON1 and SSP2CON1 control the same features for two different modules.

#### 20.3 **SPI Mode**

The SPI mode allows 8 bits of data to be synchronously transmitted and received simultaneously. All four modes of SPI are supported.

When MSSP2 is used in SPI mode, it can optionally be configured to work with the SPI DMA submodule described in Section 20.4 "SPI DMA Module".

To accomplish communication, typically three pins are used:

- Serial Data Out (SDOx) RC7/CCP10/RX1/DT1/SDO1/RP18 or SDO2/Remappable

- · Serial Data In (SDIx) -RB5/CCP5/KBI1/SDI1/SDA1/RP8 or SDI2/Remappable

- Serial Clock (SCKx) RB4/CCP4/KBI0/SCK1/SCL1/RP7 or SCK2/Remappable

Additionally, a fourth pin may be used when in a Slave mode of operation:

Slave Select (SSx) – RA5/AN4/C1INC/SS1/ HLVDIN/RCV/RP2 or SS2/Remappable

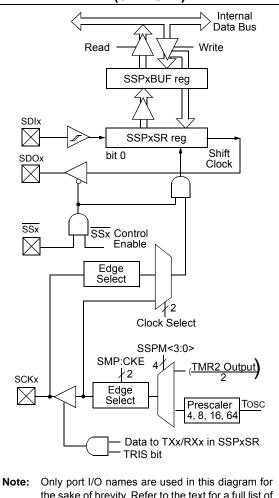

Figure 20-1 depicts the block diagram of the MSSP module when operating in SPI mode.

#### **FIGURE 20-1: MSSPx BLOCK DIAGRAM** (SPI MODE)

the sake of brevity. Refer to the text for a full list of multiplexed functions.

# PIC18F47J53

|       |                       |            |                             |                       | SYNC       | = 0, BRGH                   | I = 0, BRG            | 16 = 1     |                             |                       |            |                             |

|-------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|

| BAUD  | Fosc = 40.000 MHz     |            |                             | Fosc = 20.000 MHz     |            |                             | Fosc = 10.000 MHz     |            |                             | Fosc = 8.000 MHz      |            |                             |

| (K)   | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |

| 0.3   | 0.300                 | 0.00       | 8332                        | 0.300                 | 0.02       | 4165                        | 0.300                 | 0.02       | 2082                        | 0.300                 | -0.04      | 1665                        |

| 1.2   | 1.200                 | 0.02       | 2082                        | 1.200                 | -0.03      | 1041                        | 1.200                 | -0.03      | 520                         | 1.201                 | -0.16      | 415                         |

| 2.4   | 2.402                 | 0.06       | 1040                        | 2.399                 | -0.03      | 520                         | 2.404                 | 0.16       | 259                         | 2.403                 | -0.16      | 207                         |

| 9.6   | 9.615                 | 0.16       | 259                         | 9.615                 | 0.16       | 129                         | 9.615                 | 0.16       | 64                          | 9.615                 | -0.16      | 51                          |

| 19.2  | 19.231                | 0.16       | 129                         | 19.231                | 0.16       | 64                          | 19.531                | 1.73       | 31                          | 19.230                | -0.16      | 25                          |

| 57.6  | 58.140                | 0.94       | 42                          | 56.818                | -1.36      | 21                          | 56.818                | -1.36      | 10                          | 55.555                | 3.55       | 8                           |

| 115.2 | 113.636               | -1.36      | 21                          | 113.636               | -1.36      | 10                          | 125.000               | 8.51       | 4                           | _                     | _          | —                           |

| TABLE 21-3: BAUD RATES FOR ASYNCHRONOUS MODES (CONT |

|-----------------------------------------------------|

|-----------------------------------------------------|

|             | SYNC = 0, BRGH = 0, BRG16 = 1 |            |                             |                       |            |                             |                       |                  |                             |  |  |  |

|-------------|-------------------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------------|-----------------------------|--|--|--|

| BAUD        | Foso                          | c = 4.000  | MHz                         | Fos                   | c = 2.000  | MHz                         | Fos                   | Fosc = 1.000 MHz |                             |  |  |  |

| RATE<br>(K) | Actual<br>Rate<br>(K)         | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error       | SPBRG<br>value<br>(decimal) |  |  |  |

| 0.3         | 0.300                         | 0.04       | 832                         | 0.300                 | -0.16      | 415                         | 0.300                 | -0.16            | 207                         |  |  |  |

| 1.2         | 1.202                         | 0.16       | 207                         | 1.201                 | -0.16      | 103                         | 1.201                 | -0.16            | 51                          |  |  |  |

| 2.4         | 2.404                         | 0.16       | 103                         | 2.403                 | -0.16      | 51                          | 2.403                 | -0.16            | 25                          |  |  |  |

| 9.6         | 9.615                         | 0.16       | 25                          | 9.615                 | -0.16      | 12                          | —                     | _                | _                           |  |  |  |

| 19.2        | 19.231                        | 0.16       | 12                          | —                     | _          | _                           | —                     | _                | _                           |  |  |  |

| 57.6        | 62.500                        | 8.51       | 3                           | —                     | _          | _                           | —                     | _                | _                           |  |  |  |

| 115.2       | 125.000                       | 8.51       | 1                           | _                     | _          |                             | _                     | —                | —                           |  |  |  |

|              |                       | SYNC = 0, BRGH = 1, BRG16 = 1 or SYNC = 1, BRG16 = 1 |                             |                       |            |                             |                       |            |                             |                       |            |                             |  |  |  |

|--------------|-----------------------|------------------------------------------------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|--|--|--|

| BAUD<br>RATE | Fosc = 40.000 MHz     |                                                      |                             | Fosc = 20.000 MHz     |            |                             | Fosc = 10.000 MHz     |            |                             | Fosc = 8.000 MHz      |            |                             |  |  |  |

| (K)          | Actual<br>Rate<br>(K) | %<br>Error                                           | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |  |  |  |

| 0.3          | 0.300                 | 0.00                                                 | 33332                       | 0.300                 | 0.00       | 16665                       | 0.300                 | 0.00       | 8332                        | 0.300                 | -0.01      | 6665                        |  |  |  |

| 1.2          | 1.200                 | 0.00                                                 | 8332                        | 1.200                 | 0.02       | 4165                        | 1.200                 | 0.02       | 2082                        | 1.200                 | -0.04      | 1665                        |  |  |  |

| 2.4          | 2.400                 | 0.02                                                 | 4165                        | 2.400                 | 0.02       | 2082                        | 2.402                 | 0.06       | 1040                        | 2.400                 | -0.04      | 832                         |  |  |  |

| 9.6          | 9.606                 | 0.06                                                 | 1040                        | 9.596                 | -0.03      | 520                         | 9.615                 | 0.16       | 259                         | 9.615                 | -0.16      | 207                         |  |  |  |

| 19.2         | 19.193                | -0.03                                                | 520                         | 19.231                | 0.16       | 259                         | 19.231                | 0.16       | 129                         | 19.230                | -0.16      | 103                         |  |  |  |

| 57.6         | 57.803                | 0.35                                                 | 172                         | 57.471                | -0.22      | 86                          | 58.140                | 0.94       | 42                          | 57.142                | 0.79       | 34                          |  |  |  |

| 115.2        | 114.943               | -0.22                                                | 86                          | 116.279               | 0.94       | 42                          | 113.636               | -1.36      | 21                          | 117.647               | -2.12      | 16                          |  |  |  |

|       |                       | SYNC = 0, BRGH = 1, BRG16 = 1 or SYNC = 1, BRG16 = 1 |                             |                       |            |                             |                       |            |                             |  |  |  |  |

|-------|-----------------------|------------------------------------------------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|--|--|--|--|

| BAUD  | Fost                  | c = 4.000                                            | MHz                         | Fos                   | c = 2.000  | MHz                         | Fosc = 1.000 MHz      |            |                             |  |  |  |  |

| (K)   | Actual<br>Rate<br>(K) | %<br>Error                                           | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |  |  |  |  |

| 0.3   | 0.300                 | 0.01                                                 | 3332                        | 0.300                 | -0.04      | 1665                        | 0.300                 | -0.04      | 832                         |  |  |  |  |

| 1.2   | 1.200                 | 0.04                                                 | 832                         | 1.201                 | -0.16      | 415                         | 1.201                 | -0.16      | 207                         |  |  |  |  |

| 2.4   | 2.404                 | 0.16                                                 | 415                         | 2.403                 | -0.16      | 207                         | 2.403                 | -0.16      | 103                         |  |  |  |  |

| 9.6   | 9.615                 | 0.16                                                 | 103                         | 9.615                 | -0.16      | 51                          | 9.615                 | -0.16      | 25                          |  |  |  |  |

| 19.2  | 19.231                | 0.16                                                 | 51                          | 19.230                | -0.16      | 25                          | 19.230                | -0.16      | 12                          |  |  |  |  |

| 57.6  | 58.824                | 2.12                                                 | 16                          | 55.555                | 3.55       | 8                           | —                     | _          | —                           |  |  |  |  |

| 115.2 | 111.111               | -3.55                                                | 8                           | —                     | _          | —                           | —                     | _          | —                           |  |  |  |  |

# 22.1 A/D Acquisition Requirements

For the A/D Converter to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage level. The analog input model is illustrated in Figure 22-2. The source impedance (Rs) and the internal sampling switch (Rss) impedance directly affect the time required to charge the capacitor, CHOLD. The sampling switch (Rss) impedance varies over the device voltage (VDD). The source impedance affects the offset voltage at the analog input (due to pin leakage current). The maximum recommended impedance for analog sources is 2.5 k $\Omega$  for 10-bit conversions and 1 k $\Omega$ for 12-bit conversions. After the analog input channel is selected (changed), the channel must be sampled for at least the minimum acquisition time before starting a conversion.

| Note: | When    | the    | conversion      | is   | started,   | the |

|-------|---------|--------|-----------------|------|------------|-----|

|       | holding | g capa | acitor is disco | onne | ected from | the |

|       | input p | in.    |                 |      |            |     |

### EQUATION 22-1: ACQUISITION TIME

TACQ = Amplifier Settling Time + Holding Capacitor Charging Time + Temperature Coefficient = TAMP + TC + TCOFF

#### EQUATION 22-2: A/D MINIMUM CHARGING TIME

$VHOLD = (VREF - (VREF/2048)) \cdot (1 - e^{(-TC/CHOLD(RIC + RSS + RS))})$ or  $TC = -(CHOLD)(RIC + RSS + RS) \ln(1/2048)$

#### EQUATION 22-3: CALCULATING THE MINIMUM REQUIRED ACQUISITION TIME

| J | Facq    | =      | TAMP + TC + TCOFF                                                                                                                                |

|---|---------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| ] | ГАМР    | =      | 0.2 μs                                                                                                                                           |

| 1 | ſcoff   | =      | (Temp – 25°C)(0.02 μs/°C)<br>(85°C – 25°C)(0.02 μs/°C)<br>1.2 μs                                                                                 |

| Г | Fempera | ture c | oefficient is only required for temperatures > 25°C. Below 25°C, TCOFF = 0 $\mu$ s.                                                              |

| 1 | ГC      | =      | -(Chold)(Ric + Rss + Rs) $\ln(1/2048) \ \mu s$<br>-(25 pF) (1 k $\Omega$ + 2 k $\Omega$ + 2.5 k $\Omega$ ) ln(0.0004883) $\mu s$<br>1.05 $\mu s$ |

| 1 | Γacq    | =      | 0.2 μs + 1.05 μs + 1.2 μs<br>2.45 μs                                                                                                             |

To calculate the minimum acquisition time, Equation 22-1 may be used. This equation assumes that 1/2 LSb error is used (1,024 steps for the 10-bit A/D). The 1/2 LSb error is the maximum error allowed for the A/D to meet its specified resolution.

Equation 22-3 provides the calculation of the minimum required acquisition time, TACQ. This calculation is based on the following application system assumptions:

| CHOLD            | =      | 25 pF                              |

|------------------|--------|------------------------------------|

| Rs               | =      | 2.5 kΩ                             |

| Conversion Error | $\leq$ | 1/2 LSb                            |

| Vdd              | =      | $3V \rightarrow Rss = 2 \ k\Omega$ |

| Temperature      | =      | 85°C (system max.)                 |

| R/W-0      | R/W-0                                                                              | U-0                                | R/W-0                                | R/W-0                   | R/W-0               | R/W-0              | R/W-0        |

|------------|------------------------------------------------------------------------------------|------------------------------------|--------------------------------------|-------------------------|---------------------|--------------------|--------------|

| UTEYE      | E UOEMON                                                                           | _                                  | UPUEN <sup>(1,2)</sup>               | UTRDIS <sup>(1,3)</sup> | FSEN <sup>(1)</sup> | PPB1               | PPB0         |

| bit 7      |                                                                                    |                                    |                                      |                         |                     | ·                  | bit C        |

|            |                                                                                    |                                    |                                      |                         |                     |                    |              |

| Legend:    |                                                                                    |                                    |                                      |                         |                     |                    |              |

| R = Reada  | able bit                                                                           | W = Writable                       | e bit                                | U = Unimplen            | nented bit, read    | d as '0'           |              |

| -n = Value | at POR                                                                             | '1' = Bit is se                    | t                                    | '0' = Bit is clea       | ared                | x = Bit is unkr    | nown         |

| hit 7      |                                                                                    | Dettorn                            | Fact Enchla hit                      |                         |                     |                    |              |

| bit 7      |                                                                                    | ern test is ena                    | Test Enable bit                      |                         |                     |                    |              |

|            |                                                                                    | ern test is disa                   |                                      |                         |                     |                    |              |

| bit 6      | UOEMON: U                                                                          | SB OE Monito                       | r Enable bit                         |                         |                     |                    |              |

|            | $1 = \overline{\text{UOE}} \text{ sig}$<br>$0 = \overline{\text{UOE}} \text{ sig}$ |                                    | cating intervals                     | during which t          | he D+/D- lines      | are driving        |              |

| bit 5      | •                                                                                  | nted: Read as                      | ʻ0'                                  |                         |                     |                    |              |

| bit 4      | -                                                                                  |                                    | -up Enable bit <sup>(*</sup>         | 1,2)                    |                     |                    |              |

|            |                                                                                    |                                    | led (pull-up on                      |                         | = 1 or D- with      | FSEN = 0)          |              |

|            |                                                                                    | oull-up is disab                   |                                      |                         |                     |                    |              |

| bit 3      |                                                                                    |                                    | ver Disable bit                      | 1,3)                    |                     |                    |              |

|            |                                                                                    | ransceiver is o<br>ransceiver is a |                                      |                         |                     |                    |              |

| bit 2      | •                                                                                  | peed Enable b                      |                                      |                         |                     |                    |              |

|            |                                                                                    |                                    | rols transceiver                     |                         |                     |                    |              |

|            |                                                                                    |                                    | trols transceive                     | -                       | equires input cl    | lock at 6 MHz      |              |

| bit 1-0    |                                                                                    |                                    | ers Configuratio                     |                         | =                   |                    |              |

|            |                                                                                    |                                    | ouffers are enal<br>ouffers are enal |                         |                     |                    |              |

|            |                                                                                    |                                    | ouffer are enabl                     |                         |                     |                    |              |

|            | 00 = Even/O                                                                        | dd ping-pong l                     | ouffers are disa                     | bled                    | •                   |                    |              |

| Note 1:    | The UPUEN, UTF                                                                     | DIS and FSE                        | N bits should ne                     | ever be change          | d while the US      | B module is en     | abled. These |

|            | values must be pr                                                                  | • ·                                | •                                    |                         |                     |                    |              |

| 2:         | This bit is only vali                                                              | d when the on-                     | chip transceive                      | r is active (UTF        | RDIS = 0); othe     | rwise, it is ignor | ed.          |

**3:** If UTRDIS is set, the  $\overline{\text{UOE}}$  signal will be active – independent of the UOEMON bit setting.

| Mnemonic,<br>Operands    |                                 | Description                              |            | 16-Bit Instruction Word |      |      |          | Status          |            |

|--------------------------|---------------------------------|------------------------------------------|------------|-------------------------|------|------|----------|-----------------|------------|

|                          |                                 | Description                              | Cycles     | MSb                     |      | LSb  | Affected | Notes           |            |

| BYTE-ORIENTED OPERATIONS |                                 |                                          |            |                         |      |      |          |                 |            |

| ADDWF                    | f, d, a                         | f, d, a Add WREG and f                   |            | 0010                    | 01da | ffff | ffff     | C, DC, Z, OV, N | 1, 2       |

| ADDWFC                   | f, d, a                         | Add WREG and Carry bit to f              | 1          | 0010                    | 00da | ffff | ffff     | C, DC, Z, OV, N | 1, 2       |

| ANDWF                    | f, d, a                         | AND WREG with f                          | 1          | 0001                    | 01da | ffff | ffff     | Z, N            | 1,2        |

| CLRF                     | f, a                            | Clear f                                  | 1          | 0110                    | 101a | ffff | ffff     | Z               | 2          |

| COMF                     | f, d, a                         | Complement f                             | 1          | 0001                    | 11da | ffff | ffff     | Z, N            | 1, 2       |

| CPFSEQ                   | f, a                            | Compare f with WREG, Skip =              | 1 (2 or 3) | 0110                    | 001a | ffff | ffff     | None            | 4          |

| CPFSGT                   | f, a                            | Compare f with WREG, Skip >              | 1 (2 or 3) | 0110                    | 010a | ffff | ffff     | None            | 4          |

| CPFSLT                   | f, a                            | Compare f with WREG, Skip <              | 1 (2 or 3) | 0110                    | 000a | ffff | ffff     | None            | 1, 2       |

| DECF                     | f, d, a                         | Decrement f                              | 1          | 0000                    | 01da | ffff | ffff     | C, DC, Z, OV, N | 1, 2, 3, 4 |

| DECFSZ                   | f, d, a                         | Decrement f, Skip if 0                   | 1 (2 or 3) | 0010                    | 11da | ffff | ffff     |                 | 1, 2, 3, 4 |