Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                     |

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 48MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART, USB                               |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                        |

| Number of I/O              | 34                                                                           |

| Program Memory Size        | 128KB (64K x 16)                                                             |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 3.8K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 2.75V                                                                   |

| Data Converters            | A/D 13x10b/12b                                                               |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 44-VQFN Exposed Pad                                                          |

| Supplier Device Package    | 44-QFN (8x8)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf47j53t-i-ml |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 28-SPDIP/<br>SSOP/<br>SOIC                                                                                                                                                                                                                                                                   | 28-QFN                                | Pin<br>Type                                     | Buffer<br>Type                                                   | Description                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|-------------------------------------------------|------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 1 <sup>(2)</sup>                                                                                                                                                                                                                                                                             |                                       |                                                 |                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

|                                                                                                                                                                                                                                                                                              | 26 <sup>(2)</sup>                     | I                                               | ST                                                               | Master Clear (Reset) input. This pin is an active-low Reset to the device.                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| 9                                                                                                                                                                                                                                                                                            | 6                                     | I                                               | ST                                                               | Oscillator crystal or external clock input.<br>Oscillator crystal input or external clock source<br>input. ST buffer when configured in RC mode;<br>CMOS otherwise. Main oscillator input<br>connection.                                                                                                                                                                                                          |  |  |  |  |

|                                                                                                                                                                                                                                                                                              |                                       | I                                               | CMOS                                                             | External clock source input; always associated with pin function OSC1 (see related OSC1/CLKI pins).                                                                                                                                                                                                                                                                                                               |  |  |  |  |

|                                                                                                                                                                                                                                                                                              |                                       | I/O                                             | TTL/DIG                                                          | Digital I/O.                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| 10                                                                                                                                                                                                                                                                                           | 7                                     | 0                                               | _                                                                | Oscillator crystal or clock output.<br>Oscillator crystal output. Connects to crystal or<br>resonator in Crystal Oscillator mode.                                                                                                                                                                                                                                                                                 |  |  |  |  |

|                                                                                                                                                                                                                                                                                              |                                       | 0                                               | DIG                                                              | Main oscillator feedback output connection.<br>In RC mode, OSC2 pin outputs CLKO, which<br>has 1/4 the frequency of OSC1 and denotes<br>the instruction cycle rate.                                                                                                                                                                                                                                               |  |  |  |  |

|                                                                                                                                                                                                                                                                                              |                                       | I/O                                             | TTL/DIG                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| Legend:       TTL = TTL compatible input       CMOS       = CMOS compatible input or output         ST = Schmitt Trigger input with CMOS levels       Analog       = Analog input         I = Input       O       = Output         P = Power       OD       = Open-Drain (no P diode to VDD) |                                       |                                                 |                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| t                                                                                                                                                                                                                                                                                            | 10<br>Datible input<br>rigger input w | 10 7<br>batible input<br>rigger input with CMOS | I I I/O<br>10 7 O<br>0<br>1/O<br>1/O<br>1/O<br>1/O<br>1/O<br>1/O | I     ST       I     CMOS       I     II/O       I     TTL/DIG       I     I/O       I/O     TTL/DIG       I/O     I/O       I/O     TTL/DIG       I/O     TTL/DIG       I/O     TTL/DIG       I/O     TTL/DIG       I/O     Ar       O     O       O     O       I     O |  |  |  |  |

TABLE 1-3:

PIC18F2XJ53 PINOUT I/O DESCRIPTIONS

Note 1: RA7 and RA6 will be disabled if OSC1 and OSC2 are used for the clock function.

2: 5.5V tolerant.

|                                                                                                                                | Pin Nu                            | mber |                              |                                                           |                                                                                                                                                                                                    |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|------|------------------------------|-----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Pin Name                                                                                                                       | 28-SPDIP/<br>SSOP/ 28-QFN<br>SOIC |      | Pin Buffer<br>Type Type      |                                                           | Description                                                                                                                                                                                        |  |  |  |

|                                                                                                                                |                                   |      |                              |                                                           | PORTB is a bidirectional I/O port. PORTB can be<br>software programmed for internal weak pull-ups<br>on all inputs.                                                                                |  |  |  |

| RB0/AN12/C3IND/INT0/RP3<br>RB0<br>AN12<br>C3IND<br>INT0<br>RP3                                                                 | 21                                | 18   | I/O<br>I<br>I<br>I/O         | TTL/DIG<br>Analog<br>Analog<br>ST<br>ST/DIG               | Digital I/O.<br>Analog Input 12.<br>Comparator 3 Input D.<br>External Interrupt 0.<br>Remappable Peripheral Pin 3 input/output.                                                                    |  |  |  |

| RB1/AN10/C3INC/RTCC/RP4<br>RB1<br>AN10<br>C3INC<br>RTCC<br>RP4                                                                 | 22                                | 19   | I/O<br>I<br>I<br>O<br>I/O    | TTL/DIG<br>Analog<br>Analog<br>DIG<br>ST/DIG              | Digital I/O.<br>Analog Input 10.<br>Comparator 3 input.<br>Asynchronous serial transmit data output.<br>Remappable Peripheral Pin 4 input/output.                                                  |  |  |  |

| RB2/AN8/C2INC/CTED1/<br>VMO/REFO/RP5<br>RB2<br>AN8<br>C2INC<br>CTED1<br>VMO<br>REFO<br>RP5                                     | 23                                | 20   | I/O<br> <br> <br> <br>0 0 /O | TTL/DIG<br>Analog<br>Analog<br>ST<br>DIG<br>DIG<br>ST/DIG | Digital I/O.<br>Analog Input 8.<br>Comparator 2 Input C.<br>CTMU Edge 1 input.<br>External USB Transceiver D- data output.<br>Reference output clock.<br>Remappable Peripheral Pin 5 input/output. |  |  |  |

| RB3/AN9/C3INA/CTED2/<br>VPO/RP6<br>RB3<br>AN9<br>C3INA<br>CTED2<br>VPO<br>RP6                                                  | 24                                | 21   | I/O<br> <br> <br> <br>0<br>  | TTL/DIG<br>Analog<br>Analog<br>ST<br>DIG<br>ST/DIG        | Digital I/O.<br>Analog Input 9.<br>Comparator 3 Input A.<br>CTMU edge 2 Input.<br>External USB Transceiver D+ data output.<br>Remappable Peripheral Pin 6 input/output.                            |  |  |  |

| Legend: TTL = TTL compati<br>ST = Schmitt Trigg<br>I = Input<br>P = Power<br>DIG = Digital outpu<br>Note 1: RA7 and RA6 will b | ger input wi<br>t                 |      |                              | Ar<br>O<br>OI<br>I <sup>2</sup> (                         | MOS = CMOS compatible input or output<br>nalog = Analog input<br>= Output<br>D = Open-Drain (no P diode to VDD)                                                                                    |  |  |  |

## TABLE 1-3: PIC18F2XJ53 PINOUT I/O DESCRIPTIONS (CONTINUED)

Note 1: RA7 and RA6 will be disabled if OSC1 and OSC2 are used for the clock function.

2: 5.5V tolerant.

| TABLE 1-3: | PIC18F2XJ53 PINOUT I/O DESCRIPTIONS (CONTINUED) |

|------------|-------------------------------------------------|

| IADLL I-J. |                                                 |

|                                                                                                                                                      | Pin Number<br>28-SPDIP/<br>SSOP/<br>SOIC |                   |                           |                                                   |                                                                                                                                                                                                         |

|------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|-------------------|---------------------------|---------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name                                                                                                                                             |                                          |                   | Pin<br>Type               | Buffer<br>Type                                    | Description                                                                                                                                                                                             |

|                                                                                                                                                      |                                          |                   |                           |                                                   | PORTC is a bidirectional I/O port.                                                                                                                                                                      |

| RC0/T1OSO/T1CKI/RP11<br>RC0<br>T1OSO<br>T1CKI<br>RP11                                                                                                | 11                                       | 8                 | I/O<br>O<br>I<br>I/O      | ST/DIG<br>Analog<br>ST<br>ST/DIG                  | Digital I/O.<br>Timer1 oscillator output.<br>Timer1 external digital clock input.<br>Remappable Peripheral Pin 11 input/output.                                                                         |

| RC1/CCP8/T1OSI/UOE/RP12<br>RC1<br>CCP8<br>T1OSI<br>UOE<br>RP12                                                                                       | 12                                       | 9                 | I/O<br>I/O<br>I<br>I/O    | ST/DIG<br>ST/DIG<br>Analog<br>DIG<br>ST/DIG       | Digital I/O.<br>Capture/Compare/PWM input/output.<br>Timer1 oscillator input.<br>External USB transceiver NOE output.<br>Remappable Peripheral Pin 12 input/output.                                     |

| RC2/AN11/C2IND/CTPLS/<br>RP13<br>RC2<br>AN11<br>C2IND<br>CTPLS<br>RP13                                                                               | 13                                       | 10                | I/O<br>I<br>I<br>0<br>I/O | ST/DIG<br>Analog<br>Analog<br>DIG<br>ST/DIG       | Digital I/O.<br>Analog Input 11.<br>Comparator 2 Input D.<br>CTMU pulse generator output.<br>Remappable Peripheral Pin 13 input/output.                                                                 |

| RC4/D-/VM<br>RC4<br>D-<br>VM                                                                                                                         | 15                                       | 12                | l<br>I/O<br>I             | ST<br>—<br>ST                                     | Digital Input.<br>USB bus minus line input/output.<br>External USB transceiver FM input.                                                                                                                |

| RC5/D+/VP<br>RC5<br>D+<br>VP                                                                                                                         | 16                                       | 13                | <br> /O<br>               | ST<br>—<br>ST                                     | Digital Input.<br>USB bus plus line input/output.<br>External USB transceiver VP input.                                                                                                                 |

| RC6/CCP9/TX1/CK1/RP17<br>RC6<br>CCP9<br>TX1<br>CK1<br>RP17                                                                                           | 17 <sup>(2)</sup>                        | 14 <sup>(2)</sup> | I/O<br>I/O<br>I/O<br>I/O  | ST/DIG<br>ST/DIG<br>DIG<br>ST/DIG<br>ST/DIG       | Digital I/O.<br>Capture/Compare/PWM input/output.<br>EUSART1 asynchronous transmit.<br>EUSART1 synchronous clock (see related<br>RX1/DT1).<br>Remappable Peripheral Pin 17 input/output.                |

| RC7/CCP10/RX1/DT1/SDO1/<br>RP18<br>RC7<br>CCP10<br>RX1<br>DT1<br>SDO1<br>RP18                                                                        | 18 <sup>(2)</sup>                        | 15 <sup>(2)</sup> | I/O<br>I/O<br>I/O<br>I/O  | ST/DIG<br>ST/DIG<br>ST<br>ST/DIG<br>DIG<br>ST/DIG | Digital I/O.<br>Asynchronous serial receive data input.<br>Capture/Compare/PWM input/output.<br>Synchronous serial data output/input.<br>SPI data output.<br>Remappable Peripheral Pin 18 input/output. |

| Legend: TTL = TTL compati<br>ST = Schmitt Trigg<br>I = Input<br>P = Power<br>DIG = Digital outpu<br>Note 1: RA7 and RA6 will be<br>2: 5.5V tolerant. | ger input wi                             |                   |                           | Ar<br>O<br>OI<br>I <sup>2</sup> (                 | D = Open-Drain (no P diode to VDD)                                                                                                                                                                      |

| Input Oscillator<br>Frequency | PLL Division<br>(PLLDIV<2:0>) | Clock Mode<br>(FOSC<2:0>) | MCU Clock Division<br>(CPDIV<1:0>) | Microcontroller<br>Clock Frequency |

|-------------------------------|-------------------------------|---------------------------|------------------------------------|------------------------------------|

|                               |                               |                           | None (11)                          | 48 MHz                             |

|                               | N1/A                          | 50                        | ÷2(10)                             | 24 MHz                             |

| 48 MHz                        | N/A                           | EC                        | ÷3(01)                             | 16 MHz                             |

|                               |                               |                           | ÷6 (00)                            | 8 MHz                              |

|                               |                               |                           | None (11)                          | 48 MHz                             |

|                               | 10 (000)                      | FORM                      | ÷2(10)                             | 24 MHz                             |

| 48 MHz                        | ÷12 (000)                     | ECPLL                     | ÷3(01)                             | 16 MHz                             |

|                               |                               |                           | ÷6 (00)                            | 8 MHz                              |

|                               |                               |                           | None (11)                          | 48 MHz                             |

|                               | 10 (001)                      | FORM                      | ÷2(10)                             | 24 MHz                             |

| 40 MHz                        | ÷10(001)                      | ECPLL                     | ÷3(01)                             | 16 MHz                             |

|                               |                               |                           | ÷6 (00)                            | 8 MHz                              |

|                               |                               |                           | None (11)                          | 48 MHz                             |

|                               | 0 (00.0)                      | FORM                      | ÷2 (10)                            | 24 MHz                             |

| 24 MHz                        | ÷6 (010)                      | ECPLL                     | ÷3(01)                             | 16 MHz                             |

|                               |                               |                           | ÷6 (00)                            | 8 MHz                              |

|                               |                               | EC <sup>(1)</sup>         | None (11)                          | 24 MHz                             |

| 24 MHz                        | N//A                          |                           | ÷2 (10)                            | 12 MHz                             |

| 24 MHZ                        | N/A                           |                           | ÷3 (01)                            | 8 MHz                              |

|                               |                               |                           | ÷6 (00)                            | 4 MHz                              |

|                               |                               |                           | None (11)                          | 48 MHz                             |

|                               | - ()                          | 50011                     | ÷2 (10)                            | 24 MHz                             |

| 20 MHz                        | ÷5 (011)                      | ECPLL                     | ÷3(01)                             | 16 MHz                             |

|                               |                               |                           | ÷6 (00)                            | 8 MHz                              |

|                               |                               |                           | None (11)                          | 48 MHz                             |

|                               |                               |                           | ÷2 (10)                            | 24 MHz                             |

| 16 MHz                        | ÷4 (100)                      | HSPLL, ECPLL              | ÷3 (01)                            | 16 MHz                             |

|                               |                               |                           | ÷6 (00)                            | 8 MHz                              |

|                               |                               |                           | None (11)                          | 48 MHz                             |

|                               | 0 (2.22.)                     |                           | ÷2 (10)                            | 24 MHz                             |

| 12 MHz                        | ÷3(101)                       | HSPLL, ECPLL              | ÷3(01)                             | 16 MHz                             |

|                               |                               |                           | ÷6 (00)                            | 8 MHz                              |

|                               |                               |                           | None (11)                          | 48 MHz                             |

| 0.0411-                       | 0 (5 5 5)                     | HSPLL, ECPLL,             | ÷2 (10)                            | 24 MHz                             |

| 8 MHz                         | ÷2 (110)                      | INTOSCPLL/<br>INTOSCPLLO  | ÷3(01)                             | 16 MHz                             |

|                               |                               |                           | ÷6 (00)                            | 8 MHz                              |

|                               |                               |                           | None (11)                          | 48 MHz                             |

| 4.8411                        | 4 ()                          |                           | ÷2 (10)                            | 24 MHz                             |

| 4 MHz                         | ÷ <b>1</b> (111)              | HSPLL, ECPLL              | ÷3(01)                             | 16 MHz                             |

|                               |                               |                           | ÷6 (00)                            | 8 MHz                              |

| <b>TABLE 3-5:</b> | OSCILLATOR CONFIGURATION OPTIONS FOR USB OPERATION |

|-------------------|----------------------------------------------------|

|                   |                                                    |

Note 1: The 24 MHz EC mode (without PLL) is only compatible with low-speed USB. Full-speed USB requires a 48 MHz system clock.

#### REGISTER 5-1: RCON: RESET CONTROL REGISTER (ACCESS FD0h)

| R/W-0 | U-0 | R/W-1 | R/W-1 | R-1 | R-1 | R/W-0 | R/W-0 |

|-------|-----|-------|-------|-----|-----|-------|-------|

| IPEN  | —   | CM    | RI    | TO  | PD  | POR   | BOR   |

| bit 7 |     |       |       |     |     |       | bit 0 |

| Legend:    |           |                                                                                 |                                                                   |                                       |

|------------|-----------|---------------------------------------------------------------------------------|-------------------------------------------------------------------|---------------------------------------|

| R = Reada  | ble bit   | W = Writable bit                                                                | U = Unimplemented bit                                             | , read as '0'                         |

| -n = Value | at POR    | '1' = Bit is set                                                                | '0' = Bit is cleared                                              | x = Bit is unknown                    |

| bit 7      | IPEN: Int | errupt Priority Enable bit                                                      |                                                                   |                                       |

|            |           | ble priority levels on interrup<br>ble priority levels on interru               | its<br>ots (PIC16CXXX Compatibility                               | mode)                                 |

| bit 6      | Unimple   | mented: Read as '0'                                                             |                                                                   |                                       |

| bit 5      | CM: Con   | figuration Mismatch Flag bit                                                    |                                                                   |                                       |

|            | 0 = A C c | onfiguration Mismatch Rese<br>onfiguration Mismatch Rese<br>natch Reset occurs) |                                                                   | in software after a Configuratio      |

| bit 4      | RI: RESE  | ${\mathbb T}$ Instruction Flag bit                                              |                                                                   |                                       |

|            | 0 = The   |                                                                                 | executed (set by firmware only<br>cuted causing a device Rese     | )<br>t (must be set in software after |

| bit 3      | TO: Wate  | chdog Time-out Flag bit                                                         |                                                                   |                                       |

|            |           | by power-up, CLRWDT instru<br>DT time-out occurred                              | ction or SLEEP instruction                                        |                                       |

| bit 2      | PD: Pow   | er-Down Detection Flag bit                                                      |                                                                   |                                       |

|            |           | by power-up or by the CLRW<br>by execution of the SLEEP in                      |                                                                   |                                       |

| bit 1      | POR: Po   | wer-on Reset Status bit                                                         |                                                                   |                                       |

|            |           | ower-on Reset has not occu<br>ower-on Reset occurred (mu                        | rred (set by firmware only)<br>Ist be set in software after a Po  | ower-on Reset occurs)                 |

| bit 0      | BOR: Br   | own-out Reset Status bit                                                        |                                                                   |                                       |

|            |           | rown-out Reset has not occ                                                      | urred (set by firmware only)<br>uust be set in software after a E | Brown-out Reset occurs)               |

<sup>2:</sup> If the on-chip voltage regulator is disabled, BOR remains '0' at all times. See Section 5.4.1 "Detecting BOR" for more information.

**<sup>3:</sup>** Brown-out Reset is said to have occurred when BOR is '0' and POR is '1' (assuming that POR was set to '1' by software immediately after a Power-on Reset).

## 5.5 Configuration Mismatch (CM)

The Configuration Mismatch (CM) Reset is designed to detect, and attempt to recover from, random memory corrupting events. These include Electrostatic Discharge (ESD) events, which can cause widespread single bit changes throughout the device and result in catastrophic failure.

In PIC18FXXJ Flash devices, the device Configuration registers (located in the configuration memory space) are continuously monitored during operation by comparing their values to complimentary shadow registers. If a mismatch is detected between the two sets of registers, a CM Reset automatically occurs. These events are captured by the CM bit (RCON<5>). The state of the bit is set to '0' whenever a CM event occurs; it does not change for any other Reset event.

A CM Reset behaves similarly to a MCLR, RESET instruction, WDT time-out or Stack Event Resets. As with all hard and power Reset events, the device Configuration Words are reloaded from the Flash Configuration Words in program memory as the device restarts.

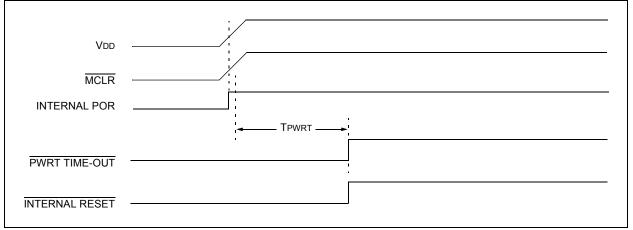

### 5.6 Power-up Timer (PWRT)

PIC18F47J53 family devices incorporate an on-chip PWRT to help regulate the POR process. The PWRT is always enabled. The main function is to ensure that the device voltage is stable before code is executed.

The Power-up Timer (PWRT) of the PIC18F47J53 family devices is a 5-bit counter which uses the INTRC source as the clock input. This yields an approximate time interval of  $32 \times 32 \ \mu s = 1 \ ms$ . While the PWRT is counting, the device is held in Reset.

The power-up time delay depends on the INTRC clock and will vary from chip-to-chip due to temperature and process variation. See DC parameter 33 (TPWRT) for details.

#### 5.6.1 TIME-OUT SEQUENCE

The PWRT time-out is invoked after the POR pulse has cleared. The total time-out will vary based on the status of the PWRT. Figure 5-2, Figure 5-3, Figure 5-4 and Figure 5-5 all depict time-out sequences on power-up with the PWRT.

Since the time-outs occur from the POR pulse, if  $\overline{\text{MCLR}}$ is kept low long enough, the PWRT will expire. Bringing  $\overline{\text{MCLR}}$  high will begin execution immediately if a clock source is available (Figure 5-4). This is useful for testing purposes or to synchronize more than one PIC18F device operating in parallel.

## FIGURE 5-2: TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD, VDD RISE < TPWRT)

| Addr.               | File Name | Bit 7 | Bit 6 | Bit 5    | Bit 4          | Bit 3                                 | Bit 2            | Bit 1         | Bit 0   | Value on<br>POR, BOR |

|---------------------|-----------|-------|-------|----------|----------------|---------------------------------------|------------------|---------------|---------|----------------------|

| EF4h                | RPINR14   | _     | _     | _        | Timer5 Gate I  | nput (T5G) to                         | Input Pin Map    | ping bits     |         | 1 1111               |

| EF3h                | RPINR13   | _     | _     | _        | Timer3 Gate I  | nput (T3G) to                         | Input Pin Map    | ping bits     |         | 1 1111               |

| EF2h                | RPINR12   | _     | _     | _        | Timer1 Gate I  | nput (T1G) to                         | Input Pin Map    | ping bits     |         | 1 1111               |

| EF1h                | —         | _     | _     | _        | _              | _                                     | _                | _             | _       |                      |

| EF0h                | _         | _     | _     | _        | _              | _                                     | _                | _             | _       |                      |

| EEFh                | —         | _     | _     | _        | _              | _                                     | _                | _             | _       |                      |

| EEEh                | _         | _     | _     | _        | _              | _                                     | _                | _             | _       |                      |

| EEDh                | —         | _     | _     | _        | _              | _                                     | _                | _             | _       |                      |

| EECh                | —         | _     | _     | _        | _              | _                                     | _                | _             | _       |                      |

| EEBh                | —         | _     | _     | _        | _              | _                                     | _                | _             | _       |                      |

| EEAh                | RPINR9    | _     | _     | _        | ECCP3 Input    | Capture (IC3)                         | ) to Input Pin N | lapping bits  |         | 1 1111               |

| EE9h                | RPINR8    | _     | _     | _        | ECCP2 Input    | Capture (IC2)                         | ) to Input Pin N | lapping bits  |         | 1 1111               |

| EE8h                | RPINR7    | _     | _     | _        | ECCP1 Input    | Capture (IC1)                         | ) to Input Pin N | lapping bits  |         | 1 1111               |

| EE7h                | RPINR15   | _     | _     | _        | Timer5 Extern  | al Clock Inpu                         | t (T5CKI) to In  | put Pin Mappi | ng bits | 1 1111               |

| EE6h                | RPINR6    | _     | _     | _        | Timer3 Extern  | al Clock Inpu                         | t (T3CKI) to In  | put Pin Mappi | ng bits | 1 1111               |

| EE5h                | —         | _     | _     | _        | _              | _                                     | _                | _             | _       |                      |

| EE4h                | RPINR4    | _     | _     | _        | Timer0 Extern  | al Clock Inpu                         | t (T0CKI) to In  | put Pin Mappi | ng bits | 1 1111               |

| EE3h                | RPINR3    | _     | _     | _        |                |                                       | Input Pin Map    |               | 0       | 1 1111               |

| EE2h                | RPINR2    | _     | _     | _        | External Inter | rupt (INT2) to                        | Input Pin Map    | ping bits     |         | 1 1111               |

| EE1h                | RPINR1    | _     | _     | _        |                | · · ·                                 | Input Pin Map    |               |         | 1 1111               |

| EE0h                | _         | _     | _     | _        | _              | _                                     | _                | _             | _       |                      |

| EDFh                |           | _     | _     | <u> </u> |                | _                                     | _                | _             | _       |                      |

| EDEh                |           | _     | _     | <u> </u> |                | _                                     | _                | _             | _       |                      |

| EDDh                |           | _     | _     | <u> </u> |                | _                                     | _                | _             | _       |                      |

| EDCh                | _         | _     | _     | _        | _              | _                                     | _                | _             | _       |                      |

| EDBh                |           | _     | _     | <u> </u> |                | _                                     | _                | _             | _       |                      |

| EDAh                | _         | _     | _     | _        | _              | _                                     | _                | _             | _       |                      |

| ED9h                |           | _     | _     | <u> </u> |                | _                                     | _                | _             | _       |                      |

| ED8h <sup>(1)</sup> | RPOR24    | _     | _     | _        | Remappable     | Pin RP24 Out                          | put Signal Sele  | ect bits      |         | 0 0000               |

| ED7h <sup>(1)</sup> | RPOR23    | _     | _     | <u> </u> |                |                                       | put Signal Sele  |               |         | 0 0000               |

| ED6h <sup>(1)</sup> | RPOR22    |       | _     | _        | Remappable     | Pin RP22 Out                          | put Signal Sele  | ect bits      |         | 0 0000               |

| ED5h <sup>(1)</sup> | RPOR21    | _     | _     | <u> </u> |                |                                       | put Signal Sele  |               |         | 0 0000               |

| ED4h <sup>(1)</sup> | RPOR20    | _     | _     | <u> </u> |                |                                       | put Signal Sele  |               |         | 0 0000               |

| ED3h <sup>(1)</sup> | RPOR19    | _     | _     | _        | Remappable     | Pin RP19 Out                          | put Signal Sele  | ect bits      |         | 0 0000               |

| ED2h                | RPOR18    | _     | _     | <u> </u> |                |                                       | put Signal Sele  |               |         | 0 0000               |

| ED1h                | RPOR17    | _     | _     | _        |                |                                       | put Signal Sele  |               |         | 0 0000               |

| ED0h <sup>)</sup>   | _         | _     | _     | _        | _              | _                                     | _                | —             | _       | 0 0000               |

| ECFh                | _         | _     | _     |          | _              | _                                     | _                | _             | _       | 0 0000               |

| ECEh                | _         | _     | _     | _        | _              | _                                     | _                | _             | _       | 0 0000               |

| ECDh                | RPOR13    | _     | _     | _        | Remappable     | Pin RP13 Out                          | put Signal Sele  | ect bits      |         | 0 0000               |

| ECCh                | RPOR12    | _     | _     | _        |                |                                       | put Signal Sele  |               |         | 0 0000               |

| ECBh                | RPOR11    | _     | _     | _        |                |                                       | put Signal Sele  |               |         | 0 0000               |

| ECAh                | RPOR10    | _     | _     | _        |                |                                       | put Signal Sele  |               |         | 0 0000               |

| EC9h                | RPOR9     | _     | _     |          |                |                                       | ut Signal Selec  |               |         | 0 0000               |

| EC8h                | RPOR8     | _     | _     |          |                |                                       | ut Signal Selec  |               |         | 0 0000               |

| EC7h                | RPOR7     | _     | _     | _        |                |                                       | ut Signal Selec  |               |         | 0 0000               |

| EC6h                | RPOR6     | _     | _     | _        |                | · · · · · · · · · · · · · · · · · · · | ut Signal Selec  |               |         | 0 0000               |

| EC5h                | RPOR5     |       |       |          |                |                                       | ut Signal Selec  |               |         | 0 0000               |

Legend:x = unknown, u = unchanged, - = unimplemented, q = value depends on condition, r = reserved, do not modifyNote1:Implemented only for 44-pin devices (PIC18F46J53, PIC18F47J53, PIC18F46J53 and PIC18LF47J53).

2: Implemented only for 28-pin devices (PIC18F26J53, PIC18F27J53, PIC18LF26J53 and PIC18LF27J53).

3: Implemented only for devices with 128 Kbyte of program memory (PIC18F27J53, PIC18F47J53, PIC18LF27J53 and PIC18LF47J53).

# 10.5 PORTD, TRISD and LATD Registers

| Note: | PORTD    | is | available | only | in | 44-pin |

|-------|----------|----|-----------|------|----|--------|

|       | devices. |    |           | -    |    |        |

PORTD is an 8-bit wide, bidirectional port. The corresponding Data Direction register is TRISD. Setting a TRISD bit (= 1) will make the corresponding PORTD pin an input (i.e., put the corresponding output driver in a High-Impedance mode). Clearing a TRISD bit (= 0) will make the corresponding PORTD pin an output (i.e., put the contents of the output latch on the selected pin).

The Data Latch register (LATD) is also memory mapped. Read-modify-write operations on the LATD register read and write the latched output value for PORTD.

All pins on PORTD are implemented with Schmitt Trigger input buffers. Each pin is individually configurable as an input or output.

| Note: | On a POR, these pins are configured as |

|-------|----------------------------------------|

|       | digital inputs.                        |

#### EXAMPLE 10-5: INITIALIZING PORTD

| CLRF  | PORTD | ; Initialize PORTD by   |

|-------|-------|-------------------------|

|       |       | ; clearing output       |

|       |       | ; data latches          |

| CLRF  | LATD  | ; Alternate method      |

|       |       | ; to clear output       |

|       |       | ; data latches          |

| MOVLW | 0CFh  | ; Value used to         |

|       |       | ; initialize data       |

|       |       | ; direction             |

| MOVWF | TRISD | ; Set RD<3:0> as inputs |

|       |       | ; RD<5:4> as outputs    |

|       |       | ; RD<7:6> as inputs     |

|       |       |                         |

Each of the PORTD pins has a weak internal pull-up. A single control bit can turn on all the pull-ups. This is performed by setting bit, RDPU (TRISE<7>). The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on a POR. The integrated weak pull-ups consist of a semiconductor structure similar to, but somewhat different, from, a discrete resistor. On an unloaded I/O pin the weak pull-ups are intended to provide logic high indication, but will not necessarily pull the pin all the way to VDD levels.

Note that the pull-ups can be used for any set of features, similar to the pull-ups found on PORTB.

| R-0                                                                                                                                                                                                                                                                                                                                                   | R/W-0                                                                                                                                                                                                                      | U-0              | U-0 | R-0               | R-0              | R-0             | R-0   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----|-------------------|------------------|-----------------|-------|

| IBF                                                                                                                                                                                                                                                                                                                                                   | IBOV                                                                                                                                                                                                                       | —                | —   | IB3F              | IB2F             | IB1F            | IB0F  |

| bit 7                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                            |                  |     |                   |                  |                 | bit 0 |

|                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                            |                  |     |                   |                  |                 |       |

| Legend:                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                            |                  |     |                   |                  |                 |       |

| R = Readable                                                                                                                                                                                                                                                                                                                                          | bit                                                                                                                                                                                                                        | W = Writable     | bit | U = Unimplem      | nented bit, read | l as '0'        |       |

| -n = Value at I                                                                                                                                                                                                                                                                                                                                       | POR                                                                                                                                                                                                                        | '1' = Bit is set |     | '0' = Bit is clea | ared             | x = Bit is unkn | own   |

| bit 7 <b>IBF:</b> Input Buffer Full Status bit<br>1 = All writable input buffer registers are full<br>0 = Some or all of the writable input buffer registers are empty<br>bit 6 <b>IBOV:</b> Input Buffer Overflow Status bit<br>1 = A write attempt to a full input byte register occurred (must be cleared in software)<br>0 = No overflow occurred |                                                                                                                                                                                                                            |                  |     |                   |                  |                 |       |

| bit 5-4<br>bit 3-0                                                                                                                                                                                                                                                                                                                                    | Unimplemented: Read as '0'<br>IB<3:0>F: Input Buffer x Status Full bits<br>1 = Input buffer contains data that has not been read (reading buffer will clear this bit)<br>0 = Input buffer does not contain any unread data |                  |     |                   |                  |                 |       |

## REGISTER 11-7: PMSTATH: PARALLEL PORT STATUS REGISTER HIGH BYTE (BANKED F55h)<sup>(1)</sup>

Note 1: This register is only available on 44-pin devices.

# REGISTER 11-8: PMSTATL: PARALLEL PORT STATUS REGISTER LOW BYTE (BANKED F54h)<sup>(1)</sup>

| R-1   | R/W-0 | U-0 | U-0 | R-1  | R-1  | R-1  | R-1   |

|-------|-------|-----|-----|------|------|------|-------|

| OBE   | OBUF  | —   | —   | OB3E | OB2E | OB1E | OB0E  |

| bit 7 |       |     |     |      |      |      | bit 0 |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

| bit 7   | <ul> <li>OBE: Output Buffer Empty Status bit</li> <li>1 = All readable output buffer registers are empty</li> <li>0 = Some or all of the readable output buffer registers are full</li> </ul>            |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6   | <ul> <li>OBUF: Output Buffer Underflow Status bit</li> <li>1 = A read occurred from an empty output byte register (must be cleared in software)</li> <li>0 = No underflow occurred</li> </ul>            |

| bit 5-4 | Unimplemented: Read as '0'                                                                                                                                                                               |

| bit 3-0 | <b>OB&lt;3:0&gt;E:</b> Output Buffer x Status Empty bits<br>1 = Output buffer is empty (writing data to the buffer will clear this bit)<br>0 = Output buffer contains data that has not been transmitted |

Note 1: This register is only available on 44-pin devices.

### 18.4.2 PWM DUTY CYCLE

The PWM duty cycle is specified by writing to the CCPR4L register and to the CCP4CON<5:4> bits. Up to 10-bit resolution is available. The CCPR4L contains the eight MSbs and the CCP4CON<5:4> contains the two LSbs. This 10-bit value is represented by CCPR4L:CCP4CON<5:4>. The following equation is used to calculate the PWM duty cycle in time:

#### **EQUATION 18-2:**

PWM Duty Cycle = (CCPR4L:CCP4CON<5:4>) • Tosc • (TMR2 Prescale Value)

CCPR4L and CCP4CON<5:4> can be written to at any time, but the duty cycle value is not latched into CCPR4H until after a match between PR2 and TMR2 occurs (that is, the period is complete). In PWM mode, CCPR4H is a read-only register.

The CCPR4H register and a two-bit internal latch are used to double-buffer the PWM duty cycle. This double-buffering is essential for glitchless PWM operation.

When the CCPR4H and two-bit latch match TMR2, concatenated with an internal two-bit Q clock or two bits of the TMR2 prescaler, the CCP4 pin is cleared.

The maximum PWM resolution (bits) for a given PWM frequency is given by the equation:

#### **EQUATION 18-3:**

PWM Resolution (max) =

$$\frac{\log(\frac{FOSC}{FPWM})}{\log(2)}$$

bits

**Note:** If the PWM duty cycle value is longer than the PWM period, the CCP4 pin will not be cleared.

### TABLE 18-5: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS AT 40 MHz

| PWM Frequency              | 2.44 kHz | 9.77 kHz | 39.06 kHz | 156.25 kHz | 312.50 kHz | 416.67 kHz |

|----------------------------|----------|----------|-----------|------------|------------|------------|

| Timer Prescaler (1, 4, 16) | 16       | 4        | 1         | 1          | 1          | 1          |

| PR2 Value                  | FFh      | FFh      | FFh       | 3Fh        | 1Fh        | 17h        |

| Maximum Resolution (bits)  | 14       | 12       | 10        | 8          | 7          | 6.58       |

### 18.4.3 SETUP FOR PWM OPERATION

To configure the CCP module for PWM operation:

- 1. Set the PWM period by writing to the PR2 register.

- 2. Set the PWM duty cycle by writing to the CCPR4L register and CCP4CON<5:4> bits.

- 3. Make the CCP4 pin an output by clearing the appropriate TRIS bit.

- 4. Set the TMR2 prescale value, then enable Timer2 by writing to T2CON.

- 5. Configure the CCP4 module for PWM operation.

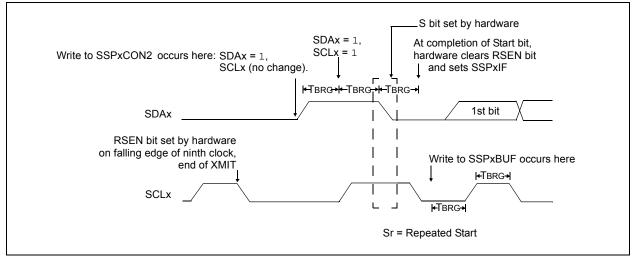

## 20.5.9 I<sup>2</sup>C MASTER MODE REPEATED START CONDITION TIMING

A Repeated Start condition occurs when the RSEN bit (SSPxCON2<1>) is programmed high and the I<sup>2</sup>C logic module is in the Idle state. When the RSEN bit is set, the SCLx pin is asserted low. When the SCLx pin is sampled low, the BRG is loaded with the contents of SSPxADD<5:0> and begins counting. The SDAx pin is released (brought high) for one BRG count (TBRG). When the BRG times out, and if SDAx is sampled high, the SCLx pin will be deasserted (brought high). When SCLx is sampled high, the BRG is reloaded with the contents of SSPxADD<6:0> and begins counting. SDAx and SCLx must be sampled high for one TBRG. This action is then followed by assertion of the SDAx pin (SDAx = 0) for one TBRG while SCLx is high. Following this, the RSEN bit (SSPxCON2<1>) will be automatically cleared and the BRG will not be reloaded, leaving the SDAx pin held low. As soon as a Start condition is detected on the SDAx and SCLx pins, the Start bit (SSPxSTAT<3>) will be set. The SSPxIF bit will not be set until the BRG has timed out.

- Note 1: If RSEN is programmed while any other event is in progress, it will not take effect.

- **2:** A bus collision during the Repeated Start condition occurs if:

- SDAx is sampled low when SCLx goes from low-to-high.

- SCLx goes low before SDAx is asserted low. This may indicate that another master is attempting to transmit a data '1'.

Immediately following the SSPxIF bit getting set, the user may write the SSPxBUF with the 7-bit address in 7-bit mode, or the default first address in 10-bit mode. After the first eight bits are transmitted and an ACK is received, the user may then transmit an additional 8 bits of address (10-bit mode) or 8 bits of data (7-bit mode).

#### 20.5.9.1 WCOL Status Flag

If the user writes the SSPxBUF when a Repeated Start sequence is in progress, the WCOL is set and the contents of the buffer are unchanged (the write does not occur).

### FIGURE 20-22: REPEATED START CONDITION WAVEFORM

**Note:** Because queueing of events is not allowed, writing of the lower five bits of SSPxCON2 is disabled until the Repeated Start condition is complete.

| Name                   | Bit 7                | Bit 6           | Bit 5                     | Bit 4                 | Bit 3                 | Bit 2                       | Bit 1                      | Bit 0  |

|------------------------|----------------------|-----------------|---------------------------|-----------------------|-----------------------|-----------------------------|----------------------------|--------|

| INTCON                 | GIE/GIEH             | PEIE/GIEL       | TMR0IE                    | INT0IE                | RBIE                  | TMR0IF                      | INT0IF                     | RBIF   |

| PIR1                   | PMPIF <sup>(3)</sup> | ADIF            | RC1IF                     | TX1IF                 | SSP1IF                | CCP1IF                      | TMR2IF                     | TMR1IF |

| PIE1                   | PMPIE <sup>(3)</sup> | ADIE            | RC1IE                     | TX1IE                 | SSP1IE                | CCP1IE                      | TMR2IE                     | TMR1IE |

| IPR1                   | PMPIP <sup>(3)</sup> | ADIP            | RC1IP                     | TX1IP                 | SSP1IP                | CCP1IP                      | TMR2IP                     | TMR1IP |

| PIR2                   | OSCFIF               | CM2IF           | CM1IF                     | USBIF                 | BCL1IF                | HLVDIF                      | TMR3IF                     | CCP2IF |

| PIE2                   | OSCFIE               | CM2IE           | CM1IE                     | USBIE                 | BCL1IE                | HLVDIE                      | TMR3IE                     | CCP2IE |

| IPR2                   | OSCFIP               | CM2IP           | CM1IP                     | USBIP                 | BCL1IP                | HLVDIP                      | TMR3IP                     | CCP2IP |

| PIR3                   | SSP2IF               | BCL2IF          | RC2IF                     | TX2IF                 | TMR4IF                | CTMUIF                      | TMR3GIF                    | RTCCIF |

| PIE3                   | SSP2IE               | BCL2IE          | RC2IE                     | TX2IE                 | TMR4IE                | CTMUIE                      | TMR3GIE                    | RTCCIE |

| IPR3                   | SSP2IP               | BCL2IP          | RC2IP                     | TX2IP                 | TMR4IP                | CTMUIP                      | TMR3GIP                    | RTCCIP |

| TRISC                  | TRISC7               | TRISC6          | _                         | _                     | _                     | TRISC2                      | TRISC1                     | TRISC0 |

| TRISB                  | TRISB7               | TRISB6          | TRISB5                    | TRISB4                | TRISB3                | TRISB2                      | TRISB1                     | TRISB0 |

| SSP1BUF                | MSSP1 Rece           | eive Buffer/Tra | nsmit Registe             | r                     |                       |                             |                            |        |

| SSP1ADD                | MSSP1 Addr           | ess Register (I | <sup>2</sup> C Slave mod  | e), MSSP1 Ba          | ud Rate Reloa         | ad Register (I <sup>2</sup> | C Master mod               | e)     |

| SSPxMSK <sup>(1)</sup> | MSK7                 | MSK6            | MSK5                      | MSK4                  | MSK3                  | MSK2                        | MSK1                       | MSK0   |

| SSPxCON1               | WCOL                 | SSPOV           | SSPEN                     | CKP                   | SSPM3                 | SSPM2                       | SSPM1                      | SSPM0  |

| SSPxCON2               | GCEN                 | ACKSTAT         | ACKDT                     | ACKEN                 | RCEN                  | PEN                         | RSEN                       | SEN    |

|                        | GCEN                 | ACKSTAT         | ADMSK5 <sup>(2)</sup>     | ADMSK4 <sup>(2)</sup> | ADMSK3 <sup>(2)</sup> | ADMSK2 <sup>(2)</sup>       | ADMSK1(2)                  | SEN    |

| SSPxSTAT               | SMP                  | CKE             | D/A                       | Р                     | S                     | R/W                         | UA                         | BF     |

| SSP2BUF                | MSSP2 Rece           | eive Buffer/Tra | nsmit Registe             | r                     |                       |                             |                            |        |

| SSP2ADD                | MSSP2 Addr           | ess Register (  | I <sup>2</sup> C Slave mo | de), MSSP2 E          | Baud Rate Rel         | oad Register                | (I <sup>2</sup> C Master m | iode)  |

# TABLE 20-4: REGISTERS ASSOCIATED WITH I<sup>2</sup>C OPERATION

Legend: — = unimplemented, read as '0'. Shaded cells are not used by the MSSPx module in I<sup>2</sup>C mode.

Note 1: SSPxMSK shares the same address in SFR space as SSPxADD, but is only accessible in certain I<sup>2</sup>C Slave mode operations in 7-Bit Masking mode. See Section 20.5.3.4 "7-Bit Address Masking Mode" for more details.

2: Alternate bit definitions for use in I<sup>2</sup>C Slave mode operations only.

**3:** These bits are only available on 44-pin devices.

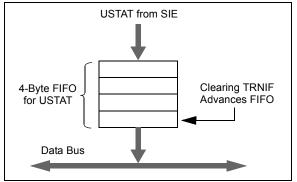

### 23.2.3 USB STATUS REGISTER (USTAT)

The USB Status register reports the transaction status within the SIE. When the SIE issues a USB transfer complete interrupt, USTAT should be read to determine the status of the transfer. USTAT contains the transfer endpoint number, direction and Ping-Pong Buffer Pointer value (if used).

| Note: | The data in the USB Status register is      |

|-------|---------------------------------------------|

|       | valid only when the TRNIF interrupt flag is |

|       | asserted.                                   |

The USTAT register is actually a read window into a 4-byte status FIFO, maintained by the SIE. It allows the microcontroller to process one transfer while the SIE processes additional endpoints (Figure 23-3). When the SIE completes using a buffer for reading or writing data, it updates the USTAT register. If another USB transfer is performed before a transaction complete interrupt is serviced, the SIE will store the status of the next transfer into the status FIFO.

Clearing the transfer complete flag bit, TRNIF, causes the SIE to advance the FIFO. If the next data in the FIFO holding register is valid, the SIE will reassert the interrupt within 5 TCY of clearing TRNIF. If no additional data is present, TRNIF will remain clear; USTAT data will no longer be reliable.

| Note: | If an endpoint request is received while the |            |       |       |      |          |       |  |

|-------|----------------------------------------------|------------|-------|-------|------|----------|-------|--|

|       | USTAT                                        | FIFO       | is    | full, | the  | SIE      | will  |  |

|       | automat                                      | ically iss | sue a | a NAK | back | to the I | nost. |  |

#### FIGURE 23-3: USTAT FIFO

### REGISTER 23-3: USTAT: USB STATUS REGISTER (ACCESS F64h)

|              |                     |                                                                                                                   |                  | •                | -               |                     |     |  |  |  |

|--------------|---------------------|-------------------------------------------------------------------------------------------------------------------|------------------|------------------|-----------------|---------------------|-----|--|--|--|

| U-0          | R-x                 | R-x                                                                                                               | R-x              | R-x              | R-x             | R-x                 | U-0 |  |  |  |

| —            | ENDP3               | ENDP2                                                                                                             | ENDP1            | ENDP0            | DIR             | PPBI <sup>(1)</sup> |     |  |  |  |

| oit 7        |                     |                                                                                                                   |                  |                  |                 | i                   | bit |  |  |  |

|              |                     |                                                                                                                   |                  |                  |                 |                     |     |  |  |  |

| Legend:      |                     |                                                                                                                   |                  |                  |                 |                     |     |  |  |  |

| R = Readab   | le bit              | W = Writable                                                                                                      | bit              | U = Unimpler     | nented bit, rea | d as '0'            |     |  |  |  |

| -n = Value a | t POR               | '1' = Bit is set                                                                                                  | t                | '0' = Bit is cle | ared            | x = Bit is unkno    | own |  |  |  |

|              |                     |                                                                                                                   |                  |                  |                 |                     |     |  |  |  |

| bit 7        | Unimplemer          | nted: Read as '                                                                                                   | 0'               |                  |                 |                     |     |  |  |  |

| bit 6-3      | ENDP<3:0>:          | Encoded Num                                                                                                       | ber of Last Er   | dpoint Activity  | bits            |                     |     |  |  |  |

|              | (represents t       | (represents the number of the BDT updated by the last USB transfer)                                               |                  |                  |                 |                     |     |  |  |  |

|              | 1111 = End          | 1111 = Endpoint 15                                                                                                |                  |                  |                 |                     |     |  |  |  |

|              | 1110 = End          | 1110 = Endpoint 14                                                                                                |                  |                  |                 |                     |     |  |  |  |

|              | •                   |                                                                                                                   |                  |                  |                 |                     |     |  |  |  |

|              | •                   |                                                                                                                   |                  |                  |                 |                     |     |  |  |  |

|              | 0001 = End          | noint 1                                                                                                           |                  |                  |                 |                     |     |  |  |  |

|              | 0000 = End          | •                                                                                                                 |                  |                  |                 |                     |     |  |  |  |

| bit 2        |                     | Direction India                                                                                                   | ator bit         |                  |                 |                     |     |  |  |  |

|              |                     |                                                                                                                   |                  |                  |                 |                     |     |  |  |  |

|              |                     | <ol> <li>The last transaction was an IN token</li> <li>The last transaction was an OUT or SETUP token</li> </ol>  |                  |                  |                 |                     |     |  |  |  |

| L:1 1        |                     |                                                                                                                   |                  |                  |                 |                     |     |  |  |  |

| bit 1        | •                   | <b>PPBI:</b> Ping-Pong BD Pointer Indicator bit <sup>(1)</sup><br>1 = The last transaction was to the Odd BD bank |                  |                  |                 |                     |     |  |  |  |

|              |                     | transaction was                                                                                                   |                  |                  |                 |                     |     |  |  |  |

| L:1 0        |                     |                                                                                                                   |                  |                  |                 |                     |     |  |  |  |