Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                     |

| Core Processor             | ARM® Cortex®-M0+                                                             |

| Core Size                  | 32-Bit Single-Core                                                           |

| Speed                      | 40MHz                                                                        |

| Connectivity               | CSIO, I <sup>2</sup> C, LINbus, SmartCard, UART/USART, USB                   |

| Peripherals                | I <sup>2</sup> S, LCD, LVD, POR, PWM, WDT                                    |

| Number of I/O              | 65                                                                           |

| Program Memory Size        | 304KB (304K x 8)                                                             |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 32K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 3.6V                                                                 |

| Data Converters            | A/D 16x12b                                                                   |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                           |

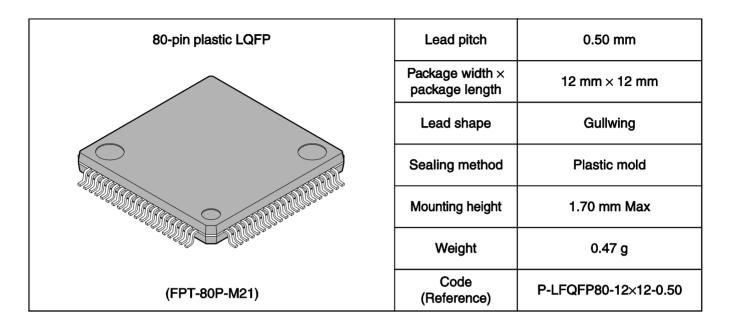

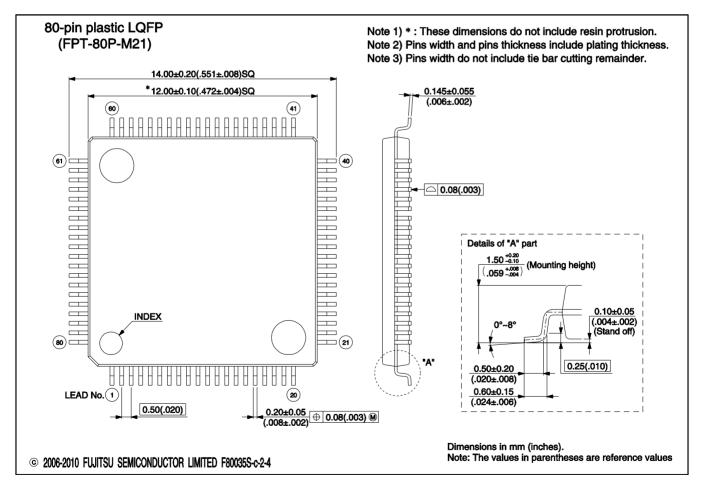

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 80-LQFP                                                                      |

| Supplier Device Package    | 80-LQFP (12x12)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/s6e1b84e0agf20000 |

#### **Watch Counter**

The Watch Counter wakes up the microcontroller from the low power consumption mode. The clock source can be selected from the main clock, the sub clock, the built-in high-speed CR clock or the built-in low-speed CR clock.

Interval timer: up to 64 s (sub clock: 32.768 kHz)

## **External Interrupt Controller Unit**

- ■Up to 24 external interrupt input pins

- ■Non-maskable interrupt (NMI) input pin: 1

#### Watchdog Timer (2 Channels)

The watchdog timer generates an interrupt or a reset when the counter reaches a time-out value.

This series consists of two different watchdogs, hardware watchdog and software watchdog.

The hardware watchdog timer is clocked by the built-in low-speed CR oscillator. Therefore, the hardware watchdog is active in any low-power consumption modes except RTC, Stop, Deep standby RTC and Deep standby Stop mode.

## **CRC (Cyclic Redundancy Check) Accelerator**

The CRC accelerator calculates the CRC which has a heavy software processing load, and achieves a reduction of the integrity check processing load for reception data and storage.

■CCITT CRC16 and IEEE-802.3 CRC32 are supported.

□ CCITT CRC16 Generator Polynomial: 0x1021

□ IEEE-802.3 CRC32 Generator Polynomial: 0x04C11DB7

# HDMI-CEC/Remote Control Receiver (Up to 2 Channels)

- ■HDMI-CEC transmitter

- □ Header block automatic transmission by judging Signal free

- □ Generating status interrupt by detecting Arbitration lost

- □ Generating START, EOM, ACK automatically to output CEC transmission by setting 1 byte data

- ☐ Generating transmission status interrupt when transmitting 1 block (1 byte data and EOM/ACK)

- ■HDMI-CEC receiver

- □ Automatic ACK reply function available

- ☐ Line error detection function available

- ■Remote control receiver

- ☐ 4 bytes reception buffer

- □ Repeat code detection function available

#### Smart Card Interface (Max 2 Channels)

- ■Compliant with ISO7816-3 specification

- ■Card Reader only/B class card only

- ■Available protocols

- ☐ Transmitter: 8E2, 8O2, 8N2

- ☐ Receiver: 8E1, 8O1, 8N2, 8N1, 9N1

- □ Inverse mode

- ■TX/RX FIFO integrated (RX: 16-bytes, TX:16-bytes)

#### **AES Calculator**

- AES (Advanced Encryption Standard) calculator is an AES common key crypto accelerator that is compliant with FIPS (Federal Information Processing Standard Publication) 197.

- Available key length: 128/192/256-bit

- ■CBC mode and ECB mode support

#### **Clock and Reset**

#### ■Clocks

A clock can be selected from five clock sources (two external oscillators, two built-in CR oscillator, and main PLL).

- ☐ Main clock: 4 MHz to 40 MHz

- □ Sub clock: 32.768 kHz

- □ Built-in high-speed CR clock: 4 MHz

- □ Built-in low-speed CR clock: 100 kHz

- □ Main PLL clock

- ■Resets

- ☐ Reset request from the INITX pin

- □ Power on reset

- □ Software reset

- □ Watchdog timer reset

- □ Low-voltage detection reset

- □ Clock supervisor reset

#### **Clock Supervisor (CSV)**

The Clock Supervisor monitors the failure of external clocks with a clock generated by a built-in CR oscillator.

- If an external clock failure (clock stop) is detected, a reset is asserted.

- If an external frequency anomaly is detected, an interrupt or a reset is asserted.

#### **Low-Voltage Detector (LVD)**

This series monitors the voltage on the VCC pin with a 2-stage mechanism. When the voltage falls below a designated voltage, the Low-voltage Detector generates an interrupt or a reset.

- ■LVDR: monitor Vcc and auto-reset operation

- ■LVD1: monitor Vcc and error reporting via an interrupt

- LVD2: selectable to monitor Vcc or LVDI and error reporting via an interrupt

#### **Low Power Consumption Mode**

This series has six low power consumption modes.

- ■Sleep

- ■Timer

- ■RTC

- ■Stop

- ■Deep standby RTC (selectable between keeping the value of RAM and not)

- ■Deep standby Stop (selectable between keeping the value of RAM and not)

# 4. List of Pin Functions

## **List of Pin Numbers**

The number after the underscore ("\_") in a pin name such as XXX\_1 and XXX\_2 indicates the relocated port number. The channel on such pin has multiple functions, each of which has its own pin name. Use the Extended Port Function Register (EPFR) to select the pin to be used.

|          | Pin No.  |                    | Din Nome      | I/O Cinquit Tuno | Pin State Type |  |

|----------|----------|--------------------|---------------|------------------|----------------|--|

| LQFP-120 | LQFP-100 | LQFP-80            | Pin Name      | I/O Circuit Type | Pin State Type |  |

| 1        | 1        | 1                  | VCC           | -                |                |  |

|          |          |                    | P50           |                  |                |  |

|          |          |                    | SIN3_1        |                  |                |  |

| 2        | 2        | 2                  | INT00_0       | Q                | X              |  |

|          |          |                    | VV4           |                  |                |  |

|          |          |                    | P51           |                  |                |  |

| 3        | 3        | 3                  | SOT3_1        | Q                | X              |  |

| 3        | 3        | 3                  | INT01_0       |                  | ^              |  |

|          |          |                    | VV3           |                  |                |  |

|          |          |                    | P52           |                  |                |  |

| 4        | 4        | 4                  | SCK3_1        |                  | V              |  |

| 4        | 4        | 4                  | INT02_0       | Q                | X              |  |

|          |          |                    | VV2           |                  |                |  |

|          |          |                    | P53           |                  |                |  |

|          | 5 5      |                    | SIN6_0        |                  |                |  |

| 5        |          | 5 5                | TIOA1_2       | Q                | X              |  |

| -        |          |                    | INT07_2       |                  |                |  |

|          |          |                    | VV1           |                  |                |  |

|          |          |                    |               | P54              |                |  |

|          |          |                    | SOT6_0        | Q                | X              |  |

| 6        | 6        | 6                  | TIOB1_2       |                  |                |  |

|          |          |                    | INT18_1       |                  |                |  |

|          |          |                    | VV0           |                  |                |  |

|          |          |                    | P55           |                  |                |  |

|          |          |                    | SCK6_0        |                  |                |  |

| 7        | 7        | 7                  | ADTG_1        | L                | S              |  |

|          |          |                    | INT19_1       |                  |                |  |

|          |          |                    | SEG39         |                  |                |  |

|          |          |                    | P56           |                  |                |  |

|          |          |                    | MI2SMCK6_1    |                  |                |  |

|          | 8        | 8                  | CEC1_1        |                  |                |  |

| 8        | Ö        | Ü                  | INT08_2       | L                | U              |  |

|          |          |                    | WKUP9         |                  |                |  |

|          |          |                    | SEG38         |                  |                |  |

|          | -        | -                  | SIN1_0        |                  |                |  |

| 9        | -        | -                  | P57           | F                | 1              |  |

|          |          |                    | SOT1_0        |                  | <u> </u>       |  |

| 10       | -        | -                  | P58           | F F              | 1              |  |

|          |          |                    | SCK1_0<br>P59 |                  |                |  |

| 11       | -        | -                  | SIN7_0        | 7_0 F            |                |  |

| 11       | •        | -   - <del> </del> | INT16_1       | ╡ '              | J              |  |

| Pin Function               | Pin Name           | Function Description                                                               |          | Pin No.  |         |

|----------------------------|--------------------|------------------------------------------------------------------------------------|----------|----------|---------|

| Fill Fullction             | Fill Name          | Function Description                                                               | LQFP-120 | LQFP-100 | LQFP-80 |

|                            | SIN3_0             |                                                                                    | 110      | -        | -       |

|                            | SIN3_1             | Multi-function serial interface ch.3 input pin                                     | 2        | 2        | 2       |

|                            | SIN3_2             |                                                                                    | 94       | 79       | 63      |

|                            | SOT3_0<br>(SDA3_0) | Multi-function serial interface ch.3 output pin.                                   | 109      | -        | -       |

| Multi-function             | SOT3_1<br>(SDA3_1) | This pin operates as SOT3 when used as a UART/CSIO/LIN pin (operation mode 0 to 3) | 3        | 3        | 3       |

| Serial 3                   | SOT3_2<br>(SDA3_2) | and as SDA3 when used as an I <sup>2</sup> C pin (operation mode 4).               | 92       | 77       | 61      |

|                            | SCK3_0<br>(SCL3_0) | Multi-function serial interface ch.3 clock I/O pin.                                | 108      | -        | -       |

|                            | SCK3_1<br>(SCL3_1) | This pin operates as SCK3 when used as a CSIO (operation mode 2) and as SCL3       | 4        | 4        | 4       |

|                            | SCK3_2<br>(SCL3_2) | when used as an I <sup>2</sup> C pin (operation mode 4).                           | 96       | 81       | 65      |

|                            | SIN4_0             |                                                                                    | 102      | 87       | 67      |

|                            | SIN4_1             | Multi-function serial interface ch.4 input pin                                     | 76       | 66       | 56      |

|                            | SIN4_2             | 7                                                                                  | 97       | 82       | -       |

|                            | SOT4_0<br>(SDA4_0) | Multi-function serial interface ch.4 output pin.                                   | 99       | 84       | 66      |

|                            | SOT4_1<br>(SDA4_1) | This pin operates as SOT4 when used as a UART/CSIO/LIN pin (operation mode 0 to 3) | 77       | 67       | 57      |

|                            | SOT4_2<br>(SDA4_2) | and as SDA4 when used as an I <sup>2</sup> C pin (operation mode 4).               | 98       | 83       | -       |

| Multi-function<br>Serial 4 | SCK4_0<br>(SCL4_0) | Multi-function serial interface ch.4 clock I/O pin.                                | 107      | 92       | 72      |

| Ochai 4                    | SCK4_1<br>(SCL4_1) | This pin operates as SCK4 when used as a CSIO (operation mode 2) and as SCL4       | 78       | 68       | -       |

|                            | SCK4_2<br>(SCL4_2) | when used as an I <sup>2</sup> C pin (operation mode 4).                           | 99       | 84       | 66      |

|                            | CTS4_0             | Multi function period interface ob 4 CTC input                                     | 106      | 91       | 71      |

|                            | CTS4_1             | Multi-function serial interface ch4 CTS input                                      | 79       | 69       | -       |

|                            | CTS4_2             | Ρ"1                                                                                | 100      | 85       | -       |

|                            | RTS4_0             | Multi-function serial interface ch4 RTS input                                      | 105      | 90       | 70      |

| <u> </u>                   | RTS4_1             | pin                                                                                | 80       | 70       | -       |

|                            | RTS4_2             | F                                                                                  | 101      | 86       | -       |

| Pin Function   | Pin Name             | Function Description                                            | LQFP-120 | Pin No.<br>LQFP-100 | LQFP-80 |

|----------------|----------------------|-----------------------------------------------------------------|----------|---------------------|---------|

|                | DTTI0X_0             | Input signal of waveform generator                              | 23       | 18                  | 13      |

|                | DTTI0X_1             | controlling RTO00 to RTO05 outputs of                           | 79       | 69                  | -       |

|                | DTTI0X_2             | Multi-function Timer 0.                                         | 115      | 95                  | 75      |

|                | FRCK0_0              |                                                                 | 18       | 13                  | -       |

|                | FRCK0_1              | 16-bit free-run timer ch.0 external clock input pin.            | 80       | 70                  | -       |

|                | FRCK0_2              |                                                                 | 63       | 53                  | 43      |

| _              | IC00_0               |                                                                 | 22       | 17                  | -       |

|                | IC00_1               |                                                                 | 75       | 65                  | 55      |

|                | IC00_2               |                                                                 | 64       | 54                  | 44      |

|                | IC01_0               |                                                                 | 21       | 16                  | -       |

|                | IC01_1               |                                                                 | 76       | 66                  | 56      |

|                | IC01_2               | 16-bit input capture input pin of Multi-function                | 65       | 55                  | 45      |

|                | IC02_0               | timer 0.                                                        | 20       | 15                  | -       |

|                | IC02_1               | ICxx describes channel number.                                  | 77       | 67                  | 57      |

|                | IC02_2               | <del>-</del>                                                    | 66       | 56                  | 46      |

|                | IC03_0               | 7                                                               | 19       | 14                  | -       |

|                | IC03_1               |                                                                 | 78       | 68                  | -       |

|                | IC03_2               | 7                                                               | 67       | 57                  | 47      |

| Multi-function | RTO00_0<br>(PPG00_0) | Waveform generator output pin of Multi-function timer 0.        | 24       | 19                  | 14      |

| Timer 0        | RTO00_1<br>(PPG00_1) | This pin operates as PPG00 when it is used in PPG0 output mode. | 86       | 71                  | 58      |

|                | RTO01_0<br>(PPG00_0) | Waveform generator output pin of Multi-function timer 0.        | 25       | 20                  | 15      |

|                | RTO01_1<br>(PPG00_1) | This pin operates as PPG00 when it is used in PPG0 output mode. | 85       | -                   | -       |

|                | RTO02_0<br>(PPG02_0) | Waveform generator output pin of Multi-function timer 0.        | 26       | 21                  | 16      |

|                | RTO02_1<br>(PPG02_1) | This pin operates as PPG02 when it is used in PPG0 output mode. | 84       | -                   | -       |

|                | RTO03_0<br>(PPG02_0) | Waveform generator output pin of Multi-function timer 0.        | 27       | 22                  | 17      |

|                | RTO03_1<br>(PPG02_1) | This pin operates as PPG02 when it is used in PPG0 output mode. | 83       | -                   | -       |

|                | RTO04_0<br>(PPG04_0) | Waveform generator output pin of Multi-function timer 0.        | 28       | 23                  | 18      |

|                | RTO04_1<br>(PPG04_1) | This pin operates as PPG04 when it is used in PPG0 output mode. | 82       | -                   | -       |

|                | RTO05_0<br>(PPG04_0) | Waveform generator output pin of Multi-function timer 0.        | 29       | 24                  | 19      |

|                | RTO05_1<br>(PPG04_1) | This pin operates as PPG04 when it is used in PPG0 output mode. | 81       | -                   | -       |

|                | IGTRG0_0             | PPG IGBT mode external trigger input pin                        | 48       | 43                  | 33      |

|                | IGTRG0_1             |                                                                 | 116      | 96                  | 76      |

| Pin Function  | Pin Name | Function Description                                                                                                            | LQFP-120 | Pin No.<br>LQFP-100 | LQFP-80 |

|---------------|----------|---------------------------------------------------------------------------------------------------------------------------------|----------|---------------------|---------|

|               | LVDI     | Input pin to monitor the external voltage.                                                                                      | 37       | 32                  | 22      |

| VBAT          | VWAKEUP  | The return signal input pin from a hibernation state                                                                            | 45       | 40                  | 30      |

|               | REGCTL   | On-board regulator control pin                                                                                                  | 44       | 39                  | 29      |

| Reset         | INITX    | External Reset Input pin. A reset is valid when INITX="L".                                                                      | 41       | 36                  | 26      |

|               | MD0      | Mode 0 pin. During normal operation, input MD0="L". During serial programming to Flash memory, input MD0="H".                   | 57       | 47                  | 37      |

| Mode          | MD1      | Mode 1 pin.  During normal operation, input is not needed.  During serial programming to Flash memory, MD1 = "L" must be input. | 56       | 46                  | 36      |

|               |          |                                                                                                                                 | 1        | 1                   | 1       |

|               |          |                                                                                                                                 | 31       | 26                  | -       |

| Power         | VCC      | Power supply pin                                                                                                                | 40       | 35                  | 25      |

|               |          |                                                                                                                                 | 61       | 51                  | 41      |

|               |          |                                                                                                                                 | 91       | 76                  | -       |

| VBAT power    | VBAT     | VBAT power supply pin Backup power supply (battery etc.) and system power supply                                                | 46       | 41                  | 31      |

|               |          |                                                                                                                                 | 30       | 25                  | 20      |

|               |          |                                                                                                                                 | 39       | 34                  | 24      |

| GND           | VSS      | GND pin                                                                                                                         | 60       | 50                  | 40      |

|               |          |                                                                                                                                 | 90       | 75                  | -       |

|               |          |                                                                                                                                 | 120      | 100                 | 80      |

|               | X0       | Main clock (oscillation) input pin                                                                                              | 58       | 48                  | 38      |

|               | X0A      | Sub clock (oscillation) input pin                                                                                               | 42       | 37                  | 27      |

|               | X1       | Main clock (oscillation) I/O pin                                                                                                | 59       | 49                  | 39      |

| Clock         | X1A      | Sub clock (oscillation) I/O pin                                                                                                 | 43       | 38                  | 28      |

|               | CROUT_0  | Built-in high-speed CR oscillation clock output port                                                                            | 89       | 74                  | -       |

|               | CROUT_1  | Built-in high-speed CR oscillation clock output port                                                                            | 107      | 92                  | 72      |

| Analog        | AVCC     | A/D converter analog power supply pin                                                                                           | 70       | 60                  | 50      |

| Power         | AVRH     | A/D converter analog reference voltage input pin                                                                                | 73       | 63                  | 53      |

| Analog<br>GND | AVSS     | A/D converter analog reference voltage input pin                                                                                | 71       | 61                  | 51      |

| C pin         | С        | Power supply stabilization capacitance pin                                                                                      | 38       | 33                  | 23      |

<sup>\*:</sup> PE0 is an open drain pin, cannot output high.

# 6. Handling Precautions

Any semiconductor devices have inherently a certain rate of failure. The possibility of failure is greatly affected by the conditions in which they are used (circuit conditions, environmental conditions, etc.). This page describes precautions that must be observed to minimize the chance of failure and to obtain higher reliability from your Spansion semiconductor devices.

#### 6.1 Precautions for Product Design

This section describes precautions when designing electronic equipment using semiconductor devices.

#### **Absolute Maximum Ratings**

Semiconductor devices can be permanently damaged by application of stress (voltage, current, temperature, etc.) in excess of certain established limits, called absolute maximum ratings. Do not exceed these ratings.

#### **Recommended Operating Conditions**

Recommended operating conditions are normal operating ranges for the semiconductor device. All the device's electrical characteristics are warranted when operated within these ranges.

Always use semiconductor devices within the recommended operating conditions. Operation outside these ranges may adversely affect reliability and could result in device failure.

No warranty is made with respect to uses, operating conditions, or combinations not represented on the data sheet. Users considering application outside the listed conditions are advised to contact their sales representative beforehand.

### **Processing and Protection of Pins**

These precautions must be followed when handling the pins which connect semiconductor devices to power supply and input/output functions.

- (1) Preventing Over-Voltage and Over-Current Conditions

- Exposure to voltage or current levels in excess of maximum ratings at any pin is likely to cause deterioration within the device, and in extreme cases leads to permanent damage of the device. Try to prevent such overvoltage or over-current conditions at the design stage.

- (2) Protection of Output Pins

- Shorting of output pins to supply pins or other output pins, or connection to large capacitance can cause large current flows. Such conditions if present for extended periods of time can damage the device.

- Therefore, avoid this type of connection.

- (3) Handling of Unused Input Pins

- Unconnected input pins with very high impedance levels can adversely affect stability of operation. Such pins should be connected through an appropriate resistance to a power supply pin or ground pin.

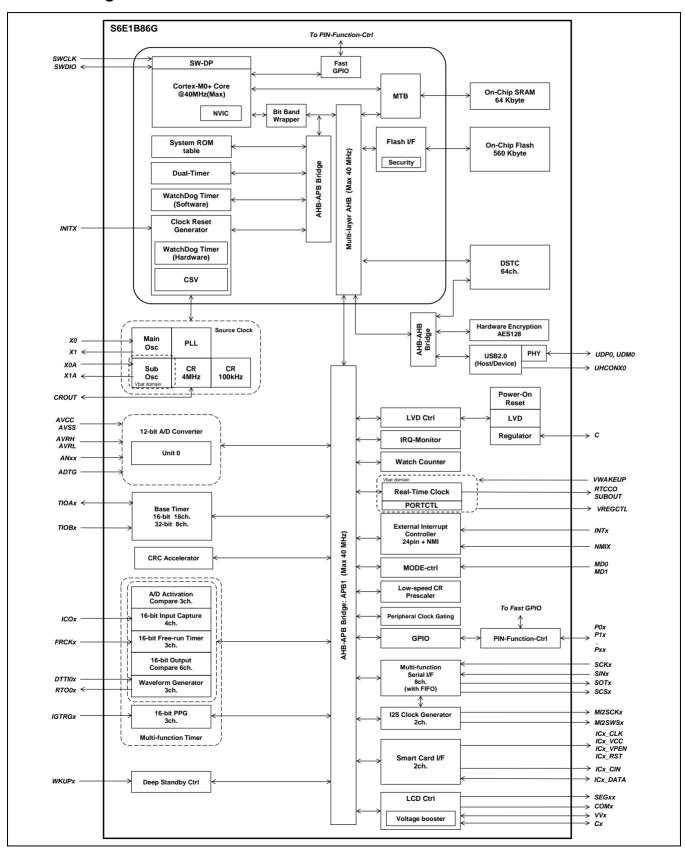

# 8. Block Diagram

| Pin Status Type | Function<br>Group                                                                     | State Upon<br>Power-on<br>Reset or<br>Low-Voltag<br>e Detection | State at<br>INITX<br>Input                                                | State<br>Upon<br>Device<br>Internal<br>Reset                              | State in<br>Run Mode<br>or Sleep<br>Mode                                  | State in Timer Mode,<br>RTC Mode, or<br>Stop Mode                         |                                                                           | RTC Mode, or Standby Stan Mode                                                |                                                                           |                                                                               |      |

|-----------------|---------------------------------------------------------------------------------------|-----------------------------------------------------------------|---------------------------------------------------------------------------|---------------------------------------------------------------------------|---------------------------------------------------------------------------|---------------------------------------------------------------------------|---------------------------------------------------------------------------|-------------------------------------------------------------------------------|---------------------------------------------------------------------------|-------------------------------------------------------------------------------|------|

| Pin             |                                                                                       | Power<br>Supply<br>Unstable                                     | Power<br>Supply<br>Stable                                                 | Power<br>Supply<br>Stable                                                 | Power<br>Supply<br>Stable                                                 | Power Sup                                                                 |                                                                           | Power Sup                                                                     | Power<br>Supply<br>Stable                                                 |                                                                               |      |

|                 |                                                                                       | -                                                               | INITX=0                                                                   | INITX=1                                                                   | INITX=1                                                                   | INIT<br>SPL=0                                                             | X=1<br>SPL=1                                                              | INIT<br>SPL=0                                                                 | X=1<br>SPL=1                                                              | INITX=1                                                                       |      |

|                 |                                                                                       |                                                                 |                                                                           |                                                                           |                                                                           | 0. 1-0                                                                    | Maintain                                                                  | Maintain                                                                      | Maintain                                                                  | Maintain                                                                      |      |

|                 | CEC<br>enabled                                                                        |                                                                 |                                                                           |                                                                           |                                                                           |                                                                           | previous                                                                  | previous                                                                      | previous                                                                  | previous                                                                      |      |

|                 | Chabled                                                                               |                                                                 |                                                                           |                                                                           |                                                                           |                                                                           | state                                                                     | state                                                                         | state                                                                     | state                                                                         |      |

|                 | WKUP<br>enabled                                                                       | Setting<br>disabled                                             | Setting<br>disabled                                                       | Setting<br>disabled                                                       | Maintain previous state                                                   | d                                                                         |                                                                           | Hi-Z /<br>Internal<br>input fixed<br>at 0                                     | WKUP<br>input<br>enabled                                                  | Hi-Z /<br>WKUP<br>input<br>enabled                                            | GPIO |

|                 | External interrupt enabled selected                                                   |                                                                 |                                                                           |                                                                           |                                                                           |                                                                           | Maintain                                                                  | Maintain                                                                      | Maintain previous state                                                   | GPIO selected /                                                               |      |

| U               | Resourc<br>e other<br>than<br>above<br>selected                                       |                                                                 | Hi-Z /                                                                    | Hi-Z /                                                                    |                                                                           | previous<br>state                                                         | Hi-Z /                                                                    | Internal<br>input fixed<br>at 0                                               | Hi-Z /<br>Internal                                                        | at 0                                                                          |      |

|                 | GPIO<br>selected                                                                      | Hi-Z                                                            | Internal                                                                  | Internal<br>input fixed<br>at 0                                           |                                                                           |                                                                           | Internal input fixed at 0                                                 | Output<br>maintains<br>previous<br>state /<br>Internal<br>input fixed<br>at 0 | input fixed<br>at 0                                                       | Output<br>maintains<br>previous<br>state /<br>Internal<br>input fixed<br>at 0 |      |

|                 | Analog<br>input<br>selected                                                           | Hi-Z                                                            | Hi-Z /<br>Internal<br>input fixed<br>at 0 /<br>Analog<br>input<br>enabled     | Hi-Z /<br>Internal<br>input fixed<br>at 0 /<br>Analog<br>input<br>enabled | Hi-Z / Internal input fixed at 0 / Analog input enabled                       |      |

| V               | External interrupt enabled selected Resourc e other than above selected GPIO selected | Setting<br>disabled                                             | Setting<br>disabled                                                       | Setting<br>disabled                                                       | Maintain<br>previous<br>state                                             | Maintain<br>previous<br>state                                             | Maintain previous state  Hi-Z / Internal input fixed at 0                 | GPIO<br>selected /<br>Internal<br>input fixed<br>at 0                         | Hi-Z /<br>Internal<br>input fixed<br>at 0                                 | GPIO<br>selected /<br>Internal<br>input fixed<br>at 0                         |      |

| Parameter         | Symbol<br>(Pin Name)      | Co             | onditions                                                                        |      | alue<br>Max | Unit | Remarks |

|-------------------|---------------------------|----------------|----------------------------------------------------------------------------------|------|-------------|------|---------|

|                   | (Pin Name)                |                |                                                                                  | Тур  | IVIAX       |      |         |

|                   |                           |                | T <sub>A</sub> =25°C<br>V <sub>CC</sub> =3.3 V                                   | 10   | TBD         | μA   | *1      |

|                   | I <sub>CCH</sub> (VCC)    | Stop mode      | T <sub>A</sub> =25°C<br>V <sub>CC</sub> =1.65 V                                  | 9    | TBD         | μA   | *1      |

|                   |                           |                | T <sub>A</sub> =105°C<br>V <sub>CC</sub> =3.6 V                                  | -    | TBD         | μA   | *1      |

| Power             |                           | Sub timer mode | T <sub>A</sub> =25°C<br>V <sub>CC</sub> =3.3 V<br>32 kHz Crystal<br>oscillation  | 13   | TBD         | μA   | *1      |

|                   | I <sub>CCT</sub> (VCC)    |                | T <sub>A</sub> =25°C<br>V <sub>CC</sub> =1.65 V<br>32 kHz Crystal<br>oscillation | 12   | TBD         | μA   | *1      |

| supply<br>current |                           |                | $T_A$ =105°C<br>$V_{CC}$ =3.6 V<br>32 kHz Crystal<br>oscillation                 |      | TBD         | μA   | *1      |

|                   |                           | RTC mode       | T <sub>A</sub> =25°C<br>V <sub>CC</sub> =3.3 V<br>32 kHz Crystal<br>oscillation  | 10.5 | TBD         | μA   | *1      |

|                   | I <sub>CCR</sub><br>(VCC) |                | T <sub>A</sub> =25°C<br>V <sub>CC</sub> =1.65 V<br>32 kHz Crystal<br>oscillation | 9.5  | TBD         | μA   | *1      |

|                   |                           |                | T <sub>A</sub> =105°C<br>V <sub>CC</sub> =3.6 V<br>32 kHz Crystal<br>oscillation | -    | TBD         | μA   | *1      |

<sup>\*1:</sup> All ports are fixed. LVD off. Flash off.

## 11.4 AC Characteristics

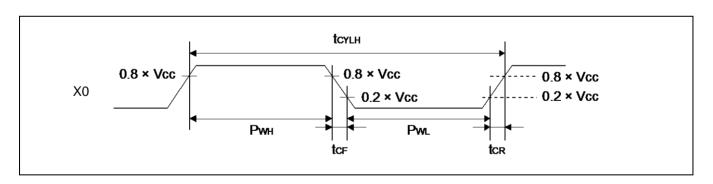

## 11.4.1 Main Clock Input Characteristics

$(V_{CC}=AV_{CC}=1.65 \text{ V to } 3.6 \text{ V}, V_{SS}=AV_{SS}=0 \text{ V}, T_{A}=-40 ^{\circ}\text{C to } +105 ^{\circ}\text{C})$

| Darameter                                | Cumbal                              | Pin Name  | Conditions              | Va    | lue  | Unit   | Remarks                         |

|------------------------------------------|-------------------------------------|-----------|-------------------------|-------|------|--------|---------------------------------|

| Parameter                                | Symbol                              | Pin Name  | Conditions              | Min   | Max  | Unit   | Remarks                         |

|                                          |                                     |           | V <sub>CC</sub> ≥ 2.7 V | 4     | 48   | MHz    | When the crystal oscillator     |

| Input frequency                          | <b>f</b>                            |           | V <sub>CC</sub> < 2.7 V | 4     | 20   | IVITIZ | is connected                    |

| Input frequency                          | f <sub>CH</sub>                     |           | -                       | 4     | 48   | MHz    | When the external clock is used |

| Input clock cycle                        | t <sub>CYLH</sub>                   | X0,<br>X1 | -                       | 20.83 | 250  | ns     | When the external clock is used |

| Input clock pulse width                  | ck pulse width -                    |           | Pwh/tcylh,<br>Pwl/tcylh | 45    | 55   | %      | When the external clock is used |

| Input clock rising time and falling time | t <sub>CF,</sub><br>t <sub>CR</sub> |           | -                       | -     | 5    | ns     | When the external clock is used |

|                                          | $f_{CM}$                            | -         | -                       | -     | 40.8 | MHz    | Master clock                    |

| Internal operating                       | f <sub>CC</sub>                     | -         | -                       | -     | 40.8 | MHz    | Base clock (HCLK/FCLK)          |

| clock <sup>*1</sup> frequency            | f <sub>CP0</sub>                    | -         | -                       | -     | 40.8 | MHz    | APB0 bus clock*2                |

|                                          | f <sub>CP1</sub>                    | -         | -                       | -     | 40.8 | MHz    | APB1 bus clock*2                |

| Internal operating                       | t <sub>CYCC</sub>                   | -         | -                       | 24.5  | -    | ns     | Base clock (HCLK/FCLK)          |

| Internal operating clock 1 cycle time    | t <sub>CYCP0</sub>                  | -         | -                       | 24.5  | -    | ns     | APB0 bus clock*2                |

| ologic of clothing                       | t <sub>CYCP1</sub>                  | -         | -                       | 24.5  | -    | ns     | APB1 bus clock*2                |

<sup>\*1:</sup> For details of each internal operating clock, refer to "Chapter: Clock" in "FM0+ Family Peripheral Manual".

<sup>\*2:</sup> For details of the APB bus to which a peripheral is connected, see "8. Block Diagram".

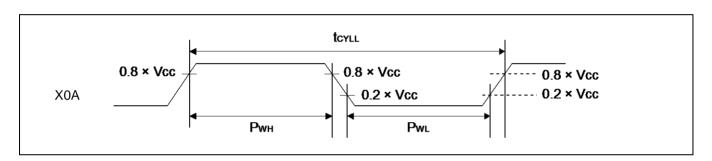

## 11.4.2 Sub Clock Input Characteristics

$(V_{CC}=AV_{CC}=1.65 \text{ V to } 3.6 \text{ V}, V_{SS}=AV_{SS}=0 \text{ V}, T_{A}=-40 ^{\circ}\text{C to } +105 ^{\circ}\text{C})$

| Parameter               | Symbol            | Pin Name    | Conditions              |     | Value  |       | Unit  | Remarks                                   |  |

|-------------------------|-------------------|-------------|-------------------------|-----|--------|-------|-------|-------------------------------------------|--|

| Parameter               | Symbol            | riii Naiile | Conditions              | Min | Тур    | Max   | Offic | Remarks                                   |  |

| Input frequency         | f <sub>CL</sub>   |             | -                       | -   | 32.768 | -     | kHz   | When the crystal oscillator is connected* |  |

|                         |                   | X0A,<br>X1A | -                       | 32  | -      | 100   | kHz   | When the external clock is used           |  |

| Input clock cycle       | t <sub>CYLL</sub> | \ \IA       | -                       | 10  | -      | 31.25 | μs    | When the external clock is used           |  |

| Input clock pulse width | -                 |             | Pwh/tcyll,<br>Pwl/tcyll | 45  | -      | 55    | %     | When the external clock is used           |  |

<sup>\*:</sup> See "Sub crystal oscillator" in "7. Handling Devices" for the crystal oscillator used.

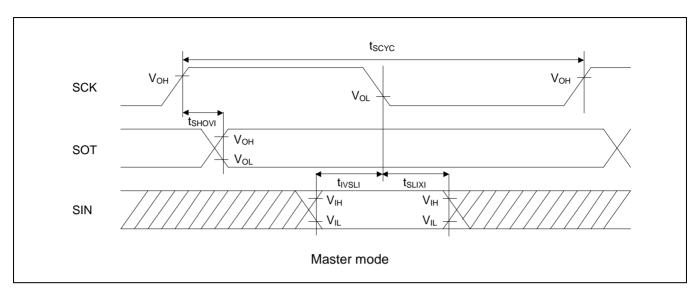

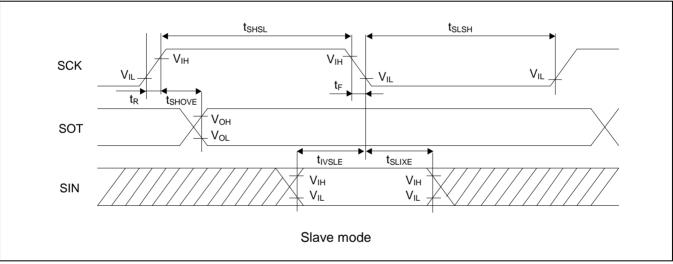

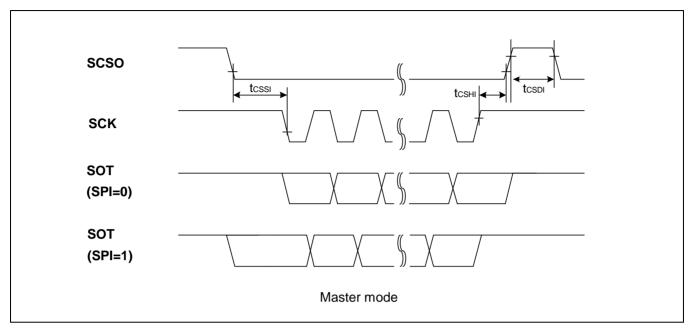

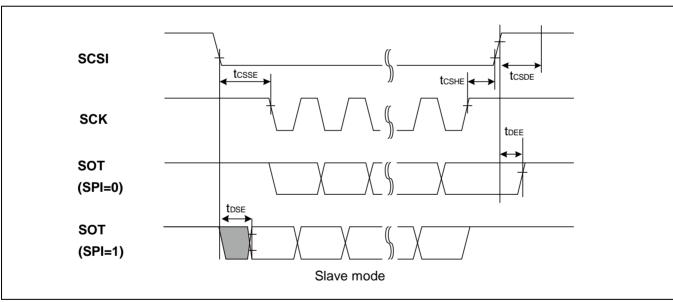

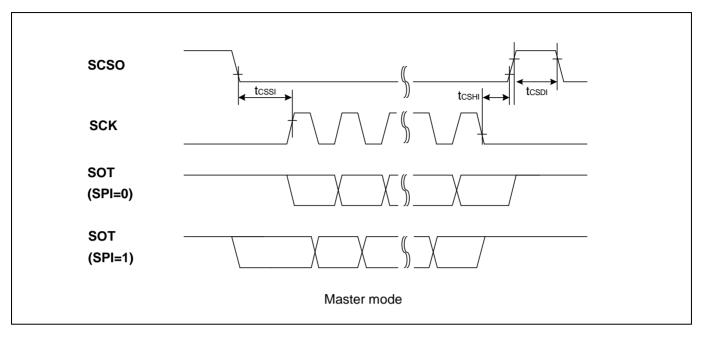

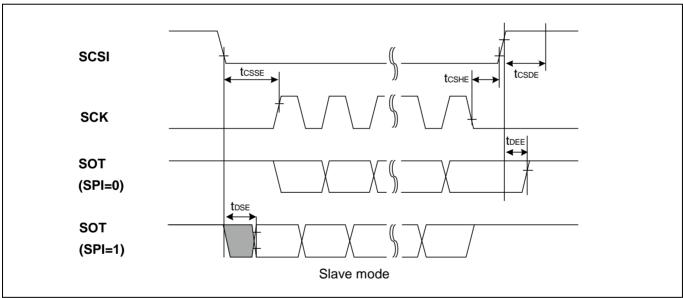

## 11.4.9 CSIO/SPI/UART Timing

## CSIO (SPI=0, SCINV=0)

$(V_{CC}=AV_{CC}=1.65 \text{ V to } 3.6 \text{ V}, V_{SS}=AV_{SS}=0 \text{ V}, T_{A}=-40^{\circ}\text{C to } +105^{\circ}\text{C})$

| Parameter                                        | Symbol             | Pin           | Conditions  | V <sub>CC</sub> < 2      | 2.7 V | V <sub>cc</sub> ≥ 2      | 2.7 V | Unit  |

|--------------------------------------------------|--------------------|---------------|-------------|--------------------------|-------|--------------------------|-------|-------|

| Farameter                                        | Syllibol           | Name          | Conditions  | Min                      | Max   | Min                      | Max   | Ollic |

| Serial clock cycle time                          | t <sub>SCYC</sub>  | SCKx          |             | 4 t <sub>CYCP</sub>      | -     | 4 t <sub>CYCP</sub>      | -     | ns    |

| $SCK \downarrow \rightarrow SOT$ delay time      | t <sub>SLOVI</sub> | SCKx,<br>SOTx |             | - 30                     | + 30  | - 20                     | + 20  | ns    |

| $SIN \rightarrow SCK \uparrow setup time$        | t <sub>IVSHI</sub> | SCKx,<br>SINx | Master mode | 60                       | -     | 50                       | -     | ns    |

| $SCK \uparrow \rightarrow SIN \text{ hold time}$ | t <sub>SHIXI</sub> | SCKx,<br>SINx |             | 0                        | -     | 0                        | -     | ns    |

| Serial clock L pulse width                       | t <sub>SLSH</sub>  | SCKx          |             | 2 t <sub>CYCP</sub> - 10 | -     | 2 t <sub>CYCP</sub> - 10 | -     | ns    |

| Serial clock H pulse width                       | t <sub>SHSL</sub>  | SCKx          |             | t <sub>CYCP</sub> +10    | -     | t <sub>CYCP</sub> +10    | -     | ns    |

| $SCK \downarrow \rightarrow SOT$ delay time      | t <sub>SLOVE</sub> | SCKx,<br>SOTx |             | -                        | 65    | -                        | 52    | ns    |

| SIN → SCK ↑ setup time                           | t <sub>IVSHE</sub> | SCKx,<br>SINx | Slave mode  | 10                       | -     | 10                       | -     | ns    |

| $SCK \uparrow \rightarrow SIN$ hold time         | t <sub>SHIXE</sub> | SCKx,<br>SINx |             | 20                       | -     | 20                       | -     | ns    |

| SCK falling time                                 | t <sub>F</sub>     | SCKx          | 1           | -                        | 5     | -                        | 5     | ns    |

| SCK rising time                                  | t <sub>R</sub>     | SCKx          |             | -                        | 5     | -                        | 5     | ns    |

#### Notes:

- The above AC characteristics are for clock synchronous mode.

- t<sub>CYCP</sub> represents the APB bus clock cycle time.

For the number of the APB bus to which Multi-function Serial has been connected, see "8. Block Diagram ".

- The characteristics are only applicable when the relocate port numbers are the same. For instance, they are not applicable for the combination of SCKx\_0 and SOTx\_1.

- External load capacitance C<sub>L</sub>=30 pF

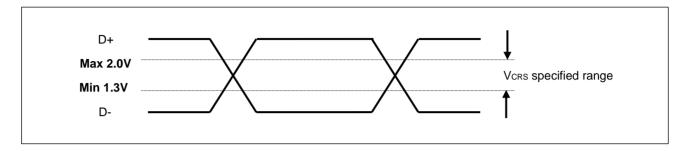

- \*3 : The output drive capability of the driver is below 0.3 V at Low-state (VoL) (to 3.6 V and 1.5 k $\Omega$  load), and 2.8 V or above (to the VSS and 1.5 k $\Omega$  load) at high-state (VoH)

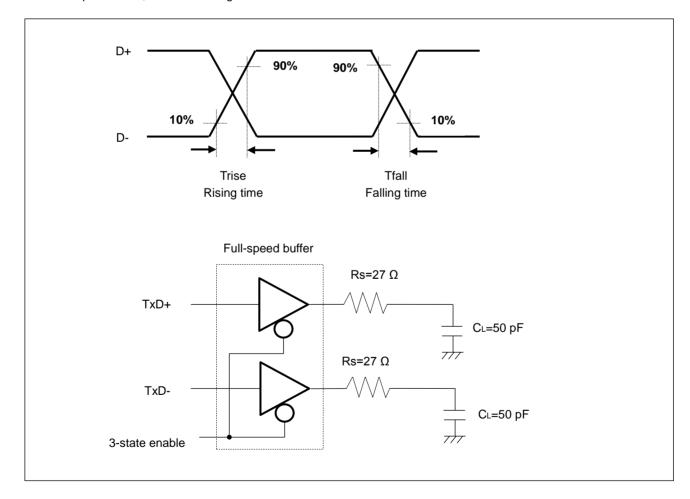

- \*4: The cross voltage of the external differential output signal (D+ / D-) of USB I/O buffer is within 1.3 V to 2.0 V.

\*5: The indicate rising time (Trise) and falling time (Tfall) of the full-speed differential data signal. They are defined by the time between 10% and 90% of the output signal voltage. For full-speed buffer, Tr/Tf ratio is regulated as within ±10% to minimize RFI emission.

\*6 : USB Full-speed connection is performed via twist pair cable shield with 90  $\Omega$  ± 15% characteristic impedance (Differential Mode).

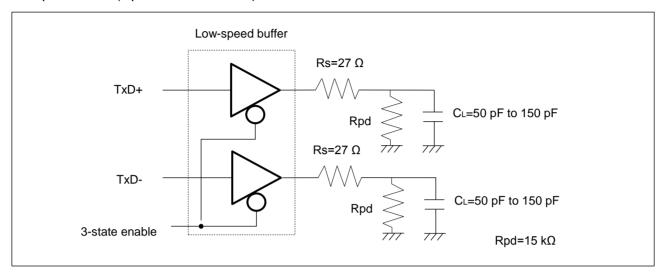

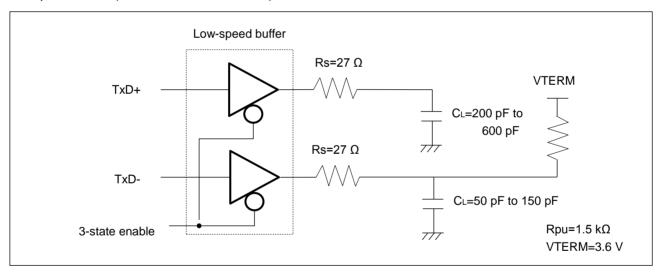

USB standard defines that output impedance of USB driver must be in range from  $28\Omega$  to  $44\Omega$ . So, discrete series resistor (Rs) addition is defined in order to satisfy the above definition and keep balance.

When using this USB I/O, use it with 25  $\Omega$  to 33  $\Omega$  (recommendation value : 27  $\Omega$ ) series resistor Rs.

# · Low-Speed Load (Upstream Port Load) - Reference 1

# · Low-Speed Load (Downstream Port Load) - Reference 2

# 11.7.2 Low-Voltage Detection Interrupt

$(T_A = -40^{\circ}C \text{ to } +105^{\circ}C)$

| Parameter                   | Symbol             | Conditions   |      | Value |                               | Unit  | Remarks            |

|-----------------------------|--------------------|--------------|------|-------|-------------------------------|-------|--------------------|

| Farailletei                 | Syllibol           | Conditions   | Min  | Тур   | Max                           | Oilit | Keiliaiks          |

| Detected voltage            | VDL                | SVHI=00100   | 1.56 | 1.70  | 1.84                          | V     | When voltage drops |

| Released voltage            | VDH                | SVHRLI=00100 | 1.61 | 1.75  | 1.89                          | V     | When voltage rises |

| Detected voltage            | VDL                | SVHI=00101   | 1.61 | 1.75  | 1.89                          | V     | When voltage drops |

| Released voltage            | VDH                | SVHRLI=00101 | 1.66 | 1.80  | 1.94                          | V     | When voltage rises |

| Detected voltage            | VDL                | SVHI=00110   | 1.66 | 1.80  | 1.94                          | V     | When voltage drops |

| Released voltage            | VDH                | SVHRLI=00110 | 1.70 | 1.85  | 2.00                          | V     | When voltage rises |

| Detected voltage            | VDL                | SVHI=00111   | 1.70 | 1.85  | 2.00                          | V     | When voltage drops |

| Released voltage            | VDH                | SVHRLI=00111 | 1.75 | 1.90  | 2.05                          | V     | When voltage rises |

| Detected voltage            | VDL                | SVHI=01000   | 1.75 | 1.90  | 2.05                          | V     | When voltage drops |

| Released voltage            | VDH                | SVHRLI=01000 | 1.79 | 1.95  | 2.11                          | V     | When voltage rises |

| Detected voltage            | VDL                | SVHI=01001   | 1.79 | 1.95  | 2.11                          | V     | When voltage drops |

| Released voltage            | VDH                | SVHRLI=01001 | 1.84 | 2.00  | 2.16                          | V     | When voltage rises |

| Detected voltage            | VDL                | SVHI=01010   | 1.84 | 2.00  | 2.16                          | V     | When voltage drops |

| Released voltage            | VDH                | SVHRLI=01010 | 1.89 | 2.05  | 2.21                          | V     | When voltage rises |

| Detected voltage            | VDL                | SVHI=01011   | 1.89 | 2.05  | 2.21                          | V     | When voltage drops |

| Released voltage            | VDH                | SVHRLI=01011 | 1.93 | 2.10  | 2.27                          | V     | When voltage rises |

| Detected voltage            | VDL                | SVHI=01100   | 2.30 | 2.50  | 2.70                          | V     | When voltage drops |

| Released voltage            | VDH                | SVHRLI=01100 | 2.39 | 2.60  | 2.81                          | V     | When voltage rises |

| Detected voltage            | VDL                | SVHI=01101   | 2.39 | 2.60  | 2.81                          | V     | When voltage drops |

| Released voltage            | VDH                | SVHRLI=01101 | 2.48 | 2.70  | 2.92                          | V     | When voltage rises |

| Detected voltage            | VDL                | SVHI=01110   | 2.48 | 2.70  | 2.92                          | V     | When voltage drops |

| Released voltage            | VDH                | SVHRLI=01110 | 2.58 | 2.80  | 3.02                          | V     | When voltage rises |

| Detected voltage            | VDL                | SVHI=01111   | 2.58 | 2.80  | 3.02                          | V     | When voltage drops |

| Released voltage            | VDH                | SVHRLI=01111 | 2.67 | 2.90  | 3.13                          | V     | When voltage rises |

| Detected voltage            | VDL                | SVHI=10000   | 2.67 | 2.90  | 3.13                          | V     | When voltage drops |

| Released voltage            | VDH                | SVHRLI=10000 | 2.76 | 3.00  | 3.24                          | V     | When voltage rises |

| Detected voltage            | VDL                | SVHI=10001   | 2.76 | 3.00  | 3.24                          | V     | When voltage drops |

| Released voltage            | VDH                | SVHRLI=10001 | 2.85 | 3.10  | 3.35                          | V     | When voltage rises |

| Detected voltage            | VDL                | SVHI=10010   | 2.85 | 3.10  | 3.35                          | V     | When voltage drops |

| Released voltage            | VDH                | SVHRLI=10010 | 2.94 | 3.20  | 3.46                          | V     | When voltage rises |

| Detected voltage            | VDL                | SVHI=10011   | 2.94 | 3.20  | 3.46                          | V     | When voltage drops |

| Released voltage            | VDH                | SVHRLI=10011 | 3.04 | 3.30  | 3.56                          | V     | When voltage rises |

| LVD stabilization wait time | $t_{\text{LVDW}}$  | -            | -    | -     | 8160 x<br>t <sub>CYCP</sub> * | μs    |                    |

| LVD detection delay time    | t <sub>LVDDL</sub> | -            | -    | -     | 200                           | μs    |                    |

$<sup>^{\</sup>star}$ :  $t_{\text{CYCP}}$  represents the APB1 bus clock cycle time.

# 11.8 Flash Memory Write/Erase Characteristics

$(V_{CC}=1.65 \text{ V to } 3.6 \text{ V}, T_{A}=-40^{\circ}\text{C to } +105^{\circ}\text{C})$

| Paramet                      | Parameter    |     | Value |      |      | Remarks                                                                   |  |  |

|------------------------------|--------------|-----|-------|------|------|---------------------------------------------------------------------------|--|--|

| Parameter                    |              | Min | Typ*  | Max* | Unit | Remarks                                                                   |  |  |

|                              | Large sector | -   | 1.1   | 2.7  |      | The sector erase time includes the time of                                |  |  |

| Sector erase time            | Small sector | -   | 0.3   | 0.9  | S    | writing prior to internal erase.                                          |  |  |

| Halfword (16-bit) write time |              | -   | 30    | 528  | μs   | The halfword (16-bit) write time excludes the system-level overhead.      |  |  |

| Chip erase time              |              | -   | 11.2  | 28.8 | S    | The chip erase time includes the time of writing prior to internal erase. |  |  |

<sup>\*:</sup> The typical value is immediately after shipment, the maximum value is guarantee value under 10,000 cycle of erase/write.

Write/Erase Cycle and Data Hold Time (Target Value)

| Write/Erase Cycle | Data Hold Time (Year) | Remarks |

|-------------------|-----------------------|---------|

| 1,000             | 20*                   |         |

| 10,000            | 10*                   |         |

<sup>\*:</sup> At average + 85°C