Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product StatusActiveCore ProcessorARM® Cortex®-M3Core Size32-Bit Single-CoreSpeed32MHzConnectivityI²C, IrDA, LINbus, SPI, UART/USART, USBPeripheralsBrown-out Detect/Reset, DMA, I²S, LCD, POR, PWM, WDTNumber of I/O51Program Memory Size256KB (256K x 8)Program Memory TypeFLASHEEPROM Size8K x 8RAM Size32K x 8Voltage - Supply (Vcc/Vdd)1.8V ~ 3.6VData ConvertersA/D 21x12b; D/A 2x12bOscillator TypeInternal |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Core Size32-Bit Single-CoreSpeed32MHzConnectivityI²C, IrDA, LINbus, SPI, UART/USART, USBPeripheralsBrown-out Detect/Reset, DMA, I²S, LCD, POR, PWM, WDTNumber of I/O51Program Memory Size256KB (256K x 8)Program Memory TypeFLASHEEPROM Size8K x 8RAM Size32K x 8Voltage - Supply (Vcc/Vdd)1.8V ~ 3.6VData ConvertersA/D 21x12b; D/A 2x12b                                                                         |

| Speed32MHzConnectivityI*C, IrDA, LINbus, SPI, UART/USART, USBPeripheralsBrown-out Detect/Reset, DMA, I*S, LCD, POR, PWM, WDTNumber of I/O51Program Memory Size256KB (256K x 8)Program Memory TypeFLASHEEPROM Size8K x 8RAM Size32K x 8Voltage - Supply (Vcc/Vdd)1.8V ~ 3.6VData ConvertersA/D 21x12b; D/A 2x12b                                                                                                    |

| ConnectivityI²C, IrDA, LINbus, SPI, UART/USART, USBPeripheralsBrown-out Detect/Reset, DMA, I²S, LCD, POR, PWM, WDTNumber of I/O51Program Memory Size256KB (256K x 8)Program Memory TypeFLASHEEPROM Size8K x 8RAM Size32K x 8Voltage - Supply (Vcc/Vdd)1.8V ~ 3.6VData ConvertersA/D 21x12b; D/A 2x12b                                                                                                              |

| PeripheralsBrown-out Detect/Reset, DMA, I²S, LCD, POR, PWM, WDTNumber of I/O51Program Memory Size256KB (256K x 8)Program Memory TypeFLASHEEPROM Size8K x 8RAM Size32K x 8Voltage - Supply (Vcc/Vdd)1.8V ~ 3.6VData ConvertersA/D 21x12b; D/A 2x12b                                                                                                                                                                 |

| Number of I/O51Program Memory Size256KB (256K x 8)Program Memory TypeFLASHEEPROM Size8K x 8RAM Size32K x 8Voltage - Supply (Vcc/Vdd)1.8V ~ 3.6VData ConvertersA/D 21x12b; D/A 2x12b                                                                                                                                                                                                                                |

| Program Memory Size256KB (256K x 8)Program Memory TypeFLASHEEPROM Size8K x 8RAM Size32K x 8Voltage - Supply (Vcc/Vdd)1.8V ~ 3.6VData ConvertersA/D 21x12b; D/A 2x12b                                                                                                                                                                                                                                               |

| Program Memory TypeFLASHEEPROM Size8K x 8RAM Size32K x 8Voltage - Supply (Vcc/Vdd)1.8V ~ 3.6VData ConvertersA/D 21x12b; D/A 2x12b                                                                                                                                                                                                                                                                                  |

| EEPROM Size8K x 8RAM Size32K x 8Voltage - Supply (Vcc/Vdd)1.8V ~ 3.6VData ConvertersA/D 21x12b; D/A 2x12b                                                                                                                                                                                                                                                                                                          |

| RAM Size32K x 8Voltage - Supply (Vcc/Vdd)1.8V ~ 3.6VData ConvertersA/D 21x12b; D/A 2x12b                                                                                                                                                                                                                                                                                                                           |

| Voltage - Supply (Vcc/Vdd)1.8V ~ 3.6VData ConvertersA/D 21x12b; D/A 2x12b                                                                                                                                                                                                                                                                                                                                          |

| Data Converters     A/D 21x12b; D/A 2x12b                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Oscillator Type Internal                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Operating Temperature -40°C ~ 85°C (TA)                                                                                                                                                                                                                                                                                                                                                                            |

| Mounting Type Surface Mount                                                                                                                                                                                                                                                                                                                                                                                        |

| Package / Case 64-LQFP                                                                                                                                                                                                                                                                                                                                                                                             |

| Supplier Device Package64-LQFP (10x10)                                                                                                                                                                                                                                                                                                                                                                             |

| Purchase URL https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l162rct6tr                                                                                                                                                                                                                                                                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2.1 Device overview

### Table 2. Ultra-low power STM32L162xC device features and peripheral counts

| Peripheral                                    |                     | STM32L162RC                                                                                                | STM32L162VC         |  |  |  |

|-----------------------------------------------|---------------------|------------------------------------------------------------------------------------------------------------|---------------------|--|--|--|

| Flash (Kbytes)                                |                     | 25                                                                                                         | 56                  |  |  |  |

| Data EEPROM (Kbytes)                          |                     | 8                                                                                                          |                     |  |  |  |

| RAM (Kbytes)                                  |                     | 3                                                                                                          | 2                   |  |  |  |

| AES                                           |                     | 1                                                                                                          |                     |  |  |  |

|                                               | 32 bit              |                                                                                                            | 1                   |  |  |  |

| Timers                                        | General-<br>purpose | 6                                                                                                          |                     |  |  |  |

|                                               | Basic               | 2                                                                                                          | 2                   |  |  |  |

|                                               | SPI                 | 8(3                                                                                                        | i) <sup>(1)</sup>   |  |  |  |

|                                               | l <sup>2</sup> S    | 2                                                                                                          | 2                   |  |  |  |

| Communicatio<br>n interfaces                  | l <sup>2</sup> C    | 2                                                                                                          | 2                   |  |  |  |

|                                               | USART               | 3                                                                                                          |                     |  |  |  |

|                                               | USB                 | 1                                                                                                          |                     |  |  |  |

| GPIOs                                         | ·                   | 51                                                                                                         | 83                  |  |  |  |

| Operation ampli                               | ifiers              | 2                                                                                                          |                     |  |  |  |

| 12-bit synchronized ADC<br>Number of channels |                     | 1<br>21                                                                                                    | 1<br>25             |  |  |  |

| 12-bit DAC<br>Number of chan                  | inels               | 2 2                                                                                                        |                     |  |  |  |

| LCD<br>COM x SEG                              |                     | 1<br>4x32 or 8x28                                                                                          | 1<br>4x44 or 8x40   |  |  |  |

| Comparators                                   |                     | 2                                                                                                          |                     |  |  |  |

| Capacitive sensing channels                   |                     | 23                                                                                                         | 23                  |  |  |  |

| Max. CPU frequency                            |                     | 32 MHz                                                                                                     |                     |  |  |  |

| Operating voltage                             |                     | 1.8 V to 3.6 V (down to 1.65 V at power-down) with BOR option<br>1.65 V to 3.6 V without BOR option        |                     |  |  |  |

| Operating temperatures                        |                     | Ambient operating temperature: -40 °C to 85 °C / -40 °C to 105 °C<br>Junction temperature: -40 to + 110 °C |                     |  |  |  |

| Packages                                      |                     | LQFP64                                                                                                     | LQFP100<br>UFBGA100 |  |  |  |

1. 5 SPIs are USART configured in synchronous mode emulating SPI master.

|                                   | Functionalities depending on the operating power supply range |                           |                                  |                      |  |

|-----------------------------------|---------------------------------------------------------------|---------------------------|----------------------------------|----------------------|--|

| Operating power supply range      | DAC and ADC operation                                         | USB                       | Dynamic voltage<br>scaling range | I/O operation        |  |

| $V_{DD} = V_{DDA} = 2.0$ to 2.4 V | Conversion time up<br>to 500 Ksps                             | Functional <sup>(2)</sup> | Range 1, Range 2<br>or Range 3   | Full speed operation |  |

| $V_{DD} = V_{DDA} = 2.4$ to 3.6 V | Conversion time up<br>to 1 Msps                               | Functional <sup>(2)</sup> | Range 1, Range 2<br>or Range 3   | Full speed operation |  |

#### Table 3. Functionalities depending on the operating power supply range (continued)

CPU frequency changes from initial to final must respect "F<sub>CPU</sub> initial < 4\*F<sub>CPU</sub> final" to limit V<sub>CORE</sub> drop due to current consumption peak when frequency increases. It must also respect 5 μs delay between two changes. For example to switch from 4.2 MHz to 32 MHz, the user can switch from 4.2 MHz to 16 MHz, wait 5 μs, then switch from 16 MHz to 32 MHz.

2. Should be USB compliant from I/O voltage standpoint, the minimum  $\rm V_{DD}$  is 3.0 V.

#### Table 4. CPU frequency range depending on dynamic voltage scaling

| CPU frequency range                                | Dynamic voltage scaling range |

|----------------------------------------------------|-------------------------------|

| 16 MHz to 32 MHz (1ws)<br>32 kHz to 16 MHz (0ws)   | Range 1                       |

| 8 MHz to 16 MHz (1ws)<br>32 kHz to 8 MHz (0ws)     | Range 2                       |

| 2.1MHz to 4.2 MHz (1ws)<br>32 kHz to 2.1 MHz (0ws) | Range 3                       |

### 3.4 Clock management

The clock controller distributes the clocks coming from different oscillators to the core and the peripherals. It also manages clock gating for low-power modes and ensures clock robustness. It features:

- Clock prescaler: to get the best trade-off between speed and current consumption, the clock frequency to the CPU and peripherals can be adjusted by a programmable prescaler.

- **Safe clock switching**: clock sources can be changed safely on the fly in run mode through a configuration register.

- **Clock management**: to reduce power consumption, the clock controller can stop the clock to the core, individual peripherals or memory.

- **System clock source**: three different clock sources can be used to drive the master clock SYSCLK:

- 1-24 MHz high-speed external crystal (HSE), that can supply a PLL

- 16 MHz high-speed internal RC oscillator (HSI), trimmable by software, that can supply a PLL

- Multispeed internal RC oscillator (MSI), trimmable by software, able to generate 7 frequencies (65 kHz, 131 kHz, 262 kHz, 524 kHz, 1.05 MHz, 2.1 MHz, 4.2 MHz).

When a 32.768 kHz clock source is available in the system (LSE), the MSI frequency can be trimmed by software down to a ±0.5% accuracy.

- **Auxiliary clock source**: two ultra-low-power clock sources that can be used to drive the LCD controller and the real-time clock:

- 32.768 kHz low-speed external crystal (LSE)

- 37 kHz low-speed internal RC (LSI), also used to drive the independent watchdog. The LSI clock can be measured using the high-speed internal RC oscillator for greater precision.

- **RTC and LCD clock sources:** the LSI, LSE or HSE sources can be chosen to clock the RTC and the LCD, whatever the system clock.

- **USB clock source:** the embedded PLL has a dedicated 48 MHz clock output to supply the USB interface.

- **Startup clock:** after reset, the microcontroller restarts by default with an internal 2 MHz clock (MSI). The prescaler ratio and clock source can be changed by the application program as soon as the code execution starts.

- Clock security system (CSS): this feature can be enabled by software. If a HSE clock failure occurs, the master clock is automatically switched to HSI and a software interrupt is generated if enabled.

- **Clock-out capability (MCO: microcontroller clock output):** it outputs one of the internal clocks for external use by the application.

Several prescalers allow the configuration of the AHB frequency, each APB (APB1 and APB2) domains. The maximum frequency of the AHB and the APB domains is 32 MHz. See *Figure 2* for details on the clock tree.

### 3.5 Low-power real-time clock and backup registers

The real-time clock (RTC) is an independent BCD timer/counter. Dedicated registers contain the sub-second, second, minute, hour (12/24 hour), week day, date, month, year, in BCD (binary-coded decimal) format. Correction for 28, 29 (leap year), 30, and 31 day of the month are made automatically. The RTC provides two programmable alarms and programmable periodic interrupts with wakeup from Stop and Standby modes.

The programmable wakeup time ranges from 120 µs to 36 hours.

The RTC can be calibrated with an external 512 Hz output, and a digital compensation circuit helps reduce drift due to crystal deviation.

The RTC can also be automatically corrected with a 50/60Hz stable powerline.

The RTC calendar can be updated on the fly down to sub second precision, which enables network system synchronization.

A time stamp can record an external event occurrence, and generates an interrupt.

There are thirty-two 32-bit backup registers provided to store 128 bytes of user application data. They are cleared in case of tamper detection.

Three pins can be used to detect tamper events. A change on one of these pins can reset backup register and generate an interrupt. To prevent false tamper event, like ESD event, these three tamper inputs can be digitally filtered.

# 3.6 GPIOs (general-purpose inputs/outputs)

Each of the GPIO pins can be configured by software as output (push-pull or open-drain), as input (with or without pull-up or pull-down) or as peripheral alternate function. Most of the GPIO pins are shared with digital or analog alternate functions, and can be individually remapped using dedicated AFIO registers. All GPIOs are high current capable. The alternate function configuration of I/Os can be locked if needed following a specific sequence in order to avoid spurious writing to the I/O registers. The I/O controller is connected to the AHB with a toggling speed of up to 16 MHz.

### External interrupt/event controller (EXTI)

The external interrupt/event controller consists of 24 edge detector lines used to generate interrupt/event requests. Each line can be individually configured to select the trigger event (rising edge, falling edge, both) and can be masked independently. A pending register maintains the status of the interrupt requests. The EXTI can detect an external line with a pulse width shorter than the Internal APB2 clock period. Up to 83 GPIOs can be connected to the 16 external interrupt lines. The 8 other lines are connected to RTC, PVD, USB, comparator events or capacitive sensing acquisition.

# 3.12 Operational amplifier

The STM32L162xC devices embed two operational amplifiers with external or internal follower routing capability (or even amplifier and filter capability with external components). When one operational amplifier is selected, one external ADC channel is used to enable output measurement.

The operational amplifiers feature:

- Low input bias current

- Low offset voltage

- Low-power mode

- Rail-to-rail input

## 3.13 Ultra-low-power comparators and reference voltage

The STM32L162xC devices embed two comparators sharing the same current bias and reference voltage. The reference voltage can be internal or external (coming from an I/O).

- One comparator with fixed threshold

- One comparator with rail-to-rail inputs, fast or slow mode. The threshold can be one of the following:

- DAC output

- External I/O

- Internal reference voltage (V<sub>REFINT</sub>) or a sub-multiple (1/4, 1/2, 3/4)

Both comparators can wake up from Stop mode, and be combined into a window comparator.

The internal reference voltage is available externally via a low-power / low-current output buffer (driving current capability of 1  $\mu$ A typical).

# 3.14 System configuration controller and routing interface

The system configuration controller provides the capability to remap some alternate functions on different I/O ports.

The highly flexible routing interface allows the application firmware to control the routing of different I/Os to the TIM2, TIM3 and TIM4 timer input captures. It also controls the routing of internal analog signals to ADC1, COMP1 and COMP2 and the internal reference voltage  $V_{\text{REFINT}}$ .

# 3.15 Touch sensing

The STM32L162xC devices provide a simple solution for adding capacitive sensing functionality to any application. These devices offer up to 23 capacitive sensing channels distributed over 10 analog I/O groups. Both software and timer capacitive sensing acquisition modes are supported.

Capacitive sensing technology is able to detect the presence of a finger near a sensor which is protected from direct touch by a dielectric (glass, plastic...). The capacitive variation introduced by the finger (or any conductive object) is measured using a proven

# 6.2 Absolute maximum ratings

Stresses above the absolute maximum ratings listed in *Table 11: Voltage characteristics*, *Table 12: Current characteristics*, and *Table 13: Thermal characteristics* may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

| Symbol                              | Ratings                                                                         | Min                  | Мах                  | Unit |

|-------------------------------------|---------------------------------------------------------------------------------|----------------------|----------------------|------|

| V <sub>DD</sub> –V <sub>SS</sub>    | External main supply voltage (including $V_{DDA}$ and $V_{DD}$ ) <sup>(1)</sup> | -0.3                 | 4.0                  |      |

| V <sub>IN</sub> <sup>(2)</sup>      | Input voltage on five-volt tolerant pin                                         | V <sub>SS</sub> –0.3 | V <sub>DD</sub> +4.0 | V    |

| VIN                                 | Input voltage on any other pin                                                  | V <sub>SS</sub> –0.3 | 4.0                  |      |

| ΔV <sub>DDx</sub>                   | Variations between different V <sub>DD</sub> power pins                         | -                    | 50                   | mV   |

| V <sub>SSX</sub> –V <sub>SS</sub>   | Variations between all different ground pins <sup>(3)</sup>                     | -                    | 50                   |      |

| V <sub>REF+</sub> –V <sub>DDA</sub> | Allowed voltage difference for V <sub>REF+</sub> > V <sub>DDA</sub>             | -                    | 0.4                  | V    |

| V <sub>ESD(HBM)</sub>               | Electrostatic discharge voltage<br>(human body model)                           | See Section 6.3 11   |                      |      |

1. All main power ( $V_{DD}$ ,  $V_{DDA}$ ) and ground ( $V_{SS}$ ,  $V_{SSA}$ ) pins must always be connected to the external power supply, in the permitted range.

2. V<sub>IN</sub> maximum must always be respected. Refer to Table 12 for maximum allowed injected current values.

3. Include  $V_{REF-}$  pin.

#### Table 12. Current characteristics

| Symbol                               | Ratings                                                                                | Max.  | Unit |

|--------------------------------------|----------------------------------------------------------------------------------------|-------|------|

| $I_{VDD(\Sigma)}$                    | Total current into sum of all V <sub>DD_x</sub> power lines (source) <sup>(1)</sup> 10 |       |      |

| $I_{VSS(\Sigma)}^{(2)}$              | Total current out of sum of all $V_{SS_x}$ ground lines (sink) <sup>(1)</sup>          | 100   |      |

| I <sub>VDD(PIN)</sub>                | Maximum current into each V <sub>DD_x</sub> power pin (source) <sup>(1)</sup>          | 70    |      |

| I <sub>VSS(PIN)</sub>                | Maximum current out of each VSS_x ground pin (sink) <sup>(1)</sup>                     | -70   |      |

|                                      | Output current sunk by any I/O and control pin                                         | 25    |      |

| I <sub>IO</sub>                      | Output current sourced by any I/O and control pin                                      | - 25  | mA   |

| 51                                   | Total output current sunk by sum of all IOs and control pins <sup>(2)</sup>            | 60    |      |

| ΣΙ <sub>ΙΟ(ΡΙΝ)</sub>                | Total output current sourced by sum of all IOs and control pins <sup>(2)</sup>         | -60   |      |

| (3)                                  | Injected current on five-volt tolerant I/O <sup>(4)</sup> , RST and B pins             | -5/+0 |      |

| I <sub>INJ(PIN)</sub> <sup>(3)</sup> | Injected current on any other pin <sup>(5)</sup>                                       | ± 5   |      |

| ΣΙ <sub>INJ(PIN)</sub>               | Total injected current (sum of all I/O and control pins) <sup>(6)</sup>                | ± 25  |      |

1. All main power ( $V_{DD}$ ,  $V_{DDA}$ ) and ground ( $V_{SS}$ ,  $V_{SSA}$ ) pins must always be connected to the external power supply, in the permitted range.

2. This current consumption must be correctly distributed over all I/Os and control pins. The total output current must not be sunk/sourced between two consecutive power supply pins referring to high pin count LQFP packages.

3. Negative injection disturbs the analog performance of the device. See note in Section 6.3.17.

| Table 25. Peripheral current consumption <sup>(1)</sup> (continued)         Typical consumption, V <sub>DD</sub> = 3.0 V, T <sub>A</sub> = 25 °C |                    |                                                              |                                                              |                                                              |                               |                      |

|--------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--------------------------------------------------------------|--------------------------------------------------------------|--------------------------------------------------------------|-------------------------------|----------------------|

| Peripheral                                                                                                                                       |                    | Typical c                                                    | consumption,                                                 | V <sub>DD</sub> = 3.0 V, 1                                   | <sub>A</sub> = 25 °C          |                      |

|                                                                                                                                                  |                    | Range 1,<br>V <sub>CORE</sub> =<br>1.8 V<br>VOS[1:0] =<br>01 | Range 2,<br>V <sub>CORE</sub> =<br>1.5 V<br>VOS[1:0] =<br>10 | Range 3,<br>V <sub>CORE</sub> =<br>1.2 V<br>VOS[1:0] =<br>11 | Low-power<br>sleep and<br>run | Unit                 |

|                                                                                                                                                  | SYSCFG &<br>RI     | 2.6                                                          | 2.0                                                          | 1.6                                                          | 2.0                           |                      |

|                                                                                                                                                  | TIM9               | 7.9                                                          | 6.4                                                          | 5.0                                                          | 6.4                           |                      |

|                                                                                                                                                  | TIM10              | 5.9                                                          | 4.7                                                          | 3.8                                                          | 4.7                           |                      |

| APB2                                                                                                                                             | TIM11              | 5.9                                                          | 4.6                                                          | 3.7                                                          | 4.6                           |                      |

|                                                                                                                                                  | ADC <sup>(2)</sup> | 10.5                                                         | 8.3                                                          | 6.6                                                          | 8.3                           |                      |

|                                                                                                                                                  | SPI1               | 4.3                                                          | 3.4                                                          | 2.8                                                          | 3.4                           |                      |

|                                                                                                                                                  | USART1             | 8.8                                                          | 7.1                                                          | 5.6                                                          | 7.1                           |                      |

|                                                                                                                                                  | GPIOA              | 4.3                                                          | 3.3                                                          | 2.6                                                          | 3.3                           |                      |

|                                                                                                                                                  | GPIOB              | 4.3                                                          | 3.5                                                          | 2.8                                                          | 3.5                           | µA/MHz               |

|                                                                                                                                                  | GPIOC              | 4.0                                                          | 3.2                                                          | 2.5                                                          | 3.2                           | (f <sub>HCLK</sub> ) |

|                                                                                                                                                  | GPIOD              | 4.1                                                          | 3.3                                                          | 2.5                                                          | 3.3                           |                      |

|                                                                                                                                                  | GPIOE              | 4.2                                                          | 3.4                                                          | 2.7                                                          | 3.4                           |                      |

| AHB                                                                                                                                              | GPIOH              | 3.7                                                          | 3.0                                                          | 2.3                                                          | 3.0                           |                      |

|                                                                                                                                                  | CRC                | 0.8                                                          | 0.6                                                          | 0.5                                                          | 0.6                           |                      |

|                                                                                                                                                  | AES                | 5                                                            | 4                                                            | 3                                                            | 4                             |                      |

|                                                                                                                                                  | FLASH              | 11.1                                                         | 9.4                                                          | 8                                                            | _(3)                          |                      |

|                                                                                                                                                  | DMA1               | 15.6                                                         | 12.7                                                         | 10                                                           | 12.7                          |                      |

|                                                                                                                                                  | DMA2               | 16.3                                                         | 13.4                                                         | 10.5                                                         | 13.4                          |                      |

| All enabled                                                                                                                                      |                    | 192                                                          | 158                                                          | 123                                                          | 148.6                         |                      |

| I <sub>DD (RTC)</sub>                                                                                                                            |                    |                                                              |                                                              |                                                              |                               |                      |

| I <sub>DD (LCD)</sub>                                                                                                                            |                    |                                                              | 3                                                            | .1                                                           |                               |                      |

| $I_{\text{DD (ADC)}}^{(4)}$                                                                                                                      |                    |                                                              | 1                                                            |                                                              |                               |                      |

| I <sub>DD (DAC)</sub> <sup>(5)</sup>                                                                                                             |                    |                                                              |                                                              |                                                              |                               |                      |

| I <sub>DD (COMP1)</sub>                                                                                                                          |                    | 0.16                                                         |                                                              |                                                              |                               | μΑ                   |

|                                                                                                                                                  | Slow mode          |                                                              |                                                              | 2                                                            |                               |                      |

| IDD (COMP2)                                                                                                                                      | Fast mode          |                                                              | Ę                                                            | 5                                                            |                               |                      |

| I <sub>DD (PVD / BOR</sub>                                                                                                                       | (6)                | 2.6                                                          |                                                              |                                                              |                               |                      |

| I <sub>DD (IWDG)</sub>                                                                                                                           |                    |                                                              | 0.:                                                          | 25                                                           |                               |                      |

Table 25. Peripheral current consumption<sup>(1)</sup> (continued)

Data based on differential I<sub>DD</sub> measurement between all peripherals OFF an one peripheral with clock enabled, in the following conditions: f<sub>HCLK</sub> = 32 MHz (range 1), f<sub>HCLK</sub> = 16 MHz (range 2), f<sub>HCLK</sub> = 4 MHz (range 3), f<sub>HCLK</sub> = 64kHz (Low-power run/sleep), f<sub>APB1</sub> = f<sub>HCLK</sub>, f<sub>APB2</sub> = f<sub>HCLK</sub>, default prescaler value for each peripheral. The CPU is in Sleep mode in both cases. No I/O pins toggling.

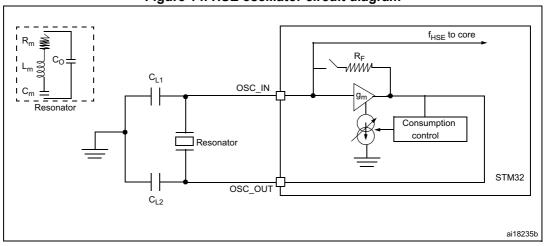

Figure 14. HSE oscillator circuit diagram

1. R<sub>EXT</sub> value depends on the crystal characteristics.

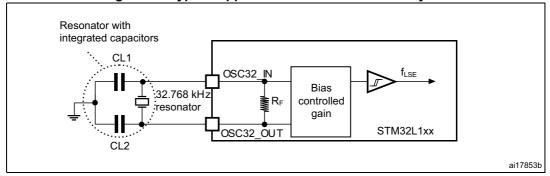

### Low-speed external clock generated from a crystal/ceramic resonator

The low-speed external (LSE) clock can be supplied with a 32.768 kHz crystal/ceramic resonator oscillator. All the information given in this paragraph are based on characterization results obtained with typical external components specified in *Table 30*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

| Symbol                  | Parameter                                                                                     | Conditions                            | Min | Тур    | Max | Unit |

|-------------------------|-----------------------------------------------------------------------------------------------|---------------------------------------|-----|--------|-----|------|

| f <sub>LSE</sub>        | Low speed external oscillator<br>frequency                                                    | -                                     | -   | 32.768 | -   | kHz  |

| R <sub>F</sub>          | Feedback resistor                                                                             | -                                     | -   | 1.2    | -   | MΩ   |

| C <sup>(2)</sup>        | Recommended load capacitance versus equivalent serial resistance of the crystal $(R_S)^{(3)}$ | R <sub>S</sub> = 30 kΩ                | -   | 8      | -   | pF   |

| I <sub>LSE</sub>        | LSE driving current                                                                           | $V_{DD}$ = 3.3 V, $V_{IN}$ = $V_{SS}$ | -   | -      | 1.1 | μA   |

|                         |                                                                                               | V <sub>DD</sub> = 1.8 V               | -   | 450    | -   |      |

| I <sub>DD (LSE)</sub>   | IDD (LSE) LSE oscillator current consumption                                                  | V <sub>DD</sub> = 3.0 V               | -   | 600    | -   | nA   |

|                         |                                                                                               | V <sub>DD</sub> = 3.6V                | -   | 750    | -   |      |

| 9 <sub>m</sub>          | Oscillator transconductance                                                                   | -                                     | 3   | -      | -   | µA/V |

| $t_{\rm SU(LSE)}^{(4)}$ | Startup time                                                                                  | $V_{\text{DD}}$ is stabilized         | -   | 1      | _   | S    |

| Table 30. LSE oscilla | tor characteristics | $(f_{LSE} = 32.768 \text{ kHz})^{(1)}$ |

|-----------------------|---------------------|----------------------------------------|

|-----------------------|---------------------|----------------------------------------|

1. Guaranteed by characterization results.

2. Refer to the note and caution paragraphs below the table, and to the application note AN2867 "Oscillator design guide for ST microcontrollers".

The oscillator selection can be optimized in terms of supply current using an high quality resonator with small R<sub>S</sub> value for example MSIV-TIN32.768kHz. Refer to crystal manufacturer for more details.

- t<sub>SU(LSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 32.768 kHz oscillation is reached. This value is measured for a standard crystal resonator and it can vary significantly with the crystal manufacturer.

- Note: For  $C_{L1}$  and  $C_{L2}$ , it is recommended to use high-quality ceramic capacitors in the 5 pF to 15 pF range selected to match the requirements of the crystal or resonator (see Figure 15).  $C_{L1}$  and  $C_{L2}$ , are usually the same size. The crystal manufacturer typically specifies a load capacitance which is the series combination of  $C_{L1}$  and  $C_{L2}$ .

Load capacitance  $C_L$  has the following formula:  $\overline{C_L} = C_{L1} \times \overline{C_{L2}} / (C_{L1} + C_{L2}) + C_{stray}$  where  $C_{stray}$  is the pin capacitance and board or trace PCB-related capacitance. Typically, it is between 2 pF and 7 pF.

**Caution:** To avoid exceeding the maximum value of  $C_{L1}$  and  $C_{L2}$  (15 pF) it is strongly recommended to use a resonator with a load capacitance  $C_L \leq 7$  pF. Never use a resonator with a load capacitance of 12.5 pF.

**Example:** if the user chooses a resonator with a load capacitance of  $C_L = 6 \text{ pF}$  and  $C_{stray} = 2 \text{ pF}$ , then  $C_{L1} = C_{L2} = 8 \text{ pF}$ .

#### Figure 15. Typical application with a 32.768 kHz crystal

### 6.3.8 PLL characteristics

The parameters given in *Table 34* are derived from tests performed under the conditions summarized in *Table 14*.

| Cumhal                 | Devenuetor                                              | Value |     |                    | l lmit |  |

|------------------------|---------------------------------------------------------|-------|-----|--------------------|--------|--|

| Symbol Parameter       |                                                         | Min   | Тур | Max <sup>(1)</sup> | - Unit |  |

| £                      | PLL input clock <sup>(2)</sup>                          | 2     | -   | 24                 | MHz    |  |

| f <sub>PLL_IN</sub>    | PLL input clock duty cycle                              | 45    | -   | 55                 | %      |  |

| f <sub>PLL_OUT</sub>   | PLL output clock                                        | 2     | -   | 32                 | MHz    |  |

| t <sub>LOCK</sub>      | PLL lock time<br>PLL input = 16 MHz<br>PLL VCO = 96 MHz | -     | 115 | 160                | μs     |  |

| Jitter                 | Cycle-to-cycle jitter                                   | -     | -   | ±600               | ps     |  |

| I <sub>DDA</sub> (PLL) | Current consumption on V <sub>DDA</sub>                 | -     | 220 | 450                |        |  |

| I <sub>DD</sub> (PLL)  | Current consumption on V <sub>DD</sub>                  | -     | 120 | 150                | - μΑ   |  |

| Table 34. | PLL | characteristics |

|-----------|-----|-----------------|

|           |     |                 |

1. Guaranteed by characterization results.

2. Take care of using the appropriate multiplier factors so as to have PLL input clock values compatible with the range defined by  $f_{PLL_OUT}$ .

### 6.3.9 Memory characteristics

The characteristics are given at  $T_A$  = -40 to 105 °C unless otherwise specified.

#### **RAM** memory

| Table 35. RAM and hardware regis |

|----------------------------------|

|----------------------------------|

| Symbol | Parameter                          | Conditions           | Min  | Тур | Max | Unit |

|--------|------------------------------------|----------------------|------|-----|-----|------|

| VRM    | Data retention mode <sup>(1)</sup> | STOP mode (or RESET) | 1.65 | -   | -   | V    |

1. Minimum supply voltage without losing data stored in RAM (in Stop mode or under Reset) or in hardware registers (only in Stop mode).

To complete these trials, ESD stress can be applied directly on the device, over the range of specification values. When unexpected behavior is detected, the software can be hardened to prevent unrecoverable errors occurring (see application note AN1015).

#### **Electromagnetic Interference (EMI)**

The electromagnetic field emitted by the device are monitored while a simple application is executed (toggling 2 LEDs through the I/O ports). This emission test is compliant with IEC 61967-2 standard which specifies the test board and the pin loading.

|                             |                                       |                          |                             | Max vs.                     | frequenc                     | cy range                     |      |

|-----------------------------|---------------------------------------|--------------------------|-----------------------------|-----------------------------|------------------------------|------------------------------|------|

| Symbol                      | ymbol Parameter Conditions            |                          | Monitored<br>frequency band | 4 MHz<br>voltage<br>range 3 | 16 MHz<br>voltage<br>range 2 | 32 MHz<br>voltage<br>range 1 | Unit |

|                             |                                       | V <sub>DD</sub> = 3.3 V, | 0.1 to 30 MHz               | 3                           | -6                           | -5                           |      |

| 6                           | Peak level                            | $T_A = 25 \degree C$ ,   | 30 to 130 MHz               | 18                          | 4                            | -7                           | dBµV |

| S <sub>EMI</sub> Peak level | LQFP100 package<br>compliant with IEC | 130 MHz to 1GHz          | 15                          | 5                           | -7                           |                              |      |

|                             |                                       | 61967-2                  | SAE EMI Level               | 2.5                         | 2                            | 1                            | -    |

Table 39. EMI characteristics

### 6.3.11 Electrical sensitivity characteristics

Based on three different tests (ESD, LU) using specific measurement methods, the device is stressed in order to determine its performance in terms of electrical sensitivity.

### Electrostatic discharge (ESD)

Electrostatic discharges (a positive then a negative pulse separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts  $\times$  (n+1) supply pins). This test conforms to the JESD22-A114, ANSI/ESD STM5.3.1. standard.

| Symbol                | Ratings                                                     | Conditions                                                   | Class | Maximum<br>value <sup>(1)</sup> | Unit |

|-----------------------|-------------------------------------------------------------|--------------------------------------------------------------|-------|---------------------------------|------|

| V <sub>ESD(HBM)</sub> | Electrostatic<br>discharge voltage<br>(human body model)    | $T_A = +25 \text{ °C}$ , conforming<br>to JESD22-A114        | 2     | 2000                            | V    |

| V <sub>ESD(CDM)</sub> | Electrostatic<br>discharge voltage<br>(charge device model) | $T_A = +25 \text{ °C}$ , conforming<br>to ANSI/ESD STM5.3.1. | C4    | 500                             | V    |

Table 40. ESD absolute maximum ratings

1. Guaranteed by characterization results.

### 6.3.13 I/O port characteristics

### General input/output characteristics

Unless otherwise specified, the parameters given in *Table 49* are derived from tests performed under the conditions summarized in *Table 14*. All I/Os are CMOS and TTL compliant.

| Symbol           | Parameter                                          | Conditions                                                                                | Min                                                                               | Тур                                | Max                                   | Unit |  |

|------------------|----------------------------------------------------|-------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|------------------------------------|---------------------------------------|------|--|

| N/               |                                                    | TC and FT I/O                                                                             | -                                                                                 | -                                  | 0.3 V <sub>DD</sub> <sup>(1)(2)</sup> |      |  |

| $V_{IL}$         | Input low level voltage                            | BOOT0                                                                                     | -                                                                                 | -                                  | 0.14 V <sub>DD</sub> <sup>(2)</sup>   |      |  |

|                  |                                                    | TC I/O                                                                                    | 0.45 V <sub>DD</sub> +0.38 <sup>(2)</sup>                                         | -                                  | -                                     |      |  |

| $V_{\text{IH}}$  | Input high level voltage                           | FT I/O                                                                                    | 0.39 V <sub>DD</sub> +0.59 <sup>(2)</sup>                                         | -                                  | -                                     | V    |  |

|                  |                                                    | BOOT0                                                                                     | 0.15 V <sub>DD</sub> +0.56 <sup>(2)</sup>                                         | -                                  | -                                     |      |  |

| V                | I/O Schmitt trigger voltage                        | TC and FT I/O                                                                             | -                                                                                 | 10% V <sub>DD</sub> <sup>(3)</sup> | -                                     |      |  |

| V <sub>hys</sub> | hysteresis <sup>(2)</sup>                          | BOOT0                                                                                     | -                                                                                 | 0.01                               | -                                     |      |  |

|                  |                                                    | V <sub>SS</sub> ≤V <sub>IN</sub> ≤V <sub>DD</sub><br>I/Os with LCD                        | -                                                                                 | -                                  | ±50                                   |      |  |

|                  | Input leakage current <sup>(4)</sup>               |                                                                                           | V <sub>SS</sub> ≤V <sub>IN</sub> ≤V <sub>DD</sub><br>I/Os with analog<br>switches | -                                  | -                                     | ±50  |  |

| l <sub>lkg</sub> |                                                    | V <sub>SS</sub> ≤V <sub>IN</sub> ≤V <sub>DD</sub><br>I/Os with analog<br>switches and LCD | -                                                                                 | -                                  | ±50                                   | nA   |  |

|                  |                                                    | V <sub>SS</sub> ≤V <sub>IN</sub> ≤V <sub>DD</sub><br>I/Os with USB                        | -                                                                                 | -                                  | ±250                                  |      |  |

|                  |                                                    | V <sub>SS</sub> ≤V <sub>IN</sub> ≤V <sub>DD</sub><br>TC and FT I/Os                       | -                                                                                 | -                                  | ±50                                   |      |  |

|                  |                                                    | FT I/O<br>V <sub>DD</sub> ≤V <sub>IN</sub> ≤5V                                            | -                                                                                 | -                                  | ±10                                   | μA   |  |

| R <sub>PU</sub>  | Weak pull-up equivalent resistor <sup>(5)(1)</sup> | $V_{IN} = V_{SS}$                                                                         | 30                                                                                | 45                                 | 60                                    | kΩ   |  |

| R <sub>PD</sub>  | Weak pull-down equivalent resistor <sup>(5)</sup>  | $V_{IN} = V_{DD}$                                                                         | 30                                                                                | 45                                 | 60                                    | kΩ   |  |

| C <sub>IO</sub>  | I/O pin capacitance                                | -                                                                                         | -                                                                                 | 5                                  | -                                     | pF   |  |

| Table 43. | I/O static | characteristics |

|-----------|------------|-----------------|

|           |            | onunuotonistios |

1. Guaranteed by test in production

2. Guaranteed by design.

3. With a minimum of 200 mV.

4. The max. value may be exceeded if negative current is injected on adjacent pins.

Pull-up and pull-down resistors are designed with a true resistance in series with a switchable PMOS/NMOS. This MOS/NMOS contribution to the series resistance is minimum (~10% order).

#### 6.3.14 **NRST** pin characteristics

The NRST pin input driver uses CMOS technology. It is connected to a permanent pull-up resistor, R<sub>PU</sub> (see Table 46)

Unless otherwise specified, the parameters given in Table 46 are derived from tests performed under the conditions summarized in Table 14.

| Symbol                                | Parameter                                          | Conditions                                                   | Min                       | Тур                               | Max                 | Unit |

|---------------------------------------|----------------------------------------------------|--------------------------------------------------------------|---------------------------|-----------------------------------|---------------------|------|

| V <sub>IL(NRST)</sub> <sup>(1)</sup>  | NRST input low level voltage                       | -                                                            | -                         | -                                 | 0.3 V <sub>DD</sub> |      |

| V <sub>IH(NRST)</sub> <sup>(1)</sup>  | NRST input high<br>level voltage                   | -                                                            | 0.39V <sub>DD</sub> +0.59 | -                                 | -                   | V    |

| V <sub>OL(NRST)</sub> <sup>(1)</sup>  | NRST output low                                    | I <sub>OL</sub> = 2 mA<br>2.7 V < V <sub>DD</sub> < 3.6 V    | -                         | -                                 | 0.4                 | v    |

|                                       | level voltage                                      | I <sub>OL</sub> = 1.5 mA<br>1.65 V < V <sub>DD</sub> < 2.7 V | -                         | -                                 | 0.4                 |      |

| V <sub>hys(NRST)</sub> <sup>(1)</sup> | NRST Schmitt trigger voltage hysteresis            | -                                                            | -                         | 10%V <sub>DD</sub> <sup>(2)</sup> | -                   | mV   |

| R <sub>PU</sub>                       | Weak pull-up<br>equivalent resistor <sup>(3)</sup> | $V_{IN} = V_{SS}$                                            | 30                        | 45                                | 60                  | kΩ   |

| V <sub>F(NRST)</sub> <sup>(1)</sup>   | NRST input filtered pulse                          | -                                                            | -                         | -                                 | 50                  | ns   |

| V <sub>NF(NRST)</sub> <sup>(3)</sup>  | NRST input not<br>filtered pulse                   | -                                                            | 350                       | -                                 | -                   | ns   |

Table 46. NRST pin characteristics

1. Guaranteed by design.

2. With a minimum of 200 mV.

The pull-up is designed with a true resistance in series with a switchable PMOS. This PMOS contribution to the series 3. resistance is around 10%.

Figure 17. Recommended NRST pin protection

1. The reset network protects the device against parasitic resets.

2. The user must ensure that the level on the NRST pin can go below the  $V_{IL(NRST)}$  max level specified in *Table 46*. Otherwise the reset will not be taken into account by the device.

### 6.3.15 TIM timer characteristics

The parameters given in the Table 47 are guaranteed by design.

Refer to *Section 6.3.13: I/O port characteristics* for details on the input/output ction characteristics (output compare, input capture, external clock, PWM output).

| Symbol                 | Parameter                                                                 | Conditions                    | Min    | Мах                     | Unit                 |

|------------------------|---------------------------------------------------------------------------|-------------------------------|--------|-------------------------|----------------------|

| t                      | Timer resolution time                                                     | -                             | 1      | -                       | t <sub>TIMxCLK</sub> |

| t <sub>res(TIM)</sub>  |                                                                           | f <sub>TIMxCLK</sub> = 32 MHz | 31.25  | -                       | ns                   |

| f                      | Timer external clock                                                      | -                             | 0      | f <sub>TIMxCLK</sub> /2 | MHz                  |

| f <sub>EXT</sub>       | frequency on CH1 to CH4                                                   | f <sub>TIMxCLK</sub> = 32 MHz | 0      | 16                      | MHz                  |

| Res <sub>TIM</sub>     | Timer resolution                                                          | -                             |        | 16                      | bit                  |

|                        | 16-bit counter clock                                                      | -                             | 1      | 65536                   | t <sub>TIMxCLK</sub> |

| t <sub>COUNTER</sub>   | period when internal clock<br>is selected (timer's<br>prescaler disabled) | f <sub>TIMxCLK</sub> = 32 MHz | 0.0312 | 2048                    | μs                   |

| t                      | Maximum possible count                                                    | -                             | -      | 65536 × 65536           | t <sub>TIMxCLK</sub> |

| <sup>t</sup> MAX_COUNT |                                                                           | f <sub>TIMxCLK</sub> = 32 MHz | -      | 134.2                   | S                    |

Table 47. TIMx<sup>(1)</sup> characteristics

1. TIMx is used as a general term to refer to the TIM2, TIM3 and TIM4 timers.

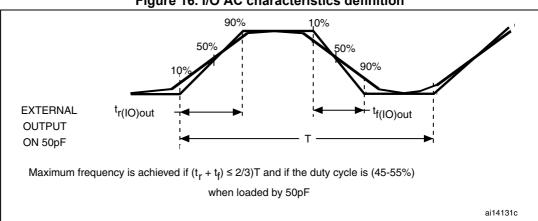

1. Measurement points are done at CMOS levels:  $0.3V_{\text{DD}}$  and  $0.7V_{\text{DD}}$

ODD bit value, digital contribution leads to a min of (I2SDIV/(2\*I2SDIV+ODD) and a max of (I2SDIV+ODD)/(2\*I2SDIV+ODD). Fs max is supported for each mode/condition.

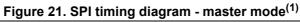

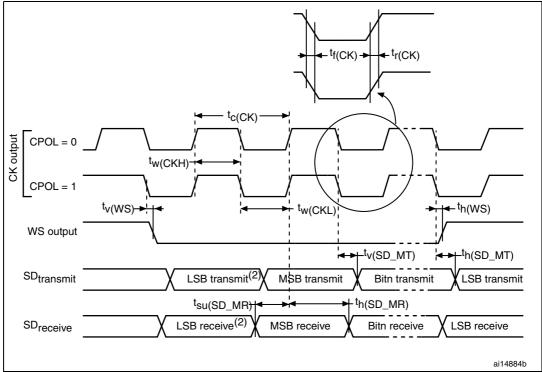

Figure 23. I<sup>2</sup>S slave timing diagram (Philips protocol)<sup>(1)</sup>

- 1. Measurement points are done at CMOS levels: 0.3 ×  $V_{DD}$  and 0.7 ×  $V_{DD}.$

- 2. LSB transmit/receive of the previously transmitted byte. No LSB transmit/receive is sent before the first byte.

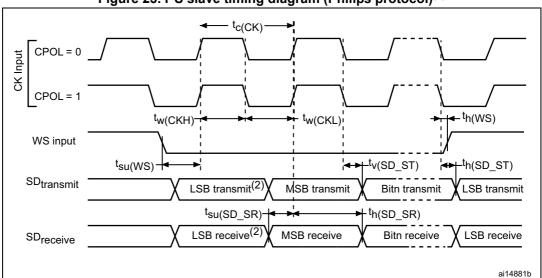

Figure 24. I<sup>2</sup>S master timing diagram (Philips protocol)<sup>(1)</sup>

- 1. Guaranteed by characterization results.

- 2. LSB transmit/receive of the previously transmitted byte. No LSB transmit/receive is sent before the first byte.

DocID022881 Rev 10

#### STM32L162VC, STM32L162RC

| Symbol | Parameter                            | Test conditions                                                                                                                                         | Min <sup>(3)</sup> | Тур | Max <sup>(3)</sup> | Unit |  |

|--------|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|--------------------|------|--|

| ET     | Total unadjusted error               |                                                                                                                                                         | -                  | 2   | 4                  |      |  |

| EO     | Offset error                         | $2.4 \text{ V} \leq \text{V}_{\text{DDA}} \leq 3.6 \text{ V}$                                                                                           | -                  | 1   | 2                  |      |  |

| EG     | Gain error                           | 2.4 V ≤V <sub>REF+</sub> ≤ 3.6 V<br>f <sub>ADC</sub> = 8 MHz, R <sub>AIN</sub> = 50 Ω                                                                   | -                  | 1.5 | 3.5                | LSB  |  |

| ED     | Differential linearity error         | $T_A = -40$ to 105 °C                                                                                                                                   | -                  | 1   | 2                  |      |  |

| EL     | Integral linearity error             |                                                                                                                                                         | -                  | 1.7 | 3                  |      |  |

| ENOB   | Effective number of bits             |                                                                                                                                                         | 9.2                | 10  | -                  | bits |  |

| SINAD  | Signal-to-noise and distortion ratio | 2.4 V $\leq$ V <sub>DDA</sub> $\leq$ 3.6 V<br>V <sub>DDA</sub> = V <sub>REF+</sub><br>f <sub>ADC</sub> = 16 MHz, R <sub>AIN</sub> = 50 Ω                | 57.5               | 62  | -                  |      |  |

| SNR    | Signal-to-noise ratio                | $T_A = -40$ to 105 ° C                                                                                                                                  | 57.5               | 62  | -                  | dB   |  |

| THD    | Total harmonic distortion            | F <sub>input</sub> =10kHz                                                                                                                               | -                  | -70 | -65                |      |  |

| ENOB   | Effective number of bits             |                                                                                                                                                         | 9.2                | 10  | -                  | bits |  |

| SINAD  | Signal-to-noise and distortion ratio | 1.8 V $\leq$ V <sub>DDA</sub> $\leq$ 2.4 V<br>V <sub>DDA</sub> = V <sub>REF+</sub><br>f <sub>ADC</sub> = 8 MHz or 4 MHz, R <sub>AIN</sub> = 50 $\Omega$ | 57.5               | 62  | -                  |      |  |

| SNR    | Signal-to-noise ratio                | T <sub>A</sub> = -40 to 105 ° C                                                                                                                         | 57.5               | 62  | -                  | dB   |  |

| THD    | Total harmonic distortion            | F <sub>input</sub> =10kHz                                                                                                                               | -                  | -70 | -65                |      |  |

| ET     | Total unadjusted error               |                                                                                                                                                         | -                  | 4   | 6.5                |      |  |

| EO     | Offset error                         | 2.4 V ≤V <sub>DDA</sub> ≤ 3.6 V                                                                                                                         | -                  | 2   | 4                  |      |  |

| EG     | Gain error                           | 1.8 V ≤V <sub>REF+</sub> ≤ 2.4 V<br>f <sub>ADC</sub> = 4 MHz, R <sub>AIN</sub> = 50 Ω                                                                   | -                  | 4   | 6                  | LSB  |  |

| ED     | Differential linearity error         | $T_A = -40$ to 105 °C                                                                                                                                   | -                  | 1   | 2                  |      |  |

| EL     | Integral linearity error             |                                                                                                                                                         | -                  | 1.5 | 3                  |      |  |

| ET     | Total unadjusted error               |                                                                                                                                                         | -                  | 2   | 3                  |      |  |

| EO     | Offset error                         | 1.8 V ≤V <sub>DDA</sub> ≤ 2.4 V                                                                                                                         | -                  | 1   | 1.5                |      |  |

| EG     | Gain error                           | 1.8 V ≤V <sub>REF+</sub> ≤ 2.4 V<br>f <sub>ADC</sub> = 4 MHz, R <sub>AIN</sub> = 50 Ω                                                                   | -                  | 1.5 | 2                  | LSB  |  |

| ED     | Differential linearity error         | $T_A = -40$ to 105 °C                                                                                                                                   | -                  | 1   | 2                  |      |  |

| EL     | Integral linearity error             |                                                                                                                                                         | -                  | 1   | 1.5                | 1    |  |

Table 57. ADC accuracy<sup>(1)(2)</sup>

1. ADC DC accuracy values are measured after internal calibration.

ADC accuracy vs. negative injection current: Injecting a negative current on any analog input pins should be avoided as this significantly reduces the accuracy of the conversion being performed on another analog input. It is recommended to add a Schottky diode (pin to ground) to analog pins which may potentially inject negative currents. Any positive injection current within the limits specified for I<sub>INJ(PIN)</sub> and ΣI<sub>INJ(PIN)</sub> in Section 6.3.12 does not affect the ADC accuracy.

3. Guaranteed by characterization results.

| Symbol               | Par                                                                                                     | rameter        | Condition <sup>(1)</sup>                                   | Min <sup>(2)</sup>       | Тур  | Max <sup>(2)</sup> | Unit |

|----------------------|---------------------------------------------------------------------------------------------------------|----------------|------------------------------------------------------------|--------------------------|------|--------------------|------|

| PSRR                 | Power supply                                                                                            | Normal mode    | DC                                                         | -                        | -85  | -                  | ٩D   |

| PSRR                 | rejection ratio                                                                                         | Low-power mode |                                                            | -                        | -90  | -                  | dB   |

|                      |                                                                                                         | Normal mode    | V >24V                                                     | 400                      | 1000 | 3000               |      |

|                      | Denducidate                                                                                             | Low-power mode | – V <sub>DD</sub> >2.4 V                                   | 150                      | 300  | 800                | 6117 |

| GBW                  | Bandwidth                                                                                               | Normal mode    | V2 4 V                                                     | 200                      | 500  | 2200               | kHZ  |

|                      |                                                                                                         | Low-power mode | – V <sub>DD</sub> <2.4 V                                   | 70                       | 150  | 800                |      |

|                      |                                                                                                         | Normal mode    | $V_{DD}$ >2.4 V<br>(between 0.1 V and $V_{DD}$ -0.1 V)     | -                        | 700  | -                  |      |

| SR                   | Slew rate                                                                                               | Low-power mode | V <sub>DD</sub> >2.4 V                                     | -                        | 100  | -                  | V/ms |

|                      |                                                                                                         | Normal mode    | V <sub>DD</sub> <2.4 V                                     | -                        | 300  | -                  | -    |

|                      |                                                                                                         | Low-power mode |                                                            | -                        | 50   | -                  |      |