Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                         |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 32MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB                    |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT       |

| Number of I/O              | 83                                                                      |

| Program Memory Size        | 256KB (256K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 8K x 8                                                                  |

| RAM Size                   | 32K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                             |

| Data Converters            | A/D 25x12b; D/A 2x12b                                                   |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 100-UFBGA                                                               |

| Supplier Device Package    | 100-UFBGA (7x7)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l162vch6tr |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2 Description

The ultra-low-power STM32L162xC devices incorporate the connectivity power of the universal serial bus (USB) with the high-performance ARM<sup>®</sup> Cortex<sup>®</sup>-M3 32-bit RISC core operating at a frequency of 32 MHz (33.3 DMIPS), a memory protection unit (MPU), high-speed embedded memories (Flash memory up to 256 Kbytes and RAM up to 32 Kbytes) and an extensive range of enhanced I/Os and peripherals connected to two APB buses.

The STM32L162xC devices offer two operational amplifiers, one 12-bit ADC, two DACs, two ultra-low-power comparators, AES, one general-purpose 32-bit timer, six general-purpose 16-bit timers and two basic timers, which can be used as time bases.

Moreover, the STM32L162xC devices contain standard and advanced communication interfaces: up to two I2Cs, three SPIs, two I2S, three USARTs and an USB. The STM32L162xC devices offer up to 23 capacitive sensing channels to simply add a touch sensing functionality to any application.

They also include a real-time clock and a set of backup registers that remain powered in Standby mode.

Finally, the integrated LCD controller has a built-in LCD voltage generator that allows to drive up to 8 multiplexed LCDs with the contrast independent of the supply voltage.

The ultra-low-power STM32L162xC devices operate from a 1.8 to 3.6 V power supply (down to 1.65 V at power down) with BOR and from a 1.65 to 3.6 V power supply without BOR option. They are available in the -40 to +85 °C and -40 to +105 °C temperature ranges. A comprehensive set of power-saving modes allows the design of low-power applications.

|                                              |                             |                        | Low-         | Low-           |                                                | Stop                                         | 5                                            | Standby                                       |

|----------------------------------------------|-----------------------------|------------------------|--------------|----------------|------------------------------------------------|----------------------------------------------|----------------------------------------------|-----------------------------------------------|

| lps                                          | Run/Active                  | Sleep                  | power<br>Run | power<br>Sleep |                                                | Wakeup<br>capability                         |                                              | Wakeup<br>capability                          |

| ADC                                          | Y                           | Y                      |              |                |                                                |                                              |                                              |                                               |

| DAC                                          | Y                           | Y                      | Y            | Y              | Y                                              |                                              |                                              |                                               |

| Tempsensor                                   | Y                           | Y                      | Y            | Y              | Y                                              |                                              |                                              |                                               |

| OP amp                                       | Y                           | Y                      | Y            | Y              | Y                                              |                                              |                                              |                                               |

| Comparators                                  | Y                           | Y                      | Y            | Y              | Y                                              | Y                                            |                                              |                                               |

| 16-bit and 32-bit<br>Timers                  | Y                           | Y                      | Y            | Y              |                                                |                                              |                                              |                                               |

| IWDG                                         | Y                           | Y                      | Y            | Y              | Y                                              | Y                                            | Y                                            | Y                                             |

| WWDG                                         | Y                           | Y                      | Y            | Y              |                                                |                                              |                                              |                                               |

| Touch sensing                                | Y                           | Y                      |              |                |                                                |                                              |                                              |                                               |

| Systic Timer                                 | Y                           | Y                      | Y            | Y              |                                                |                                              |                                              |                                               |

| GPIOs                                        | Y                           | Y                      | Y            | Y              | Y                                              | Y                                            |                                              | 3 pins                                        |

| Wakeup time to<br>Run mode                   | 0 µs                        | 0.4 µs                 | 3 µs         | 46 µs          |                                                | < 8 µs                                       |                                              | 58 µs                                         |

|                                              |                             |                        |              |                | (                                              | 0.43 µA<br>no RTC)<br>′ <sub>DD</sub> =1.8V  | (                                            | 0.29 µA<br>no RTC)<br>′ <sub>DD</sub> =1.8V   |

| Consumption<br>V <sub>DD</sub> =1.8 to 3.6 V | Down to 185<br>µA/MHz (from | Down to 34.5           | Down to      | Down to        | 1.15 μΑ<br>(with RTC)<br>V <sub>DD</sub> =1.8V |                                              | (v                                           | 0.9 μA<br>vith RTC)<br>′ <sub>DD</sub> =1.8V  |

| v <sub>DD</sub> =1.8 to 3.6 v<br>(Typ)       | Flash)                      | µA/MHz (from<br>Flash) | 8.6 µA       | 4.4 µA         | (                                              | 0.44 µA<br>no RTC)<br>′ <sub>DD</sub> =3.0V  | 0.29 μA<br>(no RTC)<br>V <sub>DD</sub> =3.0V | no RTC)                                       |

|                                              |                             |                        |              |                |                                                | 1.4 μΑ<br>vith RTC)<br>′ <sub>DD</sub> =3.0V | (v                                           | 1.15 µA<br>vith RTC)<br>′ <sub>DD</sub> =3.0V |

# Table 5. Functionalities depending on the working mode (from Run/active down to<br/>standby) (continued)

1. The startup on communication line wakes the CPU which was made possible by an EXTI, this induces a delay before entering run mode.

# 3.2 ARM<sup>®</sup> Cortex<sup>®</sup>-M3 core with MPU

The ARM<sup>®</sup> Cortex<sup>®</sup>-M3 processor is the industry leading processor for embedded systems. It has been developed to provide a low-cost platform that meets the needs of MCU implementation, with a reduced pin count and low-power consumption, while delivering outstanding computational performance and an advanced system response to interrupts.

The ARM<sup>®</sup> Cortex<sup>®</sup>-M3 32-bit RISC processor features exceptional code-efficiency, delivering the high-performance expected from an ARM core in the memory size usually associated with 8- and 16-bit devices.

DocID022881 Rev 10

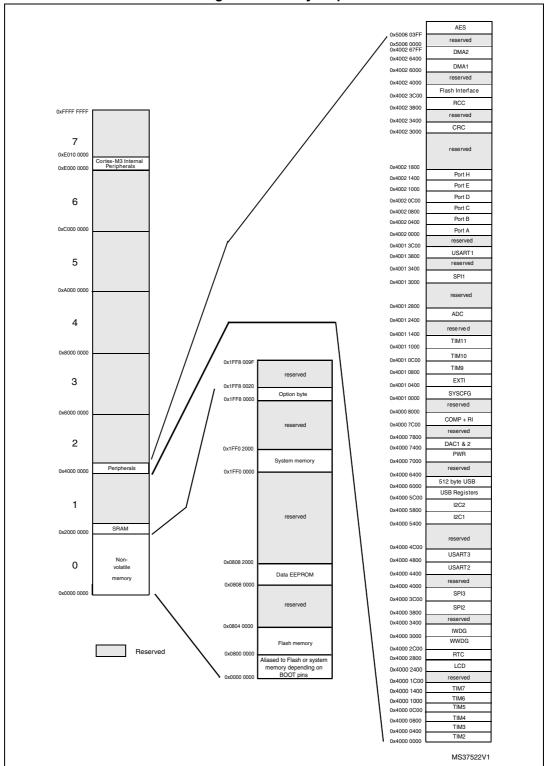

## 3.7 Memories

The STM32L162xC devices have the following features:

- 32 Kbytes of embedded RAM accessed (read/write) at CPU clock speed with 0 wait states. With the enhanced bus matrix, operating the RAM does not lead to any performance penalty during accesses to the system bus (AHB and APB buses).

- The non-volatile memory is divided into three arrays:

- 256 Kbytes of embedded Flash program memory

- 8 Kbytes of data EEPROM

- Options bytes

The options bytes are used to write-protect or read-out protect the memory (with 4 Kbytes granularity) and/or readout-protect the whole memory with the following options:

- Level 0: no readout protection

- Level 1: memory readout protection, the Flash memory cannot be read from or written to if either debug features are connected or boot in RAM is selected

- Level 2: chip readout protection, debug features (ARM Cortex-M3 JTAG and serial wire) and boot in RAM selection disabled (JTAG fuse)

The whole non-volatile memory embeds the error correction code (ECC) feature.

The user area of the Flash memory can be protected against Dbus read access by PCROP feature (see RM0038 for details).

# 3.8 DMA (direct memory access)

The flexible 12-channel, general-purpose DMA is able to manage memory-to-memory, peripheral-to-memory and memory-to-peripheral transfers. The DMA controller supports circular buffer management, avoiding the generation of interrupts when the controller reaches the end of the buffer.

Each channel is connected to dedicated hardware DMA requests, with software trigger support for each channel. Configuration is done by software and transfer sizes between source and destination are independent.

The DMA can be used with the main peripherals: AES, SPI, I<sup>2</sup>C, USART, general-purpose timers, DAC and ADC.

#### STM32L162VC, STM32L162RC

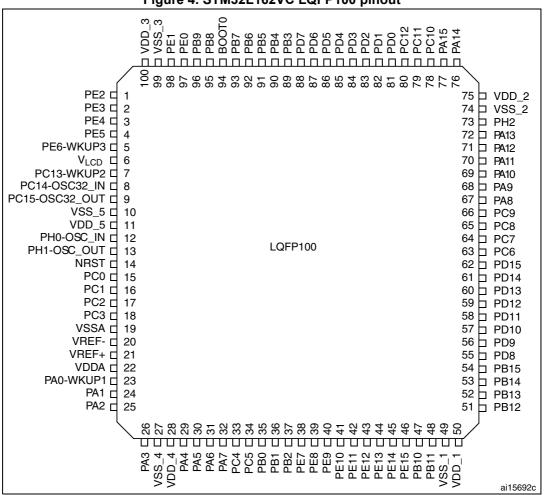

Figure 4. STM32L162VC LQFP100 pinout

1. This figure shows the package top view.

# 5 Memory mapping

Figure 6. Memory map

57

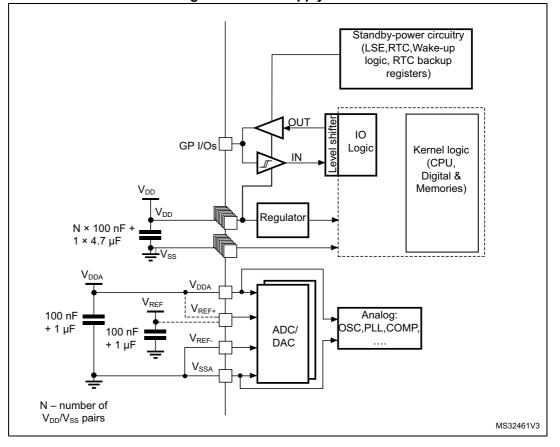

# 6.1.6 Power supply scheme

## Figure 9. Power supply scheme

#### STM32L162VC, STM32L162RC

- Positive current injection is not possible on these I/Os. A negative injection is induced by V<sub>IN</sub><V<sub>SS</sub>. I<sub>INJ(PIN)</sub> must never be exceeded. Refer to *Table 11* for maximum allowed input voltage values.

- A positive injection is induced by V<sub>IN</sub> > V<sub>DD</sub> while a negative injection is induced by V<sub>IN</sub> < V<sub>SS</sub>. I<sub>INJ(PIN)</sub> must never be exceeded. Refer to *Table 11: Voltage characteristics* for the maximum allowed input voltage values.

- 6. When several inputs are submitted to a current injection, the maximum  $\Sigma I_{INJ(PIN)}$  is the absolute sum of the positive and negative injected currents (instantaneous values).

| Symbol           | Ratings                      | Value       | Unit |

|------------------|------------------------------|-------------|------|

| T <sub>STG</sub> | Storage temperature range    | –65 to +150 | °C   |

| TJ               | Maximum junction temperature | 150         | °C   |

#### Table 13. Thermal characteristics

# 6.3 Operating conditions

## 6.3.1 General operating conditions

| Symbol                          | Parameter                                          | Conditions                            | Min  | Мах                  | Unit |  |

|---------------------------------|----------------------------------------------------|---------------------------------------|------|----------------------|------|--|

| f <sub>HCLK</sub>               | Internal AHB clock frequency                       | -                                     | 0    | 32                   |      |  |

| f <sub>PCLK1</sub>              | Internal APB1 clock frequency                      | -                                     | 0    | 32                   | MHz  |  |

| f <sub>PCLK2</sub>              | Internal APB2 clock frequency                      | -                                     | 0    | 32                   |      |  |

|                                 |                                                    | BOR detector disabled                 | 1.65 | 3.6                  |      |  |

| V <sub>DD</sub>                 | Standard operating voltage                         | BOR detector enabled, at power on     | 1.8  | 3.6                  | v    |  |

|                                 |                                                    | BOR detector disabled, after power on | 1.65 | 3.6                  |      |  |

| V <sub>DDA</sub> <sup>(1)</sup> | Analog operating voltage<br>(ADC and DAC not used) | Must be the same voltage as           | 1.65 | 3.6                  | - V  |  |

| V DDA` ´                        | Analog operating voltage<br>(ADC or DAC used)      | V <sub>DD</sub> <sup>(2)</sup>        | 1.8  | 3.6                  |      |  |

|                                 |                                                    | FT pins; 2.0 V ≤V <sub>DD</sub>       | -0.3 | 5.5 <sup>(3)</sup>   |      |  |

| V                               |                                                    | FT pins; $V_{DD}$ < 2.0 V             | -0.3 | 5.25 <sup>(3)</sup>  | V    |  |

| V <sub>IN</sub>                 | I/O input voltage                                  | BOOT0 pin                             | 0    | 5.5                  | V    |  |

|                                 |                                                    | Any other pin                         | -0.3 | V <sub>DD</sub> +0.3 |      |  |

|                                 |                                                    | LQFP48 package                        | -    | 364                  |      |  |

|                                 |                                                    | LQFP100 package                       | -    | 465                  |      |  |

|                                 | Power dissipation at TA = 85 °C for                | LQFP64 package                        | -    | 435                  |      |  |

| P <sub>D</sub>                  | suffix 6 or TA = 105 °C for suffix $7^{(4)}$       | UFQFPN48 package                      | -    | 625                  | mW   |  |

|                                 |                                                    | UFBGA100                              | -    | 339                  |      |  |

|                                 |                                                    | WLCSP63 package                       | -    | 408                  |      |  |

#### Table 14. General operating conditions

| Symbol                              | Parameter                                                                                                 | Conditions                                                  | Min | Тур | Мах                                | Unit  |

|-------------------------------------|-----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|-----|-----|------------------------------------|-------|

| f <sub>OSC_IN</sub>                 | Oscillator frequency                                                                                      | -                                                           | 1   |     | 24                                 | MHz   |

| R <sub>F</sub>                      | Feedback resistor                                                                                         | -                                                           | -   | 200 | -                                  | kΩ    |

| С                                   | Recommended load<br>capacitance versus<br>equivalent serial<br>resistance of the crystal<br>$(R_S)^{(3)}$ | R <sub>S</sub> = 30 Ω                                       | -   | 20  | -                                  | pF    |

| I <sub>HSE</sub>                    | HSE driving current                                                                                       | $V_{DD}$ = 3.3 V,<br>$V_{IN}$ = $V_{SS}$ with 30 pF<br>load | -   | -   | 3                                  | mA    |

| 1 .                                 | HSE oscillator power                                                                                      | C = 20 pF<br>f <sub>OSC</sub> = 16 MHz                      | -   | -   | 2.5 (startup)<br>0.7 (stabilized)  | m۸    |

| IDD(HSE)                            | consumption                                                                                               | C = 10 pF<br>f <sub>OSC</sub> = 16 MHz                      | -   | -   | 2.5 (startup)<br>0.46 (stabilized) | - mA  |

| 9 <sub>m</sub>                      | Oscillator<br>transconductance                                                                            | Startup                                                     | 3.5 | -   | -                                  | mA /V |

| t <sub>SU(HSE)</sub> <sup>(4)</sup> | Startup time                                                                                              | V <sub>DD</sub> is stabilized                               | -   | 1   | -                                  | ms    |

Table 29. HSE oscillator characteristics<sup>(1)(2)</sup>

1. Resonator characteristics given by the crystal/ceramic resonator manufacturer.

2. Guaranteed by characterization results.

The relatively low value of the RF resistor offers a good protection against issues resulting from use in a humid environment, due to the induced leakage and the bias condition change. However, it is recommended to take this point into account if the MCU is used in tough humidity conditions.

4. t<sub>SU(HSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 8 MHz oscillation is reached. This value is measured for a standard crystal resonator and it can vary significantly with the crystal manufacturer.

For  $C_{L1}$  and  $C_{L2}$ , it is recommended to use high-quality external ceramic capacitors in the 5 pF to 25 pF range (typ.), designed for high-frequency applications, and selected to match the requirements of the crystal or resonator (see *Figure 14*).  $C_{L1}$  and  $C_{L2}$  are usually the same size. The crystal manufacturer typically specifies a load capacitance which is the series combination of  $C_{L1}$  and  $C_{L2}$ . PCB and MCU pin capacitance must be included (10 pF can be used as a rough estimate of the combined pin and board capacitance) when sizing  $C_{L1}$  and  $C_{L2}$ . Refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from the ST website *www.st.com*.

## 6.3.8 PLL characteristics

The parameters given in *Table 34* are derived from tests performed under the conditions summarized in *Table 14*.

| Cumhal                 | Devenuetor                                              |     | 11  |                    |        |

|------------------------|---------------------------------------------------------|-----|-----|--------------------|--------|

| Symbol                 | Parameter                                               | Min | Тур | Max <sup>(1)</sup> | - Unit |

| £                      | PLL input clock <sup>(2)</sup>                          | 2   | -   | 24                 | MHz    |

| f <sub>PLL_IN</sub>    | PLL input clock duty cycle                              | 45  | -   | 55                 | %      |

| f <sub>PLL_OUT</sub>   | PLL output clock                                        | 2   | -   | 32                 | MHz    |

| t <sub>LOCK</sub>      | PLL lock time<br>PLL input = 16 MHz<br>PLL VCO = 96 MHz | -   | 115 | 160                | μs     |

| Jitter                 | Cycle-to-cycle jitter                                   | -   | -   | ±600               | ps     |

| I <sub>DDA</sub> (PLL) | Current consumption on V <sub>DDA</sub>                 | -   | 220 | 450                |        |

| I <sub>DD</sub> (PLL)  | Current consumption on V <sub>DD</sub>                  | -   | 120 | 150                | - μΑ   |

| Table 34. | PLL | characteristics |

|-----------|-----|-----------------|

|           |     |                 |

1. Guaranteed by characterization results.

2. Take care of using the appropriate multiplier factors so as to have PLL input clock values compatible with the range defined by  $f_{PLL_OUT}$ .

### 6.3.9 Memory characteristics

The characteristics are given at  $T_A$  = -40 to 105 °C unless otherwise specified.

#### **RAM** memory

| Table 35. RAM and hardware regis |

|----------------------------------|

|----------------------------------|

| Symbol | Parameter                          | Conditions           | Min  | Тур | Max | Unit |

|--------|------------------------------------|----------------------|------|-----|-----|------|

| VRM    | Data retention mode <sup>(1)</sup> | STOP mode (or RESET) | 1.65 | -   | -   | V    |

1. Minimum supply voltage without losing data stored in RAM (in Stop mode or under Reset) or in hardware registers (only in Stop mode).

To complete these trials, ESD stress can be applied directly on the device, over the range of specification values. When unexpected behavior is detected, the software can be hardened to prevent unrecoverable errors occurring (see application note AN1015).

#### **Electromagnetic Interference (EMI)**

The electromagnetic field emitted by the device are monitored while a simple application is executed (toggling 2 LEDs through the I/O ports). This emission test is compliant with IEC 61967-2 standard which specifies the test board and the pin loading.

| Symbol |                                                                                    | Conditions               |                             | Max vs.                     |                              |                              |      |

|--------|------------------------------------------------------------------------------------|--------------------------|-----------------------------|-----------------------------|------------------------------|------------------------------|------|

|        | Parameter                                                                          |                          | Monitored<br>frequency band | 4 MHz<br>voltage<br>range 3 | 16 MHz<br>voltage<br>range 2 | 32 MHz<br>voltage<br>range 1 | Unit |

|        | $S_{EMI} \begin{tabular}{c} $V_{DD}$ = 3.3 V, $$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$ | V <sub>DD</sub> = 3.3 V, | 0.1 to 30 MHz               | 3                           | -6                           | -5                           |      |

| 6      |                                                                                    |                          | 30 to 130 MHz               | 18                          | 4                            | -7                           | dBµV |

| SEMI   |                                                                                    | compliant with IEC       | 130 MHz to 1GHz             | 15                          | 5                            | -7                           |      |

|        |                                                                                    |                          | SAE EMI Level               | 2.5                         | 2                            | 1                            | -    |

Table 39. EMI characteristics

## 6.3.11 Electrical sensitivity characteristics

Based on three different tests (ESD, LU) using specific measurement methods, the device is stressed in order to determine its performance in terms of electrical sensitivity.

### Electrostatic discharge (ESD)

Electrostatic discharges (a positive then a negative pulse separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts  $\times$  (n+1) supply pins). This test conforms to the JESD22-A114, ANSI/ESD STM5.3.1. standard.

| Symbol                | Ratings                                                     | Conditions                                                   | Class | Maximum<br>value <sup>(1)</sup> | Unit |

|-----------------------|-------------------------------------------------------------|--------------------------------------------------------------|-------|---------------------------------|------|

| V <sub>ESD(HBM)</sub> | Electrostatic<br>discharge voltage<br>(human body model)    | $T_A = +25 \text{ °C}$ , conforming<br>to JESD22-A114        | 2     | 2000                            | V    |

| V <sub>ESD(CDM)</sub> | Electrostatic<br>discharge voltage<br>(charge device model) | $T_A = +25 \text{ °C}$ , conforming<br>to ANSI/ESD STM5.3.1. | C4    | 500                             | V    |

Table 40. ESD absolute maximum ratings

1. Guaranteed by characterization results.

#### **SPI** characteristics

Unless otherwise specified, the parameters given in the following table are derived from tests performed under the conditions summarized in *Table 14*.

Refer to Section 6.3.12: I/O current injection characteristics for more details on the input/output alternate function characteristics (NSS, SCK, MOSI, MISO).

| Symbol                                                                     | Parameter                        | Conditions                 | Min                   | Max <sup>(2)</sup>    | Unit |

|----------------------------------------------------------------------------|----------------------------------|----------------------------|-----------------------|-----------------------|------|

| _                                                                          |                                  | Master mode                | -                     | 16                    |      |

| f <sub>SCK</sub><br>1/t <sub>c(SCK)</sub>                                  | SPI clock frequency              | Slave mode                 | -                     | 16                    | MHz  |

| ~~C(SCK)                                                                   |                                  | Slave transmitter          | -                     | 12 <sup>(3)</sup>     |      |

| $t_{r(SCK)}^{(2)}$<br>$t_{f(SCK)}^{(2)}$                                   | SPI clock rise and fall time     | Capacitive load: C = 30 pF | -                     | 6                     | ns   |

| DuCy(SCK)                                                                  | SPI slave input clock duty cycle | Slave mode                 | 30                    | 70                    | %    |

| t <sub>su(NSS)</sub>                                                       | NSS setup time                   | Slave mode                 | 4t <sub>HCLK</sub>    | -                     |      |

| t <sub>h(NSS)</sub>                                                        | NSS hold time                    | Slave mode                 | 2t <sub>HCLK</sub>    | -                     |      |

| t <sub>w(SCKH)</sub> <sup>(2)</sup><br>t <sub>w(SCKL)</sub> <sup>(2)</sup> | SCK high and low time            | Master mode                | t <sub>SCK</sub> /2-5 | t <sub>SCK</sub> /2+3 |      |

| $t_{su(MI)}^{(2)}$                                                         | - Data input setup time          | Master mode                | 5                     | -                     |      |

| t <sub>su(SI)</sub> <sup>(2)</sup>                                         | - Data input setup time          | Slave mode                 | 6                     | -                     |      |

| t <sub>h(MI)</sub> <sup>(2)</sup>                                          | Data input hold time             | Master mode                | 5                     | -                     | ns   |

| t <sub>h(SI)</sub> <sup>(2)</sup>                                          | Data input hold time             | Slave mode                 | 5                     | -                     |      |

| t <sub>a(SO)</sub> <sup>(4)</sup>                                          | Data output access time          | Slave mode                 | 0                     | 3t <sub>HCLK</sub>    |      |

| t <sub>v(SO)</sub> (2)                                                     | Data output valid time           | Slave mode                 | -                     | 33                    |      |

| t <sub>v(MO)</sub> <sup>(2)</sup>                                          | Data output valid time           | Master mode                | -                     | 6.5                   |      |

| t <sub>h(SO)</sub> <sup>(2)</sup>                                          | Data output hold time            | Slave mode                 | 17                    | -                     |      |

| t <sub>h(MO)</sub> <sup>(2)</sup>                                          | - Data output noid time          | Master mode                | 0.5                   | -                     |      |

Table 50. SPI characteristics<sup>(1)</sup>

1. The characteristics above are given for voltage range 1.

2. Guaranteed by characterization results.

The maximum SPI clock frequency in slave transmitter mode is given for an SPI slave input clock duty cycle (DuCy(SCK)) ranging between 40 to 60%.

4. Min time is for the minimum time to drive the output and max time is for the maximum time to validate the data.

| Symbol                          | Parameter                                          | Conditions                                             | Min                                                        | Тур | Max     | Unit               |  |

|---------------------------------|----------------------------------------------------|--------------------------------------------------------|------------------------------------------------------------|-----|---------|--------------------|--|

|                                 |                                                    | Direct channels<br>2.4 V ≤V <sub>DDA</sub> ≤3.6 V      | 0.25                                                       | -   | -       |                    |  |

|                                 |                                                    | Multiplexed channels<br>2.4 V ≤V <sub>DDA</sub> ≤3.6 V | 0.56                                                       | -   | -       |                    |  |

| t <sub>S</sub> <sup>(5)</sup>   | Sampling time                                      | Direct channels<br>1.8 V ≤V <sub>DDA</sub> ≤2.4 V      | 0.56                                                       | -   | -       | μs                 |  |

|                                 |                                                    | Multiplexed channels<br>1.8 V ≤V <sub>DDA</sub> ≤2.4 V | 1                                                          | -   | -       |                    |  |

|                                 |                                                    | -                                                      | 4                                                          | -   | 384     | 1/f <sub>ADC</sub> |  |

|                                 | Total conversion time                              | f <sub>ADC</sub> = 16 MHz                              | 1                                                          | -   | 24.75   | μs                 |  |

| t <sub>CONV</sub>               | Total conversion time<br>(including sampling time) | -                                                      | 4 to 384 (sampling phase) +1<br>(successive approximation) |     |         | 1/f <sub>ADC</sub> |  |

| o Inter                         | nternal sample and hold                            | Direct channels                                        | -                                                          | 16  | -       | рF                 |  |

| C <sub>ADC</sub>                | capacitor                                          | Multiplexed channels                                   | -                                                          | 10  | -       |                    |  |

| f                               | External trigger frequency                         | 12-bit conversions                                     | -                                                          | -   | Tconv+1 | 1/f <sub>ADC</sub> |  |

| f <sub>TRIG</sub>               | Regular sequencer                                  | 6/8/10-bit conversions                                 | -                                                          | -   | Tconv   | 1/f <sub>ADC</sub> |  |

| £                               | External trigger frequency                         | 12-bit conversions                                     | -                                                          | -   | Tconv+2 | 1/f <sub>ADC</sub> |  |

| f <sub>TRIG</sub>               | Injected sequencer                                 | 6/8/10-bit conversions                                 | -                                                          | -   | Tconv+1 | 1/f <sub>ADC</sub> |  |

| R <sub>AIN</sub> <sup>(6)</sup> | Signal source impedance                            |                                                        | -                                                          | -   | 50      | kΩ                 |  |

| +                               | Injection trigger conversion                       | f <sub>ADC</sub> = 16 MHz                              | 219                                                        | -   | 281     | ns                 |  |

| t <sub>lat</sub>                | latency                                            | -                                                      | 3.5                                                        | -   | 4.5     | 1/f <sub>ADC</sub> |  |

| t.                              | Regular trigger conversion                         | f <sub>ADC</sub> = 16 MHz                              | 156                                                        | -   | 219     | ns                 |  |

|                                 | latency                                            | -                                                      | 2.5                                                        | -   | 3.5     | 1/f <sub>ADC</sub> |  |

| t <sub>STAB</sub>               | Power-up time                                      | -                                                      | -                                                          | -   | 3.5     | μs                 |  |

## Table 56. ADC characteristics (continued)

1. The Vref+ input can be grounded if neither the ADC nor the DAC are used (this allows to shut down an external voltage reference).

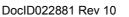

2. The current consumption through VREF is composed of two parameters:

- one constant (max 300 µA)

- one variable (max 400  $\mu A$ ), only during sampling time + 2 first conversion pulses

So, peak consumption is 300+400 = 700  $\mu A$  and average consumption is 300 + [(4 sampling + 2) /16] x 400 = 450  $\mu A$  at 1Msps

V<sub>REF+</sub> can be internally connected to V<sub>DDA</sub> and V<sub>REF-</sub> can be internally connected to V<sub>SSA</sub>, depending on the package. Refer to Section 4: Pin descriptions for further details.

4.  $V_{SSA}$  or  $V_{REF-}$  must be tied to ground.

5. Minimum sampling time is reached for an external input impedance limited to a value as defined in *Table 58: Maximum source impedance RAIN max*.

6. External impedance has another high value limitation when using short sampling time as defined in *Table 58: Maximum source impedance RAIN max*.

# Figure 27. Maximum dynamic current consumption on V<sub>REF+</sub> supply pin during ADC conversion

## Table 58. Maximum source impedance $R_{AIN} max^{(1)}$

| Ts<br>(µs) | Multiplexe                       | d channels                       | Direct channels                  |                                  | Ts (cycles)<br>f <sub>ADC</sub> =16 MHz <sup>(2)</sup> |  |

|------------|----------------------------------|----------------------------------|----------------------------------|----------------------------------|--------------------------------------------------------|--|

|            | 2.4 V < V <sub>DDA</sub> < 3.6 V | 1.8 V < V <sub>DDA</sub> < 2.4 V | 2.4 V < V <sub>DDA</sub> < 3.6 V | 1.8 V < V <sub>DDA</sub> < 2.4 V | ADC                                                    |  |

| 0.25       | Not allowed                      | Not allowed                      | 0.7                              | Not allowed                      | 4                                                      |  |

| 0.5625     | 0.8                              | Not allowed                      | 2.0                              | 1.0                              | 9                                                      |  |

| 1          | 2.0                              | 0.8                              | 4.0                              | 3.0                              | 16                                                     |  |

| 1.5        | 3.0                              | 1.8                              | 6.0                              | 4.5                              | 24                                                     |  |

| 3          | 6.8                              | 4.0                              | 15.0                             | 10.0                             | 48                                                     |  |

| 6          | 15.0                             | 10.0                             | 30.0                             | 20.0                             | 96                                                     |  |

| 12         | 32.0                             | 25.0                             | 50.0                             | 40.0                             | 192                                                    |  |

| 24         | 50.0                             | 50.0                             | 50.0                             | 50.0                             | 384                                                    |  |

1. Guaranteed by design.

2. Number of samples calculated for  $f_{ADC}$  = 16 MHz. For  $f_{ADC}$  = 8 and 4 MHz the number of sampling cycles can be reduced with respect to the minimum sampling time Ts (µs),

### **General PCB design guidelines**

Power supply decoupling should be performed as shown in *Figure 9*. The applicable procedure depends on whether  $V_{REF+}$  is connected to  $V_{DDA}$  or not. The 100 nF capacitors should be ceramic (good quality). They should be placed as close as possible to the chip.

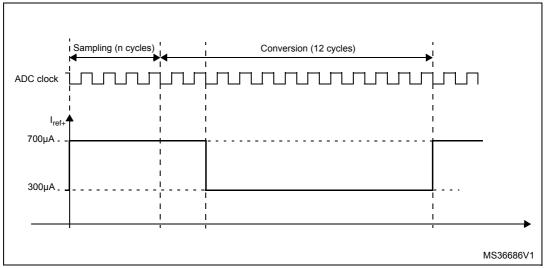

# 6.3.18 DAC electrical specifications

Data guaranteed by design, unless otherwise specified.

| Symbol                              | Parameter                                             | Conditions                                                                     | Min              | Тур  | Max                         | Unit |

|-------------------------------------|-------------------------------------------------------|--------------------------------------------------------------------------------|------------------|------|-----------------------------|------|

| V <sub>DDA</sub>                    | Analog supply voltage                                 | -                                                                              | 1.8              | -    | 3.6                         |      |

| V <sub>REF+</sub>                   | Reference supply voltage                              | V <sub>REF+</sub> must always be below<br>V <sub>DDA</sub>                     | 1.8              | -    | 3.6                         | V    |

| V <sub>REF-</sub>                   | Lower reference voltage                               | -                                                                              | V <sub>SSA</sub> |      |                             |      |

| . (1)                               | Current consumption on                                | No load, middle code (0x800)                                                   | -                | 130  | 220                         |      |

| I <sub>DDVREF+</sub> <sup>(1)</sup> | V <sub>REF+</sub> supply<br>V <sub>REF+</sub> = 3.3 V | No load, worst code (0x000)                                                    | -                | 220  | 350                         |      |

| (1)                                 | Current consumption on                                | No load, middle code (0x800)                                                   | -                | 210  | 320                         | μA   |

| I <sub>DDA</sub> <sup>(1)</sup>     | V <sub>DDA</sub> supply<br>V <sub>DDA</sub> = 3.3 V   | No load, worst code (0xF1C)                                                    | -                | 320  | 520                         |      |

| $R_L^{(2)}$                         | Resistive load                                        |                                                                                | 5                | -    | -                           | kΩ   |

| C <sub>L</sub> <sup>(2)</sup>       | Capacitive load                                       | DAC output buffer ON                                                           | -                | -    | 50                          | pF   |

| R <sub>O</sub>                      | Output impedance                                      | DAC output buffer OFF                                                          | 12               | 16   | 20                          | kΩ   |

| V <sub>DAC_OUT</sub>                | Voltage on DAC_OUT<br>output                          | DAC output buffer ON                                                           | 0.2              | -    | V <sub>DDA</sub> – 0.2      | V    |

|                                     |                                                       | DAC output buffer OFF                                                          | 0.5              | -    | V <sub>REF+</sub> –<br>1LSB | mV   |

| DNL <sup>(1)</sup>                  | Differential non                                      | $C_{L} \le 50 \text{ pF}, R_{L} \ge 5 \text{ k}\Omega$<br>DAC output buffer ON | -                | 1.5  | 3                           |      |

|                                     | linearity <sup>(3)</sup>                              | No R <sub>L</sub> , C <sub>L</sub> $\leq$ 50 pF<br>DAC output buffer OFF       | -                | 1.5  | 3                           |      |

| INL <sup>(1)</sup>                  | Integral non linearity <sup>(4)</sup>                 | $C_{L} \le 50 \text{ pF}, R_{L} \ge 5 \text{ k}\Omega$<br>DAC output buffer ON | -                | 2    | 4                           | -    |

| INL                                 | Integral non linearity <sup>(4)</sup>                 | No $R_L$ , $C_L \le 50 \text{ pF}$<br>DAC output buffer OFF                    | -                | 2    | 4                           | LSB  |

| Offset <sup>(1)</sup>               | Offset error at code                                  | $C_{L} \le 50 \text{ pF}, R_{L} \ge 5 \text{ k}\Omega$<br>DAC output buffer ON | -                | ±10  | ±25                         | ]    |

|                                     | 0x800 <sup>(5)</sup>                                  | No R <sub>L</sub> , C <sub>L</sub> ≤50 pF<br>DAC output buffer OFF             | -                | ±5   | ±8                          |      |

| Offset1 <sup>(1)</sup>              | Offset error at code 0x001 <sup>(6)</sup>             | No $R_L$ , $C_L \le 50 \text{ pF}$<br>DAC output buffer OFF                    | -                | ±1.5 | ±5                          |      |

- 4. Difference between measured value at Code i and the value at Code i on a line drawn between Code 0 and last Code 4095.

- 5. Difference between the value measured at Code (0x800) and the ideal value =  $V_{REF+}/2$ .

- 6. Difference between the value measured at Code (0x001) and the ideal value.

- 7. Difference between ideal slope of the transfer function and measured slope computed from code 0x000 and 0xFFF when buffer is OFF, and from code giving 0.2 V and ( $V_{DDA} 0.2$ ) V when buffer is ON.

- 8. In buffered mode, the output can overshoot above the final value for low input code (starting from min value).

The DAC integrates an output buffer that can be used to reduce the output impedance and to drive external loads directly without the use of an external operational amplifier. The buffer can be bypassed by configuring the BOFFx bit in the DAC\_CR register.

## 6.3.19 Operational amplifier characteristics

| Symbol               | Para                 | neter                     | Condition <sup>(1)</sup> | Min <sup>(2)</sup> | Тур | Max <sup>(2)</sup> | Unit  |  |

|----------------------|----------------------|---------------------------|--------------------------|--------------------|-----|--------------------|-------|--|

| CMIR                 | Common mode inpu     | ut range                  | -                        | 0                  | -   | V <sub>DD</sub>    |       |  |

|                      | Input offset voltage | Maximum calibration range | -                        | -                  | -   | ±15                |       |  |

| VI <sub>OFFSET</sub> |                      | After offset calibration  | -                        | -                  | -   | ±1.5               | mV    |  |

| A)/I                 | Input offset voltage | Normal mode               | -                        | -                  | -   | ±40                | µV/°C |  |

| $\Delta VI_{OFFSET}$ | drift                | Low-power mode            | -                        | -                  | -   | ±80                |       |  |

|                      | Input current bias   | Dedicated input           |                          | -                  | -   | 1                  |       |  |

| I <sub>IB</sub>      |                      | General purpose input     |                          | -                  | -   | 10                 | nA    |  |

|                      |                      | Normal mode               | -                        | -                  | -   | 500                |       |  |

| ILOAD                | Drive current        | Low-power mode            | -                        | -                  | -   | 100                | μA    |  |

|                      | Concurrentian        | Normal mode               | No load,                 | -                  | 100 | 220                |       |  |

| I <sub>DD</sub>      | Consumption          | Low-power mode            | quiescent mode           | -                  | 30  | 60                 | μA    |  |

| CMDD                 | Common mode          | Normal mode               | -                        | -                  | -85 | -                  | dB    |  |

| CMRR                 | rejection ration     | Low-power mode            | -                        | -                  | -90 | -                  |       |  |

#### Table 60. Operational amplifier characteristics

# 6.3.20 Temperature sensor characteristics

| Calibration value name | Description                                                                                                   | Memory address            |

|------------------------|---------------------------------------------------------------------------------------------------------------|---------------------------|

| TS_CAL1                | TS ADC raw data acquired at temperature of 30 °C $\pm$ 5 °C V <sub>DDA</sub> = 3 V $\pm$ 10 mV                | 0x1FF8 00FA - 0x1FF8 00FB |

| TS_CAL2                | TS ADC raw data acquired at temperature of 110 $^{\circ}C \pm 5 ^{\circ}C$ V <sub>DDA</sub> = 3 V $\pm 10$ mV | 0x1FF8 00FE - 0x1FF8 00FF |

#### Table 61. Temperature sensor calibration values

#### Table 62. Temperature sensor characteristics

| Symbol                                | Parameter                                      | Min  | Тур   | Мах   | Unit  |

|---------------------------------------|------------------------------------------------|------|-------|-------|-------|

| T <sub>L</sub> <sup>(1)</sup>         | V <sub>SENSE</sub> linearity with temperature  | -    | ±1    | ±2    | °C    |

| Avg_Slope <sup>(1)</sup>              | Average slope                                  | 1.48 | 1.61  | 1.75  | mV/°C |

| V <sub>110</sub>                      | Voltage at 110°C ±5°C <sup>(2)</sup>           | 612  | 626.8 | 641.5 | mV    |

| I <sub>DDA(TEMP)</sub> <sup>(3)</sup> | Current consumption                            | -    | 3.4   | 6     | μA    |

| t <sub>START</sub> <sup>(3)</sup>     | Startup time                                   | -    | -     | 10    |       |

| T <sub>S_temp</sub> <sup>(3)</sup>    | ADC sampling time when reading the temperature | 4    | -     | -     | μs    |

1. Guaranteed by characterization results.

2. Measured at V\_{DD} = 3 V  $\pm$ 10 mV. V110 ADC conversion result is stored in the TS\_CAL2 byte.

3. Guaranteed by design.

## 6.3.21 Comparator

| Symbol                   | Parameter                                                            | Conditions                                                                | Min <sup>(1)</sup> | Тур | Max <sup>(1)</sup> | Unit      |

|--------------------------|----------------------------------------------------------------------|---------------------------------------------------------------------------|--------------------|-----|--------------------|-----------|

| V <sub>DDA</sub>         | Analog supply voltage                                                | -                                                                         | 1.65               |     | 3.6                | V         |

| R <sub>400K</sub>        | R <sub>400K</sub> value                                              | -                                                                         | -                  | 400 | -                  | kΩ        |

| R <sub>10K</sub>         | R <sub>10K</sub> value                                               | -                                                                         | -                  | 10  | -                  | N32       |

| V <sub>IN</sub>          | Comparator 1 input<br>voltage range                                  | -                                                                         | 0.6                | -   | V <sub>DDA</sub>   | V         |

| t <sub>START</sub>       | Comparator startup time                                              | -                                                                         | -                  | 7   | 10                 | 116       |

| td                       | Propagation delay <sup>(2)</sup>                                     | -                                                                         | -                  | 3   | 10                 | μs        |

| Voffset                  | Comparator offset                                                    | -                                                                         | -                  | ±3  | ±10                | mV        |

| d <sub>Voffset</sub> /dt | Comparator offset<br>variation in worst voltage<br>stress conditions | $V_{DDA} = 3.6 V$ $V_{IN+} = 0 V$ $V_{IN-} = V_{REFINT}$ $T_{A} = 25 ° C$ | 0                  | 1.5 | 10                 | mV/1000 h |

| I <sub>COMP1</sub>       | Current consumption <sup>(3)</sup>                                   | -                                                                         | -                  | 160 | 260                | nA        |

Table 63. Comparator 1 characteristics

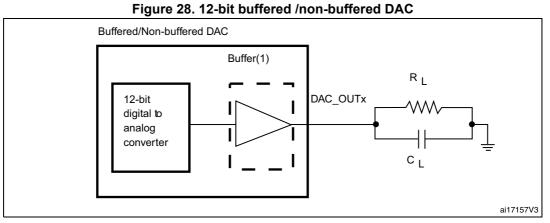

### Marking of engineering samples

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Figure 31. LQFP100, 14 x 14 mm, 100-pin low-profile quad flat package top view example

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity

| Symbol |     | millimeters |       | inches <sup>(1)</sup> |     |        |

|--------|-----|-------------|-------|-----------------------|-----|--------|

| Symbol | Min | Тур         | Мах   | Min                   | Тур | Max    |

| eee    | -   | -           | 0.150 | -                     | -   | 0.0059 |

| fff    | -   | -           | 0.050 | -                     | -   | 0.0020 |

#### Table 68. UFBGA100, 7 x 7 mm, 0.5 mm pitch package mechanical data (continued)

1. Values in inches are converted from mm and rounded to 4 decimal digits.

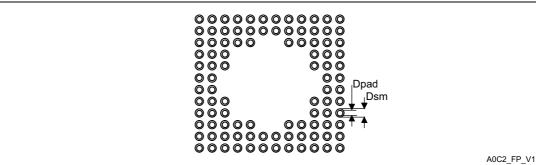

#### Figure 36. UFBGA100, 7 x 7 mm, 0.5 mm pitch, package recommended footprint

#### Table 69. UFBGA100, 7 x 7 mm, 0.50 mm pitch, recommended PCB design rules

| Dimension         | Recommended values                                               |

|-------------------|------------------------------------------------------------------|

| Pitch             | 0.5                                                              |

| Dpad              | 0.280 mm                                                         |

| Dsm               | 0.370 mm typ. (depends on the soldermask registration tolerance) |

| Stencil opening   | 0.280 mm                                                         |

| Stencil thickness | Between 0.100 mm and 0.125 mm                                    |

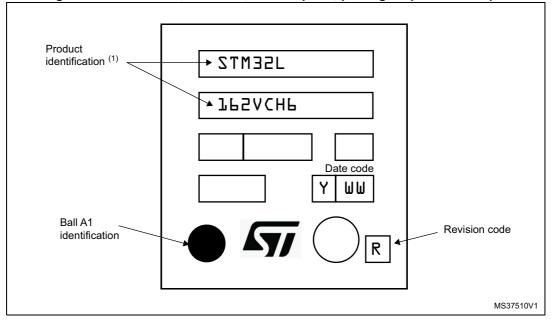

### Marking of engineering samples

The following figure gives an example of topside marking orientation versus ball A1 identifier location.

Figure 37. UFBGA100, 7 x 7 mm, 0.5 mm pitch, package top view example

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity

# STM32L162VC, STM32L162RC

|             | Table 72. Document revision history (continued) |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

|-------------|-------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Date        | Revision                                        | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| 19-May-2014 | 6<br>(continued)                                | Updated <i>Table 48: I2C characteristics.</i><br>Removed minimum values for $f_S$ in <i>Table 56: ADC characteristics.</i><br>Updated Output impedance values in <i>Table 59: DAC characteristics.</i><br>Moved <i>Table 61: Temperature sensor calibration values</i> from<br><i>Section 3.10.1: Temperature sensor to Section 6.3.20: Temperature</i><br><i>sensor characteristics</i> and updated the table. Removed note 4 in<br><i>Table 62: Temperature sensor characteristics.</i><br>Modified <i>General PCB design guidelines.</i><br>Removed figures "Power supply and reference decoupling (V <sub>REF+</sub> not<br>connected to V <sub>DDA</sub> ) and "Power supply and reference decoupling<br>(V <sub>REF+</sub> connected to V <sub>DDA</sub> )".<br>Updated <i>Figure 26: Typical connection diagram using the ADC.</i><br>Added "Marking of engineering samples" sections in <i>Figure : In order</i><br><i>to meet environmental requirements, ST offers these devices in</i><br><i>different grades of ECOPACK® packages, depending on their level of</i><br><i>environmental compliance. ECOPACK® specifications, grade</i><br><i>definitions and product status are available at: www.st.com.</i><br><i>ECOPACK® is an ST trademark</i><br>Updated the conditions in <i>Table 26: Low-power mode wakeup timings.</i><br>Removed ambiguity of "ambient temperature" in the electrical<br><i>characteristics description.</i> |  |  |  |

| 13-Oct-2014 | 7                                               | Updated Section 3.18: Communication interfaces putting I2S<br>characteristics inside.<br>Updated DMIPS features in cover page and Section 2: Description.<br>Updated max temperature at 105°C instead of 85°C in the whole<br>datasheet.<br>Updated Table 9: STM32L162xC pin definitions with additional<br>functions column.<br>Updated current consumption in Table 20: Current consumption in<br>Sleep mode.<br>Updated Table 25: Peripheral current consumption with new measured<br>current values.<br>Updated Table 58: Maximum source impedance RAIN max adding<br>note 2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| 06-Mar-2015 | 8                                               | Updated Section 7: Package information with new package device marking.<br>Updated Figure 6: Memory map.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| Table 72. | Document revis | ion historv | (continued) |

|-----------|----------------|-------------|-------------|

|           | Document revis |             | (continued) |