Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                      |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 72MHz                                                                 |

| Connectivity               | FlexIO, I <sup>2</sup> C, SPI, UART/USART                             |

| Peripherals                | DMA, LVD, PWM, WDT                                                    |

| Number of I/O              | 89                                                                    |

| Program Memory Size        | 128KB (128K x 8)                                                      |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | 34K x 8                                                               |

| RAM Size                   | 16K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                           |

| Data Converters            | A/D 16x12b; D/A 1x8b                                                  |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 100-LQFP                                                              |

| Supplier Device Package    | 100-LQFP (14x14)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mke14z128vll7 |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

rights for each transaction routed to the on-chip flash memory. Configurability allows an increasing number of protected segments while supporting two levels of vendors adding their proprietary software to a device.

# 2.1.8 Power management

The Power Management Controller (PMC) expands upon ARM's operational modes of Run, Sleep, and Deep Sleep, to provide multiple configurable modes. These modes can be used to optimize current consumption for a wide range of applications. The WFI or WFE instruction invokes a Wait or a Stop mode, depending on the current configuration. For more information on ARM's operational modes, See the ARM<sup>®</sup> Cortex<sup>®</sup> User Guide.

The PMC provides Normal Run (RUN), and Very Low Power Run (VLPR) configurations in ARM's Run operation mode. In these modes, the MCU core is active and can access all peripherals. The difference between the modes is the maximum clock frequency of the system and therefore the power consumption. The configuration that matches the power versus performance requirements of the application can be selected.

The PMC provides Wait (Wait) and Very Low Power Wait (VLPW) configurations in ARM's Sleep operation mode. In these modes, even though the MCU core is inactive, all of the peripherals can be enabled and operate as programmed. The difference between the modes is the maximum clock frequency of the system and therefore the power consumption.

The PMC provides Stop (Stop), Very Low Power Stop (VLPS) configurations in ARM's Deep Sleep operational mode. In these modes, the MCU core and most of the peripherals are disabled. Depending on the requirements of the application, different portions of the analog, logic, and memory can be retained or disabled to conserve power.

The Nested Vectored Interrupt Controller (NVIC), the Asynchronous Wake-up Interrupt Controller (AWIC) are used to wake up the MCU from low power states. The NVIC is used to wake up the MCU core from WAIT and VLPW modes. The AWIC is used to wake up the MCU core from STOP and VLPS modes.

For additional information regarding operational modes, power management, the NVIC, AWIC, please refer to the Reference Manual.

The following table provides information about the state of the peripherals in the various operational modes and the modules that can wake MCU from low power modes.

| Core mode  | Device mode         | Descriptions                                                                                                                                                                                                                                                                                                                           |

|------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Run mode   | Run                 | In Run mode, all device modules are operational.                                                                                                                                                                                                                                                                                       |

|            | Very Low Power Run  | In VLPR mode, all device modules are operational at a reduced frequency except the Low Voltage Detect (LVD) monitor, which is disabled.                                                                                                                                                                                                |

| Sleep mode | Wait                | In Wait mode, all peripheral modules are operational. The MCU core is placed into Sleep mode.                                                                                                                                                                                                                                          |

|            | Very Low Power Wait | In VLPW mode, all peripheral modules are operational at a reduced frequency except the Low Voltage Detect (LVD) monitor, which is disabled. The MCU core is placed into Sleep mode.                                                                                                                                                    |

| Deep sleep | Stop                | In Stop mode, most peripheral clocks are disabled and placed in a static state. Stop mode retains all registers and SRAMs while maintaining Low Voltage Detection protection. In Stop mode, the ADC, CMP, LPTMR, RTC, and pin interrupts are operational. The NVIC is disabled, but the AWIC can be used to wake up from an interrupt. |

|            | Very Low Power Stop | In VLPS mode, the contents of the SRAM are retained. The CMP (low speed), ADC, OSC, RTC, LPTMR, LPIT, FlexIO, LPUART, LPI2C,LPSPI, and DMA are operational, LVD and NVIC are disabled, AWIC is used to wake up from interrupt.                                                                                                         |

Table 5.

Peripherals states in different operational modes

# 2.1.9 Debug controller

This device has extensive debug capabilities including run control and tracing capabilities. The standard ARM debug port supports SWD interface.

# 2.2 Peripheral features

The following sections describe the features of each peripherals of the chip.

# 2.2.1 eDMA and DMAMUX

The eDMA is a highly programmable data-transfer engine optimized to minimize any required intervention from the host processor. It is intended for use in applications where the data size to be transferred is statically known and not defined within the transferred data itself. The DMA controller in this device implements 8 channels which can be routed from up to 63 DMA request sources through DMA MUX module.

Main features of eDMA are listed below:

- Single or continuous conversion

- Configurable sample time and conversion speed/power

- Input clock selectable from up to four sources

- Operation in low-power modes for lower noise

- Selectable hardware conversion trigger

- Automatic compare with interrupt for less-than, greater-than or equal-to, within range, or out-of-range, programmable value

- Temperature sensor

- Hardware average function

- Selectable Voltage reference: from external or alternate

- Self-Calibration mode

## 2.2.3.1 Temperature sensor

This device contains one temperature sensor internally connected to the input channel of AD26, see ADC electrical characteristics for details of the linearity factor.

The sensor must be calibrated to gain good accuracy, so as to provide good linearity, see also AN3031 for more detailed application information of the temperature sensor.

# 2.2.4 CMP

There are two analog comparators on this device.

- Each CMP has its own independent 8-bit DAC.

- Each CMP supports up to 6 analog inputs from external pins.

- Each CMP is able to convert an internal reference from the bandgap.

- Each CMP supports the round-robin sampling scheme. In summary, this allow the CMP to operate independently in VLPS and Stop modes, whilst being triggered periodically to sample up to 8 inputs. Only if an input changes state is a full wakeup generated.

The CMP has the following features:

- Inputs may range from rail to rail

- Programmable hysteresis control

- Selectable interrupt on rising-edge, falling-edge, or both rising and falling edges of the comparator output

- Selectable inversion on comparator output

- Capability to produce a wide range of outputs such as sampled, windowed, or digitally filtered

# 2.2.7 PDB

The Programmable Delay Block (PDB) provides controllable delays from either an internal or an external trigger, or a programmable interval tick, to the hardware trigger inputs of ADCs and/or generates the interval triggers to DACs, so that the precise timing between ADC conversions and/or DAC updates can be achieved. The PDB can optionally provide pulse outputs (Pulse-Out's) that are used as the sample window in the CMP block.

The PDB module has the following capabilities:

- trigger input sources and one software trigger source

- 1 DAC refresh trigger output, for this device

- configurable PDB channels for ADC hardware trigger

- 1 pulse output, for this device

# 2.2.8 LPTMR

The low-power timer (LPTMR) can be configured to operate as a time counter with optional prescaler, or as a pulse counter with optional glitch filter, across all power modes, including the low-leakage modes. It can also continue operating through most system reset events, allowing it to be used as a time of day counter.

The LPTMR module has the following features:

- 16-bit time counter or pulse counter with compare

- Optional interrupt can generate asynchronous wakeup from any low-power mode

- Hardware trigger output

- Counter supports free-running mode or reset on compare

- Configurable clock source for prescaler/glitch filter

- Configurable input source for pulse counter

# 2.2.9 CRC

This device contains one cyclic redundancy check (CRC) module which can generate 16/32-bit CRC code for error detection.

The CRC module provides a programmable polynomial, WAS, and other parameters required to implement a 16-bit or 32-bit CRC standard.

The CRC module has the following features:

#### Overview

- Hardware CRC generator circuit using a 16-bit or 32-bit programmable shift register

- Programmable initial seed value and polynomial

- Option to transpose input data or output data (the CRC result) bitwise or bytewise.

- Option for inversion of final CRC result

- 32-bit CPU register programming interface

# 2.2.10 LPUART

This product contains three Low-Power UART modules, and can work in Stop and VLPS modes. The module also supports  $4 \times$  to  $32 \times$  data oversampling rate to meet different applications.

The LPUART module has the following features:

- Programmable baud rates (13-bit modulo divider) with configurable oversampling ratio from  $4 \times$  to  $32 \times$

- Transmit and receive baud rate can operate asynchronous to the bus clock and can be configured independently of the bus clock frequency, support operation in Stop mode

- Interrupt, DMA or polled operation

- Hardware parity generation and checking

- Programmable 8-bit, 9-bit or 10-bit character length

- Programmable 1-bit or 2-bit stop bits

- Three receiver wakeup methods

- Idle line wakeup

- Address mark wakeup

- Receive data match

- Automatic address matching to reduce ISR overhead:

- Address mark matching

- Idle line address matching

- Address match start, address match end

- Optional 13-bit break character generation / 11-bit break character detection

- Configurable idle length detection supporting 1, 2, 4, 8, 16, 32, 64 or 128 idle characters

- Selectable transmitter output and receiver input polarity

# 3 Memory map

This device contains various memories and memory-mapped peripherals which are located in a 4 GB memory space. For more details of the system memory and peripheral locations, see the Memory Map chapter in the Reference Manual.

# 4.3.1 Core Modules

| Table | 7. SWD Signal Descriptions |

|-------|----------------------------|

|       |                            |

| Chip signal name | Module signal<br>name | Description       | I/O |

|------------------|-----------------------|-------------------|-----|

| SWD_CLK          | SWD_CLK               | Serial Wire Clock | Ι   |

| SWD_DIO          | SWD_DIO               | Serial Wire Data  | I/O |

# 4.3.2 System Modules

### Table 8. System Signal Descriptions

| Chip signal name | Module signal<br>name | Description                                                                                                                                              | I/O |

|------------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| NMI_b            | _                     | Non-maskable interrupt NOTE: Driving the NMI signal low forces<br>a non-maskable interrupt, if the NMI function is selected on the<br>corresponding pin. | I   |

| RESET_b          | —                     | Reset bidirectional signal                                                                                                                               | I/O |

| VDD              |                       | MCU power                                                                                                                                                | I   |

| VSS              | _                     | MCU ground                                                                                                                                               | I   |

### Table 9. EWM Signal Descriptions

| Chip signal name | Module signal<br>name | Description                                                                                                                                                        | I/O |

|------------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| EWM_IN           | EWM_in                | EWM input for safety status of external safety circuits. The polarity of EWM_IN is programmable using the EWM_CTRL[ASSIN] bit. The default polarity is active-low. | Ι   |

| EWM_OUT_b        | EWM_out               | EWM reset out signal                                                                                                                                               | 0   |

# 4.3.3 Clock Modules

### Table 10. OSC (in SCG) Signal Descriptions

| Chip<br>signal<br>name | Module signal name | Description                     | I/O |

|------------------------|--------------------|---------------------------------|-----|

| EXTAL                  | EXTAL              | External clock/Oscillator input | I   |

| XTAL                   | XTAL               | Oscillator output               | 0   |

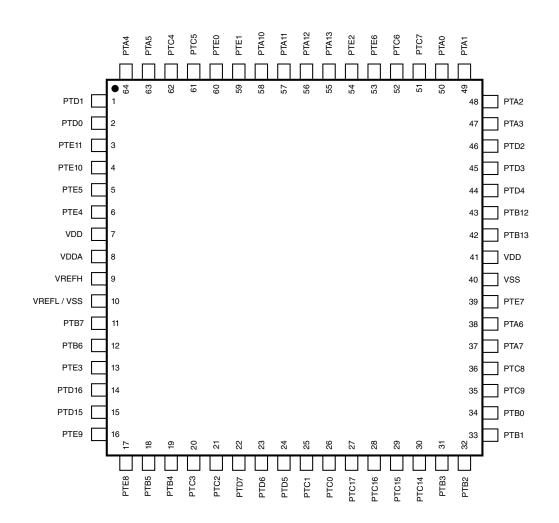

Figure 8. 64 LQFP Pinout Diagram

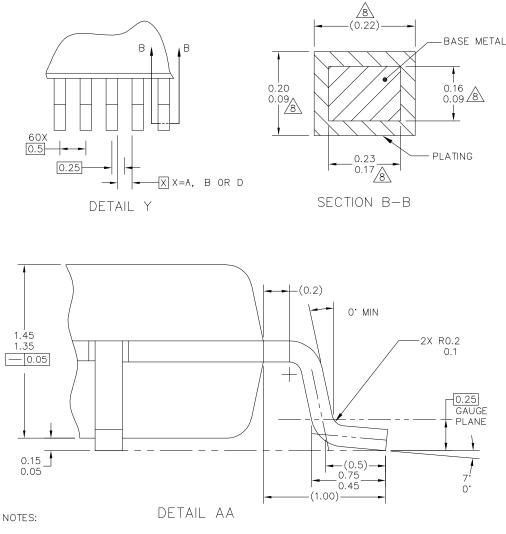

# 4.5 Package dimensions

The following figures show the dimensions of the package options for the devices supported by this document.

#### **Pinouts**

1. DIMENSIONS ARE IN MILLIMETERS.

2. DIMENSIONING AND TOLERANCING PER ASME Y14.5M-1994.

$\boxed{3}$  datums a, b and d to be determined at datum plane H.

$\overline{/4.}$  dimensions to be determined at seating plane c.

- THIS DIMENSION DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL NOT CAUSE THE LEAD WIDTH TO EXCEED THE UPPER LIMIT BY MORE THAN 0.08 MM AT MAXIMUM MATERIAL CONDITION. DAMBAR CANNOT BE LOCATED ON THE LOWER RADIUS OR THE FOOT. MINIMUM SPACE BETWEEN PROTRUSION AND ADJACENT LEAD SHALL NOT BE LESS THAN 0.07 MM.

- 6. THIS DIMENSION DOES NOT INCLUDE MOLD PROTRUSION. ALLOWABLE PROTRUSION IS 0.25 MM PER SIDE. THIS DIMENSION IS MAXIMUM PLASTIC BODY SIZE DIMENSION INCLUDING MOLD MISMATCH.

(7) EXACT SHAPE OF EACH CORNER IS OPTIONAL.

A THESE DIMENSIONS APPLY TO THE FLAT SECTION OF THE LEAD BETWEEN 0.1 MM AND 0.25 MM FROM THE LEAD TIP.

#### Figure 12. 64-pin LQFP package dimensions 2

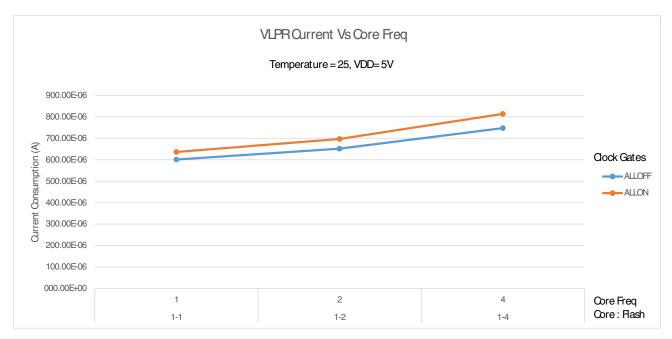

Figure 15. VLPR mode supply current vs. core frequency

# 5.3.1.7 EMC performance

Electromagnetic compatibility (EMC) performance is highly dependent on the environment in which the MCU resides. Board design and layout, circuit topology choices, location and characteristics of external components, and MCU software operation play a significant role in the EMC performance. The system designer can consult the following applications notes, available on http://www.nxp.com for advice and guidance specifically targeted at optimizing EMC performance.

- AN2321: Designing for Board Level Electromagnetic Compatibility

- AN1050: Designing for Electromagnetic Compatibility (EMC) with HCMOS Microcontrollers

- AN1263: Designing for Electromagnetic Compatibility with Single-Chip Microcontrollers

- AN2764: Improving the Transient Immunity Performance of Microcontroller-Based Applications

- AN1259: System Design and Layout Techniques for Noise Reduction in MCU-Based Systems

### 5.3.1.7.1 EMC radiated emissions operating behaviors

EMC measurements to IC-level IEC standards are available from NXP on request.

### 5.3.2.4 AC specifications at 3.3 V range Table 37. Functional pad AC specifications

| Characteristic     | Symbol           | Min | Тур | Мах | Unit |

|--------------------|------------------|-----|-----|-----|------|

| I/O Supply Voltage | Vdd <sup>1</sup> | 2.7 |     | 4   | V    |

1. Max power supply ramp rate is 500 V/ms.

| Name                    | Prop Delay (ns) <sup>1</sup> | Rise/Fall Edge (ns) <sup>2</sup> |     | Drive Load (pF) |

|-------------------------|------------------------------|----------------------------------|-----|-----------------|

|                         | Max                          | Min                              | Max |                 |

| Normal drive I/O pad    | 17.5                         | 5                                | 17  | 25              |

|                         | 28                           | 9                                | 32  | 50              |

| High drive I/O pad      | 19                           | 5                                | 17  | 25              |

|                         | 26                           | 9                                | 33  | 50              |

| CMOS Input <sup>3</sup> | 4                            | 1.2                              | 3   | 0.5             |

1. Propagation delay measured from 50% of core side input to 50% of the output.

2. Edges measured using 20% and 80% of the VDD supply.

3. Input slope = 2 ns.

### NOTE

All measurements were taken accounting for 150 mV drop across VDD and VSS.

### 5.3.2.5 AC specifications at 5 V range Table 38. Functional pad AC specifications

| Characteristic     | Symbol           | Min | Тур | Max | Unit |

|--------------------|------------------|-----|-----|-----|------|

| I/O Supply Voltage | Vdd <sup>1</sup> | 4   |     | 5.5 | V    |

1. Max power supply ramp rate is 500 V/ms.

| Name                    | Prop Delay (ns) <sup>1</sup> | Rise/Fall Edge (ns) <sup>2</sup> |     | Drive Load (pF) |

|-------------------------|------------------------------|----------------------------------|-----|-----------------|

|                         | Max                          | Min                              | Мах |                 |

| Normal drive I/O pad    | 12                           | 3.6                              | 10  | 25              |

|                         | 18                           | 8                                | 17  | 50              |

| High drive I/O pad      | 13                           | 3.6                              | 10  | 25              |

|                         | 19                           | 8                                | 19  | 50              |

| CMOS Input <sup>3</sup> | 3                            | 1.2                              | 2.8 | 0.5             |

1. As measured from 50% of core side input to 50% of the output.

2. Edges measured using 20% and 80% of the VDD supply.

3. Input slope = 2 ns.

| Rating                                                                | Conditions              | Symbol            | Value | Unit |

|-----------------------------------------------------------------------|-------------------------|-------------------|-------|------|

| Thermal resistance, Junction to Ambient (@200 ft/min) <sup>1, 3</sup> | Four layer board (2s2p) | R <sub>θJMA</sub> | 37    | °C/W |

| Thermal resistance, Junction to Board <sup>4</sup>                    | _                       | R <sub>θJB</sub>  | 26    | °C/W |

| Thermal resistance, Junction to Case <sup>5</sup>                     | —                       | R <sub>θJC</sub>  | 14    | °C/W |

| Thermal resistance, Junction to Package Top <sup>6</sup>              | Natural Convection      | ΨJT               | 2     | °C/W |

### Table 40. Thermal characteristics for the 64-pin LQFP package (continued)

- 1. Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, air flow, power dissipation of other components on the board, and board thermal resistance.

- 2. Per JEDEC JESD51-2 with natural convection for horizontally oriented board. Board meets JESD51-9 specification for 1s or 2s2p board, respectively.

- 3. Per JEDEC JESD51-6 with forced convection for horizontally oriented board. Board meets JESD51-9 specification for 1s or 2s2p board, respectively.

- 4. Thermal resistance between the die and the printed circuit board per JEDEC JESD51-8. Board temperature is measured on the top surface of the board near the package.

- 5. Thermal resistance between the die and the case top surface as measured by the cold plate method (MIL SPEC-883 Method 1012.1).

- 6. Thermal characterization parameter indicating the temperature difference between package top and the junction temperature per JEDEC JESD51-2.

### 5.3.3.2.3 Thermal characteristics for the 100-pin LQFP package Table 41. Thermal characteristics for the 100-pin LQFP package

| Rating                                                                          | Conditions              | Symbol            | Value | Unit |

|---------------------------------------------------------------------------------|-------------------------|-------------------|-------|------|

| Thermal resistance, Junction to Ambient (Natural Convection) <sup>1, 2</sup>    | Single layer board (1s) | R <sub>θJA</sub>  | 59    | °C/W |

| Thermal resistance, Junction to Ambient<br>(Natural Convection) <sup>1, 2</sup> | Four layer board (2s2p) | R <sub>θJA</sub>  | 46    | °C/W |

| Thermal resistance, Junction to Ambient<br>(@200 ft/min) <sup>1, 3</sup>        | Single layer board (1s) | R <sub>θJMA</sub> | 49    | °C/W |

| Thermal resistance, Junction to Ambient<br>(@200 ft/min) <sup>1, 3</sup>        | Four layer board (2s2p) | R <sub>θJMA</sub> | 40    | °C/W |

| Thermal resistance, Junction to Board <sup>4</sup>                              | _                       | R <sub>θJB</sub>  | 31    | °C/W |

| Thermal resistance, Junction to Case <sup>5</sup>                               | —                       | R <sub>θJC</sub>  | 16    | °C/W |

| Thermal resistance, Junction to Package Top <sup>6</sup>                        | Natural Convection      | ΨJT               | 2     | °C/W |

- 1. Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, air flow, power dissipation of other components on the board, and board thermal resistance.

- 2. Per JEDEC JESD51-2 with natural convection for horizontally oriented board. Board meets JESD51-9 specification for 1s or 2s2p board, respectively.

- 3. Per JEDEC JESD51-6 with forced convection for horizontally oriented board. Board meets JESD51-9 specification for 1s or 2s2p board, respectively.

- 4. Thermal resistance between the die and the printed circuit board per JEDEC JESD51-8. Board temperature is measured on the top surface of the board near the package.

- 5. Thermal resistance between the die and the case top surface as measured by the cold plate method (MIL SPEC-883 Method 1012.1).

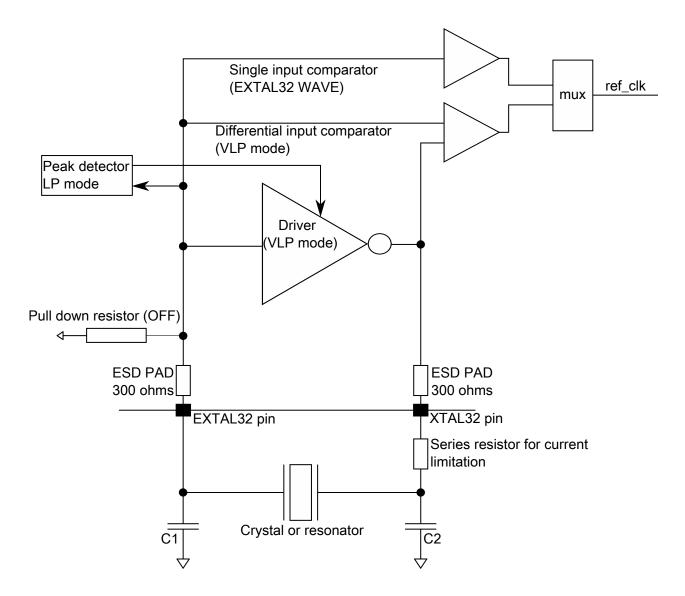

Figure 17. Oscillator connections scheme (OSC32)

| Symbol          | Description                                                           | Min.                  | Тур. | Max.                      | Unit | Notes |

|-----------------|-----------------------------------------------------------------------|-----------------------|------|---------------------------|------|-------|

| V <sub>IH</sub> | Input high voltage — EXTAL pin in external clock mode                 | 0.7 x V <sub>DD</sub> | —    | V <sub>DD</sub>           | V    |       |

| V <sub>IL</sub> | Input low voltage — EXTAL pin in external clock mode                  | V <sub>SS</sub>       | _    | 0.35 x<br>V <sub>DD</sub> | V    |       |

| C <sub>1</sub>  | EXTAL load capacitance                                                | —                     | —    | —                         |      | 2     |

| C <sub>2</sub>  | XTAL load capacitance                                                 | —                     | —    | —                         |      | 2     |

| R <sub>F</sub>  | Feedback resistor                                                     |                       |      | •                         | •    | 3     |

|                 | Low-frequency, high-gain mode (32 kHz)                                | —                     | 10   | _                         | MΩ   | 1     |

|                 | High-frequency, low-gain mode (low-power mode)<br>(4-8 MHz, 8-40 MHz) |                       | _    | -                         | MΩ   |       |

|                 | High-frequency, high-gain mode (4-8 MHz, 8-40 MHz)                    | _                     | 1    | _                         | MΩ   | 1     |

| R <sub>S</sub>  | Series resistor                                                       | ι                     |      | -                         |      |       |

|                 | Low-frequency, high-gain mode (32 kHz)                                | _                     | 200  | _                         |      |       |

|                 | High-frequency, low-gain mode (low-power mode)<br>(4-8 MHz, 8-40 MHz) | —                     | 0    | -                         | kΩ   |       |

|                 | High-frequency, high-gain mode (4-8 MHz, 8-40 MHz)                    | —                     | 0    | _                         | kΩ   | 1     |

| V <sub>pp</sub> | Peak-to-peak amplitude of oscillation (oscillator mode)               | · · · · · ·           |      | •                         |      | 4     |

|                 | Low-frequency, high-gain mode                                         | —                     | 3.3  | _                         | V    | 1     |

|                 | High-frequency, low-gain mode                                         | _                     | 1.0  | —                         | V    | 1     |

|                 | High-frequency, high-gain mode                                        | _                     | 3.3  | _                         | V    | 1     |

# Table 43. External Oscillator electrical specifications (OSC)<br/>(continued)

1. Measured at  $V_{DD} = 5 \text{ V}$ , Temperature = 25 °C

2. C1 and C2 must be provided by external capacitors and their load capacitance depends on the crystal or resonator manufacturers' recommendation. Please check the crystal datasheet for the recommended values.

3. When low power mode is selected,  $R_F$  is integrated and must not be attached externally.

4. The EXTAL and XTAL pins should only be connected to required oscillator components and must not be connected to any other devices.

### 5.4.2.1.2 External Oscillator frequency specifications Table 44. External Oscillator frequency specifications (OSC32)

| Symbol                | Description                                                            | Min.                                  | Тур. | Max. | Unit | Notes |

|-----------------------|------------------------------------------------------------------------|---------------------------------------|------|------|------|-------|

| f <sub>osc_lo</sub>   | Oscillator crystal or resonator frequency — low-<br>frequency mode     | 30                                    | _    | 40   | kHz  |       |

| t <sub>dc_extal</sub> | Input clock duty cycle (external clock mode)                           | 40                                    | 50   | 60   | %    |       |

| t <sub>cst</sub>      | Crystal startup time — 32 kHz low-frequency,<br>low-power mode (HGO=0) | · · · · · · · · · · · · · · · · · · · |      | ms   | 1    |       |

1. The start-up measured after 4096 cycles. Proper PC board layout procedures must be followed to achieve specifications.

| Symbol                | Description                                                               | Min. | Тур. | Max. | Unit   | Notes |

|-----------------------|---------------------------------------------------------------------------|------|------|------|--------|-------|

| f <sub>osc_lo</sub>   | Oscillator crystal or resonator frequency — Low Frequency, High Gain Mode | 32   | —    | 40   | 40 kHz |       |

| f <sub>osc_me</sub>   | Oscillator crystal or resonator frequency —<br>Medium Frequency           | 1    |      | 8    | MHz    |       |

| f <sub>osc_hi</sub>   | Oscillator crystal or resonator frequency —<br>High Frequency             | 8    | —    | 32   |        |       |

| t <sub>dc_extal</sub> | Input clock duty cycle (external clock mode)                              | 40   | 50   | 60   | %      |       |

| t <sub>cst</sub>      | Crystal startup time — 32 kHz Low Frequency,<br>High-Gain Mode            | —    | 500  | —    | ms     | 1     |

|                       | Crystal startup time — 8 MHz High Frequency,<br>Low-Power Mode            | —    | 1.5  | —    |        |       |

|                       | Crystal startup time — 8 MHz High Frequency,<br>High-Gain Mode            | —    | 2.5  |      |        |       |

|                       | Crystal startup time — 40 MHz High<br>Frequency, Low-Power Mode           | —    | 2    | —    |        |       |

|                       | Crystal startup time — 40 MHz High<br>Frequency, High-Gain Mode           | _    | 2.5  | —    |        |       |

### Table 45. External Oscillator frequency specifications (OSC)

1. The start-up measured after 4096 cycles. Proper PC board layout procedures must be followed to achieve specifications.

## 5.4.2.2 System Clock Generation (SCG) specifications

### 5.4.2.2.1 Fast internal RC Oscillator (FIRC) electrical specifications Table 46. Fast internal RC Oscillator electrical specifications

| Symbol                 | Parameter                                                                            |                               | Value |                               | Unit               |

|------------------------|--------------------------------------------------------------------------------------|-------------------------------|-------|-------------------------------|--------------------|

|                        |                                                                                      | Min.                          | Тур.  | Max.                          |                    |

| F <sub>FIRC</sub>      | Fast internal reference frequency                                                    | _                             | 48    | _                             | MHz                |

|                        | Trim range = 00                                                                      |                               | 52    |                               |                    |

|                        | range = 01 (Note: 52/56 MHz are not trimmed)                                         |                               | 56    |                               |                    |

|                        | range = 10 (Note: 52/56 MHz are not trimmed)                                         |                               | 60    |                               |                    |

|                        | Trim range = 11                                                                      |                               |       |                               |                    |

| I <sub>VDD</sub>       | Supply current                                                                       | _                             | 400   | 500                           | μA                 |

| F <sub>Untrimmed</sub> | IRC frequency (untrimmed)                                                            | F <sub>IRC</sub> ×<br>(1-0.3) | —     | F <sub>IRC</sub> ×<br>(1+0.3) | MHz                |

| ΔF <sub>OL</sub>       | Open loop total deviation of IRC frequency over voltage and temperature <sup>1</sup> |                               |       |                               |                    |

|                        | Regulator enable                                                                     | _                             | ±0.5  | ±1                            | %F <sub>FIRC</sub> |

| T <sub>Startup</sub>   | Startup time                                                                         |                               | —     | 3                             | μs <sup>2</sup>    |

| T <sub>JIT</sub>       | Period jitter (RMS)                                                                  | _                             | 35    | 150                           | ps                 |

1.  $\Delta F_{cl}$  is dependent on reference clock accuracy. For example, if locked to crystal oscillator,  $\Delta F_{cl}$  is typically limited by trimming ability of the module itself; if locked to other clock source which has 3% accuracy, then  $\Delta F_{cl}$  can only be  $\pm 3\%$ .

# 5.4.3 Memories and memory interfaces

### 5.4.3.1 Flash memory module (FTFE) electrical specifications

This section describes the electrical characteristics of the flash memory module (FTFE).

### 5.4.3.1.1 Flash timing specifications — program and erase

The following specifications represent the amount of time the internal charge pumps are active and do not include command overhead.

| Symbol                    | Description                                    | Min. | Тур. | Max. | Unit | Notes |

|---------------------------|------------------------------------------------|------|------|------|------|-------|

| t <sub>hvpgm8</sub>       | Program Phrase high-voltage time               | —    | 7.5  | 18   | μs   |       |

| t <sub>hversscr</sub>     | Erase Flash Sector high-voltage time           | —    | 13   | 113  | ms   | 1     |

| t <sub>hversblk32k</sub>  | Erase Flash Block high-voltage time for 32 KB  | —    | 26   | 226  | ms   | 1     |

| t <sub>hversblk256k</sub> | Erase Flash Block high-voltage time for 256 KB | _    | 208  | 1808 | ms   | 1     |

Table 50. NVM program/erase timing specifications

1. Maximum time based on expectations at cycling end-of-life.

### 5.4.3.1.2 Flash timing specifications — commands Table 51. Flash command timing specifications

| Symbol                  | Description                                 | Min. | Тур. | Max. | Unit | Notes |

|-------------------------|---------------------------------------------|------|------|------|------|-------|

|                         | Read 1s Block execution time                |      |      |      |      |       |

| t <sub>rd1blk32k</sub>  | • 32 KB data flash                          | _    | —    | 0.3  | ms   |       |

| t <sub>rd1blk256k</sub> | • 256 KB program flash                      | _    |      | 1.8  | ms   |       |

| t <sub>rd1sec2k</sub>   | Read 1s Section execution time (2 KB flash) | —    | _    | 75   | μs   | 1     |

| t <sub>pgmchk</sub>     | Program Check execution time                | _    | —    | 95   | μs   | 1     |

| t <sub>rdrsrc</sub>     | Read Resource execution time                | _    | —    | 40   | μs   | 1     |

| t <sub>pgm8</sub>       | Program Phrase execution time               | —    | 90   | 150  | μs   |       |

|                         | Erase Flash Block execution time            |      |      |      |      | 2     |

| t <sub>ersblk32k</sub>  | • 32 KB data flash                          | _    | 28   | 240  | ms   |       |

| t <sub>ersblk256k</sub> | • 256 KB program flash                      | _    | 220  | 1850 | ms   |       |

| t <sub>ersscr</sub>     | Erase Flash Sector execution time           | _    | 15   | 115  | ms   | 2     |

Table continues on the next page ...

|                         |                                                        | •    |      |      |      |       |  |

|-------------------------|--------------------------------------------------------|------|------|------|------|-------|--|

| Symbol                  | Description                                            | Min. | Тур. | Max. | Unit | Notes |  |

| t <sub>pgmsec512</sub>  | Program Section execution time (512B flash)            |      | 2.5  | _    | ms   |       |  |

| t <sub>rd1all</sub>     | Read 1s All Blocks execution time                      | _    | —    | 2.2  | ms   |       |  |

| t <sub>rdonce</sub>     | Read Once execution time                               | _    | —    | 30   | μs   | 1     |  |

| t <sub>pgmonce</sub>    | Program Once execution time                            | _    | 90   | _    | μs   |       |  |

| t <sub>ersall</sub>     | Erase All Blocks execution time                        | _    | 250  | 2100 | ms   | 2     |  |

| t <sub>vfykey</sub>     | Verify Backdoor Access Key execution time              | _    | —    | 30   | μs   | 1     |  |

| t <sub>ersallu</sub>    | Erase All Blocks Unsecure execution time               | _    | 250  | 2100 | ms   | 2     |  |

|                         | Program Partition for EEPROM execution time            |      |      |      |      |       |  |

| t <sub>pgmpart24k</sub> | 24 KB EEPROM backup                                    | —    | 69   | _    | ms   |       |  |

| t <sub>pgmpart32k</sub> | 32 KB EEPROM backup                                    | —    | 70   | _    | ms   |       |  |

|                         | Set FlexRAM Function execution time:                   |      |      |      |      |       |  |

| t <sub>setramff</sub>   | Control Code 0xFF                                      | —    | 50   | _    | μs   |       |  |

| t <sub>setram24k</sub>  | 24 KB EEPROM backup                                    | —    | 0.6  | 1.1  | ms   |       |  |

| t <sub>setram32k</sub>  | • 32 KB EEPROM backup                                  | —    | 0.8  | 1.2  | ms   |       |  |

|                         | Byte-write to FlexRAM execution time:                  |      |      |      |      |       |  |

| t <sub>eewr8b24k</sub>  | 24 KB EEPROM backup                                    | —    | 370  | 1625 | μs   |       |  |

| t <sub>eewr8b32k</sub>  | 32 KB EEPROM backup                                    | —    | 385  | 1700 | μs   |       |  |

|                         | 16-bit write to FlexRAM execution time:                |      |      |      |      |       |  |

| t <sub>eewr16b24k</sub> | 24 KB EEPROM backup                                    | —    | 370  | 1625 | μs   |       |  |

| t <sub>eewr16b32k</sub> | 32 KB EEPROM backup                                    | —    | 385  | 1700 | μs   |       |  |

| t <sub>eewr32bers</sub> | 32-bit write to erased FlexRAM location execution time |      | 360  | 1500 | μs   |       |  |

|                         | 32-bit write to FlexRAM execution time:                |      |      |      |      |       |  |

| t <sub>eewr32b24k</sub> | 24 KB EEPROM backup                                    | _    | 600  | 1950 | μs   |       |  |

| t <sub>eewr32b32k</sub> | 32 KB EEPROM backup                                    | _    | 630  | 2000 | μs   |       |  |

Table 51. Flash command timing specifications (continued)

1. Assumes 25MHz or greater flash clock frequency.

2. Maximum times for erase parameters based on expectations at cycling end-of-life.

### 5.4.3.1.3 Flash high voltage current behaviors Table 52. Flash high voltage current behaviors

| Symbol              | Description                                                           | Min. | Тур. | Max. | Unit |

|---------------------|-----------------------------------------------------------------------|------|------|------|------|

| I <sub>DD_PGM</sub> | Average current adder during high voltage flash programming operation | —    | 3.5  | 7.5  | mA   |

| I <sub>DD_ERS</sub> | Average current adder during high voltage flash erase operation       |      | 1.5  | 4.0  | mA   |

| Symbol            | Description                            | Conditions                                                                                                             | Min.              | Typ. <sup>1</sup> | Max.                       | Unit | Notes |

|-------------------|----------------------------------------|------------------------------------------------------------------------------------------------------------------------|-------------------|-------------------|----------------------------|------|-------|

| V <sub>DDA</sub>  | Supply voltage                         | Absolute                                                                                                               | 2.7               | _                 | 5.5                        | V    |       |

| $\Delta V_{DDA}$  | Supply voltage                         | Delta to V <sub>DD</sub><br>(V <sub>DD</sub> – V <sub>DDA</sub> )                                                      | -100              | 0                 | +100                       | mV   | 2     |

| $\Delta V_{SSA}$  | Ground voltage                         | Delta to V <sub>SS</sub> (V <sub>SS</sub><br>– V <sub>SSA</sub> )                                                      | -100              | 0                 | +100                       | mV   | 2     |

| V <sub>REFH</sub> | ADC reference voltage high             |                                                                                                                        | 2.5               | V <sub>DDA</sub>  | V <sub>DDA</sub> +<br>100m | V    | 3     |

| V <sub>REFL</sub> | ADC reference voltage low              |                                                                                                                        | - 100             | 0                 | 100                        | mV   | 3     |

| V <sub>ADIN</sub> | Input voltage                          |                                                                                                                        | V <sub>REFL</sub> | _                 | V <sub>REFH</sub>          | V    |       |

| C <sub>ADIN</sub> | Input capacitance                      |                                                                                                                        |                   | 4                 | 5                          | pF   |       |

| R <sub>ADIN</sub> | Input series resistance                |                                                                                                                        |                   | 2                 | 5                          | kΩ   |       |

| R <sub>AS</sub>   | Analog source resistance<br>(external) |                                                                                                                        | —                 |                   | 5                          | kΩ   | 4     |

| f <sub>ADCK</sub> | ADC conversion clock frequency         |                                                                                                                        | 2                 | 40                | 50                         | MHz  | 5, 6  |

| C <sub>rate</sub> | ADC conversion rate                    | No ADC<br>hardware<br>averaging <sup>7</sup><br>Continuous<br>conversions<br>enabled,<br>subsequent<br>conversion time | 20                |                   | 1200                       | Ksps | 8     |

### 5.4.5.1.1 12-bit ADC operating conditions Table 54. 12-bit ADC operating conditions

Typical values assume V<sub>DDA</sub> = 5 V, Temp = 25 °C, f<sub>ADCK</sub> = 40 MHz, unless otherwise stated. Typical values are for reference only, and are not tested in production.

- 2. DC potential difference.

- For packages without dedicated V<sub>REFH</sub> and V<sub>REFL</sub> pins, V<sub>REFH</sub> is internally tied to V<sub>DDA</sub>, and V<sub>REFL</sub> is internally tied to V<sub>SSA</sub>.

- 4. This resistance is external to MCU. To achieve the best results, the analog source resistance must be kept as low as possible. The results in this data sheet were derived from a system that had < 8  $\Omega$  analog source resistance. The R<sub>AS</sub>/C<sub>AS</sub> time constant should be kept to < 1 ns.

- 5. Clock and compare cycle need to be set according the guidelines in the block guide.

- 6. ADC conversion will become less reliable above maximum frequency.

- 7. When using ADC hardware averaging, refer to the device *Reference Manual* to determine the most appropriate setting for AVGS.

- 8. Max ADC conversion rate of 1200 Ksps is with 10-bit mode

| Symbol              | Description                                           | Conditions <sup>1</sup>                                  | Min.  | Typ. <sup>2</sup>      | Max. <sup>3</sup>                                                | Unit             | Notes                                                                                                       |

|---------------------|-------------------------------------------------------|----------------------------------------------------------|-------|------------------------|------------------------------------------------------------------|------------------|-------------------------------------------------------------------------------------------------------------|

|                     | Sample Time                                           |                                                          | 275   | _                      | Refer to<br>the<br>device's<br><i>Reference</i><br><i>Manual</i> | ns               |                                                                                                             |

| TUE                 | Total unadjusted error at 2.7 to 5.5 V                |                                                          | _     | ±4.5                   | ±6.11                                                            | LSB <sup>5</sup> | 6                                                                                                           |

| DNL                 | Differential non-<br>linearity at 2.7 to 5.5 V        |                                                          | -     | ±0.8                   | ±1.07                                                            | LSB <sup>5</sup> | 6                                                                                                           |

| INL                 | Integral non-linearity at 2.7 to 5.5 V                |                                                          | -     | ±1.4                   | ±3.54                                                            | LSB <sup>5</sup> | 6                                                                                                           |

| E <sub>FS</sub>     | Full-scale error at 2.7<br>to 5.5 V                   |                                                          | _     | -2                     | -3.60                                                            | LSB <sup>5</sup> | $V_{ADIN} = V_{DDA}^{6}$                                                                                    |

| E <sub>ZS</sub>     | Zero-scale error at 2.7<br>to 5.5 V                   |                                                          | -     | -2.7                   | -4.24                                                            | LSB <sup>5</sup> |                                                                                                             |

| EQ                  | Quantization error at 2.7 to 5.5 V                    |                                                          | -     | _                      | ±0.5                                                             | LSB <sup>5</sup> |                                                                                                             |

| ENOB                | Effective number of bits at 2.7 to 5.5 V              |                                                          | -     | 11.3                   | —                                                                | bits             | 7                                                                                                           |

| SINAD               | Signal-to-noise plus<br>distortion at 2.7 to 5.5<br>V | See ENOB                                                 | _     | 70                     | -                                                                | dB               | SINAD = 6.02 ×<br>ENOB + 1.76                                                                               |

| E <sub>IL</sub>     | Input leakage error at<br>2.7 to 5.5 V                |                                                          |       | $I_{ln} \times R_{AS}$ |                                                                  | mV               | I <sub>In</sub> = leakage<br>current (refer to<br>the MCU's<br>voltage and<br>current operating<br>ratings) |

| V <sub>TEMP_S</sub> | Temp sensor slope at<br>2.7 to 5.5 V                  | Across the full<br>temperature<br>range of the<br>device | 1.492 | 1.564                  | 1.636                                                            | mV/°C            | 8, 9                                                                                                        |

| V <sub>TEMP25</sub> | Temp sensor voltage<br>at 2.7 to 5.5 V                | 25 °C                                                    | 730   | 740.5                  | 751                                                              | mV               | 8, 9                                                                                                        |

1. All accuracy numbers assume the ADC is calibrated with  $V_{\mathsf{REFH}}$  =  $V_{\mathsf{DDA}}$

- 2. Typical values assume  $V_{DDA}$  = 5.0 V, Temp = 25 °C,  $f_{ADCK}$  = 48 MHz unless otherwise stated.

- 3. These values are based on characterization but not covered by test limits in production.

- The ADC supply current depends on the ADC conversion clock speed, conversion rate and ADC\_CFG1[ADLPC] (low power). For lowest power operation, ADC\_CFG1[ADLPC] must be set, the ADC\_CFG2[ADHSC] bit must be clear with 1 MHz ADC conversion clock speed.

- 5. 1 LSB =  $(V_{REFH} V_{REFL})/2^N$

- 6. ADC conversion clock < 16 MHz, Max hardware averaging (AVGE = %1, AVGS = %11)

- 7. Input data is 100 Hz sine wave. ADC conversion clock < 40 MHz.

- 8. ADC conversion clock < 3 MHz

- 9. The sensor must be calibrated to gain good accuracy, so as to provide good linearity, see also AN3031 for more detailed application information of the temperature sensor.

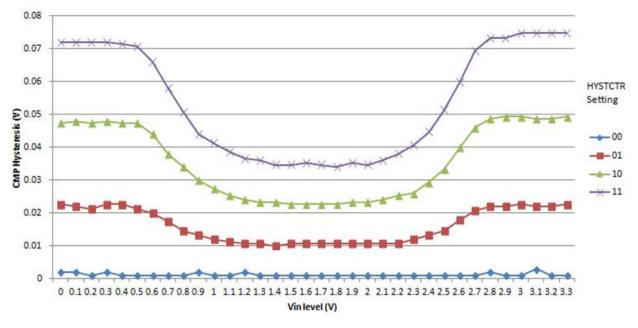

Figure 21. Typical hysteresis vs. Vin level (VDD = 3.3 V, PMODE = 1)

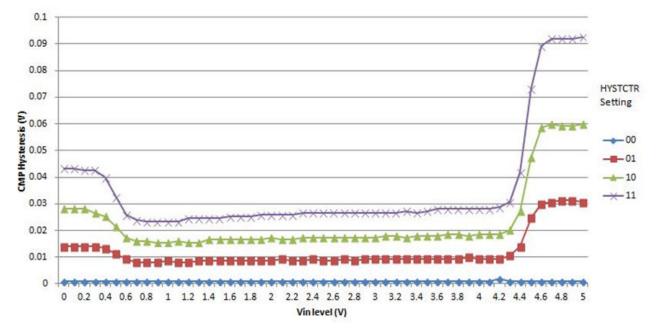

Figure 22. Typical hysteresis vs. Vin level (VDD = 5 V, PMODE = 0)