# E·XFL

#### NXP USA Inc. - MKE14Z256VLH7R Datasheet

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                 |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                       |

| Core Size                  | 32-Bit Single-Core                                                     |

| Speed                      | 72MHz                                                                  |

| Connectivity               | FlexIO, I <sup>2</sup> C, SPI, UART/USART                              |

| Peripherals                | DMA, LVD, PWM, WDT                                                     |

| Number of I/O              | 58                                                                     |

| Program Memory Size        | 256KB (256K x 8)                                                       |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | 34K x 8                                                                |

| RAM Size                   | 32K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                            |

| Data Converters            | A/D 16x12b; D/A 1x8b                                                   |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 64-LQFP                                                                |

| Supplier Device Package    | 64-LQFP (10x10)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mke14z256vlh7r |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

is reset by the corresponding Reset source. N means the specific module is not reset by the corresponding Reset source.

| Reset            | Descriptions                                                 | Modules        |                |                |                |                            |                |                |     |           |            |

|------------------|--------------------------------------------------------------|----------------|----------------|----------------|----------------|----------------------------|----------------|----------------|-----|-----------|------------|

| sources          |                                                              | РМС            | SIM            | SMC            | RCM            | Reset<br>pin is<br>negated | WDO<br>G       | SCG            | RTC | LPTM<br>R | Other<br>s |

| POR reset        | Power-on reset (POR)                                         | Y              | Y              | Y              | Y              | Y                          | Y              | Y              | Y   | Y         | Y          |

| System<br>resets | Low-voltage detect<br>(LVD)                                  | Y <sup>1</sup> | Y              | Y              | Y              | Y                          | Y              | Y              | Ν   | Y         | Y          |

|                  | External pin reset<br>(RESET)                                | Y <sup>1</sup> | Y <sup>2</sup> | Y <sup>3</sup> | Y <sup>4</sup> | Y                          | Y <sup>5</sup> | Y <sup>6</sup> | Ν   | N         | Y          |

|                  | Watchdog (WDOG)<br>reset                                     | Y <sup>1</sup> | Y <sup>2</sup> | Y <sup>3</sup> | Y <sup>4</sup> | Y                          | Y <sup>5</sup> | Y <sup>6</sup> | Ν   | N         | Y          |

|                  | Multipurpose clock<br>generator loss of clock<br>(LOC) reset | Y <sup>1</sup> | Y <sup>2</sup> | Y <sup>3</sup> | Y <sup>4</sup> | Y                          | Y <sup>5</sup> | Y <sup>6</sup> | Ν   | N         | Y          |

|                  | Multipurpose clock<br>generator loss of lock<br>(LOL) reset  | Y <sup>1</sup> | Y <sup>2</sup> | Y <sup>3</sup> | Y <sup>4</sup> | Y                          | Y <sup>5</sup> | Y <sup>6</sup> | Ν   | N         | Y          |

|                  | Stop mode acknowledge error (SACKERR)                        | Y <sup>1</sup> | Y <sup>2</sup> | Y <sup>3</sup> | Y <sup>4</sup> | Y                          | Y <sup>5</sup> | Y <sup>6</sup> | Ν   | N         | Y          |

|                  | Software reset (SW)                                          | Y <sup>1</sup> | Y <sup>2</sup> | Y <sup>3</sup> | Y <sup>4</sup> | Y                          | Y <sup>5</sup> | Y <sup>6</sup> | Ν   | N         | Y          |

|                  | Lockup reset (LOCKUP)                                        | Y <sup>1</sup> | Y <sup>2</sup> | Y <sup>3</sup> | Y <sup>4</sup> | Y                          | Y <sup>5</sup> | Y <sup>6</sup> | Ν   | Ν         | Y          |

|                  | MDM DAP system reset                                         | Y <sup>1</sup> | Y <sup>2</sup> | Y <sup>3</sup> | Y <sup>4</sup> | Y                          | Y <sup>5</sup> | Y <sup>6</sup> | Ν   | Ν         | Y          |

| Debug reset      | Debug reset                                                  | Y <sup>1</sup> | Y <sup>2</sup> | Y <sup>3</sup> | Y <sup>4</sup> | Y                          | Y <sup>5</sup> | Y <sup>6</sup> | Ν   | N         | Y          |

Table 3.Reset source

1. Except PMC\_LVDSC1[LVDV] and PMC\_LVDSC2[LVWV]

- 2. Except SIM\_SOPT1

- 3. Except SMC\_PMPROT, SMC\_PMCTRL\_RUM, SMC\_PMCTRL\_STOPM, SMC\_STOPCTRL, SMC\_PMSTAT

- 4. Except RCM\_RPC, RCM\_MR, RCM\_FM, RCM\_SRIE, RCM\_SRS, RCM\_SSRS

- 5. Except WDOG\_CS[TST]

- 6. Except SCG\_CSR and SCG\_FIRCSTAT

This device supports booting from:

- internal flash

- boot ROM

rights for each transaction routed to the on-chip flash memory. Configurability allows an increasing number of protected segments while supporting two levels of vendors adding their proprietary software to a device.

## 2.1.8 Power management

The Power Management Controller (PMC) expands upon ARM's operational modes of Run, Sleep, and Deep Sleep, to provide multiple configurable modes. These modes can be used to optimize current consumption for a wide range of applications. The WFI or WFE instruction invokes a Wait or a Stop mode, depending on the current configuration. For more information on ARM's operational modes, See the ARM<sup>®</sup> Cortex<sup>®</sup> User Guide.

The PMC provides Normal Run (RUN), and Very Low Power Run (VLPR) configurations in ARM's Run operation mode. In these modes, the MCU core is active and can access all peripherals. The difference between the modes is the maximum clock frequency of the system and therefore the power consumption. The configuration that matches the power versus performance requirements of the application can be selected.

The PMC provides Wait (Wait) and Very Low Power Wait (VLPW) configurations in ARM's Sleep operation mode. In these modes, even though the MCU core is inactive, all of the peripherals can be enabled and operate as programmed. The difference between the modes is the maximum clock frequency of the system and therefore the power consumption.

The PMC provides Stop (Stop), Very Low Power Stop (VLPS) configurations in ARM's Deep Sleep operational mode. In these modes, the MCU core and most of the peripherals are disabled. Depending on the requirements of the application, different portions of the analog, logic, and memory can be retained or disabled to conserve power.

The Nested Vectored Interrupt Controller (NVIC), the Asynchronous Wake-up Interrupt Controller (AWIC) are used to wake up the MCU from low power states. The NVIC is used to wake up the MCU core from WAIT and VLPW modes. The AWIC is used to wake up the MCU core from STOP and VLPS modes.

For additional information regarding operational modes, power management, the NVIC, AWIC, please refer to the Reference Manual.

The following table provides information about the state of the peripherals in the various operational modes and the modules that can wake MCU from low power modes.

| Core mode  | Device mode         | Descriptions                                                                                                                                                                                                                                                                                                                           |

|------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Run mode   | Run                 | In Run mode, all device modules are operational.                                                                                                                                                                                                                                                                                       |

|            | Very Low Power Run  | In VLPR mode, all device modules are operational at a reduced frequency except the Low Voltage Detect (LVD) monitor, which is disabled.                                                                                                                                                                                                |

| Sleep mode | Wait                | In Wait mode, all peripheral modules are operational. The MCU core is placed into Sleep mode.                                                                                                                                                                                                                                          |

|            | Very Low Power Wait | In VLPW mode, all peripheral modules are operational at a reduced frequency except the Low Voltage Detect (LVD) monitor, which is disabled. The MCU core is placed into Sleep mode.                                                                                                                                                    |

| Deep sleep | Stop                | In Stop mode, most peripheral clocks are disabled and placed in a static state. Stop mode retains all registers and SRAMs while maintaining Low Voltage Detection protection. In Stop mode, the ADC, CMP, LPTMR, RTC, and pin interrupts are operational. The NVIC is disabled, but the AWIC can be used to wake up from an interrupt. |

|            | Very Low Power Stop | In VLPS mode, the contents of the SRAM are retained. The CMP (low speed), ADC, OSC, RTC, LPTMR, LPIT, FlexIO, LPUART, LPI2C,LPSPI, and DMA are operational, LVD and NVIC are disabled, AWIC is used to wake up from interrupt.                                                                                                         |

Table 5.

Peripherals states in different operational modes

## 2.1.9 Debug controller

This device has extensive debug capabilities including run control and tracing capabilities. The standard ARM debug port supports SWD interface.

# 2.2 Peripheral features

The following sections describe the features of each peripherals of the chip.

# 2.2.1 eDMA and DMAMUX

The eDMA is a highly programmable data-transfer engine optimized to minimize any required intervention from the host processor. It is intended for use in applications where the data size to be transferred is statically known and not defined within the transferred data itself. The DMA controller in this device implements 8 channels which can be routed from up to 63 DMA request sources through DMA MUX module.

Main features of eDMA are listed below:

#### Overview

- Hardware CRC generator circuit using a 16-bit or 32-bit programmable shift register

- Programmable initial seed value and polynomial

- Option to transpose input data or output data (the CRC result) bitwise or bytewise.

- Option for inversion of final CRC result

- 32-bit CPU register programming interface

## 2.2.10 LPUART

This product contains three Low-Power UART modules, and can work in Stop and VLPS modes. The module also supports  $4 \times$  to  $32 \times$  data oversampling rate to meet different applications.

The LPUART module has the following features:

- Programmable baud rates (13-bit modulo divider) with configurable oversampling ratio from  $4 \times$  to  $32 \times$

- Transmit and receive baud rate can operate asynchronous to the bus clock and can be configured independently of the bus clock frequency, support operation in Stop mode

- Interrupt, DMA or polled operation

- Hardware parity generation and checking

- Programmable 8-bit, 9-bit or 10-bit character length

- Programmable 1-bit or 2-bit stop bits

- Three receiver wakeup methods

- Idle line wakeup

- Address mark wakeup

- Receive data match

- Automatic address matching to reduce ISR overhead:

- Address mark matching

- Idle line address matching

- Address match start, address match end

- Optional 13-bit break character generation / 11-bit break character detection

- Configurable idle length detection supporting 1, 2, 4, 8, 16, 32, 64 or 128 idle characters

- Selectable transmitter output and receiver input polarity

# 2.2.13 FlexIO

The FlexIO is a highly configurable module providing a wide range of protocols including, but not limited to UART, I2C, SPI, I2S, Camera IF, LCD RGB, PWM/ Waveform generation. The module supports programmable baud rates independent of bus clock frequency, with automatic start/stop bit generation.

The FlexIO module has the following features:

- Functional in VLPR/VLPW/Stop/VLPS mode provided the clock it is using remains enabled

- Four 32-bit double buffered shift registers with transmit, receive, and data match modes, and continuous data transfer

- The timing of the shifter's shift, load and store events are controlled by the highly flexible 16-bit timer assigned to the shifter

- Two or more shifters can be concatenated to support large data transfer sizes

- Each 16-bit timers operates independently, supports for reset, enable and disable on a variety of internal or external trigger conditions with programmable trigger polarity

- Flexible pin configuration supporting output disabled, open drain, bidirectional output data and output mode

- Supports interrupt, DMA or polled transmit/receive operation

# 2.2.14 Port control and GPIO

The Port Control and Interrupt (PORT) module provides support for port control, digital filtering, and external interrupt functions. The GPIO data direction and output data registers control the direction and output data of each pin when the pin is configured for the GPIO function. The GPIO input data register displays the logic value on each pin when the pin is configured for any digital function, provided the corresponding Port Control and Interrupt module for that pin is enabled.

The following figure shows the basic I/O pad structure. Pseudo open-drain pins have the p-channel output driver disabled when configured for open-drain operation. None of the I/O pins, including open-drain and pseudo open-drain pins, are allowed to go above VDD.

## NOTE

The RESET\_b pin is also a normal I/O pad with pseudo opendrain.

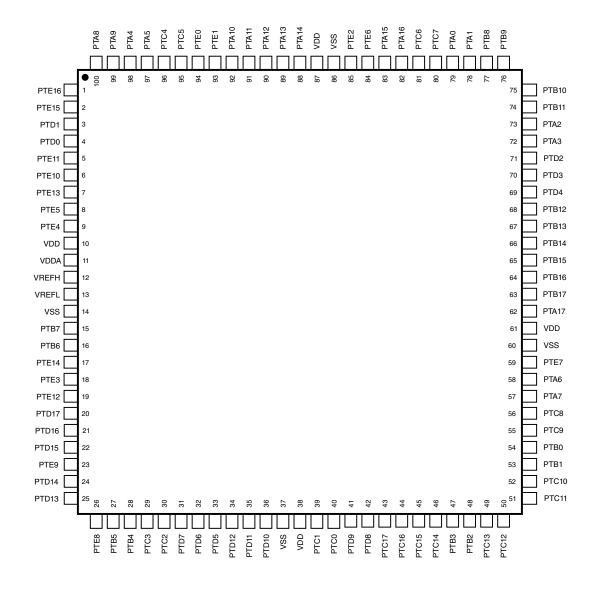

# 4 Pinouts

# 4.1 KE1xZ Signal Multiplexing and Pin Assignments

The following table shows the signals available on each pin and the locations of these pins on the devices supported by this document. The Port Control Module is responsible for selecting which ALT functionality is available on each pin.

## NOTE

On this device, there are several special ADC channels which support hardware interleave between multiple ADCs. Taking ADC0\_SE4 and ADC1\_SE14 channels as an example, these two channels can work independently, but they can also be hardware interleaved. In the hardware interleaved mode, a signal on the pin PTB0 can be sampled by both ADC0 and ADC1. The interleaved mode is enabled by SIM\_CHIPCTL[ADC\_INTERLEAVE\_EN] bits. For more information, see "ADC Hardware Interleaved Channels" in the ADC chapter of Reference Manual.

| 100<br>LQFP | 64<br>LQFP | Pin Name      | Default       | ALT0          | ALT1  | ALT2     | ALT3            | ALT4     | ALT5 | ALT6    | ALT7            |

|-------------|------------|---------------|---------------|---------------|-------|----------|-----------------|----------|------|---------|-----------------|

| -           | 10         | VREFL/<br>VSS | VREFL/<br>VSS | VREFL/<br>VSS |       |          |                 |          |      |         |                 |

| 1           | _          | PTE16         | DISABLED      |               | PTE16 |          |                 |          |      | FXIO_D3 | TRGMUX_<br>OUT7 |

| 2           | _          | PTE15         | DISABLED      |               | PTE15 |          |                 |          |      | FXIO_D2 | TRGMUX_<br>OUT6 |

| 3           | 1          | PTD1          | TSI0_CH5      | TSI0_CH5      | PTD1  | FTM0_CH3 | LPSPI1_SIN      | FTM2_CH1 |      | FXIO_D1 | TRGMUX_<br>OUT2 |

| 4           | 2          | PTD0          | TSI0_CH4      | TSI0_CH4      | PTD0  | FTM0_CH2 | LPSPI1_SCK      | FTM2_CH0 |      | FXIO_D0 | TRGMUX_<br>OUT1 |

| 5           | 3          | PTE11         | TSI0_CH3      | TSI0_CH3      | PTE11 | PWT_IN1  | LPTMR0_<br>ALT1 |          |      | FXIO_D5 | TRGMUX_<br>OUT5 |

| 6           | 4          | PTE10         | TSI0_CH2      | TSI0_CH2      | PTE10 | CLKOUT   |                 |          |      | FXIO_D4 | TRGMUX_<br>OUT4 |

| 7           | _          | PTE13         | DISABLED      |               | PTE13 |          |                 |          |      |         |                 |

| 8           | 5          | PTE5          | TSI0_CH0      | TSI0_CH0      | PTE5  | TCLK2    | FTM2_QD_<br>PHA | FTM2_CH3 |      | FXIO_D7 | EWM_IN          |

| 9           | 6          | PTE4          | TSI0_CH1      | TSI0_CH1      | PTE4  | BUSOUT   | FTM2_QD_<br>PHB | FTM2_CH2 |      | FXIO_D6 | EWM_OUT_b       |

| 100<br>LQFP | 64<br>LQFP | Pin Name | Default                              | ALTO                                 | ALT1  | ALT2       | ALT3            | ALT4      | ALT5    | ALT6            | ALT7       |

|-------------|------------|----------|--------------------------------------|--------------------------------------|-------|------------|-----------------|-----------|---------|-----------------|------------|

| 10          | 7          | VDD      | VDD                                  | VDD                                  |       |            |                 |           |         |                 |            |

| 11          | 8          | VDDA     | VDDA                                 | VDDA                                 |       |            |                 |           |         |                 |            |

| 12          | 9          | VREFH    | VREFH                                | VREFH                                |       |            |                 |           |         |                 |            |

| 13          | _          | VREFL    | VREFL                                | VREFL                                |       |            |                 |           |         |                 |            |

| 14          | _          | VSS      | VSS                                  | VSS                                  |       |            |                 |           |         |                 |            |

| 15          | 11         | PTB7     | EXTAL                                | EXTAL                                | PTB7  | LPI2C0_SCL |                 |           |         |                 |            |

| 16          | 12         | PTB6     | XTAL                                 | XTAL                                 | PTB6  | LPI2C0_SDA |                 |           |         |                 |            |

| 17          | _          | PTE14    | DISABLED                             |                                      | PTE14 | FTM0_FLT1  |                 |           |         |                 |            |

| 18          | 13         | PTE3     | TSI0_CH24                            | TSI0_CH24                            | PTE3  | FTM0_FLT0  | LPUART2_<br>RTS |           |         | TRGMUX_IN6      |            |

| 19          | _          | PTE12    | DISABLED                             |                                      | PTE12 | FTM0_FLT3  | LPUART2_TX      |           |         |                 |            |

| 20          | _          | PTD17    | DISABLED                             |                                      | PTD17 | FTM0_FLT2  | LPUART2_RX      |           |         |                 |            |

| 21          | 14         | PTD16    | DISABLED                             |                                      | PTD16 | FTM0_CH1   |                 |           |         |                 |            |

| 22          | 15         | PTD15    | DISABLED                             |                                      | PTD15 | FTM0_CH0   |                 |           |         |                 |            |

| 23          | 16         | PTE9     | DAC0_OUT                             | DAC0_OUT                             | PTE9  | FTM0_CH7   | LPUART2_<br>CTS |           |         |                 |            |

| 24          | —          | PTD14    | DISABLED                             |                                      | PTD14 |            |                 |           |         |                 | CLKOUT     |

| 25          | _          | PTD13    | DISABLED                             |                                      | PTD13 |            |                 |           |         |                 | RTC_CLKOUT |

| 26          | 17         | PTE8     | ACMP0_IN3/<br>TSI0_CH11              | ACMP0_IN3/<br>TSI0_CH11              | PTE8  | FTM0_CH6   |                 |           |         |                 |            |

| 27          | 18         | PTB5     | TSI0_CH9                             | TSI0_CH9                             | PTB5  | FTM0_CH5   | LPSPI0_PCS1     |           |         | TRGMUX_IN0      | ACMP1_OUT  |

| 28          | 19         | PTB4     | ACMP1_IN2/<br>TSI0_CH8               | ACMP1_IN2/<br>TSI0_CH8               | PTB4  | FTM0_CH4   | LPSPI0_SOUT     |           |         | TRGMUX_IN1      |            |

| 29          | 20         | PTC3     | ADC0_SE11/<br>ACMP0_IN4/<br>EXTAL32  | ADC0_SE11/<br>ACMP0_IN4/<br>EXTAL32  | PTC3  | FTM0_CH3   |                 |           |         |                 |            |

| 30          | 21         | PTC2     | ADC0_SE10/<br>ACMP0_IN5/<br>XTAL32   | ADC0_SE10/<br>ACMP0_IN5/<br>XTAL32   | PTC2  | FTM0_CH2   |                 |           |         |                 |            |

| 31          | 22         | PTD7     | TSI0_CH10                            | TSI0_CH10                            | PTD7  | LPUART2_TX |                 | FTM2_FLT3 |         |                 |            |

| 32          | 23         | PTD6     | TSI0_CH7                             | TSI0_CH7                             | PTD6  | LPUART2_RX |                 | FTM2_FLT2 |         |                 |            |

| 33          | 24         | PTD5     | TSI0_CH6                             | TSI0_CH6                             | PTD5  | FTM2_CH3   | LPTMR0_<br>ALT2 |           | PWT_IN2 | TRGMUX_IN7      |            |

| 34          | _          | PTD12    | DISABLED                             |                                      | PTD12 | FTM2_CH2   | LPI2C1_HREQ     |           |         | LPUART2_<br>RTS |            |

| 35          | —          | PTD11    | DISABLED                             |                                      | PTD11 | FTM2_CH1   | FTM2_QD_<br>PHA |           |         | LPUART2_<br>CTS |            |

| 36          | _          | PTD10    | DISABLED                             |                                      | PTD10 | FTM2_CH0   | FTM2_QD_<br>PHB |           |         |                 |            |

| 37          | -          | VSS      | VSS                                  | VSS                                  |       |            |                 |           |         |                 |            |

| 38          | -          | VDD      | VDD                                  | VDD                                  |       |            |                 |           |         |                 |            |

| 39          | 25         | PTC1     | ADC0_SE9/<br>ACMP1_IN3/<br>TSI0_CH23 | ADC0_SE9/<br>ACMP1_IN3/<br>TSI0_CH23 | PTC1  | FTM0_CH1   |                 |           |         |                 |            |

#### Pinouts

| 100<br>LQFP | 64<br>LQFP | Pin Name | Default                              | ALT0                                 | ALT1  | ALT2       | ALT3        | ALT4            | ALT5    | ALT6            | ALT7  |

|-------------|------------|----------|--------------------------------------|--------------------------------------|-------|------------|-------------|-----------------|---------|-----------------|-------|

| 40          | 26         | PTC0     | ADC0_SE8/<br>ACMP1_IN4/<br>TSI0_CH22 | ADC0_SE8/<br>ACMP1_IN4/<br>TSI0_CH22 | PTC0  | FTM0_CH0   |             |                 |         |                 |       |

| 41          | -          | PTD9     | ACMP1_IN5                            | ACMP1_IN5                            | PTD9  | LPI2C1_SCL |             | FTM2_FLT3       |         |                 |       |

| 42          | -          | PTD8     | DISABLED                             |                                      | PTD8  | LPI2C1_SDA |             | FTM2_FLT2       |         |                 |       |

| 43          | 27         | PTC17    | ADC0_SE15                            | ADC0_SE15                            | PTC17 | FTM1_FLT3  |             | LPI2C1_SCLS     |         |                 |       |

| 44          | 28         | PTC16    | ADC0_SE14                            | ADC0_SE14                            | PTC16 | FTM1_FLT2  |             | LPI2C1_SDAS     |         |                 |       |

| 45          | 29         | PTC15    | ADC0_SE13                            | ADC0_SE13                            | PTC15 | FTM1_CH3   |             |                 |         |                 |       |

| 46          | 30         | PTC14    | ADC0_SE12                            | ADC0_SE12                            | PTC14 | FTM1_CH2   |             |                 |         |                 |       |

| 47          | 31         | PTB3     | ADC0_SE7/<br>TSI0_CH21               | ADC0_SE7/<br>TSI0_CH21               | PTB3  | FTM1_CH1   | LPSPI0_SIN  | FTM1_QD_<br>PHA |         | TRGMUX_IN2      |       |

| 48          | 32         | PTB2     | ADC0_SE6/<br>TSI0_CH20               | ADC0_SE6/<br>TSI0_CH20               | PTB2  | FTM1_CH0   | LPSPI0_SCK  | FTM1_QD_<br>PHB |         | TRGMUX_IN3      |       |

| 49          | -          | PTC13    | DISABLED                             |                                      | PTC13 |            |             |                 |         |                 |       |

| 50          | -          | PTC12    | DISABLED                             |                                      | PTC12 |            |             |                 |         |                 |       |

| 51          | _          | PTC11    | DISABLED                             |                                      | PTC11 |            |             |                 |         |                 |       |

| 52          | _          | PTC10    | DISABLED                             |                                      | PTC10 |            |             |                 |         |                 |       |

| 53          | 33         | PTB1     | ADC0_SE5                             | ADC0_SE5                             | PTB1  | LPUART0_TX | LPSPI0_SOUT | TCLK0           |         |                 |       |

| 54          | 34         | PTB0     | ADC0_SE4                             | ADC0_SE4                             | PTB0  | LPUART0_RX | LPSPI0_PCS0 | LPTMR0_<br>ALT3 | PWT_IN3 |                 |       |

| 55          | 35         | PTC9     | DISABLED                             |                                      | PTC9  | LPUART1_TX |             |                 |         | LPUART0_<br>RTS |       |

| 56          | 36         | PTC8     | DISABLED                             |                                      | PTC8  | LPUART1_RX |             |                 |         | LPUART0_<br>CTS |       |

| 57          | 37         | PTA7     | ADC0_SE3/<br>ACMP1_IN1               | ADC0_SE3/<br>ACMP1_IN1               | PTA7  | FTM0_FLT2  |             | RTC_CLKIN       |         | LPUART1_<br>RTS |       |

| 58          | 38         | PTA6     | ADC0_SE2/<br>ACMP1_IN0               | ADC0_SE2/<br>ACMP1_IN0               | PTA6  | FTM0_FLT1  | LPSPI1_PCS1 |                 |         | LPUART1_<br>CTS |       |

| 59          | 39         | PTE7     | DISABLED                             |                                      | PTE7  | FTM0_CH7   |             |                 |         |                 |       |

| 60          | 40         | VSS      | VSS                                  | VSS                                  |       |            |             |                 |         |                 |       |

| 61          | 41         | VDD      | VDD                                  | VDD                                  |       |            |             |                 |         |                 |       |

| 62          | -          | PTA17    | DISABLED                             |                                      | PTA17 | FTM0_CH6   |             | EWM_OUT_b       |         |                 |       |

| 63          | -          | PTB17    | DISABLED                             |                                      | PTB17 | FTM0_CH5   | LPSPI1_PCS3 |                 |         |                 |       |

| 64          | -          | PTB16    | DISABLED                             |                                      | PTB16 | FTM0_CH4   | LPSPI1_SOUT |                 |         |                 |       |

| 65          | -          | PTB15    | DISABLED                             |                                      | PTB15 | FTM0_CH3   | LPSPI1_SIN  |                 |         |                 |       |

| 66          | _          | PTB14    | ADC1_SE9                             | ADC1_SE9                             | PTB14 | FTM0_CH2   | LPSPI1_SCK  |                 |         |                 |       |

| 67          | 42         | PTB13    | ADC1_SE8                             | ADC1_SE8                             | PTB13 | FTM0_CH1   |             |                 |         |                 |       |

| 68          | 43         | PTB12    | ADC1_SE7                             | ADC1_SE7                             | PTB12 | FTM0_CH0   |             |                 |         |                 |       |

| 69          | 44         | PTD4     | ADC1_SE6                             | ADC1_SE6                             | PTD4  | FTM0_FLT3  |             |                 |         |                 |       |

| 70          | 45         | PTD3     | NMI_b                                | ADC1_SE3                             | PTD3  |            | LPSPI1_PCS0 | FXIO_D5         |         | TRGMUX_IN4      | NMI_b |

| 71          | 46         | PTD2     | ADC1_SE2                             | ADC1_SE2                             | PTD2  |            | LPSPI1_SOUT | FXIO_D4         |         | TRGMUX_IN5      |       |

| 72          | 47         | PTA3     | ADC1_SE1                             | ADC1_SE1                             | PTA3  |            | LPI2C0_SCL  | EWM_IN          |         | LPUART0_TX      |       |

Figure 7. 100 LQFP Pinout Diagram

| Symbol           | Parameter                                                  |     | Value |     | Unit | Notes |  |  |

|------------------|------------------------------------------------------------|-----|-------|-----|------|-------|--|--|

|                  |                                                            | Min | Тур   | Max | 1    |       |  |  |

| I <sub>OLT</sub> | Output low current total for all ports                     | _   | _     | 100 | mA   |       |  |  |

| I <sub>IN</sub>  | Input leakage current (per pin) for full temperature range |     |       |     |      |       |  |  |

|                  | @ V <sub>DD</sub> = 3.3 V                                  |     |       |     |      |       |  |  |

|                  | All pins other than high drive port pins                   | _   | 0.002 | 0.5 | μA   |       |  |  |

|                  | High drive port pins                                       | _   | 0.004 | 0.5 | μA   |       |  |  |

|                  | Input leakage current (per pin) for full temperature range |     |       |     |      |       |  |  |

|                  | @ V <sub>DD</sub> = 5.5 V                                  |     |       |     |      |       |  |  |

|                  | All pins other than high drive port pins                   | —   | 0.005 | 0.5 | μA   |       |  |  |

|                  | High drive port pins                                       | _   | 0.010 | 0.5 | μA   |       |  |  |

| R <sub>PU</sub>  | Internal pull-up resistors                                 | 20  | _     | 65  | kΩ   | 9     |  |  |

|                  | @ V <sub>DD</sub> = 3.3 V                                  |     |       |     |      |       |  |  |

|                  | @ V <sub>DD</sub> = 5.0 V                                  | 20  | _     | 50  | kΩ   |       |  |  |

| R <sub>PD</sub>  | Internal pull-down resistors                               | 20  | —     | 65  | kΩ   | 10    |  |  |

|                  | @ V <sub>DD</sub> = 3.3 V                                  |     |       |     |      |       |  |  |

|                  | @ V <sub>DD</sub> = 5.0 V                                  | 20  | _     | 50  | kΩ   |       |  |  |

- 1. Max power supply ramp rate is 500 V/ms.

- 2. The value given is measured at high drive strength mode. For value at low drive strength mode see the loh\_5 value given above.

- 3. The 20 mA I/O pin is capable of switching a 50 pF load at up to 40 MHz.

- 4. The value given is measured at high drive strength mode. For value at low drive strength mode see the lol\_5 value given above.

- 5. Refers to the current that leaks into the core when the pad is in Hi-Z (Off state).

- 6. Maximum pin leakage current at the ambient temperature upper limit.

- 7. PTD0, PTD1, PTD15, PTD16, PTB4, PTB5, PTE0 and PTE1 I/O have both high drive and normal drive capability selected by the associated Portx\_PCRn[DSE] control bit. All other GPIOs are normal drive only.

- 8. Refers to the pin leakage on the GPIOs when they are OFF.

- 9. Measured at  $V_{DD}$  supply voltage =  $V_{DD}$  min and input V =  $V_{SS}$

- 10. Measured at V<sub>DD</sub> supply voltage = V<sub>DD</sub> min and input V = V<sub>DD</sub>

| Mode | Symbol               | Clock<br>Configura<br>tion                                      | Description                                                    | Temperat<br>ure | Min | Тур | Max <sup>1</sup> | Unit |

|------|----------------------|-----------------------------------------------------------------|----------------------------------------------------------------|-----------------|-----|-----|------------------|------|

|      |                      |                                                                 |                                                                | 50 ℃            | —   | 47  | 66               |      |

|      |                      |                                                                 |                                                                | 85 °C           | —   | 146 | 204              |      |

|      |                      |                                                                 |                                                                | 105 °C          | —   | 277 | 388              |      |

| VLPS |                      | Very Low Power Stop current, VDD=5V, bias disabled <sup>2</sup> | 25 °C and blew                                                 | _               | 27  | 37  | μA               |      |

|      |                      |                                                                 |                                                                | 50 °C           | —   | 45  | 64               |      |

|      |                      |                                                                 |                                                                | 85 °C           | —   | 134 | 187              |      |

|      |                      |                                                                 |                                                                | 105 °C          | —   | 267 | 375              |      |

| VLPS | I <sub>DD_VLPS</sub> | -                                                               | Very Low Power Stop current, VDD=5V, bias enabled <sup>2</sup> | 25 °C and blew  | _   | 21  | 29               | μA   |

|      |                      |                                                                 |                                                                | 50 ℃            | —   | 29  | 41               |      |

|      |                      |                                                                 |                                                                | 85 °C           | —   | 66  | 92               | 1    |

|      |                      |                                                                 |                                                                | 105 °C          | —   | 109 | 153              | 1    |

Table 33. Power consumption operating behaviors (continued)

1. These values are based on characterization but not covered by test limits in production.

2. PMC\_REGSC[CLKBIASDIS] is the control bit to enable or disable bias under STOP/VLPS mode.

## NOTE

# CoreMark benchmark compiled using IAR 7.40 with optimization level high, optimized for balanced.

#### 5.3.1.6.1 Low power mode peripheral current adder — typical value

| Symbol              | Description                                                                                                                                                                                                                                             | Typical |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| I <sub>LPTMR</sub>  | LPTMR peripheral adder measured by placing the device in VLPS<br>mode with LPTMR enabled using LPO. Includes LPO power<br>consumption.                                                                                                                  | 366 nA  |

| I <sub>CMP</sub>    | CMP peripheral adder measured by placing the device in VLPS mode<br>with CMP enabled using the 8-bit DAC and a single external input for<br>compare. 8-bit DAC enabled with half VDDA voltage, low speed mode.<br>Includes 8-bit DAC power consumption. | 16 µA   |

| I <sub>RTC</sub>    | RTC peripheral adder measured by placing the device in VLPS mode<br>with external 32 kHz crystal enabled by means of the RTC_CR[OSCE]<br>bit and the RTC counter enabled. Includes EXTAL32 (32 kHz external<br>crystal) power consumption.              | 312 nA  |

| I <sub>LPUART</sub> | LPUART peripheral adder measured by placing the device in VLPS<br>mode with selected clock source waiting for RX data at 115200 baud<br>rate. Includes selected clock source power consumption. (SIRC 8 MHz)                                            | 79 µA   |

| I <sub>FTM</sub>    | FTM peripheral adder measured by placing the device in VLPW mode with selected clock source, outputting the edge aligned PWM of 100 Hz frequency.                                                                                                       | 45 µA   |

Table continues on the next page ...

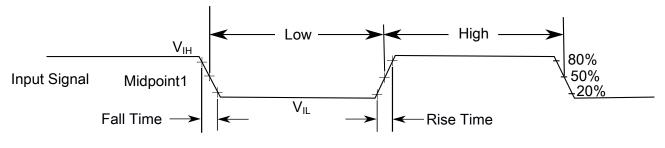

## 5.3.2.2 AC electrical characteristics

Unless otherwise specified, propagation delays are measured from the 50% to the 50% point, and rise and fall times are measured at the 20% and 80% points, as shown in the following figure.

The midpoint is  $V_{IL}$  + ( $V_{IH}$  -  $V_{IL}$ ) / 2

#### Figure 16. Input signal measurement reference

All digital I/O switching characteristics, unless otherwise specified, assume that the output pins have the following characteristics.

- $C_L=30 \text{ pF loads}$

- Normal drive strength

## 5.3.2.3 General AC specifications

These general purpose specifications apply to all signals configured for GPIO, UART, and timers.

| Symbol | Description                                                                                                        | Min. | Max. | Unit                | Notes |

|--------|--------------------------------------------------------------------------------------------------------------------|------|------|---------------------|-------|

|        | GPIO pin interrupt pulse width (digital glitch filter disabled) — Synchronous path                                 | 1.5  | —    | Bus clock<br>cycles | 1, 2  |

|        | External RESET and NMI pin interrupt pulse width — Asynchronous path                                               | 100  | —    | ns                  | 3     |

|        | GPIO pin interrupt pulse width (digital glitch filter<br>disabled, passive filter disabled) — Asynchronous<br>path | 50   | _    | ns                  | 4     |

Table 36.

General switching specifications

1. This is the minimum pulse width that is guaranteed to pass through the pin synchronization circuitry. Shorter pulses may or may not be recognized. In Stop and VLPS modes, the synchronizer is bypassed so shorter pulses can be recognized in that case.

- 2. The greater of synchronous and asynchronous timing must be met.

- 3. These pins have a passive filter enabled on the inputs. This is the shortest pulse width that is guaranteed to be recognized.

- 4. These pins do not have a passive filter on the inputs. This is the shortest pulse width that is guaranteed to be recognized.

#### 5.3.2.4 AC specifications at 3.3 V range Table 37. Functional pad AC specifications

| Characteristic     | Symbol           | Min | Тур | Мах | Unit |

|--------------------|------------------|-----|-----|-----|------|

| I/O Supply Voltage | Vdd <sup>1</sup> | 2.7 |     | 4   | V    |

1. Max power supply ramp rate is 500 V/ms.

| Name                    | Prop Delay (ns) <sup>1</sup> | Rise/Fall I | Drive Load (pF) |     |

|-------------------------|------------------------------|-------------|-----------------|-----|

|                         | Max                          | Min         | Max             |     |

| Normal drive I/O pad    | 17.5                         | 5           | 17              | 25  |

|                         | 28                           | 9           | 32              | 50  |

| High drive I/O pad      | 19                           | 5           | 17              | 25  |

|                         | 26                           | 9           | 33              | 50  |

| CMOS Input <sup>3</sup> | 4                            | 1.2         | 3               | 0.5 |

1. Propagation delay measured from 50% of core side input to 50% of the output.

2. Edges measured using 20% and 80% of the VDD supply.

3. Input slope = 2 ns.

#### NOTE

All measurements were taken accounting for 150 mV drop across VDD and VSS.

#### 5.3.2.5 AC specifications at 5 V range Table 38. Functional pad AC specifications

| Characteristic     | Symbol           | Min | Тур | Max | Unit |

|--------------------|------------------|-----|-----|-----|------|

| I/O Supply Voltage | Vdd <sup>1</sup> | 4   |     | 5.5 | V    |

1. Max power supply ramp rate is 500 V/ms.

| Name                    | Prop Delay (ns) <sup>1</sup> | Rise/Fall I | Drive Load (pF) |        |  |    |

|-------------------------|------------------------------|-------------|-----------------|--------|--|----|

|                         | Max                          | Min         | Max             |        |  |    |

| Normal drive I/O pad    | 12                           | 3.6 10      |                 | 3.6 10 |  | 25 |

|                         | 18                           | 8           | 17              | 50     |  |    |

| High drive I/O pad      | 13                           | 3.6         | 10              | 25     |  |    |

|                         | 19                           | 8           | 19              | 50     |  |    |

| CMOS Input <sup>3</sup> | 3                            | 1.2         | 2.8             | 0.5    |  |    |

1. As measured from 50% of core side input to 50% of the output.

2. Edges measured using 20% and 80% of the VDD supply.

3. Input slope = 2 ns.

## NOTE

All measurements were taken accounting for 150 mV drop across VDD and VSS.

## 5.3.3 Thermal specifications

#### 5.3.3.1 Thermal operating requirements Table 39. Thermal operating requirements

| Symbol         | Description              | Min. | Max. | Unit | Notes |

|----------------|--------------------------|------|------|------|-------|

| TJ             | Die junction temperature | -40  | 125  | °C   |       |

| T <sub>A</sub> | Ambient temperature      | -40  | 105  | °C   | 1     |

1. Maximum  $T_A$  can be exceeded only if the user ensures that  $T_J$  does not exceed maximum  $T_J$ . The simplest method to determine  $T_J$  is:  $T_J = T_A + R_{\odot JA} \times chip$  power dissipation.

## 5.3.3.2 Thermal attributes

#### 5.3.3.2.1 Description

The tables in the following sections describe the thermal characteristics of the device.

## NOTE

Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting side (board) temperature, ambient temperature, air flow, power dissipation or other components on the board, and board thermal resistance.

#### 5.3.3.2.2 Thermal characteristics for the 64-pin LQFP package Table 40. Thermal characteristics for the 64-pin LQFP package

| Rating                                                                          | Conditions              | Symbol            | Value | Unit |

|---------------------------------------------------------------------------------|-------------------------|-------------------|-------|------|

| Thermal resistance, Junction to Ambient (Natural Convection) <sup>1, 2</sup>    | Single layer board (1s) | R <sub>θJA</sub>  | 62    | °C/W |

| Thermal resistance, Junction to Ambient<br>(Natural Convection) <sup>1, 2</sup> | Four layer board (2s2p) | R <sub>θJA</sub>  | 44    | °C/W |

| Thermal resistance, Junction to Ambient<br>(@200 ft/min) <sup>1, 3</sup>        | Single layer board (1s) | R <sub>θJMA</sub> | 50    | °C/W |

Table continues on the next page ...

| Rating                                                                | Conditions              | Symbol            | Value | Unit |

|-----------------------------------------------------------------------|-------------------------|-------------------|-------|------|

| Thermal resistance, Junction to Ambient (@200 ft/min) <sup>1, 3</sup> | Four layer board (2s2p) | R <sub>θJMA</sub> | 37    | °C/W |

| Thermal resistance, Junction to Board <sup>4</sup>                    | _                       | R <sub>θJB</sub>  | 26    | °C/W |

| Thermal resistance, Junction to Case <sup>5</sup>                     | —                       | R <sub>θJC</sub>  | 14    | °C/W |

| Thermal resistance, Junction to Package Top <sup>6</sup>              | Natural Convection      | ΨJT               | 2     | °C/W |

#### Table 40. Thermal characteristics for the 64-pin LQFP package (continued)

- 1. Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, air flow, power dissipation of other components on the board, and board thermal resistance.

- 2. Per JEDEC JESD51-2 with natural convection for horizontally oriented board. Board meets JESD51-9 specification for 1s or 2s2p board, respectively.

- 3. Per JEDEC JESD51-6 with forced convection for horizontally oriented board. Board meets JESD51-9 specification for 1s or 2s2p board, respectively.

- 4. Thermal resistance between the die and the printed circuit board per JEDEC JESD51-8. Board temperature is measured on the top surface of the board near the package.

- 5. Thermal resistance between the die and the case top surface as measured by the cold plate method (MIL SPEC-883 Method 1012.1).

- 6. Thermal characterization parameter indicating the temperature difference between package top and the junction temperature per JEDEC JESD51-2.

#### 5.3.3.2.3 Thermal characteristics for the 100-pin LQFP package Table 41. Thermal characteristics for the 100-pin LQFP package

| Rating                                                                          | Conditions              | Symbol            | Value | Unit |

|---------------------------------------------------------------------------------|-------------------------|-------------------|-------|------|

| Thermal resistance, Junction to Ambient (Natural Convection) <sup>1, 2</sup>    | Single layer board (1s) | R <sub>θJA</sub>  | 59    | °C/W |

| Thermal resistance, Junction to Ambient<br>(Natural Convection) <sup>1, 2</sup> | Four layer board (2s2p) | R <sub>θJA</sub>  | 46    | °C/W |

| Thermal resistance, Junction to Ambient<br>(@200 ft/min) <sup>1, 3</sup>        | Single layer board (1s) | R <sub>θJMA</sub> | 49    | °C/W |

| Thermal resistance, Junction to Ambient<br>(@200 ft/min) <sup>1, 3</sup>        | Four layer board (2s2p) | R <sub>θJMA</sub> | 40    | °C/W |

| Thermal resistance, Junction to Board <sup>4</sup>                              | _                       | R <sub>θJB</sub>  | 31    | °C/W |

| Thermal resistance, Junction to Case <sup>5</sup>                               | —                       | R <sub>θJC</sub>  | 16    | °C/W |

| Thermal resistance, Junction to Package Top <sup>6</sup>                        | Natural Convection      | ΨJT               | 2     | °C/W |

- 1. Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, air flow, power dissipation of other components on the board, and board thermal resistance.

- 2. Per JEDEC JESD51-2 with natural convection for horizontally oriented board. Board meets JESD51-9 specification for 1s or 2s2p board, respectively.

- 3. Per JEDEC JESD51-6 with forced convection for horizontally oriented board. Board meets JESD51-9 specification for 1s or 2s2p board, respectively.

- 4. Thermal resistance between the die and the printed circuit board per JEDEC JESD51-8. Board temperature is measured on the top surface of the board near the package.

- 5. Thermal resistance between the die and the case top surface as measured by the cold plate method (MIL SPEC-883 Method 1012.1).

6. Thermal characterization parameter indicating the temperature difference between package top and the junction temperature per JEDEC JESD51-2.

#### 5.3.3.2.4 General notes for specifications at maximum junction temperature

An estimation of the chip junction temperature, T<sub>J</sub>, can be obtained from this equation:

$T_J = T_A + (R_{\theta JA} \times P_D)$

where:

- $T_A$  = ambient temperature for the package (°C)

- $R_{\theta JA}$  = junction to ambient thermal resistance (°C/W)

- $P_D$  = power dissipation in the package (W)

The junction to ambient thermal resistance is an industry standard value that provides a quick and easy estimation of thermal performance. Unfortunately, there are two values in common usage: the value determined on a single layer board and the value obtained on a board with two planes. For packages such as the PBGA, these values can be different by a factor of two. Which value is closer to the application depends on the power dissipated by other components on the board. The value obtained on a single layer board is appropriate for the tightly packed printed circuit board. The value obtained on the board with the internal planes is usually appropriate if the board has low power dissipation and the components are well separated.

When a heat sink is used, the thermal resistance is expressed in the following equation as the sum of a junction-to-case thermal resistance and a case-to-ambient thermal resistance:

$R_{\theta JA} = R_{\theta JC} + R_{\theta CA}$

where:

- $R_{\theta JA}$  = junction to ambient thermal resistance (°C/W)

- $R_{\theta JC}$  = junction to case thermal resistance (°C/W)

- $R_{\theta CA}$  = case to ambient thermal resistance (°C/W)

$R_{\theta JC}$  is device related and cannot be influenced by the user. The user controls the thermal environment to change the case to ambient thermal resistance,  $R_{\theta CA}$ . For instance, the user can change the size of the heat sink, the air flow around the device, the interface material, the mounting arrangement on printed circuit board, or change the thermal dissipation on the printed circuit board surrounding the device.

#### NOTE:

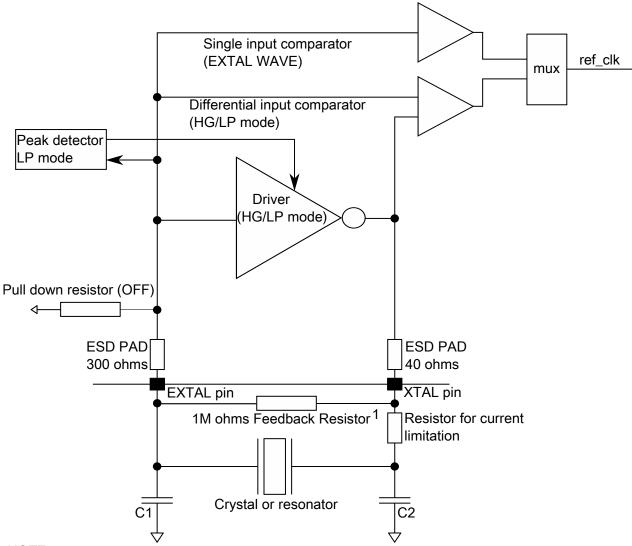

1. 1M Feedback resistor is needed only for HG mode.

#### Figure 18. Oscillator connections scheme (OSC)

#### NOTE

Data values in the following "External Oscillator electrical specifications" tables are from simulation.

#### Table 42. External Oscillator electrical specifications (OSC32)

| Symbol             | Description                                 | Min. | Тур. | Max. | Unit | Notes |

|--------------------|---------------------------------------------|------|------|------|------|-------|

| V <sub>DD</sub>    | Supply voltage                              | 2.7  | —    | 5.5  | V    |       |

| I <sub>DDOSC</sub> | Supply current                              | —    | 25   | —    | μA   | 1     |

| 9 <sub>mXOSC</sub> | Oscillator transconductance                 | 6    | _    | 9    | μA/V |       |

| V <sub>EXTAL</sub> | EXTAL32 input voltage — external clock mode | 0    | —    | 3.6  | V    |       |

Table continues on the next page...

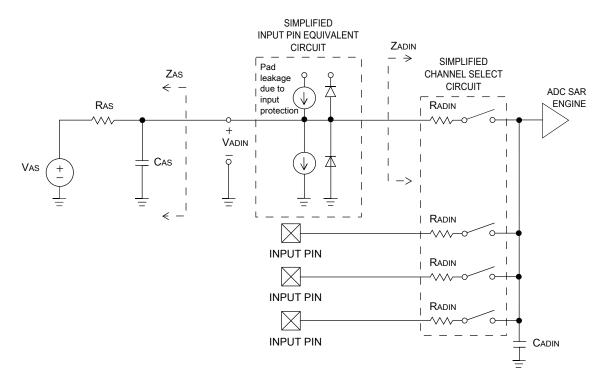

Figure 19. ADC input impedance equivalency diagram

#### 5.4.5.1.2 12-bit ADC electrical characteristics

## NOTE

All the parameters in the table are given assuming system clock as the clocking source for ADC.

## NOTE

For ADC signals adjacent to VDD/VSS or the XTAL pins some degradation in the ADC performance may be observed.

## NOTE

All values guarantee the performance of the ADC for the multiple ADC input channel pins. When using the ADC to monitor the internal analogue parameters, please assume minor degradation.

Table 55. 12-bit ADC characteristics ( $V_{REFH} = V_{DDA}$ ,  $V_{REFL} = V_{SSA}$ )

| Symbol               | Description                       | Conditions <sup>1</sup> | Min. | Typ. <sup>2</sup> | Max. <sup>3</sup> | Unit | Notes |

|----------------------|-----------------------------------|-------------------------|------|-------------------|-------------------|------|-------|

| I <sub>DDA_ADC</sub> | Supply current at 2.7<br>to 5.5 V |                         | 927  | 975 μA @<br>5 V   | 1023              | mA   | 4     |

Table continues on the next page ...

#### **Electrical characteristics**

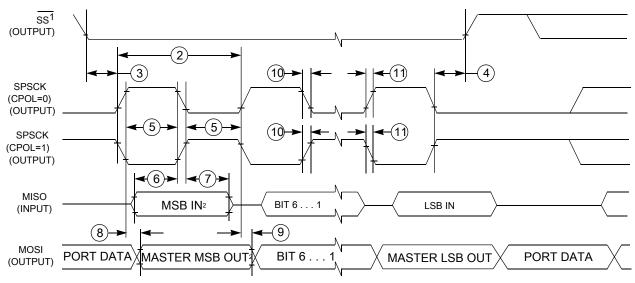

1.If configured as output

2. LSBF = 0. For LSBF = 1, bit order is LSB, bit 1, ..., bit 6, MSB.

#### Figure 25. LPSPI master mode timing (CPHA = 1)

| Num. | Symbol              | Description                    | Min.                     | Max.                     | Unit                | Note |

|------|---------------------|--------------------------------|--------------------------|--------------------------|---------------------|------|

| 1    | f <sub>op</sub>     | Frequency of operation         | 0                        | f <sub>periph</sub> /4   | Hz                  | 1    |

| 2    | t <sub>SPSCK</sub>  | SPSCK period                   | 4 x t <sub>periph</sub>  | —                        | ns                  | 2    |

| 3    | t <sub>Lead</sub>   | Enable lead time               | 1                        | —                        | t <sub>periph</sub> |      |

| 4    | t <sub>Lag</sub>    | Enable lag time                | 1                        | —                        | t <sub>periph</sub> |      |

| 5    | t <sub>WSPSCK</sub> | Clock (SPSCK) high or low time | t <sub>periph</sub> - 30 | —                        | ns                  |      |

| 6    | t <sub>SU</sub>     | Data setup time (inputs)       | 2.5                      | —                        | ns                  | —    |

| 7    | t <sub>HI</sub>     | Data hold time (inputs)        | 3.5                      | —                        | ns                  | —    |

| 8    | t <sub>a</sub>      | Slave access time              | —                        | t <sub>periph</sub>      | ns                  | 3    |

| 9    | t <sub>dis</sub>    | Slave MISO disable time        | _                        | t <sub>periph</sub>      | ns                  | 4    |

| 10   | t <sub>v</sub>      | Data valid (after SPSCK edge)  | _                        | 31                       | ns                  | —    |

| 11   | t <sub>HO</sub>     | Data hold time (outputs)       | 0                        | —                        | ns                  | —    |

| 12   | t <sub>RI</sub>     | Rise time input                | —                        | t <sub>periph</sub> - 25 | ns                  | —    |

|      | t <sub>FI</sub>     | Fall time input                | ]                        |                          |                     |      |

| 13   | t <sub>RO</sub>     | Rise time output               | _                        | 25                       | ns                  | —    |

|      | t <sub>FO</sub>     | Fall time output               | ]                        |                          |                     |      |

#### Table 58. LPSPI slave mode timing

- 1.  $f_{periph} = LPSPI$  peripheral clock

- 2.

- $t_{periph} = 1/f_{periph}$ Time to data active from high-impedance state З.

- 4. Hold time to high-impedance state

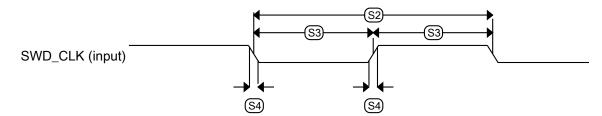

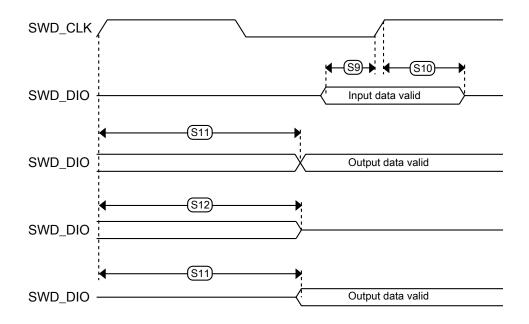

| Symbol | Description                                     | Min. | Max. | Unit |

|--------|-------------------------------------------------|------|------|------|

| S2     | SWD_CLK cycle period                            | 1/S1 | —    | ns   |

| S3     | SWD_CLK clock pulse width                       | 15   | —    | ns   |

| S4     | SWD_CLK rise and fall times                     | _    | 3    | ns   |

| S9     | SWD_DIO input data setup time to SWD_CLK rise   | 8    | —    | ns   |

| S10    | SWD_DIO input data hold time after SWD_CLK rise | 1.4  | —    | ns   |

| S11    | SWD_CLK high to SWD_DIO data valid              |      | 25   | ns   |

| S12    | SWD_CLK high to SWD_DIO high-Z                  | 5    | —    | ns   |

Table 61. SWD full voltage range electricals (continued)

Figure 28. Serial wire clock input timing

Figure 29. Serial wire data timing

# 6 Design considerations

Kinetis KE1xZ with up to 256 KB Flash, Rev. 2, 09/2016