# E·XFL

#### NXP USA Inc. - MKE15Z128VLL7 Datasheet

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                      |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 72MHz                                                                 |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART                             |

| Peripherals                | DMA, LVD, PWM, WDT                                                    |

| Number of I/O              | 89                                                                    |

| Program Memory Size        | 128KB (128K x 8)                                                      |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 16K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                           |

| Data Converters            | A/D 16x12b; D/A 1x8b                                                  |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 100-LQFP                                                              |

| Supplier Device Package    | 100-LQFP (14x14)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mke15z128vll7 |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 2.1.1 ARM Cortex-M0+ core

The enhanced ARM Cortex M0+ is the member of the Cortex-M Series of processors targeting microcontroller cores focused on very cost sensitive, low power applications. It has a single 32-bit AMBA AHB-Lite interface and includes an NVIC component. It also has hardware debug functionality including support for simple program trace capability. The processor supports the ARMv6-M instruction set (Thumb) architecture including all but three 16-bit Thumb opcodes (52 total) plus seven 32-bit instructions. It is upward compatible with other Cortex-M profile processors.

# 2.1.2 NVIC

The Nested Vectored Interrupt Controller supports nested interrupts and 4 priority levels for interrupts. In the NVIC, each source in the IPR registers contains 2 bits. It also differs in number of interrupt sources and supports 32 interrupt vectors.

The Cortex-M family uses a number of methods to improve interrupt latency to up to 15 clock cycles for Cortex-M0+. It also can be used to wake the MCU core from Wait and VLPW modes.

## 2.1.3 AWIC

The asynchronous wake-up interrupt controller (AWIC) is used to detect asynchronous wake-up events in Stop mode and signal to clock control logic to resume system clocking. After clock restarts, the NVIC observes the pending interrupt and performs the normal interrupt or event processing. The AWIC can be used to wake MCU core from Partial Stop, Stop and VLPS modes.

Wake-up sources for this SoC are listed as below:

| Wake-up source          | Description                                                                     |

|-------------------------|---------------------------------------------------------------------------------|

| Available system resets | RESET pin, WDOG , loss of clock(LOC) reset and loss of lock (LOL) reset         |

| Pin interrupts          | Port Control Module - Any enabled pin interrupt is capable of waking the system |

| ADCx                    | ADCx is optional functional with clock source from SIRC or OSC                  |

| CMPx                    | Functional in Stop/VLPS modes with clock source from SIRC or OSC                |

| LPI2C                   | Functional in Stop/VLPS modes with clock source from SIRC or OSC                |

| LPUART                  | Functional in Stop/VLPS modes with clock source from SIRC or OSC                |

Table 2. AWIC Stop and VLPS Wake-up Sources

Table continues on the next page...

| Wake-up source | Description                                                      |

|----------------|------------------------------------------------------------------|

| LPSPI          | Functional in Stop/VLPS modes with clock source from SIRC or OSC |

| LPIT           | Functional in Stop/VLPS modes with clock source from SIRC or OSC |

| FlexIO         | Functional in Stop/VLPS modes with clock source from SIRC or OSC |

| LPTMR          | Functional in Stop/VLPS modes                                    |

| RTC            | Functional in Stop/VLPS modes                                    |

| SCG            | Functional in Stop mode (Only SIRC)                              |

| TSI            | Touch sense wakeup                                               |

| NMI            | Non-maskable interrupt                                           |

#### Table 2. AWIC Stop and VLPS Wake-up Sources (continued)

## 2.1.4 Memory

This device has the following features:

- Upto 256 KB of embedded program flash memory.

- Upto 32 KB of embedded RAM accessible (read/write) at CPU clock speed with 0 wait states.

- The non-volatile memory is divided into several arrays:

- 32 KB of embedded data flash memory

- 2 KB of Emulated EEPROM

- 8 KB ROM (built-in bootloader to support UART, I2C, and SPI interfaces)

The program flash memory contains a 16-byte flash configuration field that stores default protection settings and security information. The page size of program flash is 1 KB.

The protection setting can protect 32 regions of the program flash memory from unintended erase or program operations.

The security circuitry prevents unauthorized access to RAM or flash contents from debug port.

## 2.1.5 Reset and boot

The following table lists all the reset sources supported by this device.

## NOTE

In the following table, Y means the specific module, except for the registers, bits or conditions mentioned in the footnote, is reset by the corresponding Reset source. N means the specific module is not reset by the corresponding Reset source.

| Reset            | Descriptions                                                 | Modules        |                |                |                |                            |                |                |     |           |            |

|------------------|--------------------------------------------------------------|----------------|----------------|----------------|----------------|----------------------------|----------------|----------------|-----|-----------|------------|

| sources          |                                                              | РМС            | SIM            | SMC            | RCM            | Reset<br>pin is<br>negated | WDO<br>G       | SCG            | RTC | LPTM<br>R | Other<br>s |

| POR reset        | Power-on reset (POR)                                         | Y              | Y              | Y              | Y              | Y                          | Y              | Y              | Y   | Y         | Y          |

| System<br>resets | Low-voltage detect<br>(LVD)                                  | Y <sup>1</sup> | Y              | Y              | Y              | Y                          | Y              | Y              | Ν   | Y         | Y          |

|                  | External pin reset<br>(RESET)                                | Y <sup>1</sup> | Y <sup>2</sup> | Y <sup>3</sup> | Y <sup>4</sup> | Y                          | Y <sup>5</sup> | Y <sup>6</sup> | Ν   | N         | Y          |

|                  | Watchdog (WDOG)<br>reset                                     | Y <sup>1</sup> | Y <sup>2</sup> | Y <sup>3</sup> | Y <sup>4</sup> | Y                          | Y <sup>5</sup> | Y <sup>6</sup> | Ν   | N         | Y          |

|                  | Multipurpose clock<br>generator loss of clock<br>(LOC) reset | Y <sup>1</sup> | Y <sup>2</sup> | Y <sup>3</sup> | Y <sup>4</sup> | Y                          | Y <sup>5</sup> | Y <sup>6</sup> | Ν   | N         | Y          |

|                  | Multipurpose clock<br>generator loss of lock<br>(LOL) reset  | Y <sup>1</sup> | Y <sup>2</sup> | Y <sup>3</sup> | Y <sup>4</sup> | Y                          | Y <sup>5</sup> | Y <sup>6</sup> | Ν   | N         | Y          |

|                  | Stop mode acknowledge error (SACKERR)                        | Y <sup>1</sup> | Y <sup>2</sup> | Y <sup>3</sup> | Y <sup>4</sup> | Y                          | Y <sup>5</sup> | Y <sup>6</sup> | Ν   | N         | Y          |

|                  | Software reset (SW)                                          | Y <sup>1</sup> | Y <sup>2</sup> | Y <sup>3</sup> | Y <sup>4</sup> | Y                          | Y <sup>5</sup> | Y <sup>6</sup> | Ν   | N         | Y          |

|                  | Lockup reset (LOCKUP)                                        | Y <sup>1</sup> | Y <sup>2</sup> | Y <sup>3</sup> | Y <sup>4</sup> | Y                          | Y <sup>5</sup> | Y <sup>6</sup> | Ν   | Ν         | Y          |

|                  | MDM DAP system reset                                         | Y <sup>1</sup> | Y <sup>2</sup> | Y <sup>3</sup> | Y <sup>4</sup> | Y                          | Y <sup>5</sup> | Y <sup>6</sup> | Ν   | Ν         | Y          |

| Debug reset      | Debug reset                                                  | Y <sup>1</sup> | Y <sup>2</sup> | Y <sup>3</sup> | Y <sup>4</sup> | Y                          | Y <sup>5</sup> | Y <sup>6</sup> | Ν   | N         | Y          |

Table 3.Reset source

1. Except PMC\_LVDSC1[LVDV] and PMC\_LVDSC2[LVWV]

- 2. Except SIM\_SOPT1

- 3. Except SMC\_PMPROT, SMC\_PMCTRL\_RUM, SMC\_PMCTRL\_STOPM, SMC\_STOPCTRL, SMC\_PMSTAT

- 4. Except RCM\_RPC, RCM\_MR, RCM\_FM, RCM\_SRIE, RCM\_SRS, RCM\_SSRS

- 5. Except WDOG\_CS[TST]

- 6. Except SCG\_CSR and SCG\_FIRCSTAT

This device supports booting from:

- internal flash

- boot ROM

# 2.2.13 FlexIO

The FlexIO is a highly configurable module providing a wide range of protocols including, but not limited to UART, I2C, SPI, I2S, Camera IF, LCD RGB, PWM/ Waveform generation. The module supports programmable baud rates independent of bus clock frequency, with automatic start/stop bit generation.

The FlexIO module has the following features:

- Functional in VLPR/VLPW/Stop/VLPS mode provided the clock it is using remains enabled

- Four 32-bit double buffered shift registers with transmit, receive, and data match modes, and continuous data transfer

- The timing of the shifter's shift, load and store events are controlled by the highly flexible 16-bit timer assigned to the shifter

- Two or more shifters can be concatenated to support large data transfer sizes

- Each 16-bit timers operates independently, supports for reset, enable and disable on a variety of internal or external trigger conditions with programmable trigger polarity

- Flexible pin configuration supporting output disabled, open drain, bidirectional output data and output mode

- Supports interrupt, DMA or polled transmit/receive operation

# 2.2.14 Port control and GPIO

The Port Control and Interrupt (PORT) module provides support for port control, digital filtering, and external interrupt functions. The GPIO data direction and output data registers control the direction and output data of each pin when the pin is configured for the GPIO function. The GPIO input data register displays the logic value on each pin when the pin is configured for any digital function, provided the corresponding Port Control and Interrupt module for that pin is enabled.

The following figure shows the basic I/O pad structure. Pseudo open-drain pins have the p-channel output driver disabled when configured for open-drain operation. None of the I/O pins, including open-drain and pseudo open-drain pins, are allowed to go above VDD.

## NOTE

The RESET\_b pin is also a normal I/O pad with pseudo opendrain.

| 100<br>LQFP | 64<br>LQFP | Pin Name | Default                              | ALTO                                 | ALT1  | ALT2       | ALT3            | ALT4      | ALT5    | ALT6            | ALT7       |

|-------------|------------|----------|--------------------------------------|--------------------------------------|-------|------------|-----------------|-----------|---------|-----------------|------------|

| 10          | 7          | VDD      | VDD                                  | VDD                                  |       |            |                 |           |         |                 |            |

| 11          | 8          | VDDA     | VDDA                                 | VDDA                                 |       |            |                 |           |         |                 |            |

| 12          | 9          | VREFH    | VREFH                                | VREFH                                |       |            |                 |           |         |                 |            |

| 13          | _          | VREFL    | VREFL                                | VREFL                                |       |            |                 |           |         |                 |            |

| 14          | _          | VSS      | VSS                                  | VSS                                  |       |            |                 |           |         |                 |            |

| 15          | 11         | PTB7     | EXTAL                                | EXTAL                                | PTB7  | LPI2C0_SCL |                 |           |         |                 |            |

| 16          | 12         | PTB6     | XTAL                                 | XTAL                                 | PTB6  | LPI2C0_SDA |                 |           |         |                 |            |

| 17          | _          | PTE14    | DISABLED                             |                                      | PTE14 | FTM0_FLT1  |                 |           |         |                 |            |

| 18          | 13         | PTE3     | TSI0_CH24                            | TSI0_CH24                            | PTE3  | FTM0_FLT0  | LPUART2_<br>RTS |           |         | TRGMUX_IN6      |            |

| 19          | _          | PTE12    | DISABLED                             |                                      | PTE12 | FTM0_FLT3  | LPUART2_TX      |           |         |                 |            |

| 20          | _          | PTD17    | DISABLED                             |                                      | PTD17 | FTM0_FLT2  | LPUART2_RX      |           |         |                 |            |

| 21          | 14         | PTD16    | DISABLED                             |                                      | PTD16 | FTM0_CH1   |                 |           |         |                 |            |

| 22          | 15         | PTD15    | DISABLED                             |                                      | PTD15 | FTM0_CH0   |                 |           |         |                 |            |

| 23          | 16         | PTE9     | DAC0_OUT                             | DAC0_OUT                             | PTE9  | FTM0_CH7   | LPUART2_<br>CTS |           |         |                 |            |

| 24          | —          | PTD14    | DISABLED                             |                                      | PTD14 |            |                 |           |         |                 | CLKOUT     |

| 25          | _          | PTD13    | DISABLED                             |                                      | PTD13 |            |                 |           |         |                 | RTC_CLKOUT |

| 26          | 17         | PTE8     | ACMP0_IN3/<br>TSI0_CH11              | ACMP0_IN3/<br>TSI0_CH11              | PTE8  | FTM0_CH6   |                 |           |         |                 |            |

| 27          | 18         | PTB5     | TSI0_CH9                             | TSI0_CH9                             | PTB5  | FTM0_CH5   | LPSPI0_PCS1     |           |         | TRGMUX_IN0      | ACMP1_OUT  |

| 28          | 19         | PTB4     | ACMP1_IN2/<br>TSI0_CH8               | ACMP1_IN2/<br>TSI0_CH8               | PTB4  | FTM0_CH4   | LPSPI0_SOUT     |           |         | TRGMUX_IN1      |            |

| 29          | 20         | PTC3     | ADC0_SE11/<br>ACMP0_IN4/<br>EXTAL32  | ADC0_SE11/<br>ACMP0_IN4/<br>EXTAL32  | PTC3  | FTM0_CH3   |                 |           |         |                 |            |

| 30          | 21         | PTC2     | ADC0_SE10/<br>ACMP0_IN5/<br>XTAL32   | ADC0_SE10/<br>ACMP0_IN5/<br>XTAL32   | PTC2  | FTM0_CH2   |                 |           |         |                 |            |

| 31          | 22         | PTD7     | TSI0_CH10                            | TSI0_CH10                            | PTD7  | LPUART2_TX |                 | FTM2_FLT3 |         |                 |            |

| 32          | 23         | PTD6     | TSI0_CH7                             | TSI0_CH7                             | PTD6  | LPUART2_RX |                 | FTM2_FLT2 |         |                 |            |

| 33          | 24         | PTD5     | TSI0_CH6                             | TSI0_CH6                             | PTD5  | FTM2_CH3   | LPTMR0_<br>ALT2 |           | PWT_IN2 | TRGMUX_IN7      |            |

| 34          | _          | PTD12    | DISABLED                             |                                      | PTD12 | FTM2_CH2   | LPI2C1_HREQ     |           |         | LPUART2_<br>RTS |            |

| 35          | —          | PTD11    | DISABLED                             |                                      | PTD11 | FTM2_CH1   | FTM2_QD_<br>PHA |           |         | LPUART2_<br>CTS |            |

| 36          | _          | PTD10    | DISABLED                             |                                      | PTD10 | FTM2_CH0   | FTM2_QD_<br>PHB |           |         |                 |            |

| 37          | -          | VSS      | VSS                                  | VSS                                  |       |            |                 |           |         |                 |            |

| 38          | -          | VDD      | VDD                                  | VDD                                  |       |            |                 |           |         |                 |            |

| 39          | 25         | PTC1     | ADC0_SE9/<br>ACMP1_IN3/<br>TSI0_CH23 | ADC0_SE9/<br>ACMP1_IN3/<br>TSI0_CH23 | PTC1  | FTM0_CH1   |                 |           |         |                 |            |

#### Pinouts

| 100<br>LQFP | 64<br>LQFP | Pin Name | Default                              | ALT0                                 | ALT1  | ALT2       | ALT3        | ALT4            | ALT5    | ALT6            | ALT7  |

|-------------|------------|----------|--------------------------------------|--------------------------------------|-------|------------|-------------|-----------------|---------|-----------------|-------|

| 40          | 26         | PTC0     | ADC0_SE8/<br>ACMP1_IN4/<br>TSI0_CH22 | ADC0_SE8/<br>ACMP1_IN4/<br>TSI0_CH22 | PTC0  | FTM0_CH0   |             |                 |         |                 |       |

| 41          | -          | PTD9     | ACMP1_IN5                            | ACMP1_IN5                            | PTD9  | LPI2C1_SCL |             | FTM2_FLT3       |         |                 |       |

| 42          | -          | PTD8     | DISABLED                             |                                      | PTD8  | LPI2C1_SDA |             | FTM2_FLT2       |         |                 |       |

| 43          | 27         | PTC17    | ADC0_SE15                            | ADC0_SE15                            | PTC17 | FTM1_FLT3  |             | LPI2C1_SCLS     |         |                 |       |

| 44          | 28         | PTC16    | ADC0_SE14                            | ADC0_SE14                            | PTC16 | FTM1_FLT2  |             | LPI2C1_SDAS     |         |                 |       |

| 45          | 29         | PTC15    | ADC0_SE13                            | ADC0_SE13                            | PTC15 | FTM1_CH3   |             |                 |         |                 |       |

| 46          | 30         | PTC14    | ADC0_SE12                            | ADC0_SE12                            | PTC14 | FTM1_CH2   |             |                 |         |                 |       |

| 47          | 31         | PTB3     | ADC0_SE7/<br>TSI0_CH21               | ADC0_SE7/<br>TSI0_CH21               | PTB3  | FTM1_CH1   | LPSPI0_SIN  | FTM1_QD_<br>PHA |         | TRGMUX_IN2      |       |

| 48          | 32         | PTB2     | ADC0_SE6/<br>TSI0_CH20               | ADC0_SE6/<br>TSI0_CH20               | PTB2  | FTM1_CH0   | LPSPI0_SCK  | FTM1_QD_<br>PHB |         | TRGMUX_IN3      |       |

| 49          | -          | PTC13    | DISABLED                             |                                      | PTC13 |            |             |                 |         |                 |       |

| 50          | -          | PTC12    | DISABLED                             |                                      | PTC12 |            |             |                 |         |                 |       |

| 51          | _          | PTC11    | DISABLED                             |                                      | PTC11 |            |             |                 |         |                 |       |

| 52          | _          | PTC10    | DISABLED                             |                                      | PTC10 |            |             |                 |         |                 |       |

| 53          | 33         | PTB1     | ADC0_SE5                             | ADC0_SE5                             | PTB1  | LPUART0_TX | LPSPI0_SOUT | TCLK0           |         |                 |       |

| 54          | 34         | PTB0     | ADC0_SE4                             | ADC0_SE4                             | PTB0  | LPUART0_RX | LPSPI0_PCS0 | LPTMR0_<br>ALT3 | PWT_IN3 |                 |       |

| 55          | 35         | PTC9     | DISABLED                             |                                      | PTC9  | LPUART1_TX |             |                 |         | LPUART0_<br>RTS |       |

| 56          | 36         | PTC8     | DISABLED                             |                                      | PTC8  | LPUART1_RX |             |                 |         | LPUART0_<br>CTS |       |

| 57          | 37         | PTA7     | ADC0_SE3/<br>ACMP1_IN1               | ADC0_SE3/<br>ACMP1_IN1               | PTA7  | FTM0_FLT2  |             | RTC_CLKIN       |         | LPUART1_<br>RTS |       |

| 58          | 38         | PTA6     | ADC0_SE2/<br>ACMP1_IN0               | ADC0_SE2/<br>ACMP1_IN0               | PTA6  | FTM0_FLT1  | LPSPI1_PCS1 |                 |         | LPUART1_<br>CTS |       |

| 59          | 39         | PTE7     | DISABLED                             |                                      | PTE7  | FTM0_CH7   |             |                 |         |                 |       |

| 60          | 40         | VSS      | VSS                                  | VSS                                  |       |            |             |                 |         |                 |       |

| 61          | 41         | VDD      | VDD                                  | VDD                                  |       |            |             |                 |         |                 |       |

| 62          | -          | PTA17    | DISABLED                             |                                      | PTA17 | FTM0_CH6   |             | EWM_OUT_b       |         |                 |       |

| 63          | -          | PTB17    | DISABLED                             |                                      | PTB17 | FTM0_CH5   | LPSPI1_PCS3 |                 |         |                 |       |

| 64          | -          | PTB16    | DISABLED                             |                                      | PTB16 | FTM0_CH4   | LPSPI1_SOUT |                 |         |                 |       |

| 65          | -          | PTB15    | DISABLED                             |                                      | PTB15 | FTM0_CH3   | LPSPI1_SIN  |                 |         |                 |       |

| 66          | _          | PTB14    | ADC1_SE9                             | ADC1_SE9                             | PTB14 | FTM0_CH2   | LPSPI1_SCK  |                 |         |                 |       |

| 67          | 42         | PTB13    | ADC1_SE8                             | ADC1_SE8                             | PTB13 | FTM0_CH1   |             |                 |         |                 |       |

| 68          | 43         | PTB12    | ADC1_SE7                             | ADC1_SE7                             | PTB12 | FTM0_CH0   |             |                 |         |                 |       |

| 69          | 44         | PTD4     | ADC1_SE6                             | ADC1_SE6                             | PTD4  | FTM0_FLT3  |             |                 |         |                 |       |

| 70          | 45         | PTD3     | NMI_b                                | ADC1_SE3                             | PTD3  |            | LPSPI1_PCS0 | FXIO_D5         |         | TRGMUX_IN4      | NMI_b |

| 71          | 46         | PTD2     | ADC1_SE2                             | ADC1_SE2                             | PTD2  |            | LPSPI1_SOUT | FXIO_D4         |         | TRGMUX_IN5      |       |

| 72          | 47         | PTA3     | ADC1_SE1                             | ADC1_SE1                             | PTA3  |            | LPI2C0_SCL  | EWM_IN          |         | LPUART0_TX      |       |

## 4.3.1 Core Modules

| Table | 7. SWD Signal Descriptions |

|-------|----------------------------|

|       |                            |

| Chip signal name | Module signal<br>name | Description       | I/O |

|------------------|-----------------------|-------------------|-----|

| SWD_CLK          | SWD_CLK               | Serial Wire Clock | Ι   |

| SWD_DIO          | SWD_DIO               | Serial Wire Data  | I/O |

## 4.3.2 System Modules

## Table 8. System Signal Descriptions

| Chip signal name | Module signal<br>name | Description                                                                                                                                              | I/O |

|------------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| NMI_b            | _                     | Non-maskable interrupt NOTE: Driving the NMI signal low forces<br>a non-maskable interrupt, if the NMI function is selected on the<br>corresponding pin. | I   |

| RESET_b          | —                     | Reset bidirectional signal                                                                                                                               | I/O |

| VDD              |                       | MCU power                                                                                                                                                | I   |

| VSS              | _                     | MCU ground                                                                                                                                               | I   |

#### Table 9. EWM Signal Descriptions

| Chip signal name | Module signal<br>name | Description                                                                                                                                                        | I/O |

|------------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| EWM_IN           | EWM_in                | EWM input for safety status of external safety circuits. The polarity of EWM_IN is programmable using the EWM_CTRL[ASSIN] bit. The default polarity is active-low. | Ι   |

| EWM_OUT_b        | EWM_out               | EWM reset out signal                                                                                                                                               | 0   |

# 4.3.3 Clock Modules

#### Table 10. OSC (in SCG) Signal Descriptions

| Chip<br>signal<br>name | Module signal name | Description                     | I/O |

|------------------------|--------------------|---------------------------------|-----|

| EXTAL                  | EXTAL              | External clock/Oscillator input | I   |

| XTAL                   | XTAL               | Oscillator output               | 0   |

# **5** Electrical characteristics

# 5.1 Terminology and guidelines

## 5.1.1 Definitions

Key terms are defined in the following table:

| Term                  | Definition                                                                                                                                                                                                                          |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Rating                | A minimum or maximum value of a technical characteristic that, if exceeded, may cause permanent chip failure:                                                                                                                       |

|                       | <ul> <li>Operating ratings apply during operation of the chip.</li> <li>Handling ratings apply when the chip is not powered.</li> </ul>                                                                                             |

|                       | <b>NOTE:</b> The likelihood of permanent chip failure increases rapidly as soon as a characteristic begins to exceed one of its operating ratings.                                                                                  |

| Operating requirement | A specified value or range of values for a technical characteristic that you must guarantee during operation to avoid incorrect operation and possibly decreasing the useful life of the chip                                       |

| Operating behavior    | A specified value or range of values for a technical characteristic that are guaranteed during operation if you meet the operating requirements and any other specified conditions                                                  |

| Typical value         | A specified value for a technical characteristic that:                                                                                                                                                                              |

|                       | <ul> <li>Lies within the range of values specified by the operating behavior</li> <li>Is representative of that characteristic during operation when you meet the typical-value conditions or other specified conditions</li> </ul> |

|                       | <b>NOTE:</b> Typical values are provided as design guidelines and are neither tested nor guaranteed.                                                                                                                                |

| Symbol           | Parameter                                                  | Parameter Value |       |     |    | Notes |  |

|------------------|------------------------------------------------------------|-----------------|-------|-----|----|-------|--|

|                  | 1                                                          | Min             | Тур   | Max | 1  |       |  |

| I <sub>OLT</sub> | Output low current total for all ports                     | _               | _     | 100 | mA |       |  |

| I <sub>IN</sub>  | Input leakage current (per pin) for full temperatur        | re range        | ·     |     |    | 8, 7  |  |

|                  | @ V <sub>DD</sub> = 3.3 V                                  |                 |       |     |    |       |  |

|                  | All pins other than high drive port pins                   | _               | 0.002 | 0.5 | μA |       |  |

|                  | High drive port pins                                       | _               | 0.004 | 0.5 | μA |       |  |

|                  | Input leakage current (per pin) for full temperature range |                 |       |     |    |       |  |

|                  | @ V <sub>DD</sub> = 5.5 V                                  |                 |       |     |    |       |  |

|                  | All pins other than high drive port pins                   | —               | 0.005 | 0.5 | μA |       |  |

|                  | High drive port pins                                       | _               | 0.010 | 0.5 | μA |       |  |

| R <sub>PU</sub>  | Internal pull-up resistors                                 | 20              | _     | 65  | kΩ | 9     |  |

|                  | @ V <sub>DD</sub> = 3.3 V                                  |                 |       |     |    |       |  |

|                  | @ V <sub>DD</sub> = 5.0 V                                  | 20              | _     | 50  | kΩ |       |  |

| R <sub>PD</sub>  | Internal pull-down resistors                               | 20              | —     | 65  | kΩ | 10    |  |

|                  | @ V <sub>DD</sub> = 3.3 V                                  |                 |       |     |    |       |  |

|                  | @ V <sub>DD</sub> = 5.0 V                                  | 20              | _     | 50  | kΩ |       |  |

- 1. Max power supply ramp rate is 500 V/ms.

- 2. The value given is measured at high drive strength mode. For value at low drive strength mode see the loh\_5 value given above.

- 3. The 20 mA I/O pin is capable of switching a 50 pF load at up to 40 MHz.

- 4. The value given is measured at high drive strength mode. For value at low drive strength mode see the lol\_5 value given above.

- 5. Refers to the current that leaks into the core when the pad is in Hi-Z (Off state).

- 6. Maximum pin leakage current at the ambient temperature upper limit.

- 7. PTD0, PTD1, PTD15, PTD16, PTB4, PTB5, PTE0 and PTE1 I/O have both high drive and normal drive capability selected by the associated Portx\_PCRn[DSE] control bit. All other GPIOs are normal drive only.

- 8. Refers to the pin leakage on the GPIOs when they are OFF.

- 9. Measured at  $V_{DD}$  supply voltage =  $V_{DD}$  min and input V =  $V_{SS}$

- 10. Measured at V<sub>DD</sub> supply voltage = V<sub>DD</sub> min and input V = V<sub>DD</sub>

| Mode | Symbol               | Clock<br>Configura<br>tion | Description                                                     | Temperat<br>ure | Min | Тур | Max <sup>1</sup> | Unit |

|------|----------------------|----------------------------|-----------------------------------------------------------------|-----------------|-----|-----|------------------|------|

|      |                      |                            |                                                                 | 50 ℃            | —   | 47  | 66               |      |

|      |                      |                            |                                                                 | 85 °C           | —   | 146 | 204              |      |

|      |                      |                            |                                                                 | 105 °C          | —   | 277 | 388              |      |

| VLPS | I <sub>DD_VLPS</sub> | -                          | Very Low Power Stop current, VDD=5V, bias disabled <sup>2</sup> | 25 °C and blew  | _   | 27  | 37               | μA   |

|      |                      |                            |                                                                 | 50 °C           | —   | 45  | 64               |      |

|      |                      |                            |                                                                 | 85 °C           | —   | 134 | 187              |      |

|      |                      |                            |                                                                 | 105 °C          | —   | 267 | 375              |      |

| VLPS | I <sub>DD_VLPS</sub> | -                          | Very Low Power Stop current, VDD=5V, bias enabled <sup>2</sup>  | 25 °C and blew  | _   | 21  | 29               | μA   |

|      |                      |                            |                                                                 | 50 ℃            | —   | 29  | 41               |      |

|      |                      |                            |                                                                 | 85 °C           | —   | 66  | 92               | 1    |

|      |                      |                            |                                                                 | 105 °C          | —   | 109 | 153              | 1    |

Table 33. Power consumption operating behaviors (continued)

1. These values are based on characterization but not covered by test limits in production.

2. PMC\_REGSC[CLKBIASDIS] is the control bit to enable or disable bias under STOP/VLPS mode.

## NOTE

# CoreMark benchmark compiled using IAR 7.40 with optimization level high, optimized for balanced.

#### 5.3.1.6.1 Low power mode peripheral current adder — typical value

| Symbol              | Description                                                                                                                                                                                                                                                              | Typical |  |  |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--|--|

| I <sub>LPTMR</sub>  | I <sub>LPTMR</sub> LPTMR peripheral adder measured by placing the device in VLPS<br>mode with LPTMR enabled using LPO. Includes LPO power<br>consumption.                                                                                                                |         |  |  |

| I <sub>CMP</sub>    | I <sub>CMP</sub> CMP peripheral adder measured by placing the device in VLPS mode<br>with CMP enabled using the 8-bit DAC and a single external input for<br>compare. 8-bit DAC enabled with half VDDA voltage, low speed mode.<br>Includes 8-bit DAC power consumption. |         |  |  |

| I <sub>RTC</sub>    |                                                                                                                                                                                                                                                                          |         |  |  |

| I <sub>LPUART</sub> |                                                                                                                                                                                                                                                                          |         |  |  |

| I <sub>FTM</sub>    | FTM peripheral adder measured by placing the device in VLPW mode with selected clock source, outputting the edge aligned PWM of 100 Hz frequency.                                                                                                                        | 45 µA   |  |  |

Table continues on the next page...

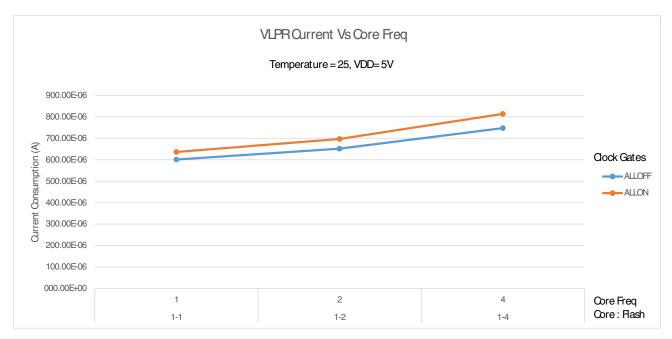

Figure 15. VLPR mode supply current vs. core frequency

## 5.3.1.7 EMC performance

Electromagnetic compatibility (EMC) performance is highly dependent on the environment in which the MCU resides. Board design and layout, circuit topology choices, location and characteristics of external components, and MCU software operation play a significant role in the EMC performance. The system designer can consult the following applications notes, available on http://www.nxp.com for advice and guidance specifically targeted at optimizing EMC performance.

- AN2321: Designing for Board Level Electromagnetic Compatibility

- AN1050: Designing for Electromagnetic Compatibility (EMC) with HCMOS Microcontrollers

- AN1263: Designing for Electromagnetic Compatibility with Single-Chip Microcontrollers

- AN2764: Improving the Transient Immunity Performance of Microcontroller-Based Applications

- AN1259: System Design and Layout Techniques for Noise Reduction in MCU-Based Systems

## 5.3.1.7.1 EMC radiated emissions operating behaviors

EMC measurements to IC-level IEC standards are available from NXP on request.

## NOTE

All measurements were taken accounting for 150 mV drop across VDD and VSS.

## 5.3.3 Thermal specifications

#### 5.3.3.1 Thermal operating requirements Table 39. Thermal operating requirements

| Symbol         | Description              | Min. | Max. | Unit | Notes |

|----------------|--------------------------|------|------|------|-------|

| TJ             | Die junction temperature | -40  | 125  | °C   |       |

| T <sub>A</sub> | Ambient temperature      | -40  | 105  | °C   | 1     |

1. Maximum  $T_A$  can be exceeded only if the user ensures that  $T_J$  does not exceed maximum  $T_J$ . The simplest method to determine  $T_J$  is:  $T_J = T_A + R_{\odot JA} \times chip$  power dissipation.

## 5.3.3.2 Thermal attributes

### 5.3.3.2.1 Description

The tables in the following sections describe the thermal characteristics of the device.

## NOTE

Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting side (board) temperature, ambient temperature, air flow, power dissipation or other components on the board, and board thermal resistance.

#### 5.3.3.2.2 Thermal characteristics for the 64-pin LQFP package Table 40. Thermal characteristics for the 64-pin LQFP package

| Rating                                                                       | Conditions              | Symbol            | Value | Unit |

|------------------------------------------------------------------------------|-------------------------|-------------------|-------|------|

| Thermal resistance, Junction to Ambient (Natural Convection) <sup>1, 2</sup> | Single layer board (1s) | R <sub>θJA</sub>  | 62    | °C/W |

| Thermal resistance, Junction to Ambient (Natural Convection) <sup>1, 2</sup> | Four layer board (2s2p) | R <sub>θJA</sub>  | 44    | °C/W |

| Thermal resistance, Junction to Ambient<br>(@200 ft/min) <sup>1, 3</sup>     | Single layer board (1s) | R <sub>ejma</sub> | 50    | °C/W |

Table continues on the next page ...

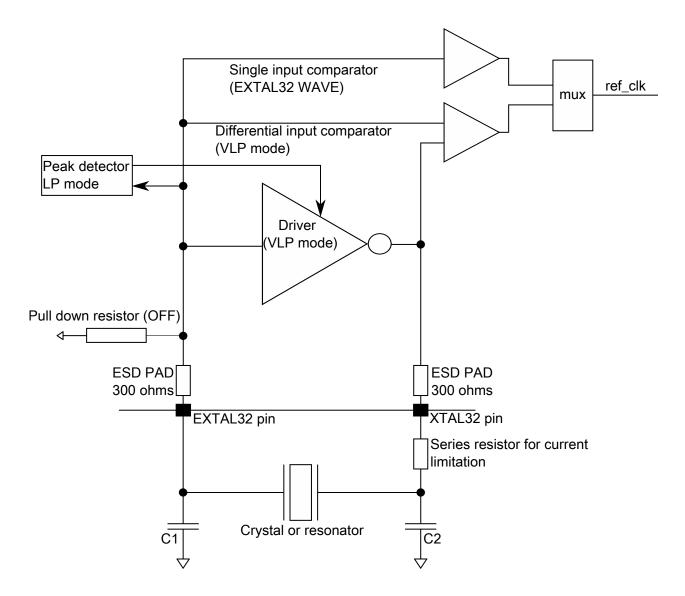

Figure 17. Oscillator connections scheme (OSC32)

- 1. The limit is respected across process, voltage and full temperature range.

- 2. Startup time is defined as the time between clock enablement and clock availability for system use.

### NOTE

Fast internal RC Oscillator is compliant with CAN and LIN standards.

#### 5.4.2.2.2 Slow internal RC oscillator (SIRC) electrical specifications Table 47. Slow internal RC oscillator (SIRC) electrical specifications

| Symbol               | Parameter                                                                            | Value |      |      | Unit               |

|----------------------|--------------------------------------------------------------------------------------|-------|------|------|--------------------|

|                      |                                                                                      | Min.  | Тур. | Max. |                    |

| F <sub>SIRC</sub>    | Slow internal reference frequency                                                    | —     | 2    | —    | MHz                |

|                      |                                                                                      |       | 8    |      |                    |

| I <sub>VDD</sub>     | Supply current                                                                       | _     | 23   | —    | μA                 |

| FUntrimmed           | IRC frequency (untrimmed)                                                            | _     | _    | —    | MHz                |

| ΔF <sub>OL</sub>     | Open loop total deviation of IRC frequency over voltage and temperature <sup>1</sup> |       |      |      |                    |

|                      | Regulator enable                                                                     | —     | _    | ±3   | %F <sub>SIRC</sub> |

| T <sub>Startup</sub> | Startup time                                                                         | —     | 6    | —    | μs <sup>2</sup>    |

- 1. The limit is respected across process, voltage and full temperature range.

- 2. Startup time is defined as the time between clock enablement and clock availability for system use.

#### 5.4.2.2.3 Low Power Oscillator (LPO) electrical specifications Table 48. Low Power Oscillator (LPO) electrical specifications

| Symbol               | Parameter                               | Min. | Тур. | Max. | Unit |

|----------------------|-----------------------------------------|------|------|------|------|

| F <sub>LPO</sub>     | Internal low power oscillator frequency | 113  | 128  | 139  | kHz  |

| I <sub>LPO</sub>     | Current consumption                     | 1    | 3    | 7    | μA   |

| T <sub>startup</sub> | Startup Time                            |      |      | 20   | μs   |

#### 5.4.2.2.4 LPFLL electrical specifications

| Symbol             | Parameter                                                                          | Min.            | Тур. | Max.           | Unit |

|--------------------|------------------------------------------------------------------------------------|-----------------|------|----------------|------|

| I <sub>avg</sub>   | Power consumption                                                                  |                 | 240  |                | μA   |

| T <sub>start</sub> | Start-up time                                                                      |                 | 3.6  |                | μs   |

| ΔF <sub>ol</sub>   | Frequency accuracy over temperature and voltage in open loop after process trimmed | -10             |      | 10             | %    |

| ΔF <sub>cl</sub>   | Frequency accuracy in closed loop                                                  | -1 <sup>1</sup> | —    | 1 <sup>1</sup> | %    |

#### Table 49. LPFLL electrical specifications

1.  $\Delta F_{cl}$  is dependent on reference clock accuracy. For example, if locked to crystal oscillator,  $\Delta F_{cl}$  is typically limited by trimming ability of the module itself; if locked to other clock source which has 3% accuracy, then  $\Delta F_{cl}$  can only be  $\pm 3\%$ .

## 5.4.3 Memories and memory interfaces

## 5.4.3.1 Flash memory module (FTFE) electrical specifications

This section describes the electrical characteristics of the flash memory module (FTFE).

#### 5.4.3.1.1 Flash timing specifications — program and erase

The following specifications represent the amount of time the internal charge pumps are active and do not include command overhead.

| Symbol                    | Description                                    | Min. | Тур. | Max. | Unit | Notes |

|---------------------------|------------------------------------------------|------|------|------|------|-------|

| t <sub>hvpgm8</sub>       | Program Phrase high-voltage time               | —    | 7.5  | 18   | μs   |       |

| t <sub>hversscr</sub>     | Erase Flash Sector high-voltage time           | —    | 13   | 113  | ms   | 1     |

| t <sub>hversblk32k</sub>  | Erase Flash Block high-voltage time for 32 KB  | —    | 26   | 226  | ms   | 1     |

| t <sub>hversblk256k</sub> | Erase Flash Block high-voltage time for 256 KB | _    | 208  | 1808 | ms   | 1     |

Table 50. NVM program/erase timing specifications

1. Maximum time based on expectations at cycling end-of-life.

#### 5.4.3.1.2 Flash timing specifications — commands Table 51. Flash command timing specifications

| Symbol                  | Description                                 | Min. | Тур. | Max. | Unit | Notes |

|-------------------------|---------------------------------------------|------|------|------|------|-------|

|                         | Read 1s Block execution time                |      |      |      |      |       |

| t <sub>rd1blk32k</sub>  | • 32 KB data flash                          | _    | —    | 0.3  | ms   |       |

| t <sub>rd1blk256k</sub> | • 256 KB program flash                      | _    |      | 1.8  | ms   |       |

| t <sub>rd1sec2k</sub>   | Read 1s Section execution time (2 KB flash) | —    | _    | 75   | μs   | 1     |

| t <sub>pgmchk</sub>     | Program Check execution time                | _    | —    | 95   | μs   | 1     |

| t <sub>rdrsrc</sub>     | Read Resource execution time                | _    | —    | 40   | μs   | 1     |

| t <sub>pgm8</sub>       | Program Phrase execution time               | —    | 90   | 150  | μs   |       |

|                         | Erase Flash Block execution time            |      |      |      |      | 2     |

| t <sub>ersblk32k</sub>  | • 32 KB data flash                          | _    | 28   | 240  | ms   |       |

| t <sub>ersblk256k</sub> | • 256 KB program flash                      | _    | 220  | 1850 | ms   |       |

| t <sub>ersscr</sub>     | Erase Flash Sector execution time           | _    | 15   | 115  | ms   | 2     |

Table continues on the next page ...

|                         |                                                        |      |      | ( )  |      |       |  |

|-------------------------|--------------------------------------------------------|------|------|------|------|-------|--|

| Symbol                  | Description                                            | Min. | Тур. | Max. | Unit | Notes |  |

| t <sub>pgmsec512</sub>  | Program Section execution time (512B flash)            |      | 2.5  | _    | ms   |       |  |

| t <sub>rd1all</sub>     | Read 1s All Blocks execution time                      | _    | —    | 2.2  | ms   |       |  |

| t <sub>rdonce</sub>     | Read Once execution time                               | _    | —    | 30   | μs   | 1     |  |

| t <sub>pgmonce</sub>    | Program Once execution time                            | _    | 90   | _    | μs   |       |  |

| t <sub>ersall</sub>     | Erase All Blocks execution time                        | _    | 250  | 2100 | ms   | 2     |  |

| t <sub>vfykey</sub>     | Verify Backdoor Access Key execution time              | _    | —    | 30   | μs   | 1     |  |

| t <sub>ersallu</sub>    | Erase All Blocks Unsecure execution time               | _    | 250  | 2100 | ms   | 2     |  |

|                         | Program Partition for EEPROM execution time            |      |      |      |      |       |  |

| t <sub>pgmpart24k</sub> | 24 KB EEPROM backup                                    | —    | 69   | _    | ms   |       |  |

| t <sub>pgmpart32k</sub> | 32 KB EEPROM backup                                    | —    | 70   | _    | ms   |       |  |

|                         | Set FlexRAM Function execution time:                   |      |      |      |      |       |  |

| t <sub>setramff</sub>   | Control Code 0xFF                                      | —    | 50   | _    | μs   |       |  |

| t <sub>setram24k</sub>  | 24 KB EEPROM backup                                    | —    | 0.6  | 1.1  | ms   |       |  |

| t <sub>setram32k</sub>  | • 32 KB EEPROM backup                                  | —    | 0.8  | 1.2  | ms   |       |  |

|                         | Byte-write to FlexRAM execution time:                  |      |      |      |      |       |  |

| t <sub>eewr8b24k</sub>  | 24 KB EEPROM backup                                    | —    | 370  | 1625 | μs   |       |  |

| t <sub>eewr8b32k</sub>  | 32 KB EEPROM backup                                    | —    | 385  | 1700 | μs   |       |  |

|                         | 16-bit write to FlexRAM execution time:                |      |      |      |      |       |  |

| t <sub>eewr16b24k</sub> | 24 KB EEPROM backup                                    | —    | 370  | 1625 | μs   |       |  |

| t <sub>eewr16b32k</sub> | 32 KB EEPROM backup                                    | —    | 385  | 1700 | μs   |       |  |

| t <sub>eewr32bers</sub> | 32-bit write to erased FlexRAM location execution time |      | 360  | 1500 | μs   |       |  |

|                         | 32-bit write to FlexRAM execution time:                |      |      |      |      |       |  |

| t <sub>eewr32b24k</sub> | 24 KB EEPROM backup                                    | _    | 600  | 1950 | μs   |       |  |

| t <sub>eewr32b32k</sub> | 32 KB EEPROM backup                                    | _    | 630  | 2000 | μs   |       |  |

Table 51. Flash command timing specifications (continued)

1. Assumes 25MHz or greater flash clock frequency.

2. Maximum times for erase parameters based on expectations at cycling end-of-life.

#### 5.4.3.1.3 Flash high voltage current behaviors Table 52. Flash high voltage current behaviors

| Symbol              | Description                                                                         | Min. | Тур. | Max. | Unit |

|---------------------|-------------------------------------------------------------------------------------|------|------|------|------|

| I <sub>DD_PGM</sub> | _PGM Average current adder during high voltage flash programming operation          |      | 3.5  | 7.5  | mA   |

| I <sub>DD_ERS</sub> | I <sub>DD_ERS</sub> Average current adder during high voltage flash erase operation |      | 1.5  | 4.0  | mA   |

| Symbol                   | Description                                                | Min.   | Typ. <sup>1</sup> | Max. | Unit   | Notes |

|--------------------------|------------------------------------------------------------|--------|-------------------|------|--------|-------|

|                          | Program F                                                  | lash   |                   |      | •      |       |

| t <sub>nvmretp10k</sub>  | Data retention after up to 10 K cycles                     | 5      | 50                |      | years  |       |

| t <sub>nvmretp1k</sub>   | Data retention after up to 1 K cycles                      | 20     | 100               |      | years  |       |

| n <sub>nvmcycp</sub>     | Cycling endurance                                          | 10 K   | 50 K              | —    | cycles | 2     |

|                          | Data Flas                                                  | sh     |                   |      | 1      |       |

| t <sub>nvmretd10k</sub>  | Data retention after up to 10 K cycles                     | 5      | 50                |      | years  |       |

| t <sub>nvmretd1k</sub>   | Data retention after up to 1 K cycles                      | 20     | 100               | _    | years  |       |

| n <sub>nvmcycd</sub>     | Cycling endurance                                          | 10 K   | 50 K              |      | cycles | 2     |

|                          | FlexRAM as El                                              | EPROM  |                   |      |        |       |

| t <sub>nvmretee100</sub> | Data retention up to 100% of write endurance               | 5      | 50                | _    | years  |       |

| t <sub>nvmretee10</sub>  | Data retention up to 10% of write endurance                | 20     | 100               | _    | years  |       |

| n <sub>nvmcycee</sub>    | Cycling endurance for EEPROM backup                        | 20 K   | 50 K              | —    | cycles | 2     |

|                          | Write endurance                                            |        |                   |      |        | 3     |

| n <sub>nvmwree16</sub>   | <ul> <li>EEPROM backup to FlexRAM ratio = 16</li> </ul>    | 140 K  | 400 K             | _    | writes |       |

| n <sub>nvmwree128</sub>  | <ul> <li>EEPROM backup to FlexRAM ratio = 128</li> </ul>   | 1.26 M | 3.2 M             | _    | writes |       |

| n <sub>nvmwree512</sub>  | <ul> <li>EEPROM backup to FlexRAM ratio = 512</li> </ul>   | 5 M    | 12.8 M            | _    | writes |       |

| n <sub>nvmwree1k</sub>   | <ul> <li>EEPROM backup to FlexRAM ratio = 1,024</li> </ul> | 10 M   | 25 M              | _    | writes |       |

#### 5.4.3.1.4 Reliability specifications Table 53. NVM reliability specifications

1. Typical data retention values are based on measured response accelerated at high temperature and derated to a constant 25°C use profile. Engineering Bulletin EB618 does not apply to this technology. Typical endurance defined in Engineering Bulletin EB619.

2. Cycling endurance represents number of program/erase cycles at -40°C  $\leq$  T<sub>i</sub>  $\leq$  125°C.

3. Write endurance represents the number of writes to each FlexRAM location at -40°C ≤Tj ≤ 125°C influenced by the cycling endurance of the FlexNVM and the allocated EEPROM backup. Minimum and typical values assume all 16-bit or 32-bit writes to FlexRAM; all 8-bit writes result in 50% less endurance.

## 5.4.4 Security and integrity modules

There are no specifications necessary for the device's security and integrity modules.

## 5.4.5 Analog

### 5.4.5.1 ADC electrical specifications

| Table 56. | Comparator with | 8-bit DAC electrical specifications | (continued) |

|-----------|-----------------|-------------------------------------|-------------|

|-----------|-----------------|-------------------------------------|-------------|

| Symbol             | Description                                         | Min. | Typ. <sup>1</sup> | Max. | Unit             |

|--------------------|-----------------------------------------------------|------|-------------------|------|------------------|

|                    | within ambient temperature range                    |      | 48                | 133  |                  |

|                    | Analog comparator hysteresis, Hyst3, Low-speed mode |      |                   |      |                  |

|                    | within ambient temperature range                    | —    | 33                | 80   |                  |

| I <sub>DAC8b</sub> | 8-bit DAC current adder (enabled)                   | —    | 10                | 16   | μA               |

| INL                | 8-bit DAC integral non-linearity                    | -0.6 | —                 | 0.5  | LSB <sup>5</sup> |

| DNL                | L 8-bit DAC differential non-linearity              |      | —                 | 0.5  | LSB              |

1. Typical values assumed at VDDA = 5.0 V, Temp = 25 °C, unless otherwise stated.

- 2. Difference at input > 200mV

- 3. Applied ± (100 mV + Hyst) around switch point

- 4. Applied  $\pm$  (30 mV + 2 × Hyst) around switch point

- 5. 1 LSB =  $V_{reference}/256$

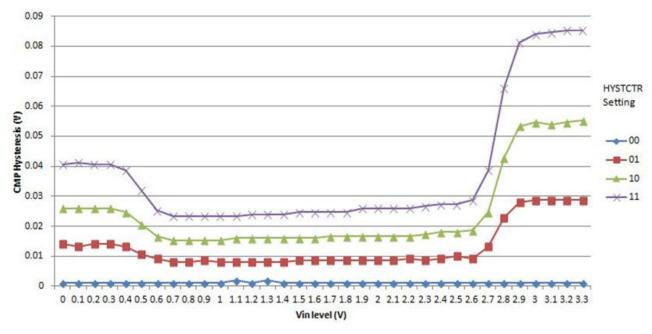

Figure 20. Typical hysteresis vs. Vin level (VDD = 3.3 V, PMODE = 0)

| Num. | Symbol          | Description                    | Min.                     | Max.                          | Unit | Note |

|------|-----------------|--------------------------------|--------------------------|-------------------------------|------|------|

| 5    | twspsck         | Clock (SPSCK) high or low time | t <sub>periph</sub> - 30 | 1024 x<br>t <sub>periph</sub> | ns   | _    |

| 6    | t <sub>SU</sub> | Data setup time (inputs)       | 18                       | —                             | ns   | —    |

| 7    | t <sub>HI</sub> | Data hold time (inputs)        | 0                        | _                             | ns   | —    |

| 8    | t <sub>v</sub>  | Data valid (after SPSCK edge)  | —                        | 15                            | ns   | _    |

| 9    | t <sub>HO</sub> | Data hold time (outputs)       | 0                        | _                             | ns   | —    |

| 10   | t <sub>RI</sub> | Rise time input                | _                        | t <sub>periph</sub> - 25      | ns   | —    |

|      | t <sub>FI</sub> | Fall time input                |                          |                               |      |      |

| 11   | t <sub>RO</sub> | Rise time output               | —                        | 25                            | ns   | _    |

|      | t <sub>FO</sub> | Fall time output               |                          |                               |      |      |

1. f<sub>periph</sub> = LPSPI peripheral clock

2.  $t_{periph} = 1/f_{periph}$

NOTE

High drive pin should be used for fast bit rate.

1. If configured as an output.

2. LSBF = 0. For LSBF = 1, bit order is LSB, bit 1, ..., bit 6, MSB.

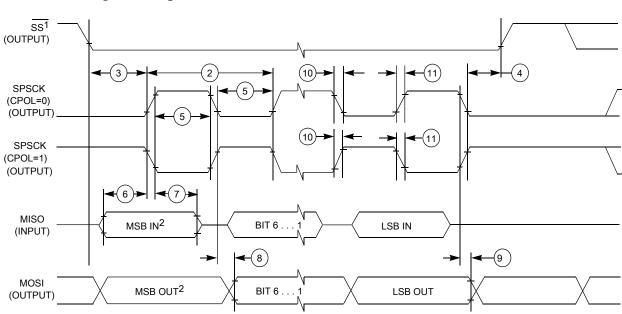

#### Figure 24. LPSPI master mode timing (CPHA = 0)

#### **Electrical characteristics**

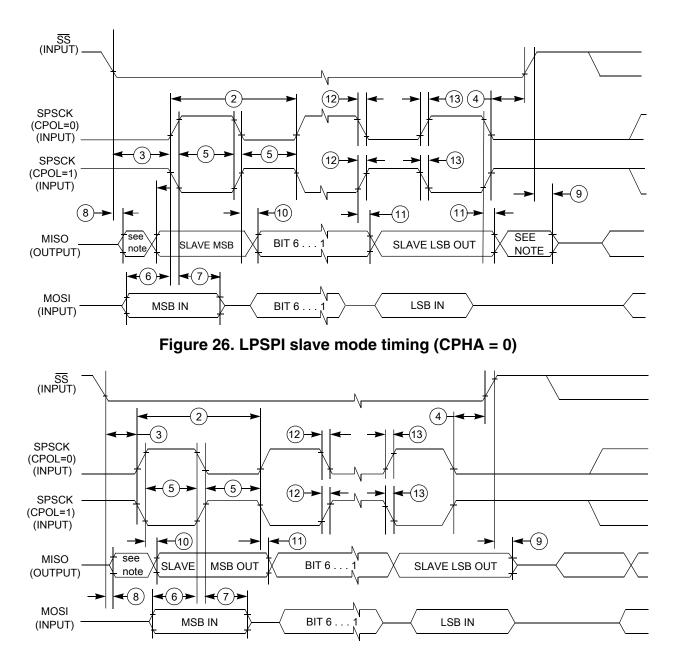

Figure 27. LPSPI slave mode timing (CPHA = 1)

## 5.4.6.3 LPI<sup>2</sup>C

| Table 59. | LPI <sup>2</sup> C s | pecifications |

|-----------|----------------------|---------------|

|-----------|----------------------|---------------|

| Symbol           | Description         |                           | Min. | Max. | Unit | Notes   |

|------------------|---------------------|---------------------------|------|------|------|---------|

| f <sub>SCL</sub> | SCL clock frequency | Standard mode (Sm)        | 0    | 100  | kHz  | 1, 2, 3 |

|                  |                     | Fast mode (Fm)            | 0    | 400  |      |         |

|                  |                     | Fast mode Plus (Fm+)      | 0    | 1000 |      |         |

|                  |                     | Ultra Fast mode (UFm)     | 0    | 5000 |      |         |

|                  |                     | High speed mode (Hs-mode) | 0    | 3400 | ]    |         |