#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                        |

|----------------------------|-------------------------------------------------------------------------------|

| Core Processor             | H8S/2000                                                                      |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 13MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, SCI, SmartCard                                              |

| Peripherals                | POR, PWM, WDT                                                                 |

| Number of I/O              | 72                                                                            |

| Program Memory Size        | 256KB (256K x 8)                                                              |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | - ·                                                                           |

| RAM Size                   | 16K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                     |

| Data Converters            | A/D 8x10b; D/A 2x8b                                                           |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -20°C ~ 75°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 100-TQFP                                                                      |

| Supplier Device Package    | 100-TQFP (12x12)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/df2238btf13v |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### • On-chip memory

| ROM          | Model       | ROM        | RAM       | Remarks |

|--------------|-------------|------------|-----------|---------|

| Flash memory | HD64F2258   | 256 kbytes | 16 kbytes |         |

| version      | HD64F2239   | 384 kbytes | 32 kbytes |         |

|              | HD64F2238B  | 256 kbytes | 16 kbytes |         |

|              | HD64F2238R  | 256 kbytes | 16 kbytes |         |

|              | HD64F2227   | 128 kbytes | 16 kbytes |         |

| PROM version | HD6472237   | 128 kbytes | 16 kbytes |         |

| Masked ROM   | HD6432258   | 256 kbytes | 16 kbytes |         |

| version      | HD6432258W  | 256 kbytes | 16 kbytes |         |

|              | HD6432256   | 128 kbytes | 8 kbytes  |         |

|              | HD6432256W  | 128 kbytes | 8 kbytes  |         |

|              | HD6432239   | 384 kbytes | 32 kbytes |         |

|              | HD6432239W  | 384 kbytes | 32 kbytes |         |

|              | HD6432238B  | 256 kbytes | 16 kbytes |         |

|              | HD6432238BW | 256 kbytes | 16 kbytes |         |

|              | HD6432238R  | 256 kbytes | 16 kbytes |         |

|              | HD6432238RW | 256 kbytes | 16 kbytes |         |

|              | HD6432236B  | 128 kbytes | 8 kbytes  |         |

|              | HD6432236BW | 128 kbytes | 8 kbytes  |         |

|              | HD6432236R  | 128 kbytes | 8 kbytes  |         |

|              | HD6432236RW | 128 kbytes | 8 kbytes  |         |

|              | HD6432237   | 128 kbytes | 16 kbytes |         |

|              | HD6432235   | 128 kbytes | 4 kbytes  |         |

|              | HD6432233   | 64 kbytes  | 4 kbytes  |         |

|              | HD6432227   | 128 kbytes | 16 kbytes |         |

|              | HD6432225   | 128 kbytes | 4 kbytes  |         |

|              | HD6432224   | 96 kbytes  | 4 kbytes  |         |

|              | HD6432223   | 64 kbytes  | 4 kbytes  |         |

- General I/O ports

- I/O pins: 72

- Input-only pins: 10

- Supports various power-down states

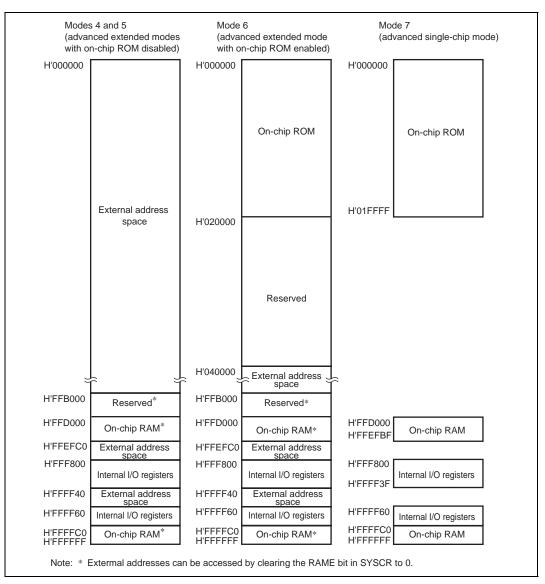

Figure 3.2 H8S/2256 Memory Map in Each Operating Mode

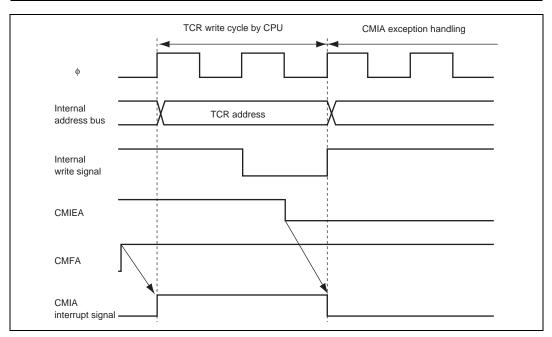

#### 5.6.2 Instructions that Disable Interrupts

The instructions that disable interrupts are LDC, ANDC, ORC, and XORC. After any of these instructions are executed, all interrupts including NMI are disabled and the next instruction is always executed. When the I bit is set by one of these instructions, the new value becomes valid two states after execution of the instruction ends.

### 5.6.3 When Interrupts are Disabled

There are times when interrupt acceptance is disabled by the interrupt controller.

The interrupt controller disables interrupt acceptance for a 3-state period after the CPU has updated the mask level with an LDC, ANDC, ORC, or XORC instruction.

### 5.6.4 Interrupts during Execution of EEPMOV Instruction

Interrupt operation differs between the EEPMOV.B instruction and the EEPMOV.W instruction.

With the EEPMOV.B instruction, an interrupt request (including NMI) issued during the transfer is not accepted until the move is completed.

Rn as its addressing mode, and that instruction is located in on-chip ROM or RAM, the instruction will be one state later than in normal operation.

### 6.4 Usage Notes

#### 6.4.1 Module Stop Mode Setting

PBC operation can be disabled or enabled using the module stop control register. The initial setting is for PBC operation to be halted. Register access is enabled by clearing module stop mode. For details, refer to section 24, Power-Down Modes.

#### 6.4.2 PC Break Interrupts

The PC break interrupt is shared by channels A and B. The channel from which the request was issued must be determined by the interrupt handler.

#### 6.4.3 CMFA and CMFB

The CMFA and CMFB flags are not automatically cleared to 0, so 0 must be written to CMFA or CMFB after first reading the flag while it is set to 1. If the flag is left set to 1, another interrupt will be requested after interrupt handling ends.

### 6.4.4 PC Break Interrupt when DTC and DMAC\* Is Bus Master

A PC break interrupt generated when the DTC and DMAC\* is the bus master is accepted after the bus has been transferred to the CPU by the bus controller.

Note: \* Supported only by the H8S/2239 Group.

### 6.4.5 PC Break Set for Instruction Fetch at Address Following BSR, JSR, JMP, TRAPA, RTE, and RTS Instruction

Even if the instruction at the address following a BSR, JSR, JMP, TRAPA, RTE, or RTS instruction is fetched, it is not executed, and so a PC break interrupt is not generated by the instruction fetch at the next address.

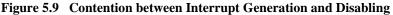

Figure 7.1 shows a block diagram of the bus controller.

Figure 7.1 Block Diagram of Bus Controller

| Channel | Bit 2<br>TPSC2 | Bit 1<br>TPSC1 | Bit 0<br>TPSC0 | Description                               |

|---------|----------------|----------------|----------------|-------------------------------------------|

| 4*      | 0              | 0              | 0              | Internal clock: counts on $\phi/1$        |

|         |                |                | 1              | Internal clock: counts on $\phi/4$        |

|         |                | 1              | 0              | Internal clock: counts on $\phi/16$       |

|         |                |                | 1              | Internal clock: counts on $\phi/64$       |

|         | 1              | 0              | 0              | External clock: counts on TCLKA pin input |

|         |                |                | 1              | External clock: counts on TCLKC pin input |

|         |                | 1              | 0              | Internal clock: counts on $\phi/1024$     |

|         |                |                | 1              | Counts on TCNT5 overflow/underflow        |

#### Table 11.9 TPSC2 to TPSC0 (Channel 4)

Notes: This setting is ignored when channel 4 is in phase counting mode.

\* Not available in the H8S/2227 Group.

#### Table 11.10 TPSC2 to TPSC0 (Channel 5)

| Channel | Bit 2<br>TPSC2 | Bit 1<br>TPSC1 | Bit 0<br>TPSC0 | Description                               |

|---------|----------------|----------------|----------------|-------------------------------------------|

| 5*      | 0              | 0              | 0              | Internal clock: counts on $\phi/1$        |

|         |                |                | 1              | Internal clock: counts on                 |

|         |                | 1              | 0              | Internal clock: counts on                 |

|         |                |                | 1              | Internal clock: counts on                 |

|         | 1              | 0              | 0              | External clock: counts on TCLKA pin input |

|         |                |                | 1              | External clock: counts on TCLKC pin input |

|         |                | 1              | 0              | Internal clock: counts on                 |

|         |                |                | 1              | External clock: counts on TCLKD pin input |

Notes: This setting is ignored when channel 5 is in phase counting mode.

\* Not available in the H8S/2227 Group.

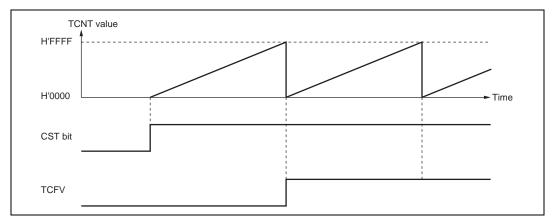

2. Free-running count operation and periodic count operation Immediately after a reset, the TPU's TCNT counters are all designated as free-running counters. When the relevant bit in TSTR is set to 1 the corresponding TCNT counter starts upcount operation as a free-running counter. When TCNT overflows (changes from H'FFFF to H'0000), the TCFV bit in TSR is set to 1. If the value of the corresponding TCIEV bit in TIER is 1 at this point, the TPU requests an interrupt. After overflow, TCNT starts counting up again from H'0000.

Figure 11.4 illustrates free-running counter operation.

Figure 11.4 Free-Running Counter Operation

When compare match is selected as the TCNT clearing source, the TCNT counter for the relevant channel performs periodic count operation. The TGR register for setting the period is designated as an output compare register, and counter clearing by compare match is selected by means of bits CCLR2 to CCLR0 in TCR. After the settings have been made, TCNT starts count-up operation as a periodic counter when the corresponding bit in TSTR is set to 1. When the count value matches the value in TGR, the TGF bit in TSR is set to 1 and TCNT is cleared to H'0000.

If the value of the corresponding TGIE bit in TIER is 1 at this point, the TPU requests an interrupt. After a compare match, TCNT starts counting up again from H'0000.

Figure 11.5 illustrates periodic counter operation.

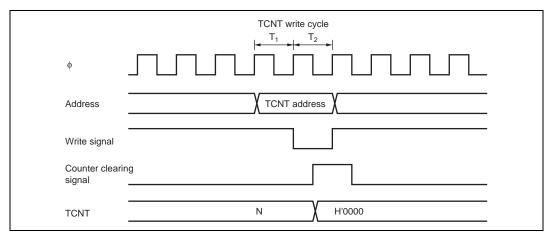

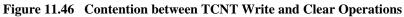

#### 11.10.5 Contention between TCNT Write and Increment Operations

If incrementing occurs in the  $T_2$  state of a TCNT write cycle, the TCNT write takes precedence and TCNT is not incremented. Figure 11.47 shows the timing in this case.

Figure 11.47 Contention between TCNT Write and Increment Operations

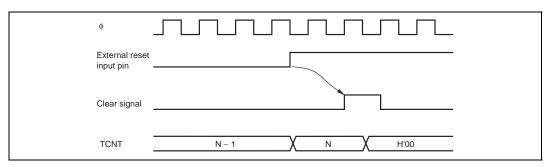

### 12.5.5 TCNT External Reset Timing

TCNT is cleared at the rising edge of an external reset input, depending on the settings of the CCLR1 and CCLR0 bits in TCR. The width of the clearing pulse must be at least 1.5 states. Figure 12.8 shows the timing of this operation.

Figure 12.8 Timing of Clearing by External Reset Input

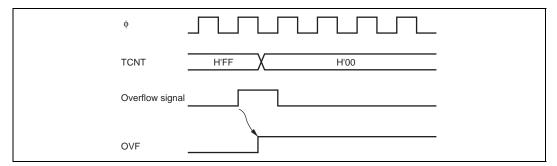

#### 12.5.6 Timing of Overflow Flag (OVF) Setting

OVF in TCSR is set to 1 when the timer count overflows (changes from H'FF to H'00). Figure 12.9 shows the timing of this operation.

Figure 12.9 Timing of OVF Setting

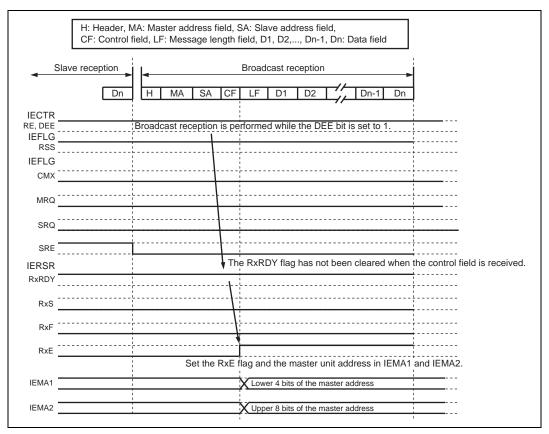

Figure 14.10 Error Occurrence in the Broadcast Reception (DEE = 1)

#### 14.4.3 Master Reception

This section shows an example of performing a master reception using the DTC after slave reception.

#### (1) IEB Initialization

(a) Setting the IEBus Control Register (IECTR)

Enable the IEBus pins, select the signal polarity, and select a clock supplied to the IEB. Set the RE bit to 1 to perform reception. The LUEE bit does not need to be specified.

(b) Setting the IEBus Master Unit Address Registers 1 and 2 (IEAR1 and IEAR2) Specify the master unit address and specify the communications mode in IEAR1. Compare with the slave address in the communications frame and receive the frame if matched.

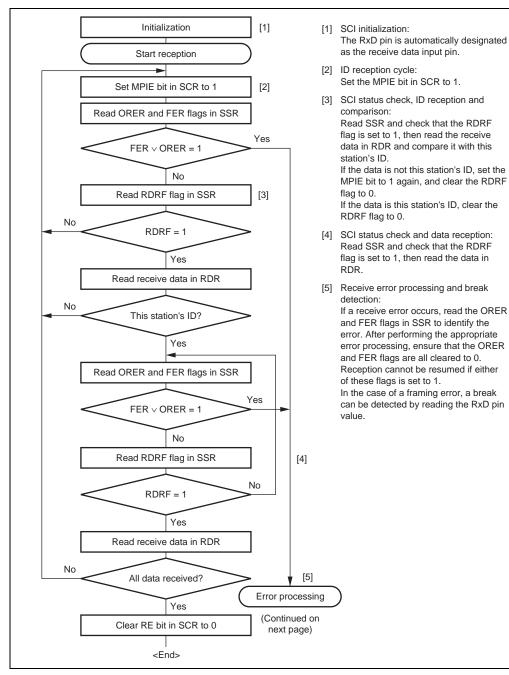

Figure 15.16 Sample Multiprocessor Serial Reception Flowchart (1)

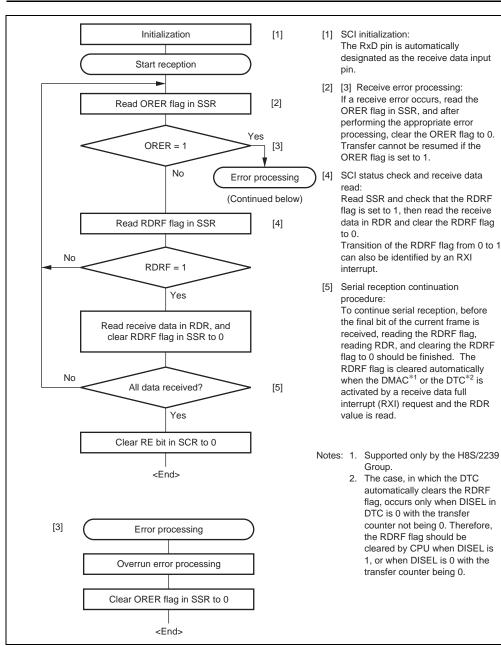

Figure 15.22 Sample Serial Reception Flowchart

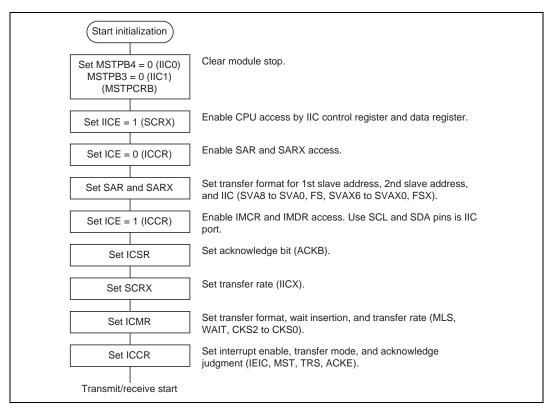

#### 16.4.2 Initial Setting

At startup the following procedure is used to initialize the IIC.

Figure 16.6 Flowchart for IIC Initialization (Example)

Note: The ICMR register should be written to only after transmit or receive operations have completed.

Writing to the ICMR register while a transmit or receive operation is in progress could cause an erroneous value to be written to bit counter bits BC2 to BC0. This could result in improper operation.

#### 16.4.3 Master Transmit Operation

In I<sup>2</sup>C bus format master transmit mode, the master device outputs the transmit clock and transmit data, and the slave device returns an acknowledge signal.

Do not select the HN27C4096 setting for the PROM programmer, and only use the specified socket adapter. Failure to observe these points may result in damage to the device.

**Powering On and Off (See Figures 20.14 to 20.16):** Do not apply a high level to the FWE pin until VCC has stabilized. Also, drive the FWE pin low before turning off VCC.

When applying or disconnecting VCC power, fix the FWE pin low and place the flash memory in the hardware protection state.

The power-on and power-off timing requirements should also be satisfied in the event of a power failure and subsequent recovery.

**FWE Application/Disconnection (See Figures 20.14 to 20.16):** FWE application should be carried out when MCU operation is in a stable condition. If MCU operation is not stable, fix the FWE pin low and set the protection state.

The following points must be observed concerning FWE application and disconnection to prevent unintentional programming or erasing of flash memory:

- Apply FWE when the VCC voltage has stabilized within its rated voltage range.

- In boot mode, apply and disconnect FWE during a reset.

- In user program mode, FWE can be switched between high and low level regardless of the reset state. FWE input can also be switched during execution of a program in flash memory.

- Do not apply FWE if program runaway has occurred.

- Disconnect FWE only when the SWE1, ESU1, PSU1, EV1, PV1, P1, and E1 bits in FLMCR1 are cleared.

Make sure that the SWE1, ESU1, PSU1, EV1, PV1, P1, and E1 bits are not set by mistake when applying or disconnecting FWE.

**Do Not Apply a Constant High Level to the FWE Pin:** Apply a high level to the FWE pin only when programming or erasing flash memory. A system configuration in which a high level is constantly applied to the FWE pin should be avoided. Also, while a high level is applied to the FWE pin, the watchdog timer should be activated to prevent overprogramming or overerasing due to program runaway, etc.

**Use the Recommended Algorithm when Programming and Erasing Flash Memory:** The recommended algorithm enables programming and erasing to be carried out without subjecting the device to voltage stress or sacrificing program data reliability. When setting the P1 or E1 bit in FLMCR1, the watchdog timer should be set beforehand as a precaution against program runaway, etc.

### Section 26 List of Registers

| Register |        |        |        |        |        |        |        |        |        |

|----------|--------|--------|--------|--------|--------|--------|--------|--------|--------|

| Name     | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Module |

| MAR_1A   |        | —      | _      | _      | _      | _      | _      | _      | DMAC   |

|          | Bit 23 | Bit 22 | Bit 21 | Bit 20 | Bit 19 | Bit 18 | Bit 17 | Bit 16 |        |

|          | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  |        |

|          | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  |        |

| IOAR_1A  | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  |        |

|          | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  |        |

| ETCR_1A  | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  |        |

|          | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  |        |

| MAR_1B   | _      | _      | _      | _      | _      | _      | _      | _      |        |

|          | Bit 23 | Bit 22 | Bit 21 | Bit 20 | Bit 19 | Bit 18 | Bit 17 | Bit 16 |        |

|          | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  |        |

|          | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  |        |

| IOAR_1B  | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  |        |

|          | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  |        |

| ETCR_1B  | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  |        |

|          | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  |        |

| P1DR     | P17DR  | P16DR  | P15DR  | P14DR  | P13DR  | P12DR  | P11DR  | P10DR  | PORT   |

| P3DR     | _      | P36DR  | P35DR  | P34DR  | P33DR  | P32DR  | P31DR  | P30DR  |        |

| P7DR     | P77DR  | P76DR  | P75DR  | P74DR  | P73DR  | P72DR  | P71DR  | P70DR  |        |

| PADR     | _      | _      | _      | _      | PA3DR  | PA2DR  | PA1DR  | PA0DR  |        |

| PBDR     | PB7DR  | PB6DR  | PB5DR  | PB4DR  | PB3DR  | PB2DR  | PB1DR  | PB0DR  |        |

| PCDR     | PC7DR  | PC6DR  | PC5DR  | PC4DR  | PC3DR  | PC2DR  | PC1DR  | PC0DR  |        |

| PDDR     | PD7DR  | PD6DR  | PD5DR  | PD4DR  | PD3DR  | PD2DR  | PD1DR  | PD0DR  |        |

| PEDR     | PE7DR  | PE6DR  | PE5DR  | PE4DR  | PE3DR  | PE2DR  | PE1DR  | PE0DR  |        |

| PFDR     | PF7DR  | PF6DR  | PF5DR  | PF4DR  | PF3DR  | PF2DR  | PF1DR  | PF0DR  |        |

| PGDR     | _      | _      | _      | PG4DR  | PG3DR  | PG2DR  | PG1DR  | PG0DR  |        |

| TCR_0    | CCLR2  | CCLR1  | CCLR0  | CKEG1  | CKEG0  | TPSC2  | TPSC1  | TPSC0  | TPU_0  |

| TMDR_0   | _      | _      | BFB    | BFA    | MD3    | MD2    | MD1    | MD0    |        |

| TIORH_0  | IOB3   | IOB2   | IOB1   | IOB0   | IOA3   | IOA2   | IOA1   | IOA0   |        |

| TIORL_0  | IOD3   | IOD2   | IOD1   | IOD0   | IOC3   | IOC2   | IOC1   | IOC0   |        |

| TIER_0   | TTGE   | _      | _      | TCIEV  | TGIED  | TGIEC  | TGIEB  | TGIEA  |        |

#### 27.3.5 D/A Conversion Characteristics

Table 27.24 lists the D/A conversion characteristics.

#### Table 27.24 D/A Conversion Characteristics

Condition A (F-ZTAT version and masked ROM version):

$V_{cc} = 2.7 \text{ V to } 3.6 \text{ V}, \text{AV}_{cc} = 2.7 \text{ V to } 3.6 \text{ V},$  $V_{ref} = 2.7 \text{ V to } \text{AV}_{cc}, \text{V}_{ss} = \text{AV}_{ss} = 0 \text{ V}, \phi = 2 \text{ to } 16.0 \text{ MHz},$  $T_a = -20^{\circ}\text{C to } +75^{\circ}\text{C} \text{ (regular specifications)}$

Condition B (Masked ROM version):  $V_{cc} = 2.2 V \text{ to } 3.6 V$ ,  $AV_{cc} = 2.2 V \text{ to } 3.6 V$ ,  $V_{ref} = 2.2 V \text{ to } AV_{cc}$ ,  $V_{ss} = AV_{ss} = 0 V$ ,  $\phi = 2 \text{ to } 6.25 \text{ MHz}$ ,  $T_a = -20^{\circ}\text{C} \text{ to } +75^{\circ}\text{C}$  (regular specifications),  $T_a = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}$  (wide-range specifications)

Condition C (F-ZTAT version and masked ROM version):

$$\begin{split} V_{cc} &= 3.0 \text{ V to } 3.6 \text{ V}, \text{AV}_{cc} = 3.0 \text{ V to } 3.6 \text{ V}, \\ V_{ref} &= 3.0 \text{ V to } \text{AV}_{cc}, \text{V}_{ss} = \text{AV}_{ss} = 0 \text{ V}, \\ \phi &= 10.0 \text{ to } 20.0 \text{ MHz}, \\ T_a &= -20^{\circ}\text{C to } +75^{\circ}\text{C} \text{ (regular specifications)}, \\ T_a &= -40^{\circ}\text{C to } +85^{\circ}\text{C} \text{ (wide-range specifications)} \end{split}$$

|                   | Co  | onditions | s A, C |     | Condition B |      |      |                                   |  |

|-------------------|-----|-----------|--------|-----|-------------|------|------|-----------------------------------|--|

| ltem              | Min | Тур       | Max    | Min | Тур         | Max  | Unit | Test Condition                    |  |

| Resolution        | 8   | 8         | 8      | 8   | 8           | 8    | bits |                                   |  |

| Conversion time   | —   | —         | 10     | _   | —           | 10   | μs   | Load capacitance<br>= 20 pF       |  |

| Absolute accuracy | *   | ±2.0      | ±3.0   | _   | ±3.0        | ±4.0 | LSB  | Load resistance<br>= 2 M $\Omega$ |  |

|                   |     |           | ±2.0   |     | _           | ±3.0 | LSB  | Load resistance<br>= 4 MΩ         |  |

Note: \* Does not apply in module stop mode, software standby mode, watch mode, subactive mode, or subsleep mode.

| Item        |                                                   | Symbol            | Min | Тур | Max               | Unit  | Test<br>Conditions |

|-------------|---------------------------------------------------|-------------------|-----|-----|-------------------|-------|--------------------|

| Programming | Maximum programming                               | N1                |     | _   | 6 <sup>*4</sup>   | Times |                    |

|             | count <sup>*1*4</sup>                             | N2                | _   | _   | 994 <sup>*4</sup> | _     |                    |

| Erase       | Wait time after SWE1<br>bit setting <sup>*1</sup> | t <sub>sswe</sub> | 1   | 1   | —                 | μs    |                    |

|             | Wait time after ESU1<br>bit setting <sup>*1</sup> | t <sub>sesu</sub> | 100 | 100 | _                 | μs    |                    |

|             | Wait time after E1 bit setting <sup>*1*5</sup>    | t <sub>se</sub>   | 10  | 10  | 100               | ms    |                    |

|             | Wait time after E1 bit clear <sup>*1</sup>        | t <sub>ce</sub>   | 10  | 10  | —                 | μs    |                    |

|             | Wait time after ESU1<br>bit clear <sup>*1</sup>   | t <sub>cesu</sub> | 10  | 10  | —                 | μs    |                    |

|             | Wait time after EV1 bit setting <sup>*1</sup>     | t <sub>sev</sub>  | 20  | 20  | _                 | μs    |                    |

|             | Wait time after H'FF<br>dummy write <sup>*1</sup> | t <sub>sevr</sub> | 2   | 2   | _                 | μs    |                    |

|             | Wait time after EV1 bit clear <sup>*1</sup>       | t <sub>cev</sub>  | 4   | 4   |                   | μs    |                    |

|             | Wait time after SWE1<br>bit clear                 | t <sub>cswe</sub> | 100 | 100 | _                 | μs    |                    |

|             | Maximum erase<br>count <sup>*1*5</sup>            | Ν                 | —   | _   | 100               | Times |                    |

Notes: 1. Make each time setting in accordance with the program/program-verify flowchart or erase/erase-verify flowchart.

- 2. Programming time per 128 bytes (Shows the total period for which the P1 bit in the flash memory control register 1 (FLMCR1) is set. It does not include the program verification time.)

- 3. Block erase time (Shows the total period for which the E1 bit in FLMCR1 is set. It does not include the erase verification time.)

- 4. Maximum programming time value  $t_p(max) = Wait$  time after P1 bit setting  $(t_{sp}) \times maximum program count (N)$   $(t_{sp30} + t_{sp10}) \times 6 + (t_{sp200}) \times 994$

- Relationship among the maximum erase time (t<sub>e</sub> (max)), the wait time after E1 bit setting (t<sub>se</sub>), and the maximum erase count (N) is shown below.

- $t_{_{E}}$  (max) = Wait time after E1 bit setting ( $t_{_{se}}$ ) × maximum erase count (N)

- 6. The minimum times that all characteristics after reprogramming are guaranteed. (The range between 1 and a minimum value is guaranteed.)

- Reference value at 25°C. (Normally, it is a reference that rewriting is enabled up to this value.)

- 8. Data hold characteristics are when reprogramming is performed within the range of specifications including a minimum value.

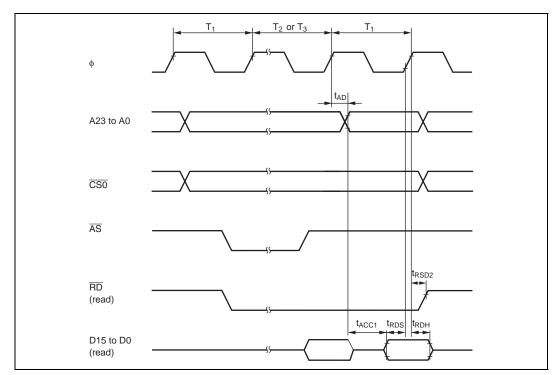

Figure 27.18 Burst ROM Access Timing (One-State Access)

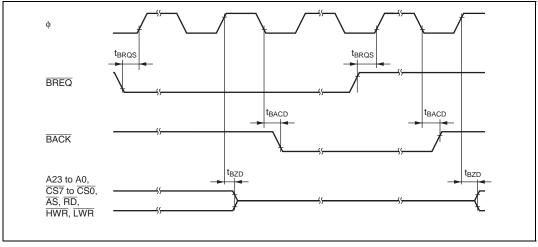

Figure 27.19 External Bus Release Timing

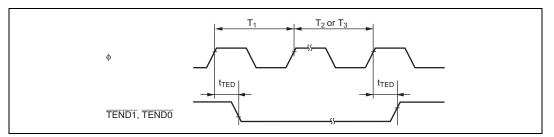

Figure 27.22 DMAC TEND Output Timing

#### 27.7.4 Timing of On-Chip Peripheral Modules

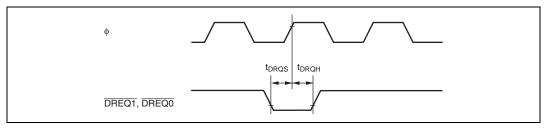

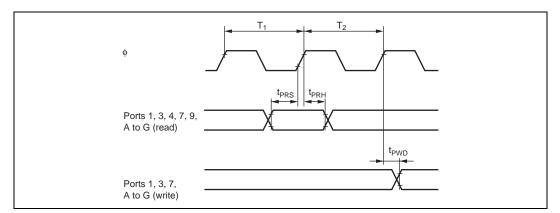

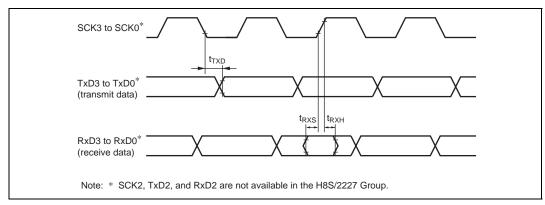

Figures 27.24 to 27.34 show the timing of on-chip peripheral modules.

Figure 27.24 I/O Port Input/Output Timing

Figure 27.32 SCI Input/Output Timing (Clocked Synchronous Mode)

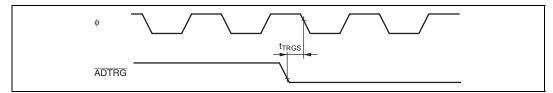

Figure 27.33 A/D Converter External Trigger Input Timing

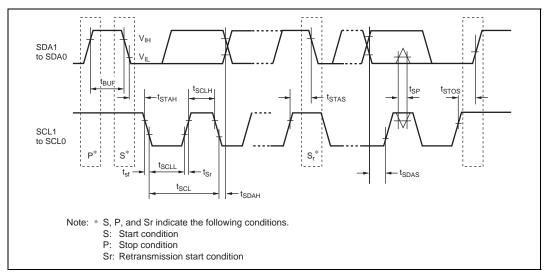

Figure 27.34 I<sup>2</sup>C Bus Interface Input/Output Timing (Optional)