Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                     |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | H8S/2000                                                                     |

| Core Size                  | 16-Bit                                                                       |

| Speed                      | 6MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, SCI, SmartCard                                             |

| Peripherals                | POR, PWM, WDT                                                                |

| Number of I/O              | 72                                                                           |

| Program Memory Size        | 256КВ (256К х 8)                                                             |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 16K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.2V ~ 3.6V                                                                  |

| Data Converters            | A/D 8x10b; D/A 2x8b                                                          |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -20°C ~ 75°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 100-TQFP                                                                     |

| Supplier Device Package    | 100-TQFP (14x14)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/df2238rte6v |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Contents

| Secti | on 1 (   | Overview                                                         | 1  |

|-------|----------|------------------------------------------------------------------|----|

| 1.1   | Feature  | S                                                                | 1  |

| 1.2   | Internal | l Block Diagram                                                  | 4  |

| 1.3   | Pin Des  | scription                                                        | 9  |

|       | 1.3.1    | Pin Arrangement                                                  | 9  |

|       | 1.3.2    | Pin Arrangements in Each Mode                                    | 20 |

|       | 1.3.3    | Pin Functions                                                    | 44 |

| Secti | on 2 (   | CPU                                                              | 63 |

| 2.1   | Feature  | S                                                                | 63 |

|       | 2.1.1    | Differences between H8S/2600 CPU and H8S/2000 CPU                | 64 |

|       | 2.1.2    | Differences from H8/300 CPU                                      | 65 |

|       | 2.1.3    | Differences from H8/300H CPU                                     | 65 |

| 2.2   | CPU O    | perating Modes                                                   | 66 |

|       | 2.2.1    | Normal Mode                                                      | 66 |

|       | 2.2.2    | Advanced Mode                                                    | 67 |

| 2.3   | Addres   | s Space                                                          | 70 |

| 2.4   | Registe  | r Configuration                                                  | 71 |

|       | 2.4.1    | General Registers                                                | 72 |

|       | 2.4.2    | Program Counter (PC)                                             | 73 |

|       | 2.4.3    | Extended Control Register (EXR)                                  | 73 |

|       | 2.4.4    | Condition-Code Register (CCR)                                    | 74 |

|       | 2.4.5    | Initial Values of CPU Registers                                  | 75 |

| 2.5   | Data Fo  | ormats                                                           | 76 |

|       | 2.5.1    | General Register Data Formats                                    | 76 |

|       | 2.5.2    | Memory Data Formats                                              | 78 |

| 2.6   | Instruct | ion Set                                                          | 79 |

|       | 2.6.1    | Table of Instructions Classified by Function                     | 80 |

|       | 2.6.2    | Basic Instruction Formats                                        |    |

| 2.7   | Addres   | sing Modes and Effective Address Calculation                     | 90 |

|       | 2.7.1    | Register Direct—Rn                                               | 91 |

|       | 2.7.2    | Register Indirect—@ERn                                           | 91 |

|       | 2.7.3    | Register Indirect with Displacement-@(d:16, ERn) or @(d:32, ERn) | 91 |

|       | 2.7.4    | Register Indirect with Post-Increment-@ERn+ or Register Indirect |    |

|       |          | with Pre-Decrement—@-ERn                                         |    |

|       | 2.7.5    | Absolute Address-@aa:8, @aa:16, @aa:24, or @aa:32                | 91 |

|       | 2.7.6    | Immediate—#xx:8, #xx:16, or #xx:32                               | 92 |

### Section 5 Interrupt Controller

| Table 5.1 | Pin Configuration                                                      | .129 |

|-----------|------------------------------------------------------------------------|------|

| Table 5.2 | Interrupt Sources, Vector Addresses, and Interrupt Priorities          | .137 |

| Table 5.3 | Interrupt Control Modes                                                | .142 |

| Table 5.4 | Interrupts Selected in Each Interrupt Control Mode (1)                 | .143 |

| Table 5.5 | Interrupts Selected in Each Interrupt Control Mode (2)                 | .144 |

| Table 5.6 | Operations and Control Signal Functions in Each Interrupt Control Mode | .144 |

| Table 5.7 | Interrupt Response Times                                               | .150 |

| Table 5.8 | Number of States in Interrupt Handling Routine Execution Status        | .151 |

| Table 5.9 | Interrupt Source Selection and Clear Control                           | .153 |

#### Section 7 Bus Controller

| Table 7.1 | Pin Configuration                                      | 167 |

|-----------|--------------------------------------------------------|-----|

| Table 7.2 | Bus Specifications for Each Area (Basic Bus Interface) | 177 |

| Table 7.3 | Data Buses Used and Valid Strobes                      |     |

| Table 7.4 | Pin States in Idle Cycle                               | 196 |

| Table 7.5 | Pin States in Bus Released State                       | 197 |

#### Section 8 DMA Controller (DMAC)

| Table 8.1  | Pin Configuration                                    | 205 |

|------------|------------------------------------------------------|-----|

| Table 8.2  | Short Address Mode and Full Address Mode (Channel 0) |     |

| Table 8.3  | DMAC Activation Sources                              | 232 |

| Table 8.4  | DMAC Transfer Modes                                  | 234 |

| Table 8.5  | Register Functions in Sequential Mode                | 236 |

| Table 8.6  | Register Functions in Idle Mode                      | 239 |

| Table 8.7  | Register Functions in Repeat Mode                    | 241 |

| Table 8.8  | Register Functions in Single Address Mode            | 245 |

| Table 8.9  | Register Functions in Normal Mode                    |     |

| Table 8.10 | Register Functions in Block Transfer Mode            | 251 |

| Table 8.11 | DMAC Channel Priority Order                          | 271 |

| Table 8.12 | Interrupt Sources and Priority Order                 | 275 |

#### Section 9 Data Transfer Controller (DTC)

| Table 9.1 | Activation Source and DTCER Clearance                            |  |

|-----------|------------------------------------------------------------------|--|

| Table 9.2 | Interrupt Sources, DTC Vector Addresses, and Corresponding DTCEs |  |

| Table 9.3 | Register Information in Normal Mode                              |  |

| Table 9.4 | Register Information in Repeat Mode                              |  |

| Table 9.5 | Register Information in Block Transfer Mode                      |  |

| Table 9.6 | DTC Execution Status                                             |  |

Section 1 Overview

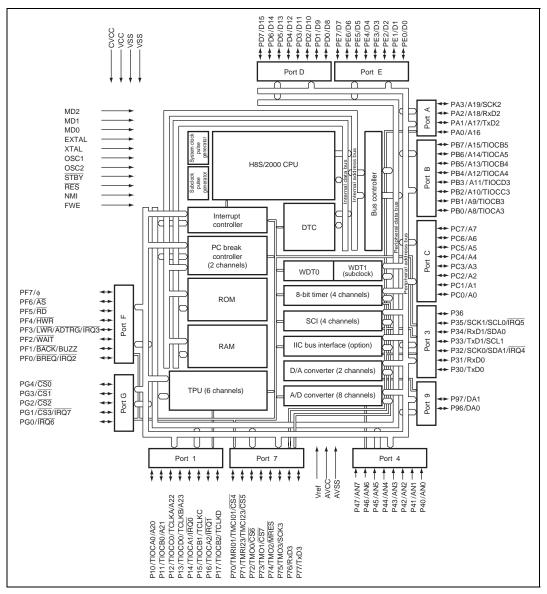

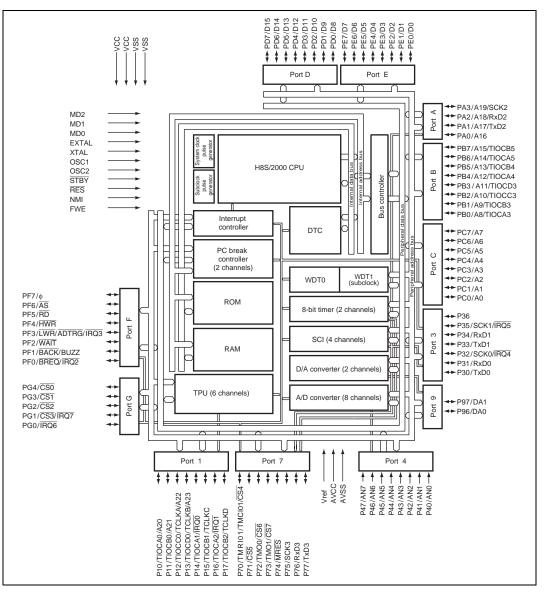

Figure 1.3 Internal Block Diagram of H8S/2238 Group

Figure 1.4 Internal Block Diagram of H8S/2237 Group

# Section 5 Interrupt Controller

### 5.1 Features

This LSI controls interrupts with the interrupt controller. The interrupt controller has the following features:

- Two interrupt control modes

- Any of two interrupt control modes can be set by means of the INTM1 and INTM0 bits in the system control register (SYSCR).

- Priorities settable with IPR

- An interrupt priority register (IPR) is provided for setting interrupt priorities. Eight priority levels can be set for each module for all interrupts except NMI. NMI is assigned the highest priority level of 8, also accepted (using nesting) during interrupt processing. Additionally accepted during state 12 if Opcode = H'57F3.

- Independent vector addresses

- All interrupt sources are assigned independent vector addresses, making it unnecessary for the source to be identified in the interrupt handling routine.

- Nine external interrupts

- NMI is the highest-priority interrupt, and is accepted at all times. Rising edge or falling edge can be selected for NMI. Falling edge, rising edge, or both edge detection, or level sensing, can be independently selected for IRQ7 to IRQ0.

- DTC and DMAC\* control

- The DTC and DMAC\* can be activated by an interrupt request.

- Note: \* Supported only by the H8S/2239 Group.

|                     |                | Object of Access   |                   |                   |                   |                   |  |

|---------------------|----------------|--------------------|-------------------|-------------------|-------------------|-------------------|--|

|                     |                |                    | External Device   |                   |                   |                   |  |

|                     |                |                    | 8                 | Bit Bus           | 16                | Bit Bus           |  |

| Symbol              |                | Internal<br>Memory | 2-State<br>Access | 3-State<br>Access | 2-State<br>Access | 3-State<br>Access |  |

| Instruction fetch   | S              | 1                  | 4                 | 6 + 2 m           | 2                 | 3 + m             |  |

| Branch address read | S              |                    |                   |                   |                   |                   |  |

| Stack manipulation  | S <sub>κ</sub> |                    |                   |                   |                   |                   |  |

#### Table 5.8 Number of States in Interrupt Handling Routine Execution Status

Legend:

m: Number of wait states in an external device access.

#### 5.5.6 DTC and DMAC\* Activation by Interrupt

The DTC and DMAC\* can be started by interrupts. The following settings are required for this operation.

- 1. Interrupt request to the CPU

- 2. Start request to the DTC

- 3. Start request to the DMAC\*

- 4. Multiple specification of items 1 to 3.

See section 8, DMA Controller (DMAC)\*, and section 9, Data Transfer Controller (DTC) for more information on the interrupts that can start the DTC and DMAC\*.

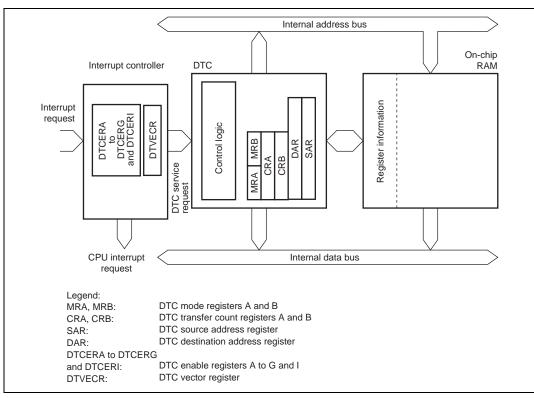

Figure 5.8 shows the block diagram of the DTC, DMAC\*, and interrupt controller circuits.

Note: \* Supported only by the H8S/2239 Group.

Transfer requests (activation sources) consist of A/D converter conversion end interrupts, external requests, SCI transmit-data-empty and receive-data-full interrupts, and TPU channel 0 to 5 compare match/input capture A interrupts. External requests can only be specified for channel B.

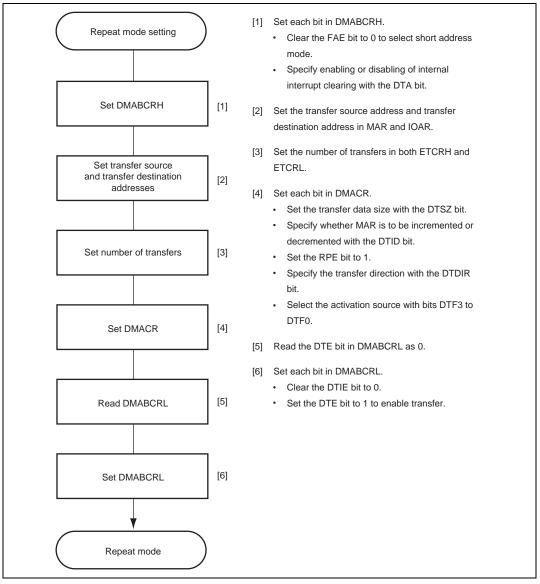

Figure 8.8 shows an example of the setting procedure for repeat mode.

#### Figure 8.8 Example of Repeat Mode Setting Procedure

Figure 9.1 Block Diagram of DTC

### 9.2 **Register Descriptions**

The DTC has the following registers.

- DTC mode register A (MRA)

- DTC mode register B (MRB)

- DTC source address register (SAR)

- DTC destination address register (DAR)

- DTC transfer count register A (CRA)

- DTC transfer count register B (CRB)

These six registers cannot be directly accessed from the CPU.

When activated, the DTC reads a set of register information that is stored in on-chip RAM to the corresponding DTC registers and transfers data. After the data transfer, it writes a set of updated register information back to the RAM.

| Interrupt<br>Source     | Origin of<br>Interrupt Source | Vector Number | DTC<br>Vector Address         | DTCE <sup>*1</sup> | Priority         |

|-------------------------|-------------------------------|---------------|-------------------------------|--------------------|------------------|

| Software                | Write to DTVECR               | DTVECR        | H'0400 +<br>vector number × 2 |                    | High<br><b>≜</b> |

| External pin            | IRQ0                          | 16            | H'0420                        | DTCEA7             | _                |

|                         | IRQ1                          | 17            | H'0422                        | DTCEA6             | -                |

|                         | IRQ2                          | 18            | H'0424                        | DTCEA5             | -                |

|                         | IRQ3                          | 19            | H'0426                        | DTCEA4             | -                |

|                         | IRQ4                          | 20            | H'0428                        | DTCEA3             | -                |

|                         | IRQ5                          | 21            | H'042A                        | DTCEA2             | -                |

|                         | IRQ6                          | 22            | H'042C                        | DTCEA1             | -                |

|                         | IRQ7                          | 23            | H'042E                        | DTCEA0             | -                |

| A/D<br>converter        | ADI (A/D conversion end)      | 28            | H'0438                        | DTCEB6             | -                |

| TPU                     | TGI0A                         | 32            | H'0440                        | DTCEB5             | _                |

| Channel 0               | TGI0B                         | 33            | H'0442                        | DTCEB4             | -                |

|                         | TGI0C                         | 34            | H'0444                        | DTCEB3             | -                |

|                         | TGI0D                         | 35            | H'0446                        | DTCEB2             | _                |

| TPU                     | TGI1A                         | 40            | H'0450                        | DTCEB1             | _                |

| Channel 1               | TGI1B                         | 41            | H'0452                        | DTCEB0             | -                |

| TPU                     | TGI2A                         | 44            | H'0458                        | DTCEC7             | _                |

| Channel 2               | TGI2B                         | 45            | H'045A                        | DTCEC6             | -                |

| TPU                     | TGI3A                         | 48            | H'0460                        | DTCEC5             | -                |

| Channel 3 <sup>*4</sup> | TGI3B                         | 49            | H'0462                        | DTCEC4             | -                |

|                         | TGI3C                         | 50            | H'0464                        | DTCEC3             | -                |

|                         | TGI3D                         | 51            | H'0466                        | DTCEC2             | -                |

| TPU                     | TGI4A                         | 56            | H'0470                        | DTCEC1             | -                |

| Channel 4*4             | TGI4B                         | 57            | H'0472                        | DTCEC0             | -                |

| TPU                     | TGI5A                         | 60            | H'0478                        | DTCED5             | -                |

| Channel 5*4             | TGI5B                         | 61            | H'047A                        | DTCED4             | -                |

| 8-bit timer             | CMIA0                         | 64            | H'0480                        | DTCED3             | -                |

| channel 0               | CMIB0                         | 65            | H'0482                        | DTCED2             | Low              |

#### Table 9.2 Interrupt Sources, DTC Vector Addresses, and Corresponding DTCEs

#### • P35/SCK1/SCL0/IRQ5

The pin functions are switched as shown below according to the combination of the ICE bit<sup>\*3</sup> in ICCR\_0 of IIC\_0, the C/A bit in SMR\_1 of SCI\_1, CKE0 and CKE1 bits in SCR\_1, and the P35DDR bit. To use this port as SCL0 I/O pin, clear the C/A bit, CKE1 bit, and CKE0 bit to 0. The SCL0 functions as NMOS open drain output and the pin can drive bus directly. When this pin is specified as the P35 output pin or SCK1 output pin, it functions as NMOS push/pull output <sup>\*4</sup>

| output.           |                  |                                 |                                  |                                  |                   |                               |

|-------------------|------------------|---------------------------------|----------------------------------|----------------------------------|-------------------|-------------------------------|

| ICE <sup>*3</sup> |                  |                                 | 0                                |                                  |                   | 1                             |

| CKE1              |                  | (                               | )                                |                                  | 1                 | 0                             |

| C/Ā               |                  | 0                               |                                  | 1                                | _                 | 0                             |

| CKE0              | 0                |                                 | 1                                | —                                | _                 | 0                             |

| P35DDR            | 0                | 1                               | —                                | —                                | _                 | —                             |

| Pin functions     | P35 input<br>pin | P35 output<br>pin <sup>*1</sup> | SCK1 output<br>pin <sup>*1</sup> | SCK1 output<br>pin <sup>*1</sup> | SCK1 input<br>pin | SCL0 I/O<br>pin <sup>*3</sup> |

|                   | IRQ5 Input pin*2 |                                 |                                  |                                  |                   |                               |

Notes: 1. When the P35ODR is set to 1, it functions as NMOS open drain output. When the P35ODR is cleared to 0, it functions as NMOS push/pull output.<sup>\*4</sup>

- 2. When this pin is used as an external interrupt pin, do not specify other functions.

- 3. Not available in the H8S/2237 Group and H8S/2227 Group.

- 4. It functions as CMOS output in the H8S/2237 Group and H8S/2227 Group.

#### • P34/RxD1/SDA0

The pin functions are switched as shown below according to the combination of the ICE bit<sup>\*2</sup> in ICCR\_0 of IIC\_0, the RE bit in SCR\_1 of SCI\_1, and the P34DDR bit. When this pin is specified as P34 output pin, it functions as NMOS push-pull output.<sup>\*3</sup> The SDA0 also functions as NMOS open drain outputs and can drive bus directly.

| ICE <sup>*2</sup> | 0 1                                        |   |                |                            |  |  |

|-------------------|--------------------------------------------|---|----------------|----------------------------|--|--|

| RE                | 0                                          |   | 1              | —                          |  |  |

| P34DDR            | 0                                          | 1 | _              | —                          |  |  |

| Pin functions     | P34 input pin P34 output pin <sup>*1</sup> |   | RxD1 input pin | SDA0 I/O pin <sup>*2</sup> |  |  |

Notes: 1. When P34ODR is set to 1, it functions as NMOS open drain output. When the P34ODR is cleared to 0, it functions as NMOS push/pull output.<sup>\*3</sup>

- 2. Not available in theH8S/2237 Group and H8S/2227 Group.

- 3. It functions as CMOS output in the H8S/2237 Group and H8S/2227 Group.

Section 11 16-Bit Timer Pulse Unit (TPU)

| ltem                             | Channel 0                                                                          | Channel 1                                              | Channel 2                                              | Channel 3                                                                          | Channel 4                                              | Channel 5                                      |

|----------------------------------|------------------------------------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|------------------------------------------------------------------------------------|--------------------------------------------------------|------------------------------------------------|

| DTC<br>activation                | TGR<br>compare<br>match or<br>input capture                                        | TGR<br>compare<br>match or<br>input capture            | TGR<br>compare<br>match or<br>input capture            | TGR<br>compare<br>match or<br>input capture                                        | TGR<br>compare<br>match or<br>input capture            | TGR<br>compare<br>match or<br>input capture    |

| DMAC <sup>*2</sup><br>activation | TGRA_0<br>compare<br>match or<br>input capture                                     | TGRA_1<br>compare<br>match or<br>input capture         | TGRA_2<br>compare<br>match or<br>input capture         | TGRA_3<br>compare<br>match or<br>input capture                                     | TGRA_4<br>compare<br>match or<br>input capture         | TGRA_5<br>compare<br>match or<br>input capture |

| A/D<br>converter<br>trigger      | TGRA_0<br>compare<br>match or<br>input capture                                     | TGRA_1<br>compare<br>match or<br>input capture         | TGRA_2<br>compare<br>match or<br>input capture         | TGRA_3<br>compare<br>match or<br>input capture                                     | TGRA_4<br>compare<br>match or<br>input capture         | TGRA_5<br>compare<br>match or<br>input capture |

| Interrupt                        | 5 sources                                                                          | 4 sources                                              | 4 sources                                              | 5 sources                                                                          | 4 sources                                              | 4 sources                                      |

| sources                          | <ul> <li>Compare<br/>match or<br/>input capture<br/>0A</li> <li>Compare</li> </ul> | Compare<br>match or<br>input capture<br>1A     Compare | Compare<br>match or<br>input<br>capture 2A     Compare | <ul> <li>Compare<br/>match or<br/>input capture<br/>3A</li> <li>Compare</li> </ul> | Compare<br>match or<br>input capture<br>4A     Compare | 5A                                             |

|                                  | • Compare<br>match or<br>input<br>capture 0B                                       | Compare<br>match or<br>input capture<br>1B             | match or                                               | match or                                                                           | Compare<br>match or<br>input capture<br>4B             | Compare<br>match or<br>input capture<br>5B     |

|                                  | Compare<br>match or<br>input capture<br>0C                                         | e                                                      |                                                        | Compare<br>match or<br>input capture<br>3C                                         | e                                                      |                                                |

|                                  | Compare<br>match or<br>input capture<br>0D                                         | e                                                      |                                                        | Compare<br>match or<br>input capture<br>3D                                         | e                                                      |                                                |

|                                  | <ul> <li>Overflow</li> </ul>                                                       |                                                        |                                                        | <ul> <li>Overflow</li> </ul>                                                       |                                                        |                                                |

|                                  |                                                                                    | <ul> <li>Overflow</li> </ul>                           | • Overflow                                             |                                                                                    | • Overflow                                             | Overflow                                       |

| Levendu                          |                                                                                    | • Underflow                                            | • Underflow                                            |                                                                                    | • Underflow                                            | Underflow                                      |

#### Legend:

O: Possible

--: Not possible

Notes: 1. Not available in the H8S/2227 Group.

2. Supported only by the H8S/2239 Group.

#### 11.3.1 Timer Control Register (TCR)

The TCR registers control the TCNT operation for each channel. The TPU of the H8S/2227 Group has a total of three TCR registers, one each for channels 0 to 2. In other groups, the TPU has a total of six TCR registers, one each for channels 0 to 5. TCR register settings should be made only when TCNT operation is stopped.

| Bit    | Bit Name       | Initial Value | R/W        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------|----------------|---------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7      | CCLR2          | 0             | R/W        | Counter Clear 2 to 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 6<br>5 | CCLR1<br>CCLR0 | 0<br>0        | R/W<br>R/W | These bits select the TCNT counter clearing source.<br>See tables 11.3 and 11.4 for details.                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 4      | CKEG1          | 0             | R/W        | Clock Edge 1 and 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 3      | CKEG0          | 0             | R/W        | These bits select the input clock edge. When the input clock is counted using both edges, the input clock period is halved (e.g. $\phi/4$ both edges = $\phi/2$ rising edge). If phase counting mode is used on channels 1, 2, 4*, and 5*, this setting is ignored and the phase counting mode setting has priority. Internal clock edge selection is valid when the input clock is $\phi/4$ or slower. When the input clock is $\phi/1$ or when overflow/underflow of another channel is selected, this setting is ignored and the falling edge of $\phi$ . |

|        |                |               |            | 00: Count at rising edge                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|        |                |               |            | 01: Count at falling edge                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|        |                |               |            | 1×: Count at both edges                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|        |                |               |            | Legend: x: Don't care                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 2      | TPSC2          | 0             | R/W        | Time Prescaler 2 to 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 1<br>0 | TPSC1<br>TPSC0 | 0<br>0        | R/W<br>R/W | These bits select the TCNT counter clock. The clock source can be selected independently for each channel. See tables 11.5 to 11.10 for details.                                                                                                                                                                                                                                                                                                                                                                                                             |

Note: \* Not available in the H8S/2227 Group.

| Channel | Bit 2<br>TPSC2 | Bit 1<br>TPSC1 | Bit 0<br>TPSC0 | Description                               |

|---------|----------------|----------------|----------------|-------------------------------------------|

| 4*      | 0              | 0              | 0              | Internal clock: counts on $\phi/1$        |

|         |                |                | 1              | Internal clock: counts on $\phi/4$        |

|         |                | 1              | 0              | Internal clock: counts on $\phi/16$       |

|         |                |                | 1              | Internal clock: counts on \u00e6/64       |

|         | 1              | 0              | 0              | External clock: counts on TCLKA pin input |

|         |                |                | 1              | External clock: counts on TCLKC pin input |

|         |                | 1              | 0              | Internal clock: counts on $\phi/1024$     |

|         |                |                | 1              | Counts on TCNT5 overflow/underflow        |

#### Table 11.9 TPSC2 to TPSC0 (Channel 4)

Notes: This setting is ignored when channel 4 is in phase counting mode.

\* Not available in the H8S/2227 Group.

#### Table 11.10 TPSC2 to TPSC0 (Channel 5)

| Channel | Bit 2<br>TPSC2 | Bit 1<br>TPSC1 | Bit 0<br>TPSC0 | Description                               |

|---------|----------------|----------------|----------------|-------------------------------------------|

| 5*      | 0              | 0              | 0              | Internal clock: counts on $\phi/1$        |

|         |                |                | 1              | Internal clock: counts on                 |

|         |                | 1              | 0              | Internal clock: counts on                 |

|         |                | 1              |                | Internal clock: counts on                 |

|         | 1              | 0              | 0              | External clock: counts on TCLKA pin input |

|         |                |                | 1              | External clock: counts on TCLKC pin input |

|         |                | 1              | 0              | Internal clock: counts on                 |

|         |                |                | 1              | External clock: counts on TCLKD pin input |

Notes: This setting is ignored when channel 5 is in phase counting mode.

\* Not available in the H8S/2227 Group.

| Table 1       | 1.16 110      | )KH_3         |               |                                  |                                    |  |  |  |  |  |

|---------------|---------------|---------------|---------------|----------------------------------|------------------------------------|--|--|--|--|--|

|               |               |               |               |                                  | Description                        |  |  |  |  |  |

| Bit 7<br>IOB3 | Bit 6<br>IOB2 | Bit 5<br>IOB1 | Bit 4<br>IOB0 | TGRB_3<br>Function <sup>*2</sup> | TIOCB3 Pin Function*2              |  |  |  |  |  |

| 0             | 0             | 0             | 0             | Output                           | Output disabled                    |  |  |  |  |  |

|               |               |               | 1             | compare<br>register              | Initial output is 0 output         |  |  |  |  |  |

|               |               |               |               | rogiotor                         | 0 output at compare match          |  |  |  |  |  |

|               |               | 1             | 0             |                                  | Initial output is 0 output         |  |  |  |  |  |

|               |               |               |               | _                                | 1 output at compare match          |  |  |  |  |  |

|               |               | 1             |               |                                  | Initial output is 0 output         |  |  |  |  |  |

|               |               |               |               |                                  | Toggle output at compare match     |  |  |  |  |  |

|               | 1             | 0 0           |               | _                                | Output disabled                    |  |  |  |  |  |

|               |               |               | 1             | -                                | Initial output is 1 output         |  |  |  |  |  |

|               |               |               |               |                                  | 0 output at compare match          |  |  |  |  |  |

|               |               | 1             | 0             |                                  | Initial output is 1 output         |  |  |  |  |  |

|               |               |               |               | _                                | 1 output at compare match          |  |  |  |  |  |

|               |               |               | 1             |                                  | Initial output is 1 output         |  |  |  |  |  |

|               |               |               |               |                                  | Toggle output at compare match     |  |  |  |  |  |

| 1             | 0             | 0             | 0             | Input                            | Capture input source is TIOCB3 pin |  |  |  |  |  |

|               |               |               |               | capture<br>register              | Input capture at rising edge       |  |  |  |  |  |

|               |               |               | 1             | . egiotoi                        | Capture input source is TIOCB3 pin |  |  |  |  |  |

Table 11.16 TIORH\_3

Legend: ×: Don't care

1

1

×

Notes: 1. When bits TPSC2 to TPSC0 in TCR\_4 are set to B'000 and  $\phi/1$  is used as the TCNT\_4 count clock, this setting is invalid and input capture is not generated.

down\*1

Input capture at falling edge

Input capture at both edges

Capture input source is TIOCB3 pin

Capture input source is channel 4/count clock

Input capture at TCNT\_4 count-up/count-

2. Not available in the H8S/2227 Group.

х

х

| Field name       | He             | ader                                                             | Maste<br>address f                                                   |        | Slave ade<br>field |      | SS   | Contro       | l fie | ld | Mes<br>lengt              | · · |   |              |      | Da   | ta fi | ield         |    |   |

|------------------|----------------|------------------------------------------------------------------|----------------------------------------------------------------------|--------|--------------------|------|------|--------------|-------|----|---------------------------|-----|---|--------------|------|------|-------|--------------|----|---|

| Number           | 1              | 1                                                                | 12                                                                   | 1      | 12                 | 1    | 1    | 4            | 1     | 1  | 8                         | 1   | 1 | 8            | 1    | 1    |       | 8            | 1  | 1 |

| of bits          | Start<br>bit   | Broad-<br>cast<br>bit                                            | Master<br>address                                                    | Ρ      | Slave<br>address   | Р    | A    | Control bits | Р     | A  | Message<br>length<br>bits | Ρ   | A | Data<br>bits | Р    | A    |       | Data<br>bits | Ρ  | A |

| Transfer<br>time |                |                                                                  | 1                                                                    |        |                    |      |      |              |       |    |                           |     |   |              | 1    |      |       |              |    |   |

| Mode 0           |                | Approximately 7330 $\mu$ s Approximately 1590 $\times$ N $\mu$ s |                                                                      |        |                    |      |      |              |       |    |                           |     |   |              |      |      |       |              |    |   |

| Mode 1           |                |                                                                  |                                                                      |        | Approxim           | atel | y 20 | )90 μs       |       |    |                           |     |   | Ap           | prox | kima | tely  | 410×№        | õs |   |

| Mode 2           |                | Approximately 1590 μs Approximately 300 × N μs                   |                                                                      |        |                    |      |      |              |       |    |                           |     |   |              |      |      |       |              |    |   |

|                  | A: A<br>W<br>W | cknov<br>'hen A<br>'hen A                                        | bit (1 bit)<br>vledge bit<br>A = 0: ACP<br>A = 1: NAP<br>er of bytes | Č<br>K | pit)               |      |      |              |       |    |                           |     |   |              |      |      |       |              |    |   |

Figure 14.2 Transfer Signal Format

#### (1) Header

Header is comprised of a start bit and a broadcast bit.

(a) Start Bit

The start bit is a signal for informing a start of data transfer to other units. A unit, which attempts to start data transfer, outputs a low-level signal (start bit) for a specified period and then outputs the broadcast bit.

If another unit is already outputting a start bit when a unit attempts to output a start bit, the unit waits for completion of output of the start bit from the other unit without outputting the start bit, and then outputs the broadcast bit synchronized with the completion timing.

Other units enter the receive state after detecting the start bit.

(b) Broadcast Bit

The broadcast bit is a bit to identify the type of communications: broadcast or normal.

When this bit is cleared to 0, it indicates the broadcast communications. When it is set to 1, it indicates the normal communications. Broadcast communications includes group broadcast and general broadcast, which are identified by a value of the slave address. (For details of the slave address, see section 14.1.2 (3), Slave Address Field.)

Since there are multiple slave units, which are communications destination units, in the case of broadcast communications, the acknowledge bit is not returned from each field described in (2) and below.

#### 14.3.9 IEBus Transmit Buffer Register (IETBR)

IETBR is a 1-byte buffer to which data to be transmitted in master or slave transmission is written. IETBR is empty when the TxRDY flag in IETSR is 1. Check the TxRDY flag before setting transmit data in IETBR.

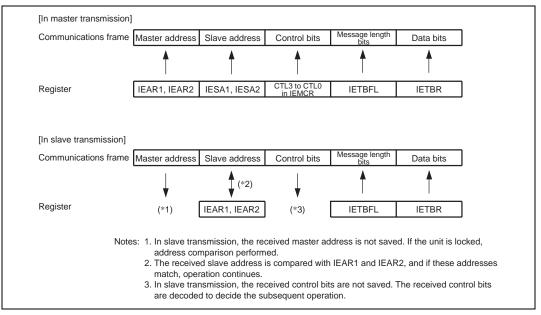

Data written in IETBR is transmitted in the data field in master or slave transmission. Figure 14.6 shows the correspondence between the communications signal format and registers for IEBus data transfer.

| Bit | Bit Name | Initial Value | R/W | Description                                      |

|-----|----------|---------------|-----|--------------------------------------------------|

| 7   | TBR7     | 0             | R/W | Data to be transmitted is written to this 1-byte |

| 6   | TBR6     | 0             | R/W | buffer.                                          |

| 5   | TBR5     | 0             | R/W |                                                  |

| 4   | TBR4     | 0             | R/W |                                                  |

| 3   | TBR3     | 0             | R/W |                                                  |

| 2   | TBR2     | 0             | R/W |                                                  |

| 1   | TBR1     | 0             | R/W |                                                  |

| 0   | TBR0     | 0             | R/W |                                                  |

| 1   | TBR1     | 0             | R/W |                                                  |

Figure 14.6 Transmission Signal Format and Registers in Data Transfer

| Bit | Bit Name | Initial<br>Value | R/W | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----|----------|------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3   | ACKE     | 0                | R/W | Acknowledge Bit Judgement Selection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|     |          |                  |     | 0: The value of the acknowledge bit is ignored, and<br>continuous transfer is performed. The value of the received<br>acknowledge bit is not indicated by the ACKB bit, which is<br>always 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|     |          |                  |     | 1: If the acknowledge bit is 1, continuous transfer is<br>interrupted.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|     |          |                  |     | In this LSI, the DTC can be used to perform continuous<br>transfer. The DTC is activated when the IRTR interrupt flag is<br>set to 1 (IRTR us one of two interrupt flags, the other being<br>IRIC). When the ACKE bit is 0, the TDRE, IRIC, and IRTR<br>flags are set on completion of data transmission, regardless of<br>the acknowledge bit. When the ACKE bit is 1, the TDRE,<br>IRIC, and IRTR flags are set on completion of data<br>transmission when the acknowledge bit is 0, and the IRIC flag<br>alone is set on completion of data transmission when the<br>acknowledge bit is 1.<br>When the DTC is activated, the TDRE, IRIC, and IRTR flags<br>are cleared to 0 after the specified number of data transfers<br>have been executed. Consequently, interrupts are not<br>generated during continuos data transfer, but if data<br>transmission is completed with a 1 acknowledge bit when the<br>ACKE bit is set to 1, the DTC is not activated and an interrupt<br>is generated, if enabled.<br>Depending on the receiving device, the acknowledge bit may<br>be significant, in indicating completion of processing of the<br>received data, for instance, or may be fixed at 1 and have no<br>significance. |

| 2   | BBSY     | 0                | R/W | Bus Busy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|     |          |                  |     | In slave mode, reading the BBSY flag enables to confirm<br>whether the $l^2C$ bus is occupied or released. The BBSY flag is<br>set to 0 when the SDA level changes from high to low under<br>the condition of SCI = high, assuming that the start condition<br>has been issued. The BBSY flag is cleared to 0 when the SDA<br>level changes from low to high under the condition of SCI =<br>high, assuming that the start condition has been issued.<br>Writing to the BBSY flag in slave mode is disabled.<br>In master mode, the BBSY flag is used to issue start and stop<br>conditions. Write 1 to BBSY and 0 to SCP to issue a start<br>condition. Follow this procedure when also re-transmitting a<br>start condition. To issue a start/stop condition, use the MOV<br>instruction. The $l^2C$ bus interface must be set in master<br>transmit mode before the issue of a start condition.                                                                                                                                                                                                                                                                                                                           |

|     |          |                  |     | Day 6.00 Mar 19, 2010 Dags 645 of 022                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

#### 17.3.2 A/D Control/Status Register (ADCSR)

ADCSR controls A/D conversion operations.

| Bit | Bit Name | Initial<br>Value | R/W    | Description                                                                                                                                                                                                                                                                                                                                                                   |

|-----|----------|------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | ADF      | 0                | R/(W)* | A/D End Flag                                                                                                                                                                                                                                                                                                                                                                  |

|     |          |                  |        | A status flag that indicates the end of A/D conversion.                                                                                                                                                                                                                                                                                                                       |

|     |          |                  |        | [Setting conditions]                                                                                                                                                                                                                                                                                                                                                          |

|     |          |                  |        | When A/D conversion ends in single mode                                                                                                                                                                                                                                                                                                                                       |

|     |          |                  |        | <ul> <li>When A/D conversion ends on all specified<br/>channels in scan mode</li> </ul>                                                                                                                                                                                                                                                                                       |

|     |          |                  |        | [Clearing conditions]                                                                                                                                                                                                                                                                                                                                                         |

|     |          |                  |        | • When 0 is written after reading ADF = 1                                                                                                                                                                                                                                                                                                                                     |

|     |          |                  |        | • When the data transfer controller (DTC) is                                                                                                                                                                                                                                                                                                                                  |

|     |          |                  |        | activated by an ADI interrupt and DISEL in DTC is 0 with the transfer counter not being 0                                                                                                                                                                                                                                                                                     |

| 6   | ADIE     | 0                | R/W    | A/D Interrupt Enable                                                                                                                                                                                                                                                                                                                                                          |

|     |          |                  |        | A/D conversion end interrupt (ADI) request enabled when 1 is set                                                                                                                                                                                                                                                                                                              |

| 5   | ADST     | 0                | R/W    | A/D Start                                                                                                                                                                                                                                                                                                                                                                     |

|     |          |                  |        | Clearing this bit to 0 stops A/D conversion, and the A/D converter enters the wait state.                                                                                                                                                                                                                                                                                     |

|     |          |                  |        | Setting this bit to 1 starts A/D conversion. In single<br>mode, this bit is cleared to 0 automatically when<br>conversion on the specified channel is complete. In<br>scan mode, conversion continues sequentially on<br>the specified channels until this bit is cleared to 0 by<br>software, a reset, software standby mode, hardware<br>standby mode, or module stop mode. |

|     |          |                  |        | The ADST bit can be set to 1 by software, a timer conversion start trigger, or the A/D external trigger input pin (ADTRG).                                                                                                                                                                                                                                                    |

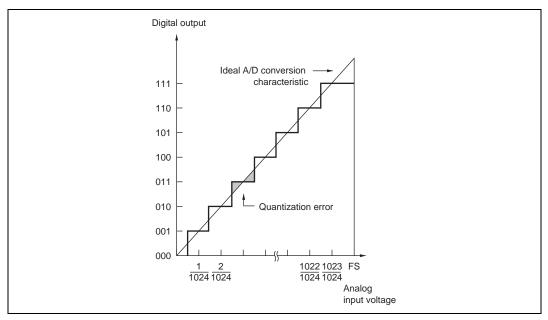

Figure 17.7 A/D Conversion Accuracy Definitions

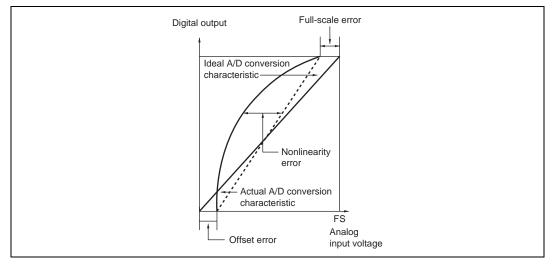

Figure 17.8 A/D Conversion Accuracy Definitions

#### (1) Clock Timing

Table 27.17 lists the clock timing.

#### Table 27.17 Clock Timing

Condition A (F-ZTAT version and masked ROM version):

$V_{cc} = 2.7 V \text{ to } 3.6 V, AV_{cc} = 2.7 V \text{ to } 3.6 V,$   $V_{ref} = 2.7 V \text{ to } AV_{cc}, V_{ss} = AV_{ss} = 0 V, \phi = 32.768 \text{ kHz},$ 2 to 16.0 MHz,  $T_a = -20^{\circ}\text{C}$  to  $+75^{\circ}\text{C}$  (regular specifications)

Condition B (Masked ROM version):

$$V_{cc} = 2.2 V \text{ to } 3.6 V$$

,  $AV_{cc} = 2.2 V \text{ to } 3.6 V$ ,

$V_{ref} = 2.2 V \text{ to } AV_{cc}$ ,  $V_{ss} = AV_{ss} = 0 V$ ,  $\phi = 32.768 \text{ kHz}$ ,

$2 \text{ to } 6.25 \text{ MHz}$ ,  $T_a = -20^{\circ}\text{C}$  to  $+75^{\circ}\text{C}$  (regular

specifications),  $T_a = -40^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$  (wide-range

specifications)

Condition C (F-ZTAT version and masked ROM version):

$V_{cc} = 3.0 \text{ V to } 3.6 \text{ V}, \text{ AV}_{cc} = 3.0 \text{ V to } 3.6 \text{ V},$   $V_{ref} = 3.0 \text{ V to } \text{AV}_{cc}, \text{ V}_{ss} = \text{AV}_{ss} = 0 \text{ V}, \phi = 32.768 \text{ kHz},$ 10.0 to 20.0 MHz,  $T_a = -20^{\circ}\text{C}$  to  $+75^{\circ}\text{C}$  (regular specifications),  $T_a = -40^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$  (wide-range specifications)

|                                                            |                   | Condition A |     |     | Condition B |     |     | (   | Conditio | on C |      | Test            |  |

|------------------------------------------------------------|-------------------|-------------|-----|-----|-------------|-----|-----|-----|----------|------|------|-----------------|--|

| Item                                                       | Symbol            | Min         | Тур | Мах | Min         | Тур | Max | Min | Тур      | Max  | Unit | Conditions      |  |

| Clock cycle<br>time                                        | t <sub>cyc</sub>  | 62.5        | —   | 500 | 160         | _   | 500 | 50  | _        | 100  | ns   | Figure<br>27.10 |  |

| Clock high pulse width                                     | t <sub>ch</sub>   | 20          | _   | —   | 50          | _   | _   | 17  | _        |      | ns   | _               |  |

| Clock low pulse width                                      | t <sub>cL</sub>   | 20          | _   | —   | 50          | _   | _   | 17  | _        |      | ns   | _               |  |

| Clock rise<br>time                                         | t <sub>cr</sub>   | _           |     | 10  | _           |     | 25  | _   |          | 10   | ns   | _               |  |

| Clock fall time                                            | t <sub>cf</sub>   | —           | _   | 10  |             | _   | 25  |     | _        | 10   | ns   | _               |  |

| Oscillation<br>stabilization<br>time at reset<br>(crystal) | t <sub>osc1</sub> | 20          |     |     | 40          |     |     | 20  |          |      | ms   | Figure<br>27.11 |  |