Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | H8S/2000                                                                     |

| Core Size                  | 16-Bit                                                                       |

| Speed                      | 16MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, SCI, SmartCard                                             |

| Peripherals                | DMA, POR, PWM, WDT                                                           |

| Number of I/O              | 72                                                                           |

| Program Memory Size        | 384KB (384K x 8)                                                             |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 32K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                                  |

| Data Converters            | A/D 8x10b; D/A 2x8b                                                          |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -20°C ~ 75°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 100-BFQFP                                                                    |

| Supplier Device Package    | 100-QFP (14x14)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/df2239fa16v |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

The revision list can be viewed directly by clicking the title page. The revision list summarizes the locations of revisions and additions. Details should always be checked by referring to the relevant text.

# H8S/2258, H8S/2239, H8S/2238, H8S/2237, H8S/2227 Groups

Hardware Manual Renesas 16-Bit Single-Chip Microcomputer H8S Family/H8S/2200 Series

| H8S/2258  | HD64F2258<br>HD6432258 | H8S/2236R | HD6432236R<br>HD6432236RW |

|-----------|------------------------|-----------|---------------------------|

|           | HD6432258W             | H8S/223   | HD6472237                 |

| H8S/2256  | HD6432256              |           | HD6432237                 |

|           | HD6432256W             | H8S/2235  | HD6432235                 |

| H8S/2239  | HD64F2239              | H8S/2233  | HD6432233                 |

|           | HD6432239              | H8S/2227  | HD64F2227                 |

|           | HD6432239W             |           | HD6432227                 |

| H8S/2238  | HD64F2238B             | H8S/2225  | HD6432225                 |

|           | HD6432238B             | H8S/2224  | HD6432224                 |

|           | HD6432238BW            | H8S/2223  | HD6432223                 |

| H8S/2238R | HD64F2238R             |           |                           |

|           | HD6432238R             |           |                           |

|           | HD6432238RW            |           |                           |

| H8S/2236B | HD6432236B             |           |                           |

|           | HD6432236BW            |           |                           |

#### • On-chip memory

| ROM          | Model       | ROM        | RAM       | Remarks |

|--------------|-------------|------------|-----------|---------|

| Flash memory | HD64F2258   | 256 kbytes | 16 kbytes |         |

| version      | HD64F2239   | 384 kbytes | 32 kbytes |         |

|              | HD64F2238B  | 256 kbytes | 16 kbytes |         |

|              | HD64F2238R  | 256 kbytes | 16 kbytes |         |

|              | HD64F2227   | 128 kbytes | 16 kbytes |         |

| PROM version | HD6472237   | 128 kbytes | 16 kbytes |         |

| Masked ROM   | HD6432258   | 256 kbytes | 16 kbytes |         |

| version      | HD6432258W  | 256 kbytes | 16 kbytes |         |

|              | HD6432256   | 128 kbytes | 8 kbytes  |         |

|              | HD6432256W  | 128 kbytes | 8 kbytes  |         |

|              | HD6432239   | 384 kbytes | 32 kbytes |         |

|              | HD6432239W  | 384 kbytes | 32 kbytes |         |

|              | HD6432238B  | 256 kbytes | 16 kbytes |         |

|              | HD6432238BW | 256 kbytes | 16 kbytes |         |

|              | HD6432238R  | 256 kbytes | 16 kbytes |         |

|              | HD6432238RW | 256 kbytes | 16 kbytes |         |

|              | HD6432236B  | 128 kbytes | 8 kbytes  |         |

|              | HD6432236BW | 128 kbytes | 8 kbytes  |         |

|              | HD6432236R  | 128 kbytes | 8 kbytes  |         |

|              | HD6432236RW | 128 kbytes | 8 kbytes  |         |

|              | HD6432237   | 128 kbytes | 16 kbytes |         |

|              | HD6432235   | 128 kbytes | 4 kbytes  |         |

|              | HD6432233   | 64 kbytes  | 4 kbytes  |         |

|              | HD6432227   | 128 kbytes | 16 kbytes |         |

|              | HD6432225   | 128 kbytes | 4 kbytes  |         |

|              | HD6432224   | 96 kbytes  | 4 kbytes  |         |

|              | HD6432223   | 64 kbytes  | 4 kbytes  |         |

- General I/O ports

- I/O pins: 72

- Input-only pins: 10

- Supports various power-down states

|    | А                              | В                                       | С                              | D                                       | E       | F                             | G      | Н                                | J                                | К                                | L                                |

|----|--------------------------------|-----------------------------------------|--------------------------------|-----------------------------------------|---------|-------------------------------|--------|----------------------------------|----------------------------------|----------------------------------|----------------------------------|

| 11 | NC<br>(Reserve)                | PF1/<br>BACK/<br>BUZZ                   | PF4/<br>HWR                    | PF7/ø                                   | EXTAL   | XTAL                          | STBY   | OSC1                             | MD0                              | P40/AN0                          | NC<br>(Reserve)                  |

| 10 | P30/<br>TxD0                   | NC<br>(Reserve)                         | PF2/<br>WAIT                   | PF5/RD                                  | FWE     | VSS                           | vcc    | OSC2                             | AVCC                             | P41/AN1                          | P42/AN2                          |

| 9  | P33/<br>TxD1/<br>SCL1          | P32/<br>SCK0/<br>SDA1/<br>IRQ4          | PF0/<br>BREQ/<br>IRQ2          | PF3/<br>LWR/<br>ADTRG/<br>IRQ3          | MD2     | VCC                           | NMI    | MD1                              | NC<br>(Reserve)                  | P43/AN3                          | P45/AN5                          |

| 8  | P36                            | P35/<br>SCK1/<br>SCL0/<br>IRQ5          | P34/<br>RxD1/<br>SDA0          | P31/<br>RxD0                            | PF6/AS  | VSS                           | RES    | Vref                             | P44/AN4                          | P46/AN6                          | P96/DA0                          |

| 7  | P75/<br>TMO3/<br>SCK3          | P74/<br>TMO2/<br>MRES                   | P76/<br>RxD3                   | P77/<br>TxD3                            | -       |                               | ٨      | P47/AN7                          | P97/DA1                          | AVSS                             | AVSS                             |

| 6  | P72/<br>TMO0/<br>TEND0/<br>CS6 | P71/<br>TMRI23/<br>TMCI23/<br>DREQ1/CS5 | P73/<br>TMO1/<br>TEND1/<br>CS7 | P70/<br>TMRI01/<br>TMCI01/<br>DREQ0/CS4 | TE      | BP-112/<br>3P-112A<br>OP VIE\ | V      | P17/<br>TIOCB2/<br>TCLKD         | P14/<br>TIOCA1/<br>IRQ0          | P16/<br>TIOCA2/<br>IRQ1          | P15/<br>TIOCB1/<br>TCLKC         |

| 5  | PG0/<br>IRQ6                   | PG1/<br>CS3/<br>IRQ7                    | PG2/<br>CS2                    | PG4/<br>CS0                             |         |                               |        | P10/<br>TIOCA0/<br>DACK0/<br>A20 | P11/<br>TIOCB0/<br>DACK1/<br>A21 | P13/<br>TIOCD0/<br>TCLKB/<br>A23 | P12/<br>TIOCC0/<br>TCLKA/<br>A22 |

| 4  | PG3/<br>CS1                    | PE0/D0                                  | PE2/D2                         | PE7/D7                                  | PD5/D13 | VSS                           | PC5/A5 | PB6/<br>A14/<br>TIOCA5           | PA1/<br>A17/<br>TxD2             | PA2/<br>A18/<br>RxD2             | PA3/<br>A19/<br>SCK2             |

| 3  | PE1/D1                         | PE3/D3                                  | NC<br>(Reserve)                | PD2/D10                                 | PD6/D14 | CVCC                          | PC3/A3 | PB0/<br>A8/<br>TIOCA3            | PB3/<br>A11/<br>TIOCD3           | PB7/<br>A15/<br>TIOCB5           | PA0/A16                          |

| 2  | PE4/D4                         | PE5/D5                                  | PD0/D8                         | PD3/D11                                 | CVCC    | VSS                           | PC2/A2 | PC6/A6                           | PB1/A9/<br>TIOCB3                | PB4/<br>A12/<br>TIOCA4           | PB5/<br>A13/<br>TIOCB4           |

| 1  | NC<br>(Reserve)                | PE6/D6                                  | PD1/D9                         | PD4/D12                                 | PD7/D15 | PC0/A0                        | PC1/A1 | PC4/A4                           | PC7/A7                           | PB2/<br>A10/<br>TIOCC3           | NC<br>(Reserve)                  |

|    |                                |                                         |                                |                                         |         |                               |        |                                  |                                  |                                  |                                  |

### Figure 1.9 Pin Arrangement of H8S/2239 Group (TBP-112A, TBP-112AV: Top View, Only for HD64F2239)

Section 1 Overview

|                                                                       | Pin No.                                         |                                                                                                        | Pin Name           |                    |                    |                |                                                    |  |  |  |

|-----------------------------------------------------------------------|-------------------------------------------------|--------------------------------------------------------------------------------------------------------|--------------------|--------------------|--------------------|----------------|----------------------------------------------------|--|--|--|

| TFP-100B<br>TFP-100BV<br>TFP-100G<br>TFP-100GV<br>FP-100B<br>FP-100BV | FP-100A <sup>*1</sup><br>FP-100AV <sup>*1</sup> | BP-112 <sup>*2</sup><br>BP-112V <sup>*2</sup><br>TBP-112A <sup>*2</sup><br>TBP-<br>112AV <sup>*2</sup> | Mode 4             | Mode 5             | Mode 6             | Mode 7         | Flash Memory<br>Programmable<br>Mode <sup>*4</sup> |  |  |  |

| 1                                                                     | 4                                               | B2                                                                                                     | PE5/D5             | PE5/D5             | PE5/D5             | PE5            | ŌĒ                                                 |  |  |  |

| 2                                                                     | 5                                               | B1                                                                                                     | PE6/D6             | PE6/D6             | PE6/D6             | PE6            | WE                                                 |  |  |  |

| 3                                                                     | 6                                               | D4                                                                                                     | PE7/D7             | PE7/D7             | PE7/D7             | PE7            | CE                                                 |  |  |  |

| 4                                                                     | 7                                               | C2                                                                                                     | D8                 | D8                 | D8                 | PD0            | D0                                                 |  |  |  |

| 5                                                                     | 8                                               | C1                                                                                                     | D9                 | D9                 | D9                 | PD1            | D1                                                 |  |  |  |

| 6                                                                     | 9                                               | D3                                                                                                     | D10                | D10                | D10                | PD2            | D2                                                 |  |  |  |

| 7                                                                     | 10                                              | D2                                                                                                     | D11                | D11                | D11                | PD3            | D3                                                 |  |  |  |

| 8                                                                     | 11                                              | D1                                                                                                     | D12                | D12                | D12                | PD4            | D4                                                 |  |  |  |

| 9                                                                     | 12                                              | E4                                                                                                     | D13                | D13                | D13                | PD5            | D5                                                 |  |  |  |

| 10                                                                    | 13                                              | E3                                                                                                     | D14                | D14                | D14                | PD6            | D6                                                 |  |  |  |

| 11                                                                    | 14                                              | E1                                                                                                     | D15                | D15                | D15                | PD7            | D7                                                 |  |  |  |

| 12                                                                    | 15                                              | E2, F3                                                                                                 | CVCC               | CVCC               | CVCC               | CVCC           | VCC                                                |  |  |  |

| 13                                                                    | 16                                              | F1                                                                                                     | A0                 | A0                 | PC0/A0             | PC0            | A0                                                 |  |  |  |

| 14                                                                    | 17                                              | F2, F4                                                                                                 | VSS                | VSS                | VSS                | VSS            | VSS                                                |  |  |  |

| 15                                                                    | 18                                              | G1                                                                                                     | A1                 | A1                 | PC1/A1             | PC1            | A1                                                 |  |  |  |

| 16                                                                    | 19                                              | G2                                                                                                     | A2                 | A2                 | PC2/A2             | PC2            | A2                                                 |  |  |  |

| 17                                                                    | 20                                              | G3                                                                                                     | A3                 | A3                 | PC3/A3             | PC3            | A3                                                 |  |  |  |

| 18                                                                    | 21                                              | H1                                                                                                     | A4                 | A4                 | PC4/A4             | PC4            | A4                                                 |  |  |  |

| 19                                                                    | 22                                              | G4                                                                                                     | A5                 | A5                 | PC5/A5             | PC5            | A5                                                 |  |  |  |

| 20                                                                    | 23                                              | H2                                                                                                     | A6                 | A6                 | PC6/A6             | PC6            | A6                                                 |  |  |  |

| 21                                                                    | 24                                              | J1                                                                                                     | A7                 | A7                 | PC7/A7             | PC7            | A7                                                 |  |  |  |

| 22                                                                    | 25                                              | H3                                                                                                     | PB0/A8/<br>TIOCA3  | PB0/A8/<br>TIOCA3  | PB0/A8/<br>TIOCA3  | PB0/<br>TIOCA3 | A8                                                 |  |  |  |

| 23                                                                    | 26                                              | J2                                                                                                     | PB1/A9/<br>TIOCB3  | PB1/A9/<br>TIOCB3  | PB1/A9/<br>TIOCB3  | PB1/<br>TIOCB3 | A9                                                 |  |  |  |

| 24                                                                    | 27                                              | K1                                                                                                     | PB2/A10/<br>TIOCC3 | PB2/A10/<br>TIOCC3 | PB2/A10/<br>TIOCC3 | PB2/<br>TIOCC3 | A10                                                |  |  |  |

| 25                                                                    | 28                                              | J3                                                                                                     | PB3/A11/<br>TIOCD3 | PB3/A11/<br>TIOCD3 | PB3/A11/<br>TIOCD3 | PB3/<br>TIOCD3 | A11                                                |  |  |  |

| 26                                                                    | 29                                              | K2                                                                                                     | PB4/A12/<br>TIOCA4 | PB4/A12/<br>TIOCA4 | PB4/A12/<br>TIOCA4 | PB4/<br>TIOCA4 | A12                                                |  |  |  |

#### Table 1.3 Pin Arrangements in Each Mode of H8S/2238 Group

Rev. 6.00 Mar. 18, 2010 Page 29 of 982 REJ09B0054-0600

|                                           |                                      |                                                                      | Pin No.               |                                                                                                    |                  |                                                                                                                       |

|-------------------------------------------|--------------------------------------|----------------------------------------------------------------------|-----------------------|----------------------------------------------------------------------------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------|

| Туре                                      | Symbol                               | TFP-100B<br>TFP-100B<br>TFP-100G<br>TFP-100GV<br>FP-100B<br>FP-100BV | FP-100A <sup>*3</sup> | BP-112 <sup>*1</sup><br>BP-112V <sup>*1</sup><br>TBP-112A <sup>*4</sup><br>TBP-112AV <sup>*4</sup> |                  | Function                                                                                                              |

| DMA<br>controller<br>(DMAC) <sup>*2</sup> | DREQ1<br>DREQ0                       | 89<br>90                                                             | _                     | B6<br>D6                                                                                           | Input            | Request DMAC activation.<br>(Supported only by the H8S/2239 Group.)                                                   |

|                                           | TEND1<br>TEND0                       | 87<br>88                                                             | —                     | C6<br>A6                                                                                           | Output           | Indicate that the DMAC has ended<br>transmitting data.<br>(Supported only by the H8S/2239 Group.)                     |

|                                           | DACK1<br>DACK0                       | 35<br>34                                                             | _                     | J5<br>H5                                                                                           | Output           | These pins function as single address<br>transmitting acknowledge of DMAC.<br>(Supported only by the H8S/2239 Group.) |

| 16-bit timer<br>pulse unit<br>(TPU)       | TCLKD<br>TCLKC<br>TCLKB<br>TCLKA     | 41<br>39<br>37<br>36                                                 | 44<br>42<br>40<br>39  | H6<br>L6<br>K5<br>L5                                                                               | Input            | These pins input an external clock.                                                                                   |

|                                           | TIOCA0<br>TIOCB0<br>TIOCC0<br>TIOCD0 | 34<br>35<br>36<br>37                                                 | 37<br>38<br>39<br>40  | H5<br>J5<br>L5<br>K5                                                                               | Input/<br>Output | Pins for the TGRA_0 to TGRD_0 input capture input, output compare output, or PWM output.                              |

|                                           | TIOCA1<br>TIOCB1                     | 38<br>39                                                             | 41<br>42              | J6<br>L6                                                                                           | Input/<br>Output | Pins for the TGRA_1 and TGRB_1 input capture input, output compare output, or PWM output.                             |

|                                           | TIOCA2<br>TIOCB2                     | 40<br>41                                                             | 43<br>44              | K6<br>H6                                                                                           | Input/<br>Output | Pins for the TGRA_2 and TGRB_2 input capture input, output compare output, or PWM output.                             |

|                                           | TIOCA3<br>TIOCB3<br>TIOCC3<br>TIOCD3 | 22<br>23<br>24<br>25                                                 | 25<br>26<br>27<br>28  | H3<br>J2<br>K1<br>J3                                                                               | Input/<br>Output | Pins for the TGRA_3 to TGRD_3 input capture input, output compare output, or PWM output.                              |

|                                           | TIOCA4<br>TIOCB4                     | 26<br>27                                                             | 29<br>30              | K2<br>L2                                                                                           | Input/<br>Output | Pins for the TGRA_4 and TGRB_4 input capture input, output compare output, or PWM output.                             |

|                                           | TIOCA5<br>TIOCB5                     | 28<br>29                                                             | 31<br>32              | H4<br>K3                                                                                           | Input/<br>Output | Pins for the TGRA_5 and TGRB_5 input<br>capture input, output compare output, or<br>PWM output.                       |

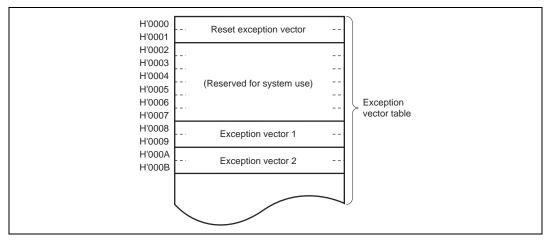

Figure 2.1 Exception Vector Table (Normal Mode)

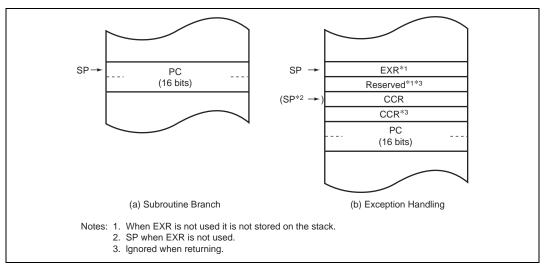

Figure 2.2 Stack Structure in Normal Mode

#### 2.2.2 Advanced Mode

Address Space

Linear access is provided to a maximum 16-Mbyte address space.

• Extended Registers (En)

The extended registers (E0 to E7) can be used as 16-bit registers, or as the upper 16-bit segments of 32-bit registers or address registers.

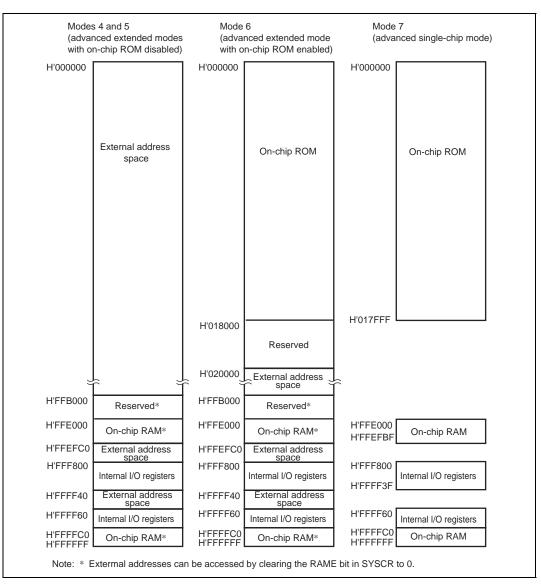

Figure 3.8 H8S/2224 Memory Map in Each Operating Mode

IOAR can be used in short address mode but not in full address mode.

#### 8.3.3 Execute Transfer Count Registers (ETCRA and ETCRB)

ETCR is a 16-bit readable/writable register that specifies the number of transfers.

The DMA has four ETCR registers: ETCR\_0A in channel 0 (channel 0A), ETCR\_0B in channel 0 (channel 0B), ETCR\_1A in channel 1 (channel 1A), and ETCR\_1B in channel 1 (channel 1B).

ETCR is not initialized by a reset or in standby mode.

Short Address Mode: The function of ETCR in sequential mode and idle mode differs from that in repeat mode.

In sequential mode and idle mode, ETCR functions as a 16-bit transfer counter. ETCR is decremented by 1 each time a transfer is performed, and when the count reaches H'00, the DTE bit in DMABCRL is cleared, and transfer ends.

In repeat mode, ETCRL functions as an 8-bit transfer counter and ETCRH functions as a transfer count holding register. ETCRL is decremented by 1 each time a transfer is performed, and when the count reaches H'00, ETCRL is loaded with the value in ETCRH. At this point, MAR is automatically restored to the value it had when the count was started. The DTE bit in DMABCRL is not cleared, and so transfers can be performed repeatedly until the DTE bit is cleared by the user.

**Full Address Mode:** The function of ETCR in normal mode differs from that in block transfer mode.

In normal mode, ETCRA functions as a 16-bit transfer counter. ETCRA is decremented by 1 each time a data transfer is performed, and transfer ends when the count reaches H'0000. ETCRB is not used in normal mode.

In block transfer mode, ETCRAL functions as an 8-bit block size counter and ETCRAH functions as a block size holding register. ETCRAL is decremented by 1 each time a 1-byte or 1-word transfer is performed, and when the count reaches H'00, ETCRAL is loaded with the value in ETCRAH. So by setting the block size in ETCRAH and ETCRAL, it is possible to repeatedly transfer blocks consisting of any desired number of bytes or words.

In block transfer mode, ETCRB functions as a 16-bit block transfer counter. ETCRB is decremented by 1 each time a block is transferred, and transfer ends when the count reaches H'0000.

#### • P15/TIOCB1/TCLKC

The pin functions are switched as shown below according to the combination of the TPU channel 1 setting, TPSC2 to TPS0 bits in TCR\_0, TCR\_2, TCR\_4, and TCR\_5 and the P15DDR bit.

| TPU Channel 1 Setting <sup>*1</sup> | Output                                 | Input or Ini                  | tial Value            |

|-------------------------------------|----------------------------------------|-------------------------------|-----------------------|

| P15DDR                              | —                                      | 0                             | 1                     |

| Pin functions                       | TIOCB1 output pin P15 input pin P15 or |                               | P15 output pin        |

|                                     |                                        | TIOCB1 in                     | put pin <sup>*2</sup> |

|                                     |                                        | TCLKC input pin <sup>*3</sup> |                       |

Notes: 1. For the setting of the TPU channel, see section 11, 16-Bit Timer Pulse Unit (TPU).

- 2. This pin functions as TIOCB1 input when TPU channel 1 timer operating mode is set to normal operating or phase counting mode and IOB3 to IOB0 in TIOR\_1 are set to10xx.

- 3. This pin functions as TCLKC input when TPSC2 to TPSC0 in TCR\_0 or TCR\_2 are set to 110 or TPSC2 to TPSC0 in TCR\_4 or TCR\_0 are 101 or when channels 2 and 4 are set to phase counting mode.

- P14/TIOCA1/IRQ0

The pin functions are switched as shown below according to the combination of the TPU channel 1 setting and the P14DDR bit.

| TPU Channel 1 Setting <sup>*1</sup> | Output            | Input or Ini     | tial Value            |

|-------------------------------------|-------------------|------------------|-----------------------|

| P14DDR                              |                   | 0                | 1                     |

| Pin functions                       | TIOCA1 output pin | P14 input pin    | P14 output pin        |

|                                     |                   | TIOCA1 in        | put pin <sup>*2</sup> |

|                                     |                   | IRQ0 input pin*3 |                       |

Notes: 1. For the setting of the TPU channel, see section 11, 16-Bit Timer Pulse Unit (TPU).

- 2. This pin functions as TIOCA1 input when TPU channel 1 timer operating mode is set to normal operating or phase counting mode and IOA3 to IOA0 in TIOR\_1 are set to 10xx.

- 3. When this pin is used as an external interrupt pin, do not specify other functions.

#### 10.9.6 Input Pull-Up MOS States in Port D

Port D has a built-in input pull-up MOS function that can be controlled by software. Input pull-up MOS can be used in mode 7 and specified as on or off on an individual bit basis.

Table 10.5 summarizes the input pull-up MOS states in port D.

#### Table 10.5 Input Pull-Up MOS States in Port D

| Pin States                                      | Power-on<br>Reset | Hardware<br>Standby<br>Mode | Manual<br>Reset | Software<br>Standby<br>Mode | In Other<br>Operations |

|-------------------------------------------------|-------------------|-----------------------------|-----------------|-----------------------------|------------------------|

| Data I/O (modes 4 to 6) an port output (mode 7) | dOFF              | OFF                         | OFF             | OFF                         | OFF                    |

| Port input (mode 7)                             |                   |                             | ON/OFF          | ON/OFF                      | ON/OFF                 |

Legend:

OFF: Input pull-up MOS is always off.

ON/OFF: On when PDDDR = 0 and PDPCR = 1; otherwise off.

## 10.10 Port E

Port E is an 8-bit I/O port and has the following registers.

- Port E data direction register (PEDDR)

- Port E data register (PEDR)

- Port E register (PORTE)

- Port E pull-up MOS control register (PEPCR)

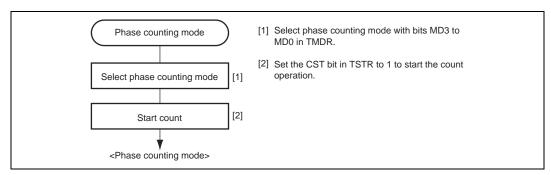

**Example of Phase Counting Mode Setting Procedure:** Figure 11.25 shows an example of the phase counting mode setting procedure.

Figure 11.25 Example of Phase Counting Mode Setting Procedure

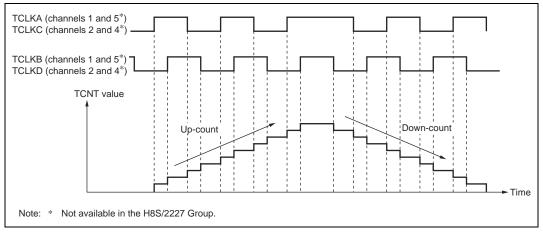

**Examples of Phase Counting Mode Operation:** In phase counting mode, TCNT counts up or down according to the phase difference between two external clocks. There are four modes, according to the count conditions.

1. Phase counting mode 1

Figure 11.26 shows an example of phase counting mode 1 operation, and table 11.32 summarizes the TCNT up/down-count conditions.

Figure 11.26 Example of Phase Counting Mode 1 Operation

# Section 12 8-Bit Timers

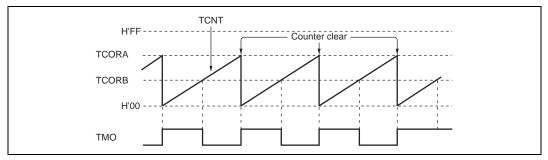

The H8S/2258 Group, H8S/2239 Group, and H8S/2238 Group have an on-chip 8-bit timer module with four channels (TMR\_0, TMR\_1, TMR\_2, and TMR\_3) operating on the basis of an 8-bit counter.

The H8S/2237 Group and H8S/2227 Group have an on-chip 8-bit timer module with two channels (TMR\_0 and TMR\_1) operating on the basis of an 8-bit counter.

The 8-bit timer module can be used to count external events and be used as a multifunction timer in a variety of applications, such as generation of counter reset, interrupt requests, and pulse output with an arbitrary duty cycle using a compare-match signal with two registers.

## 12.1 Features

- Selection of clock sources

Selected from three internal clocks (φ/8, φ/64, and φ/8192) and an external clock.

- Selection of three ways to clear the counters The counters can be cleared on compare-match A or B, or by an external reset signal.

- Timer output controlled by two compare-match signals The timer output signal in each channel is controlled by two independent compare-match signals, enabling the timer to be used for various applications, such as the generation of pulse output or PWM output with an arbitrary duty cycle.

- Cascading of the two channels

- TMR\_0 and TMR\_1 cascading

The module can operate as a 16-bit timer using TMR\_0 as the upper half and channel TMR\_1 as the lower half (16-bit count mode).

TMR\_1 can be used to count TMR\_0 compare-match occurrences (compare-match count mode).

- TMR\_2\* and TMR\_3\* cascading

The module can operate as a 16-bit timer using TMR\_2 as the upper half and channel TMR\_3 as the lower half (16-bit count mode).

TMR\_3 can be used to count TMR\_2 compare-match occurrences (compare-match count mode).

- Multiple interrupt sources for each channel Two compare-match interrupts and one overflow interrupt can be requested independently.

- Generation of A/D conversion start trigger Channel 0 compare-match signal can be used as the A/D conversion start trigger.

Figure 12.2 Example of Pulse Output

## 12.5 Operation Timing

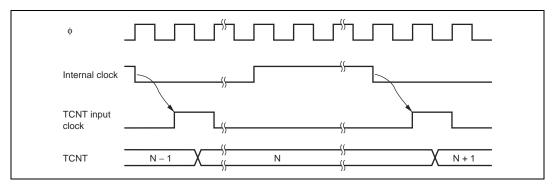

#### 12.5.1 TCNT Incrementation Timing

Figure 12.3 shows the TCNT count timing with internal clock source. Figure 12.4 shows the TCNT incrementation timing with external clock source. The pulse width of the external clock for incrementation at signal edge must be at least 1.5 system clock ( $\phi$ ) periods, and at least 2.5 states for incrementation at both edges. The counter will not increment correctly if the pulse width is less than these values.

Figure 12.3 Count Timing for Internal Clock Input

| Setting<br>Value | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Function                            |

|------------------|-------|-------|-------|-------|-------------------------------------|

| H'0              | 0     | 0     | 0     | 0     | Reads slave status                  |

| H'4              | 0     | 1     | 0     | 0     | Reads locked address (upper 8 bits) |

| H'5              | 0     | 1     | 0     | 1     | Reads locked address (lower 4 bits) |

#### Table 14.5 Control Field for Locked Slave Unit

#### (1) Slave Status Read (Control Bits: H'0, H'6)

The master unit can decide the reason the slave unit does not return the acknowledgement (ACK) by reading the slave status (H'0, H'6). The slave status indicates the result of the last communications that the slave unit performs. All slave units can provide slave status information. Figure 14.3 shows bit configuration of the slave status.

| Μ                                              | SB                                                                                                                                             |                                                                                                                                           |                                                                                                 |                                                                                         |                                                                                     |                                                                                                         |                                                                                                   | LSB                                                                                                  |            |

|------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|------------|

|                                                | Bit 7                                                                                                                                          | Bit 6                                                                                                                                     | Bit 5                                                                                           | Bit 4                                                                                   | Bit 3                                                                               | Bit 2                                                                                                   | Bit 1                                                                                             | Bit 0                                                                                                |            |

|                                                |                                                                                                                                                | Bit                                                                                                                                       | Value                                                                                           | Descriptio                                                                              | n                                                                                   |                                                                                                         |                                                                                                   |                                                                                                      |            |

|                                                |                                                                                                                                                | Bit 7,                                                                                                                                    | 00                                                                                              | Mode 0                                                                                  | Ind                                                                                 | icates the h                                                                                            | ighest mo                                                                                         | de                                                                                                   |            |

|                                                |                                                                                                                                                | bit 6                                                                                                                                     | 01                                                                                              | Mode 1                                                                                  | sup                                                                                 | ported by a                                                                                             | a unit.*1                                                                                         |                                                                                                      |            |

|                                                |                                                                                                                                                |                                                                                                                                           | 10                                                                                              | Mode 2                                                                                  |                                                                                     |                                                                                                         |                                                                                                   |                                                                                                      |            |

|                                                |                                                                                                                                                |                                                                                                                                           | 11                                                                                              | For future                                                                              | Jse                                                                                 |                                                                                                         |                                                                                                   |                                                                                                      |            |

|                                                |                                                                                                                                                | Bit 5                                                                                                                                     | 0                                                                                               | Fixed 0                                                                                 |                                                                                     |                                                                                                         |                                                                                                   |                                                                                                      |            |

|                                                |                                                                                                                                                | Bit 4*2                                                                                                                                   | 0                                                                                               | Slave trans                                                                             | mission                                                                             | halted                                                                                                  |                                                                                                   |                                                                                                      |            |

|                                                |                                                                                                                                                |                                                                                                                                           | 1                                                                                               | Slave trans                                                                             | mission                                                                             | enabled                                                                                                 |                                                                                                   |                                                                                                      |            |

|                                                |                                                                                                                                                | Bit 3                                                                                                                                     | 0                                                                                               | Fixed 0                                                                                 |                                                                                     |                                                                                                         |                                                                                                   |                                                                                                      |            |

|                                                |                                                                                                                                                | Bit 2                                                                                                                                     | 0                                                                                               | Unit is unlo                                                                            | cked                                                                                |                                                                                                         |                                                                                                   |                                                                                                      |            |

|                                                |                                                                                                                                                |                                                                                                                                           | 1                                                                                               | Unit is lock                                                                            | ed                                                                                  |                                                                                                         |                                                                                                   |                                                                                                      |            |

|                                                |                                                                                                                                                | Bit 1*3                                                                                                                                   | 0                                                                                               | Slave rece                                                                              | ive buffe                                                                           | r is empty                                                                                              |                                                                                                   |                                                                                                      |            |

|                                                |                                                                                                                                                |                                                                                                                                           | 1                                                                                               | Slave rece                                                                              | ive buffe                                                                           | r is not emp                                                                                            | oty                                                                                               |                                                                                                      |            |

|                                                |                                                                                                                                                | Bit 0*4                                                                                                                                   | 0                                                                                               | Slave trans                                                                             | smit buff                                                                           | er is empty                                                                                             |                                                                                                   |                                                                                                      |            |

|                                                |                                                                                                                                                |                                                                                                                                           | 1                                                                                               | Slave trans                                                                             | smit buff                                                                           | er is not em                                                                                            | pty                                                                                               |                                                                                                      |            |

| 3. T<br>((<br>Ir<br>a<br>4. T<br>((<br>Ir<br>w | he value of<br>he slave re<br>control bits:<br>h this LSI, ti<br>nd bit 2 is t<br>he slave tra<br>control bits:<br>h this LSI, ti<br>hen SRQ = | f bit 4 can b<br>cceive buffe<br>H'8, H'A, H<br>he slave re<br>he value off<br>ansmit buff<br>H'3, H'7).<br>he slave tra<br>= 1 in the IE | e select<br>r is a bu<br>l'B, H'E,<br>ceive bu<br>the RxF<br>er is a bu<br>unsmit bu<br>Bus ger | ed by the S<br>ffer which is<br>H'F).<br>ffer corresp<br>RDY flag in t<br>uffer which i | TE bit in<br>access<br>onds to the<br>he IEBu<br>s access<br>ponds to<br>gister (IE | the IEBus r<br>ed during d<br>the IEBus re<br>s receive st<br>sed during c<br>the IEBus t<br>:FLG); and | master uni<br>ata write<br>eceive buff<br>atus regist<br>data read<br>transmit bu<br>bit 1 is a v | t address register<br>fer register (IERB<br>ter (IERSR).<br>uffer register (IET<br>alue which revers | R);<br>BR) |

#### Figure 14.3 Bit Configuration of Slave Status (SSR)

Rev. 6.00 Mar. 18, 2010 Page 494 of 982 REJ09B0054-0600

- [1] Clear the TRS bit in ICCR to 0 to switch from transmit mode to receive mode. Clear the ACKB bit in ICSR to 0 (acknowledge data setting). Clear the IRIC flag to 0, then set the WAIT bit in ICMR to 1.

- [2] When ICDR is read (dummy data read), reception is started, and the receive clock is output, and data received, in synchronization with the internal clock.

- [3] The IRIC flag is set to 1 by the following two conditions. At that point, an interrupt request is issued to the CPU if the IEIC bit in ICCR is set to 1.

- (1) The flag is set at the falling edge of the 8th clock cycle of the receive clock for 1 frame. SCL is automatically held low, in synchronization with the internal clock, until the IRIC flag is cleared.

- (2) The flag is set at the rising edge of the 9th clock cycle of the receive clock for 1 frame. The IRTR flag is set to 1, indicating that reception of 1 frame of data has ended. The master device continues to output the receive clock for the receive data.

- [4] Read the IRTR flag in ICSR. If the IRTR flag value is 0, the wait state is cancelled by clearing the IRIC flag as described in step [6] below. If the IRTR flag value is 1 and the next receive data is the final receive data, perform the end processing described in step [7] below.

- [5] If the IRTR flag value is 1, read the ICDR receive data.

- [6] Clear the IRIC flag to 0. The reading of the ICDR flag described in step [5] and the clearing of the IRIC flag to 0 should be performed consecutively, with no interrupt processing occurring between them. During wait operation, clear the IRIC flag to 0 when the value of counter BC2 to BC0 is 2 or greater. If the IRIC flag is cleared to 0 when the value of counter BC2 to BC0 is 1 or 0, it will not be possible to determine when the transfer has completed. If condition [3]-1 is true, the master device drives SDA to low level and returns an acknowledge signal when the receive clock outputs the 9th clock cycle. Further data can be received by repeating steps [3] through [6].

[7] Set the ACKB bit in ICSR to 1 to set the acknowledge data for the final receive.

- [8] Wait for at least 1 clock cycle after the IRIC flag is set to 1 and then wait for the rising edge of the 1st clock cycle of the next receive data.

- [9] Set the TSR bit in ICCR to 1 to switch from the receive mode to the transmit mode. The TSR bit setting value at this point becomes valid when the rising edge of the next 9th clock cycle is input.

- [10] Read the ICDR receive data.

- [11] Clear the IRIC flag to 0. As in step [6], read the ICDR flag and clear the IRIC flag to 0 consecutively, with no interrupt processing occurring between them. During wait operation, clear the IRIC flag to 0 when the value of counter BC2 to BC0 is 2 or greater.

- [12] The IRIC flag is set to 1 by the following two conditions.

#### Section 20 Flash Memory (F-ZTAT Version)

|                                                           | This LSI                                 |                                                             |                 | Socket Adapter            | HN27C4096HG (40-Pin) |                       |  |

|-----------------------------------------------------------|------------------------------------------|-------------------------------------------------------------|-----------------|---------------------------|----------------------|-----------------------|--|

|                                                           | Pin No.                                  |                                                             |                 | (Conversion to<br>40-Pin  |                      |                       |  |

| P-100B <sup>*3</sup> ,TFP-100B,<br>TFP-100G <sup>*4</sup> | FP-100A <sup>*1</sup>                    | BP-112 <sup>*2</sup><br>TBP-112A <sup>*5</sup>              | Pin Name        | Arrangement)              | Pin No.              | Pin Name              |  |

| 13                                                        | 16                                       | F1                                                          | A0              |                           | 21                   | A0                    |  |

| 15                                                        | 18                                       | G1                                                          | A1 -            |                           | 22                   | A1                    |  |

| 16                                                        | 19                                       | G2                                                          | A2 -            |                           | 23                   | A2                    |  |

| 17                                                        | 20                                       | G3                                                          | A3              |                           | 24                   | A3                    |  |

| 18                                                        | 21                                       | H1                                                          | A4              |                           | 25                   | A4                    |  |

| 19                                                        | 22                                       | G4                                                          | A5              |                           | 26                   | A5                    |  |

| 20                                                        | 23                                       | H2                                                          | A6              |                           | 27                   | A6                    |  |

| 21                                                        | 24                                       | J1                                                          | A7 -            |                           | 28                   | A7                    |  |

| 22                                                        | 25                                       | H3                                                          | A8 -            |                           | 29                   | A8                    |  |

| 23                                                        | 26                                       | J2                                                          | A9              |                           | 31                   | A9                    |  |

| 24                                                        | 27                                       | K1                                                          | A10             |                           | 32                   | A10                   |  |

| 25                                                        | 28                                       | J3                                                          | A11             |                           | 33                   | A11                   |  |

| 26                                                        | 29                                       | K2                                                          | A12             |                           | 34                   | A12                   |  |

| 27                                                        | 30                                       | L2                                                          | A13             |                           | 35                   | A13                   |  |

| 28                                                        | 31                                       | H4                                                          | A14             |                           | 36                   | A14                   |  |

| 29                                                        | 32                                       | K3                                                          | A15             |                           | 37                   | A15                   |  |

| 30                                                        | 33                                       | L3                                                          | A16             |                           | 38                   | A16                   |  |

| 31                                                        | 34                                       | J4                                                          | A17             |                           | 39                   | A17                   |  |

| 32                                                        | 35                                       | K4                                                          | A18             |                           | 10                   | A18                   |  |

| 4                                                         | 7                                        | C2                                                          | D0              |                           | 19                   | I/O0                  |  |

| 5                                                         | 8                                        | C1                                                          | D1              |                           | 18                   | I/01                  |  |

| 6                                                         | 9                                        | D3                                                          | D2              |                           | 17                   | I/O2                  |  |

| 7                                                         | 10                                       | D2                                                          | D3              |                           | 16                   | I/O3                  |  |

| 8                                                         | 11                                       | D1                                                          | D4              |                           | 15                   | I/O4                  |  |

| 9                                                         | 12                                       | E4                                                          | D5              |                           | 14                   | I/O5                  |  |

| 10                                                        | 13                                       | E3                                                          | D6              |                           | 13                   | I/O6                  |  |

| 11                                                        | 14                                       | E1                                                          | D7              |                           | 12                   | I/07                  |  |

| 3                                                         | 6                                        | D4                                                          | CE              |                           | 2                    | CE                    |  |

| 1                                                         | 4                                        | B2                                                          | ŌĒ              |                           | 20                   | ŌĒ                    |  |

| 2                                                         | 5                                        | B1                                                          | WE              |                           | 3                    | WE                    |  |

| 66                                                        | 69                                       | E10                                                         | FWE             |                           | 4                    | FWE                   |  |

|                                                           |                                          |                                                             |                 |                           | 40, 1                | V <sub>cc</sub>       |  |

| 99, 75, 72 <sup>*1</sup> , 62, 61,                        | 78, 75, 65, 64,                          | E2, F3, H8, J10,                                            | V <sub>CC</sub> |                           | 30, 11               | V <sub>ss</sub>       |  |

| 60, 54, 53, 12                                            | 57, 54, 15, 2                            | G9, G11, F9, G10,<br>C9, B3                                 | *cc             |                           | 7, 6, 5              | NC                    |  |

| 100, 67, 64, 58, 56,<br>55, 42, 40, 38, 14                | 70, 67, 61, 59, 58, 45,<br>43, 41, 17, 3 | F2, F4, J6, K6, K7,<br>L7, J11, H9, H11,<br>F8, F10, E9, A2 | V <sub>SS</sub> |                           | 8<br>9               | A20<br>A19            |  |

| 59                                                        | 62                                       | G8                                                          | RES             | Power-on<br>reset circuit | Legend:<br>FWE: Fla: | sh write enable       |  |

| 63                                                        | 66                                       | F11                                                         | XTAL            | Oscillator                |                      | a input/output        |  |

| 65                                                        | 68                                       | E11                                                         | EXTAL           | circuit                   | OE: Out              | put enable            |  |

| Other than the above                                      | Other than the above                     |                                                             | NC (OPEN)       | 1                         |                      | p enable<br>te enable |  |

Notes: 1. Supported only by the H8S/2258 and H8S/2238B.

2. Supported only by the H8S/2238R.

3. Not supported by the H8S/2227.

4. Not supported by the H8S/2258.

5. Supported only by the H8S/2238R and H8S/2239.

#### Figure 20.13 Socket Adapter Pin Correspondence Diagram

Rev. 6.00 Mar. 18, 2010 Page 744 of 982 REJ09B0054-0600

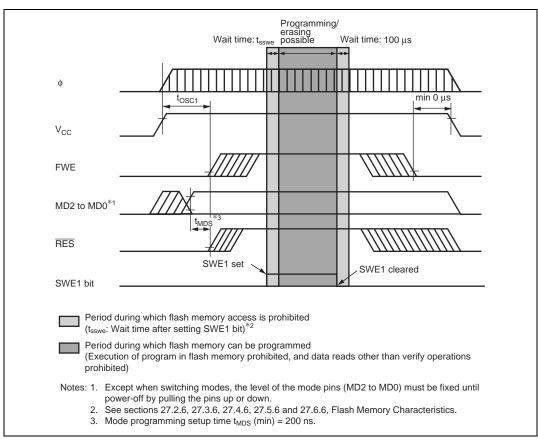

Figure 20.15 Power-On/Off Timing (User Program Mode)

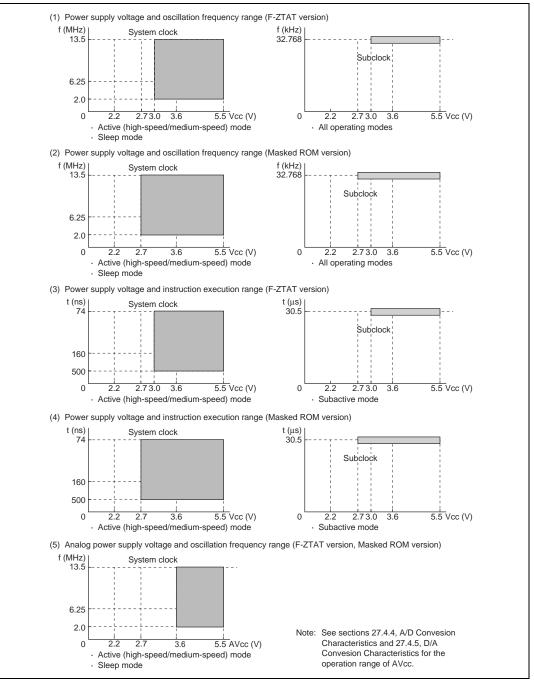

Figure 27.3 Power Supply Voltage and Operating Ranges (H8S/2238B and H8S/2236B)

#### Section 27 Electrical Characteristics

|                                                |                            | Condition A |        | Condition B |        | Condition C |        |      | Test         |

|------------------------------------------------|----------------------------|-------------|--------|-------------|--------|-------------|--------|------|--------------|

| Item                                           | Symbol                     | Min         | Max    | Min         | Max    | Min         | Max    | Unit | Conditions   |

| External clock output stabilization delay time | $\mathbf{t}_{\text{dext}}$ | 500         |        | 500         |        | 1000        |        | μs   | Figure 27.11 |

| Subclock oscillation stabilization time        | t <sub>osc3</sub>          |             | 2      |             | 2      |             | 3      | S    |              |

| Subclock oscillator<br>frequency               | f <sub>sub</sub>           | 32.768      | 32.768 | 32.768      | 32.768 | 32.768      | 32.768 | kHz  |              |

| Subclock ( $\phi_{_{SUB}}$ ) cycle time        | t <sub>sub</sub>           | 30.5        | 30.5   | 30.5        | 30.5   | 30.5        | 30.5   | μs   | _            |