Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Not For New Designs                                                           |

|----------------------------|-------------------------------------------------------------------------------|

| Core Processor             | H8S/2000                                                                      |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 20MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, SCI, SmartCard                                              |

| Peripherals                | DMA, POR, PWM, WDT                                                            |

| Number of I/O              | 72                                                                            |

| Program Memory Size        | 384KB (384K x 8)                                                              |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 32K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                                   |

| Data Converters            | A/D 8x10b; D/A 2x8b                                                           |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 100-BFQFP                                                                     |

| Supplier Device Package    | 100-QFP (14x14)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/df2239fa20iv |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 6.4.3   | CMFA and CMFB                                                                                                                                                                                                                                                                                                                            | .163                                                                        |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|

| 6.4.4   | PC Break Interrupt when DTC and DMAC Is Bus Master                                                                                                                                                                                                                                                                                       | 163                                                                         |

| 6.4.5   | PC Break Set for Instruction Fetch at Address Following BSR, JSR, JMP,                                                                                                                                                                                                                                                                   |                                                                             |

|         | TRAPA, RTE, and RTS Instruction                                                                                                                                                                                                                                                                                                          | 163                                                                         |

| 6.4.6   | I Bit Set by LDC, ANDC, ORC, and XORC Instruction                                                                                                                                                                                                                                                                                        | 164                                                                         |

| 6.4.7   | PC Break Set for Instruction Fetch at Address Following Bcc Instruction                                                                                                                                                                                                                                                                  | 164                                                                         |

| 6.4.8   | PC Break Set for Instruction Fetch at Branch Destination Address of Bcc                                                                                                                                                                                                                                                                  |                                                                             |

|         | Instruction                                                                                                                                                                                                                                                                                                                              | 164                                                                         |

| on 7 l  | Bus Controller                                                                                                                                                                                                                                                                                                                           | 165                                                                         |

| Feature | S                                                                                                                                                                                                                                                                                                                                        | 165                                                                         |

| Input/C | Putput Pins                                                                                                                                                                                                                                                                                                                              | 167                                                                         |

| -       | 1                                                                                                                                                                                                                                                                                                                                        |                                                                             |

| 7.3.1   | *                                                                                                                                                                                                                                                                                                                                        |                                                                             |

| 7.3.2   |                                                                                                                                                                                                                                                                                                                                          |                                                                             |

| 7.3.3   |                                                                                                                                                                                                                                                                                                                                          |                                                                             |

| 7.3.4   | -                                                                                                                                                                                                                                                                                                                                        |                                                                             |

| 7.3.5   |                                                                                                                                                                                                                                                                                                                                          |                                                                             |

| 7.3.6   |                                                                                                                                                                                                                                                                                                                                          |                                                                             |

| Bus Co  |                                                                                                                                                                                                                                                                                                                                          |                                                                             |

| 7.4.1   | Area Divisions                                                                                                                                                                                                                                                                                                                           | .175                                                                        |

| 7.4.2   | Bus Specifications                                                                                                                                                                                                                                                                                                                       | 176                                                                         |

| 7.4.3   | Bus Interface for Each Area                                                                                                                                                                                                                                                                                                              |                                                                             |

| 7.4.4   | Chip Select Signals                                                                                                                                                                                                                                                                                                                      | 178                                                                         |

| Basic T |                                                                                                                                                                                                                                                                                                                                          |                                                                             |

| 7.5.1   | -                                                                                                                                                                                                                                                                                                                                        |                                                                             |

| 7.5.2   |                                                                                                                                                                                                                                                                                                                                          |                                                                             |

| 7.5.3   |                                                                                                                                                                                                                                                                                                                                          |                                                                             |

| Basic B |                                                                                                                                                                                                                                                                                                                                          |                                                                             |

| 7.6.1   | Data Size and Data Alignment                                                                                                                                                                                                                                                                                                             | .181                                                                        |

| 7.6.2   | Valid Strobes                                                                                                                                                                                                                                                                                                                            | .182                                                                        |

| 7.6.3   | Basic Timing                                                                                                                                                                                                                                                                                                                             | .183                                                                        |

| 7.6.4   | Wait Control                                                                                                                                                                                                                                                                                                                             | 190                                                                         |

| Burst R | OM Interface                                                                                                                                                                                                                                                                                                                             | . 192                                                                       |

| 7.7.1   | Basic Timing                                                                                                                                                                                                                                                                                                                             | .192                                                                        |

| 7.7.2   | Wait Control                                                                                                                                                                                                                                                                                                                             |                                                                             |

| Idle Cy | cle                                                                                                                                                                                                                                                                                                                                      | .194                                                                        |

| Bus Re  | lease                                                                                                                                                                                                                                                                                                                                    | . 197                                                                       |

| 7.9.1   | Bus Release Usage Note                                                                                                                                                                                                                                                                                                                   | 198                                                                         |

| Bus Ar  | -                                                                                                                                                                                                                                                                                                                                        |                                                                             |

|         | 6.4.4<br>6.4.5<br>6.4.6<br>6.4.7<br>6.4.8<br>0n 7 J<br>Feature<br>Input/C<br>Registe<br>7.3.1<br>7.3.2<br>7.3.3<br>7.3.4<br>7.3.5<br>7.3.6<br>Bus Co<br>7.4.1<br>7.4.2<br>7.4.3<br>7.4.4<br>Basic T<br>7.5.1<br>7.5.2<br>7.5.3<br>Basic E<br>7.6.1<br>7.6.2<br>7.6.3<br>7.6.4<br>Burst R<br>7.7.1<br>7.7.2<br>Idle Cy<br>Bus Re<br>7.9.1 | <ul> <li>6.4.4 PC Break Interrupt when DTC and DMAC Is Bus Master</li></ul> |

| Figure 27.5  | Power Supply Voltage and Operating Ranges                     |     |

|--------------|---------------------------------------------------------------|-----|

|              | (H8S/2237 Group and H8S/2227 Group)                           |     |

| Figure 27.6  | Output Load Circuit                                           |     |

| Figure 27.7  | I <sup>2</sup> C Bus Interface Input/Output Timing (Optional) | 859 |

| Figure 27.8  | Output Load Circuit                                           |     |

| Figure 27.9  | Output Load Circuit                                           |     |

| Figure 27.10 | System Clock Timing                                           | 948 |

| Figure 27.11 | Oscillation Stabilization Timing                              | 948 |

| Figure 27.12 | Reset Input Timing                                            | 949 |

| Figure 27.13 | Interrupt Input Timing                                        | 949 |

| Figure 27.14 | Basic Bus Timing (Two-State Access)                           | 950 |

| Figure 27.15 | Basic Bus Timing (Three-State Access)                         | 951 |

| Figure 27.16 | Basic Bus Timing (Three-State Access with One Wait State)     | 952 |

| Figure 27.17 | Burst ROM Access Timing (Two-State Access)                    | 953 |

| Figure 27.18 | Burst ROM Access Timing (One-State Access)                    | 954 |

| Figure 27.19 | External Bus Release Timing                                   | 954 |

| Figure 27.20 | DMAC Single Address Transfer Timing (Two-State Access)        | 955 |

| Figure 27.21 | DMAC Single Address Transfer Timing (Three-State Access)      |     |

| Figure 27.22 | DMAC TEND Output Timing                                       | 957 |

| Figure 27.23 | DMAC DREQ Input Timing                                        | 957 |

| Figure 27.24 | I/O Port Input/Output Timing                                  | 957 |

| Figure 27.25 | TPU Input/Output Timing                                       | 958 |

| Figure 27.26 | TPU Clock Input Timing                                        | 958 |

| Figure 27.27 | 8-Bit Timer Output Timing                                     | 958 |

| Figure 27.28 | 8-Bit Timer Clock Input Timing                                | 959 |

| Figure 27.29 | 8-Bit Timer Reset Input Timing                                | 959 |

| Figure 27.30 | WDT_1 Output Timing                                           | 959 |

| Figure 27.31 | SCK Clock Input Timing                                        | 959 |

| Figure 27.32 | SCI Input/Output Timing (Clocked Synchronous Mode)            | 960 |

| Figure 27.33 | A/D Converter External Trigger Input Timing                   | 960 |

| Figure 27.34 | I <sup>2</sup> C Bus Interface Input/Output Timing (Optional) | 960 |

|              |                                                               |     |

| Appendix C   | Package Dimensions                                            |     |

| TFP-100B Package Dimensions            |                                                                                         |

|----------------------------------------|-----------------------------------------------------------------------------------------|

| TFP-100G Package Dimensions            |                                                                                         |

| FP-100A Package Dimensions             |                                                                                         |

| FP-100B Package Dimensions             |                                                                                         |

| BP-112 Package Dimensions              |                                                                                         |

| TBP-112A, TBP-112AV Package Dimensions |                                                                                         |

|                                        | TFP-100G Package Dimensions<br>FP-100A Package Dimensions<br>FP-100B Package Dimensions |

• Compact package

| Package                 | (Code) <sup>*6</sup>   | Body Size                     | Pin Pitch |

|-------------------------|------------------------|-------------------------------|-----------|

| TQFP-100                | TFP-100B,<br>TFP-100BV | $14.0 \times 14.0 \text{ mm}$ | 0.5 mm    |

| TQFP-100*1              | TFP-100G,<br>TFP-100GV | 12.0 × 12.0 mm                | 0.4 mm    |

| QFP-100 <sup>*2</sup>   | FP-100A, FP-100AV      | $14.0 \times 20.0 \text{ mm}$ | 0.65 mm   |

| QFP-100 <sup>*3</sup>   | FP-100B, FP-100BV      | $14.0 \times 14.0 \text{ mm}$ | 0.5 mm    |

| LFBGA-112 <sup>*4</sup> | BP-112, BP-112V        | $10.0 \times 10.0 \text{ mm}$ | 0.8 mm    |

| TFBGA-112 <sup>*5</sup> | TBP-112A,<br>TBP-112AV | 10.0 × 10.0 mm                | 0.8 mm    |

Notes: 1. Not supported by the H8S/2258 Group.

2. Supported only by the H8S/2258 Group, H8S/2238B, H8S/2236B, H8S/2237 Group, and HD6432227.

- 3. Not supported by the HD64F2227.

- 4. Supported only by the HD64F2238R.

- 5. Supported only by theHD64F2238R and HD64F2239.

- 6. Package code ending in the letter V designate Pb-free Product.

| • DM | • DMACR_0B and DMACR_1B |               |                                                                                                                                                              |                                                                                          |  |  |  |

|------|-------------------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|--|--|--|

| Bit  | Bit Name                | Initial Value | R/W                                                                                                                                                          | Description                                                                              |  |  |  |

| 7    |                         | 0             | R/W                                                                                                                                                          | Reserved                                                                                 |  |  |  |

|      |                         |               |                                                                                                                                                              | This bit can be read from or written to.<br>However, the write value should always be 0. |  |  |  |

| 6    | DAID                    | 0             | R/W                                                                                                                                                          | Destination Address Increment/Decrement                                                  |  |  |  |

| 5    | DAIDE                   | 0             | R/W                                                                                                                                                          | Destination Address Increment/Decrement<br>Enable                                        |  |  |  |

|      |                         |               | These bits specify whether destination address<br>register MARB is to be incremented,<br>decremented, or left unchanged, when data<br>transfer is performed. |                                                                                          |  |  |  |

|      |                         |               |                                                                                                                                                              | 00: MARB is fixed                                                                        |  |  |  |

|      |                         |               |                                                                                                                                                              | 01: MARB is incremented after a data transfer                                            |  |  |  |

|      |                         |               |                                                                                                                                                              | <ul> <li>When DTSZ = 0, MARB is incremented by<br/>1</li> </ul>                          |  |  |  |

|      |                         |               |                                                                                                                                                              | <ul> <li>When DTSZ = 1, MARB is incremented by 2</li> </ul>                              |  |  |  |

|      |                         |               |                                                                                                                                                              | 10: MARB is fixed                                                                        |  |  |  |

|      |                         |               |                                                                                                                                                              | 11: MARB is decremented after a data transfer                                            |  |  |  |

|      |                         |               |                                                                                                                                                              | <ul> <li>When DTSZ = 0, MARB is decremented by<br/>1</li> </ul>                          |  |  |  |

|      |                         |               |                                                                                                                                                              | • When DTSZ = 1, MARB is decremented by 2                                                |  |  |  |

| 4    | —                       | 0             | R/W                                                                                                                                                          | Reserved                                                                                 |  |  |  |

|      |                         |               |                                                                                                                                                              | This bit can be read from or written to.<br>However, the write value should always be 0. |  |  |  |

| Transfer M              | ode                                                                                                                                                                                                                                                                  | Transfer Source                                                                                                                                                                                                                                                            | Remarks                                                                              |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|

| Full<br>address<br>mode | <ul> <li>Normal mode</li> <li>(1) Auto-request</li> <li>Transfer request is internally held</li> <li>Number of transfers (1 to 65,536)<br/>is continuously sent</li> <li>Burst/cycle steal transfer can be<br/>selected</li> </ul>                                   | Auto-request                                                                                                                                                                                                                                                               | <ul> <li>Max. 2-channel<br/>operation,<br/>combining<br/>channels A and B</li> </ul> |

|                         | <ul> <li>(2) External request</li> <li>1-byte or 1-word transfer for a single transfer request</li> <li>Number of transfers: 1 to 65,536</li> </ul>                                                                                                                  | External request                                                                                                                                                                                                                                                           |                                                                                      |

|                         | <ul> <li>Block transfer mode</li> <li>Transfer of 1-block, size selected for a single transfer request</li> <li>Number of transfers: 1 to 65,536</li> <li>Source or destination can be selected as block area</li> <li>Block size: 1 to 256 bytes or word</li> </ul> | <ul> <li>TPU channel 0 to<br/>5 compare<br/>match/input<br/>capture A interrupt</li> <li>SCI transmit-data-<br/>empty interrupt</li> <li>SCI receive-data-<br/>full interrupt</li> <li>A/D converter<br/>conversion end<br/>interrupt</li> <li>External request</li> </ul> | -                                                                                    |

#### 11.3.5 Timer Status Register (TSR)

The TSR registers indicate the status of each channel. The TPU of the H8S/2227 Group has a total of three TSR registers, one each for channels 0 to 2. In other groups, the TPU has a total of six TSR registers, one each for channels 0 to 5.

| Bit | Bit Name | Initial value | R/W     | Description                                                                                                                                                                                                                               |

|-----|----------|---------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | TCFD     | 1             | R       | Count Direction Flag                                                                                                                                                                                                                      |

|     |          |               |         | Status flag that shows the direction in which TCNT counts in channels 1, 2, $4^{*3}$ , and $5^{*3}$ .<br>In channels 0 and $3^{*3}$ , bit 7 is reserved. It is always read as 1 and cannot be modified.                                   |

|     |          |               |         | 0: TCNT counts down                                                                                                                                                                                                                       |

|     |          |               |         | 1: TCNT counts up                                                                                                                                                                                                                         |

| 6   | _        | 1             | _       | Reserved                                                                                                                                                                                                                                  |

|     |          |               |         | This bit is always read as 1 and cannot be modified.                                                                                                                                                                                      |

| 5   | TCFU     | 0             | R/(W)*1 | Underflow Flag                                                                                                                                                                                                                            |

|     |          |               |         | Status flag that indicates that TCNT underflow has occurred when channels 1, 2, $4^{*3}$ , and $5^{*3}$ are set to phase counting mode.<br>In channels 0 and $3^{*3}$ , bit 5 is reserved. It is always read as 0 and cannot be modified. |

|     |          |               |         | [Setting condition]                                                                                                                                                                                                                       |

|     |          |               |         | When the TCNT value underflows (changes from H'0000 to H'FFFF)                                                                                                                                                                            |

|     |          |               |         | [Clearing condition]                                                                                                                                                                                                                      |

|     |          |               |         | When 0 is written to TCFU after reading TCFU = 1                                                                                                                                                                                          |

| 4   | TCFV     | 0             | R/(W)*1 | Overflow Flag                                                                                                                                                                                                                             |

|     |          |               |         | Status flag that indicates that TCNT overflow has occurred.                                                                                                                                                                               |

|     |          |               |         | [Setting condition]                                                                                                                                                                                                                       |

|     |          |               |         | When the TCNT value overflows (changes from<br>H'FFFF to H'0000)                                                                                                                                                                          |

|     |          |               |         | [Clearing condition]                                                                                                                                                                                                                      |

|     |          |               |         | When 0 is written to TCFV after reading TCFV = 1                                                                                                                                                                                          |

|     |          |               |         |                                                                                                                                                                                                                                           |

#### 12.3.3 Time Constant Register B (TCORB)

TCORB is an 8-bit readable/writable register. TCORB\_0 and TCORB\_1 (TCORB\_2 and TCORB\_3)\* comprise a single 16-bit register, so they can be accessed together by word access.

TCORB is continually compared with the value in TCNT. When a match is detected, the corresponding compare-match flag B (CMFB) in TCSR is set. Note, however, that comparison is disabled during the T2 state of a TCORB write cycle.

The timer output from the TMO pin can be freely controlled by the compare-match signal B and the settings of output select bits OS1 and OS0 in TCSR.

The initial value of TCORB is H'FF.

Note: \* Not available in the H8S/2237 Group and H8S/2227 Group.

#### 12.3.4 Timer Control Register (TCR)

TCR selects the TCNT clock source and the time at which TCNT is cleared, and controls interrupt requests.

| Bit | Bit Name | Initial<br>Value | R/W | Description                                                                                                            |

|-----|----------|------------------|-----|------------------------------------------------------------------------------------------------------------------------|

| 7   | CMIEB    | 0                | R/W | Compare-Match Interrupt Enable B                                                                                       |

|     |          |                  |     | Selects whether the CMFB interrupt request (CMIB) is<br>enabled or disabled when the CMFB flag in TCSR is<br>set to 1. |

|     |          |                  |     | 0: CMFB interrupt request (CMIB) is disabled                                                                           |

|     |          |                  |     | 1: CMFB interrupt request (CMIB) is enabled                                                                            |

| 6   | CMIEA    | 0                | R/W | Compare-Match Interrupt Enable A                                                                                       |

|     |          |                  |     | Selects whether the CMFA interrupt request (CMIA) is<br>enabled or disabled when the CMFA flag in TCSR is<br>set to 1. |

|     |          |                  |     | 0: CMFA interrupt request (CMIA) is disabled                                                                           |

|     |          |                  |     | 1: CMFA interrupt request (CMIA) is enabled                                                                            |

| 5   | OVIE     | 0                | R/W | Timer Overflow Interrupt Enable                                                                                        |

|     |          |                  |     | Selects whether the OVF interrupt request (OVI) is<br>enabled or disabled when the OVF flag in TCSR is set<br>to 1.    |

|     |          |                  |     | 0: OVF interrupt request (OVI) is disabled                                                                             |

|     |          |                  |     | 1: OVF interrupt request (OVI) is enabled                                                                              |

#### 14.1.3 Transfer Data (Data Field Contents)

The data filed contents are specified by the control bits.

#### Table 14.4 Control Bit Contents

. . . .

| H'0 | 0 | - |   | Bit 0 | Function <sup>*2</sup>               |

|-----|---|---|---|-------|--------------------------------------|

|     |   | 0 | 0 | 0     | Reads slave status (SSR)             |

| H'1 | 0 | 0 | 0 | 1     | Undefined — do not use               |

| H'2 | 0 | 0 | 1 | 0     | Undefined — do not use               |

| H'3 | 0 | 0 | 1 | 1     | Reads data and locks                 |

| H'4 | 0 | 1 | 0 | 0     | Reads locked address (lower 8 bits)  |

| H'5 | 0 | 1 | 0 | 1     | Reads locked address (upper 4 bits)  |

| H'6 | 0 | 1 | 1 | 0     | Reads slave status (SSR) and unlocks |

| H'7 | 0 | 1 | 1 | 1     | Reads data                           |

| H'8 | 1 | 0 | 0 | 0     | Undefined — do not use               |

| H'9 | 1 | 0 | 0 | 1     | Undefined — do not use               |

| H'A | 1 | 0 | 1 | 0     | Writes command and locks             |

| H'B | 1 | 0 | 1 | 1     | Writes data and locks                |

| H'C | 1 | 1 | 0 | 0     | Undefined — do not use               |

| H'D | 1 | 1 | 0 | 1     | Undefined — do not use               |

| H'E | 1 | 1 | 1 | 0     | Writes command                       |

| H'F | 1 | 1 | 1 | 1     | Writes data                          |

Notes: 1. According to the value of bit 3 (MSB), the transfer directions of the message length bits in the following message length field and data in the data field vary.

When bit 3 is 1: Data is transferred from the master unit to the slave unit.

When bit 3 is 0: Data is transferred from the slave unit to the master unit.

2. H'3, H'6, H'A, and H'B are control bits to specify lock setting and cancellation. When the undefined values of H'1, H'2, H'8, H'9, H'C, and H'D are transmitted, the acknowledge bit is not returned.

When the control bits received from another unit which locked are not included in table 14.5, the slave unit which has been locked by the master unit rejects acceptance of the control bits and does not return the acknowledge bit.

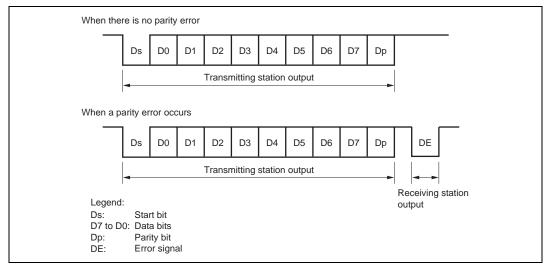

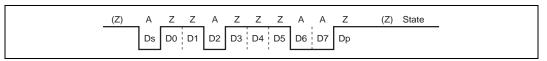

Figure 15.25 Normal Smart Card Interface Data Format

Data transfer with other types of IC cards (direct convention and inverse convention) are performed as described in the following.

Figure 15.26 Direct Convention (SDIR = SINV =  $O/\overline{E} = 0$ )

With the direction convention type IC and the above sample start character, the logic 1 level corresponds to state Z and the logic 0 level to state A, and transfer is performed in LSB-first order. The start character data above is H'3B. For the direct convention type, clear the SDIR and SINV bits in SCMR to 0. According to Smart Card regulations, clear the  $O/\overline{E}$  bit in SMR to 0 to select even parity mode.

(Z)

A

Z

Z

A

A

A

A

Z

(Z)

State

Ds

D7

D6

D5

D4

D3

D2

D1

D0

Dp

#### Figure 15.27 Inverse Convention (SDIR = SINV = $O/\overline{E} = 1$ )

With the inverse convention type, the logic 1 level corresponds to state A and the logic 0 level to state Z, and transfer is performed in MSB-first order. The start character data for the above is H'3F. For the inverse convention type, set the SDIR and SINV bits in SCMR to 1. According to Smart Card regulations, even parity mode is the logic 0 level of the parity bit, and corresponds to

ICE is 1. For details on the module stop control register, refer to section 24.1.2, Module Stop Control Registers A to C (MSTPCRA to MSTPCRC).

- I<sup>2</sup>C bus data register\_0 (ICDR\_0)\*

- Slave address register\_0 (SAR\_0)\*

- Second slave address register\_0 (SARX\_0)\*

- I<sup>2</sup>C bus mode register\_0 (ICMR\_0)\*

- I<sup>2</sup>C bus control register\_0 (ICCR\_0)\*

- I<sup>2</sup>C bus status register\_0 (ICSR\_0)\*

- I<sup>2</sup>C bus data register\_1 (ICDR\_1)\*

- Slave address register\_1 (SAR\_1)\*

- Second slave address register\_1 (SARX\_1)\*

- I<sup>2</sup>C bus mode register\_1 (ICMR\_1)\*

- I<sup>2</sup>C bus control register\_1 (ICCR\_1)\*

- I<sup>2</sup>C bus status register\_1 (ICSR\_1)\*

- DDC switch register (DDCSWR)

- Serial control register X (SCRX)

- Note: \* Some of the registers in the I<sup>2</sup>C bus interface are allocated to the same addresses of other registers. The IICE bit in serial control register X (SCRX) selects each register.

### 16.3.1 I<sup>2</sup>C Bus Data Register (ICDR)

ICDR is an 8-bit readable/writable register that is used as a transmit data register when transmitting and a receive data register when receiving. ICDR is divided internally into a shift register (ICDRS), receive buffer (ICDRR), and transmit buffer (ICDRT). Data transfers among the three registers are performed automatically in coordination with changes in the bus state, and affect the status of internal flags such as TDRE and RDRF. When TDRE is 1 and the transmit buffer is empty, TDRE shows that the next transmit data can be written from the CPU. When RDRF is 1, it shows that the valid receive data is stored in the receive buffer.

If I<sup>2</sup>C is in transmit mode and the next data is in ICDRT (the TDRE flag is 0) following transmission/reception of one frame of data using ICDRS, data is transferred automatically from ICDRT to ICDRS. If I<sup>2</sup>C is in receive mode and no previous data remains in ICDRR (the RDRF flag is 0) following transmission/reception of one frame of data using ICDRS, data is transferred automatically from ICDRS to ICDRR.

If the number of bits in a frame, excluding the acknowledge bit, is less than 8, transmit data and receive data are stored differently. Transmit data should be written justified toward the MSB side

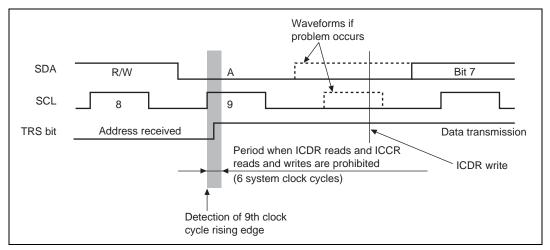

11. Notes on ICDR Reads and ICCR Access in Slave Transmit Mode

In a transmit operation in the slave mode of the  $I^2C$  bus interface, do not read the ICDR register or read or write to the ICCR register during the period indicated by the shaded portion in figure 16.25.

Normally, when interrupt processing is triggered in synchronization with the rising edge of the 9th clock cycle, the period in question has already elapsed when the transition to interrupt processing takes place, so there is no problem with reading the ICDR register or reading or writing to the ICCR register.

To ensure that the interrupt processing is performed properly, one of the following two conditions should be applied.

- (1) Make sure that reading received data from the ICDR register, or reading or writing to the ICCR register, is completed before the next slave address receive operation starts.

- (2) Monitor the BC2 to BC0 counter in the ICMR register and, when the value of BC2 to BC0 is 000 (8th or 9th clock cycle), allow a waiting time of at least 2 transfer clock cycles in order to involve the problem period in question before reading from the ICDR register, or reading or writing to the ICCR register.

Figure 16.25 ICDR Read and ICCR Access Timing in Slave Transmit Mode

**Do Not Set or Clear the SWE1 Bit during Execution of a Program in Flash Memory:** Wait for at least 100 µs after clearing the SWE1 bit before executing a program or reading data in flash memory.

When the SWE1 bit is set, data in flash memory can be rewritten. Access flash memory only for verify operations (verification during programming/erasing). Also, do not clear the SWE1 bit during programming, erasing, or verifying. Similarly, when using the RAM emulation function while a high level is being input to the FWE pin, the SWE1 bit must be cleared before executing a program or reading data in flash memory.

However, the RAM area overlapping flash memory space can be read and written to regardless of whether the SWE1 bit is set or cleared.

**Do Not Use Interrupts while Flash Memory Is Being Programmed or Erased:** All interrupt requests, including NMI, should be disabled during FWE application to give priority to program/erase operations.

**Do Not Perform Additional Programming. Erase the Memory before Reprogramming:** In on-board programming, perform only one programming operation on a 128-byte programming unit block. In programmer mode, too, perform only one programming operation on a 128-byte programming unit block. Programming should be carried out with the entire programming unit block erased.

**Before Programming, Check That the Chip Is Correctly Mounted in the PROM Programmer:** Overcurrent damage to the device can result if the index marks on the PROM programmer socket, socket adapter, and chip are not correctly aligned.

**Do Not Touch the Socket Adapter or Chip during Programming:** Touching either of these can cause contact faults and write errors.

**Reset the Flash Memory before Turning on the Power:** To reset the flash memory during oscillation stabilization period, the reset signal must be input for at least 100 µs.

Apply the Reset Signal while SWE Is Low to Reset the Flash Memory during its operation: The reset signal is applied at least 100 µs after the SWE bit has been cleared.

# Section 22 PROM

The PROM version can be set to PROM mode and programmed with a PROM programmer.

### 22.1 PROM Mode Setting

The PROM version (HD6472237) suspends its microcomputer functions when placed in PROM mode, enabling the on-chip PROM to be programmed. This programming can be done with a PROM programmer set up in the same way as for the HN27C101 ( $V_{PP} = 12.5$  V) EPROM. Use of a socket adapter to convert from 100 pins to 32 pins enables programming with a commercial PROM programmer.

Caution is required when selecting the PROM programmer, as this LSI does not support page mode.

Table 22.1 shows how PROM mode is selected.

| <b>Table 22.1</b> | Selecting PROM Mode |

|-------------------|---------------------|

|-------------------|---------------------|

| Pin Names     | Setting |  |

|---------------|---------|--|

| MD2, MD1, MD0 | Low     |  |

| STBY          |         |  |

| PA2, PA1      | High    |  |

### 22.2 Socket Adapter and Memory Map

Programs can be written and verified by attaching a socket adapter to convert from 100 pins to 32 pins to the PROM programmer. Figure 22.1 shows the wiring of the socket adapter, and table 22.2 gives ordering information for the socket adapter. Figure 22.2 shows the memory map in PROM mode.

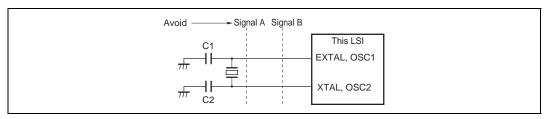

#### 23.9.2 Note on Board Design

When designing the board, place the crystal resonator and its load capacitors as close as possible to the EXTAL, XTAL, OSC1, and OSC2 pins. Make wires as short as possible. Other signal lines should be routed away from the oscillator circuit, as shown in figure 23.11. This is to prevent induction from interfering with correct oscillation.

Figure 23.11 Note on Board Design of Oscillator Circuit

### 24.9 Subactive Mode

#### 24.9.1 Transition to Subactive Mode

When the SLEEP instruction is executed in high-speed mode with the SSBY bit in SBYCR = 1, the DTON bit in LPWRCR = 1, the LSON bit = 1, and the PSS bit in TCSR\_1 (WDT\_1) = 1, CPU operation shifts to subactive mode. When an interrupt occurs in watch mode, and if the LSON bit of LPWRCR is 1, a transition is made to subactive mode. And if an interrupt occurs in subsleep mode, a transition is made to subactive mode.

In subactive mode, the CPU operates at low speed on the subclock, and the program is executed step by step. Peripheral modules other than PBC, TMR\_0 to TMR\_3, WDT\_0, and WDT\_1, and system clock oscillator are also stopped.

When operating the CPU in subactive mode, the SCKCR SCK2 to SCK0 bits must be set to 0.

#### 24.9.2 Exiting Subactive Mode

Subactive mode is exited by the SLEEP instruction or the  $\overline{\text{RES}}$ ,  $\overline{\text{MRES}}$  or  $\overline{\text{STBY}}$  pin.

• Exiting Subactive Mode by SLEEP Instruction

When the SLEEP instruction is executed with the SSBY bit in SBYCR = 1, the DTON bit in LPWRCR = 0, and the PSS bit in TCSR\_1 (WDT\_1) = 1, the CPU exits subactive mode and a transition is made to watch mode. When the SLEEP instruction is executed with the SSBY bit in SBYCR = 0, the LSON bit in LPWRCR = 1, and the PSS bit in TCSR\_1 (WDT\_1) = 1, a transition is made to subsleep mode. Finally, when the SLEEP instruction is executed with the SSBY bit in SBYCR = 1, the DTON bit in LPWRCR = 1, the LSON bit = 0, and the PSS bit in TCSR\_1 (WDT\_1) = 1, a direct transition is made to high-speed mode (SCK2 to SCK0 all 0).

- Exiting Subactive Mode by RES Pin or MRES Pin For exiting subactive mode by the RES or MRES pin, see section 24.4.2, Clearing Software Standby Mode.

- Exiting Subactive Mode by STBY Pin When the STBY pin level is driven low, a transition is made to hardware standby mode.

#### Section 26 List of Registers

| Register Name                          | Abbrevia-<br>tion | Bit No. | Address <sup>*1</sup> | Module | Data Bus<br>Width | Access<br>State |

|----------------------------------------|-------------------|---------|-----------------------|--------|-------------------|-----------------|

| I <sup>2</sup> C bus status register_1 | ICSR_1            | 8       | H'FF81*3              | IIC_1  | 8                 | 2               |

| Serial control register_1              | SCR_1             | 8       | H'FF82                | SCI_1  | 8                 | 2               |

| Transmit data register_1               | TDR_1             | 8       | H'FF83                | SCI_1  | 8                 | 2               |

| Serial status register_1               | SSR_1             | 8       | H'FF84                | SCI_1  | 8                 | 2               |

| Receive data register_1                | RDR_1             | 8       | H'FF85                | SCI_1  | 8                 | 2               |

| Smart card mode register_1             | SCMR_1            | 8       | H'FF86 <sup>*3</sup>  | SCI_1  | 8                 | 2               |

| I <sup>2</sup> C bus data register_1   | ICDR_1            | 8       | H'FF86 <sup>*3</sup>  | IIC_1  | 8                 | 2               |

| Second slave address register_1        | SARX_1            | 8       | H'FF86 <sup>*3</sup>  | IIC_1  | 8                 | 2               |

| I <sup>2</sup> C bus mode register_1   | ICMR_1            | 8       | H'FF87                | IIC_1  | 8                 | 2               |

| Slave address register_1               | SAR_1             | 8       | H'FF87                | IIC_1  | 8                 | 2               |

| Serial mode register_2                 | SMR_2             | 8       | H'FF88                | SCI_2  | 8                 | 2               |

| Bit rate register_2                    | BRR_2             | 8       | H'FF89                | SCI_2  | 8                 | 2               |

| Serial control register_2              | SCR_2             | 8       | H'FF8A                | SCI_2  | 8                 | 2               |

| Transmit data register_2               | TDR_2             | 8       | H'FF8B                | SCI_2  | 8                 | 2               |

| Serial status register_2               | SSR_2             | 8       | H'FF8C                | SCI_2  | 8                 | 2               |

| Receive data register_2                | RDR_2             | 8       | H'FF8D                | SCI_2  | 8                 | 2               |

| Smart card mode register_2             | SCMR_2            | 8       | H'FF8E                | SCI_2  | 8                 | 2               |

| A/D data register AH                   | ADDRAH            | 8       | H'FF90                | A/D    | 8                 | 2               |

| A/D data register AL                   | ADDRAL            | 8       | H'FF91                | A/D    | 8                 | 2               |

| A/D data register BH                   | ADDRBH            | 8       | H'FF92                | A/D    | 8                 | 2               |

| A/D data register BL                   | ADDRBL            | 8       | H'FF93                | A/D    | 8                 | 2               |

| A/D data register CH                   | ADDRCH            | 8       | H'FF94                | A/D    | 8                 | 2               |

| A/D data register CL                   | ADDRCL            | 8       | H'FF95                | A/D    | 8                 | 2               |

| A/D data register DH                   | ADDRDH            | 8       | H'FF96                | A/D    | 8                 | 2               |

| A/D data register DL                   | ADDRDL            | 8       | H'FF97                | A/D    | 8                 | 2               |

| A/D control/status register            | ADCSR             | 8       | H'FF98                | A/D    | 8                 | 2               |

| A/D control register                   | ADCR              | 8       | H'FF99                | A/D    | 8                 | 2               |

| Timer control/status register_1        | TCSR_1            | 8       | H'FFA2                | WDT_1  | 16                | 2               |

| Timer counter_1                        | TCNT_1            | 8       | H'FFA2<br>(write)     | WDT_1  | 16                | 2               |

| Timer counter_1                        | TCNT_1            | 8       | H'FFA3<br>(read)      | WDT_1  | 16                | 2               |

| Flash memory control register 1        | FLMCR1            | 8       | H'FFA8                | FLASH  | 8                 | 2               |

Rev. 6.00 Mar. 18, 2010 Page 816 of 982 REJ09B0054-0600

| Register |        |        |        |        |        |        |        |        |        |

|----------|--------|--------|--------|--------|--------|--------|--------|--------|--------|

| Name     | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Module |

| IPRF     | _      | IPR6   | IPR5   | IPR4   | —      | IPR2   | IPR1   | IPR0   | INT    |

| IPRG     | _      | IPR6   | IPR5   | IPR4   | _      | IPR2   | IPR1   | IPR0   |        |

| IPRH     | _      | IPR6   | IPR5   | IPR4   | _      | IPR2   | IPR1   | IPR0   |        |

| IPRI     | _      | IPR6   | IPR5   | IPR4   | _      | IPR2   | IPR1   | IPR0   |        |

| IPRJ     | _      | IPR6   | IPR5   | IPR4   | _      | IPR2   | IPR1   | IPR0   |        |

| IPRK     | _      | IPR6   | IPR5   | IPR4   | _      | IPR2   | IPR1   | IPR0   |        |

| IPRL     | _      | IPR6   | IPR5   | IPR4   | _      | IPR2   | IPR1   | IPR0   |        |

| IPRO     | —      | IPR6   | IPR5   | IPR4   | _      | IPR2   | IPR1   | IPR0   |        |

| ABWCR    | ABW7   | ABW6   | ABW5   | ABW4   | ABW3   | ABW2   | ABW1   | ABW0   | BSC    |

| ASTCR    | AST7   | AST6   | AST5   | AST4   | AST3   | AST2   | AST1   | AST0   |        |

| WCRH     | W71    | W70    | W61    | W60    | W51    | W50    | W41    | W40    |        |

| WCRL     | W31    | W30    | W21    | W20    | W11    | W10    | W01    | W00    |        |

| BCRH     | ICIS1  | ICIS0  | BRSTRM | BRSTS1 | BRSTS0 | _      | _      | _      |        |

| BCRL     | BRLE   | _      | _      | _      | _      | _      | _      | WAITE  |        |

| RAMER    | _      | _      | _      | _      | RAMS   | RAM2   | RAM1   | RAM0   | FLASH  |

| MAR_0A   | _      | _      | _      | _      | _      | _      | _      | _      | DMAC   |

|          | Bit 23 | Bit 22 | Bit 21 | Bit 20 | Bit 19 | Bit 18 | Bit 17 | Bit 16 |        |

|          | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  |        |

|          | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  |        |

| IOAR_0A  | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  |        |

|          | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  |        |

| ETCR_0A  | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  |        |

|          | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  |        |

| MAR_0B   | _      | _      | _      | _      | _      | _      | _      | _      |        |

|          | Bit 23 | Bit 22 | Bit 21 | Bit 20 | Bit 19 | Bit 18 | Bit 17 | Bit 16 |        |

|          | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  |        |

|          | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  |        |

| IOAR_0B  | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  |        |

|          | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  |        |

| ETCR_0B  | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  |        |

|          | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  |        |

|          |        |        |        |        |        |        |        |        |        |

#### Table 27.27DC Characteristics (2)

Condition A (F-ZTAT version):

$$V_{cc} = 3.0 \text{ V}$$

to 5.5 V,  $AV_{cc} = 3.6 \text{ V}$  to 5.5 V,

$V_{ref} = 3.6 \text{ V}$  to  $AV_{cc}$ ,  $V_{ss} = AV_{ss} = 0 \text{ V}$ ,

$T_a = -20^{\circ}\text{C}$  to  $+75^{\circ}\text{C}$  (regular specifications),

$T_a = -40^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$  (wide-range specifications)<sup>\*1</sup>

| ltem                                 |                                       | Symbol             | Min | Тур                           | Мах                           | Unit | Test Conditions                                                                |

|--------------------------------------|---------------------------------------|--------------------|-----|-------------------------------|-------------------------------|------|--------------------------------------------------------------------------------|

| Input                                | RES                                   | C <sub>in</sub>    |     | _                             | 30                            | pF   | Vin = 0 V,                                                                     |

| capacitance                          | NMI                                   |                    |     | _                             | 30                            | pF   | f = 1 MHz,<br>- Ta = 25°C                                                      |

|                                      | P32 to P35                            | _                  |     |                               | 20                            | pF   | -1a = 25 C                                                                     |

|                                      | All input pins<br>except the<br>above | _                  |     | _                             | 15                            | pF   | -                                                                              |

| Current<br>dissipation <sup>*2</sup> | Normal operation                      | I_cc <sup>*4</sup> |     | 23<br>V <sub>cc</sub> = 3.0 V | 40<br>V <sub>cc</sub> = 5.5 V | mA   | f = 13.5 MHz                                                                   |

|                                      | Sleep mode                            | -                  |     | 18<br>V <sub>cc</sub> = 3.0 V | 30<br>V <sub>cc</sub> = 5.5 V | mA   | f = 13.5 MHz                                                                   |

|                                      | All modules stopped                   | _                  |     | 13                            | _                             | mA   | $      f = 13.5 \text{ MHz}, \\ V_{cc} = 3.0 \text{ V} \\ (reference values) $ |

|                                      | Medium-<br>speed mode<br>(¢/32)       | _                  |     | 13                            | _                             | mA   | $      f = 13.5 \text{ MHz}, \\ V_{cc} = 3.0 \text{ V} \\ (reference values) $ |

|                                      | Subactive<br>mode                     | -                  |     | 80                            | 180                           | μA   | $V_{cc} = 3.0 V,$<br>When 32.768<br>kHz crystal<br>resonator is used           |

|                                      | Subsleep<br>mode                      | _                  |     | 60                            | 130                           | μA   | $V_{cc} = 3.0 V,$<br>When 32.768<br>kHz crystal<br>resonator is used           |

|                                      | Watch mode                            | _                  |     | 8                             | 40                            | μA   | V <sub>cc</sub> = 3.0 V,<br>When 32.768<br>kHz crystal<br>resonator is used    |

### 27.5 Electrical Characteristics of H8S/2238R and H8S/2236R

#### 27.5.1 Absolute Maximum Ratings

Table 27.38 lists the absolute maximum ratings.

#### Table 27.38 Absolute Maximum Ratings

| Item                                 | Symbol           | Value                                   | Unit |

|--------------------------------------|------------------|-----------------------------------------|------|

| Power supply voltage                 | V <sub>cc</sub>  | -0.3 to +4.3                            | V    |

|                                      | CV <sub>cc</sub> | -0.3 to +4.3                            | V    |

| Input voltage (except ports 4 and 9) | $V_{in}$         | -0.3 to V <sub>cc</sub> +0.3            | V    |

| Input voltage (ports 4 and 9)        | $V_{in}$         | –0.3 to AV <sub>cc</sub> +0.3           | V    |

| Reference power supply voltage       | $V_{ref}$        | –0.3 to AV <sub>cc</sub> +0.3           | V    |

| Analog power supply voltage          | $AV_{cc}$        | -0.3 to +4.3                            | V    |

| Analog input voltage                 | V <sub>AN</sub>  | –0.3 to AV <sub>cc</sub> +0.3           | V    |

| Operating temperature                | T <sub>opr</sub> | Regular specifications: -20 to +75*1    | °C   |

|                                      |                  | Wide-range specifications: -40 to +85*2 | _    |

| Storage temperature                  | $T_{stg}$        | -55 to +125                             | °C   |

Caution: Permanent damage to the chip may result if absolute maximum rating are exceeded.

Notes: 1. When the operating voltage in read is  $V_{cc} = 2.7 \text{ V}$  to 3.6 V, the operating temperature ranges for flash memory programming/erasing are  $T_a = -20^{\circ}\text{C}$  to  $+75^{\circ}\text{C}$ . When the operating voltage in read is  $V_{cc} = 2.2 \text{ V}$  to 3.6 V, the operating temperature ranges for flash memory programming/erasing are  $T_a = -20^{\circ}\text{C}$  to  $+50^{\circ}\text{C}$ .

2. The operating temperature ranges for flash memory programming/erasing are  $T_a = -40^{\circ}$ C to +80°C (regular specifications).