#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                              |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ST7                                                                   |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 8MHz                                                                  |

| Connectivity               | SCI, SPI                                                              |

| Peripherals                | POR, PWM, WDT                                                         |

| Number of I/O              | 32                                                                    |

| Program Memory Size        | 16KB (16K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 512 x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 2.85V ~ 3.6V                                                          |

| Data Converters            | A/D 12x10b                                                            |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 44-LQFP                                                               |

| Supplier Device Package    | -                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st72f324lj4t6 |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

|    | 12.7 EMC CHARACTERISTICS                                       | 121 |

|----|----------------------------------------------------------------|-----|

|    | 12.7.1 Functional EMS (Electro Magnetic Susceptibility)        |     |

|    | 12.7.2 Electro Magnetic Interference (EMI)                     |     |

|    | 12.7.3 Absolute Maximum Ratings (Electrical Sensitivity)       |     |

|    | 12.8 I/O PORT PIN CHARACTERISTICS                              |     |

|    | 12.8.1 General Characteristics                                 |     |

|    |                                                                |     |

|    | 12.9 CONTROL PIN CHARACTERISTICS                               |     |

|    | 12.9.1 Asynchronous RESET Pin                                  |     |

|    | 12.10 TIMER PERIPHERAL CHARACTERISTICS                         |     |

|    | 12.10.116-Bit Timer                                            |     |

|    | 12.11 COMMUNICATION INTERFACE CHARACTERISTICS                  | 130 |

|    | 12.11.1SPI - Serial Peripheral Interface                       |     |

|    | 12.12 10-BIT ADC CHARACTERISTICS                               |     |

|    | 12.12.1Analog Power Supply and Reference Pins                  |     |

|    | 12.12.2General PCB Design Guidelines                           |     |

|    | 12.12.3ADC Accuracy                                            |     |

| -  | PACKAGE CHARACTERISTICS                                        |     |

|    | 13.1 PACKAGE MECHANICAL DATA                                   | 136 |

|    | 13.2 THERMAL CHARACTERISTICS                                   | 138 |

|    | 13.3 SOLDERING INFORMATION                                     | 139 |

| 14 | DEVICE CONFIGURATION AND ORDERING INFORMATION                  | 140 |

|    | 14.1 FLASH OPTION BYTES                                        | 140 |

|    | 14.2 DEVICE ORDERING INFORMATION AND TRANSFER OF CUSTOMER CODE | 142 |

|    | 14.3 DEVELOPMENT TOOLS                                         | 145 |

|    | 14.3.1 Starter kits                                            | 145 |

|    | 14.3.2 Development and debugging tools                         |     |

|    | 14.3.3 Programming tools                                       | 145 |

|    | 14.3.4 Socket and Emulator Adapter Information                 |     |

|    | 14.4 ST7 APPLICATION NOTES                                     |     |

|    | KNOWN LIMITATIONS                                              |     |

|    | 15.1 ALL FLASH AND ROM DEVICES                                 |     |

|    | 15.1.1 Safe Connection of OSC1/OSC2 Pins                       |     |

|    | 15.1.2 Unexpected Reset Fetch                                  |     |

|    | 15.1.4 16-bit Timer PWM Mode                                   |     |

|    | 15.1.5 ADC Conversion Spurious Results                         |     |

|    | 15.1.6 SCI Wrong Break duration                                |     |

|    | 15.1.7 External interrupt missed                               | 150 |

|    | 15.2 ROM DEVICES ONLY                                          | 151 |

|    | 15.2.1 I/O Port A and F Configuration                          |     |

|    | 15.3 FLASH DEVICES ONLY                                        | 152 |

|    | 15.3.1 Timer A Restrictions in Flash Devices                   |     |

|    | 15.3.2 External clock source with PLL                          |     |

| 40 | 15.3.3 39-Pulse ICC Entry Mode                                 |     |

| 16 | REVISION HISTORY                                               | 153 |

|        | Pin    | n n°   |        |                         |      | Le                        | evel   |       |     | Ρ   | ort |     |      | Main                                      |                                                                                          |                                                         |  |

|--------|--------|--------|--------|-------------------------|------|---------------------------|--------|-------|-----|-----|-----|-----|------|-------------------------------------------|------------------------------------------------------------------------------------------|---------------------------------------------------------|--|

| P48    | P44    | P32    | 32     | Pin Name                | Type | ut                        | out    |       | In  | put |     | Out | tput | function<br>(after                        | Alternate                                                                                | Function                                                |  |

| LQFP48 | LQFP44 | LQFP32 | SDIP32 |                         |      | Input                     | Output | float | ndm | int | ana | OD  | ЪР   | reset)                                    |                                                                                          |                                                         |  |

| 27     | 25     | 10     | 13     | PC2 (HS)/ICAP2_B        | I/O  | $C_T$                     | HS     | Χ     | Х   |     |     | Х   | Х    | Port C2                                   | Port C2 Timer B Input Capture 2                                                          |                                                         |  |

| 28     | 26     | 11     | 14     | PC3 (HS)/ICAP1_B        | I/O  | $\mathrm{C}_{\mathrm{T}}$ | HS     | Х     | Х   |     |     | Х   | Х    | Port C3                                   | Timer B Inpu                                                                             | t Capture 1                                             |  |

| 29     | 27     | 12     | 15     | PC4/MISO/ICCDA-<br>TA   | I/O  | CT                        |        | x     | х   |     |     | х   | x    | Port C4                                   | SPI Master<br>In / Slave<br>Out Data                                                     | ICC Data In-<br>put                                     |  |

| 30     | 28     | 13     | 16     | PC5/MOSI/AIN14          | I/O  | CT                        |        | x     | х   |     | х   | х   | х    | Port C5                                   | SPI Master<br>Out / Slave<br>In Data                                                     | ADC Analog<br>Input 14                                  |  |

| 31     | 29     | 14     | 17     | PC6/SCK/ICCCLK          | I/O  | C <sub>T</sub>            |        | х     | Х   |     |     | х   | х    | Port C6                                   | SPI Serial<br>Clock                                                                      | ICC Clock<br>Output                                     |  |

| 32     | 30     | 15     | 18     | PC7/SS/AIN15            | I/O  | CT                        |        | x     | х   |     | х   | х   | х    | Port C7                                   | SPI Slave<br>Select (ac-<br>tive low)                                                    | ADC Analog<br>Input 15                                  |  |

| 34     | 31     | 16     | 19     | PA3 (HS)                | I/O  | $C_{T}$                   | HS     | Χ     |     | ei0 |     | Х   | Х    | Port A3                                   |                                                                                          |                                                         |  |

| 35     | 32     |        |        | V <sub>DD_1</sub>       | S    |                           |        |       |     |     |     |     |      | Digital M                                 | ain Supply Vol                                                                           | tage <sup>5)</sup>                                      |  |

| 36     | 33     |        |        | V <sub>SS_1</sub>       | S    |                           |        |       |     |     |     |     |      | Digital G                                 | Digital Ground Voltage <sup>5)</sup>                                                     |                                                         |  |

| 37     | 34     | 17     | 20     | PA4 (HS)                | I/O  | $C_{T}$                   | HS     | Χ     | Х   |     |     | Х   | Х    | Port A4                                   |                                                                                          |                                                         |  |

| 38     | 35     |        |        | PA5 (HS)                | I/O  | $C_T$                     | HS     | Χ     | Х   |     |     | Х   | Х    | Port A5                                   |                                                                                          |                                                         |  |

| 39     | 36     | 18     | 21     | PA6 (HS)                | I/O  | $\mathrm{C}_{\mathrm{T}}$ | HS     | Х     |     |     |     | Т   |      | Port A6 <sup>1</sup>                      | )                                                                                        |                                                         |  |

| 40     | 37     | 19     | 22     | PA7 (HS)                | I/O  | $\mathrm{C}_{\mathrm{T}}$ | HS     | Х     |     |     |     | Т   |      | Port A7 <sup>1</sup>                      | )                                                                                        |                                                         |  |

| 41     | 38     | 20     | 23     | V <sub>PP</sub> /ICCSEL | I    |                           |        |       |     |     |     |     |      | grammin<br>program<br>Section 1           | ied low. In the<br>g mode, this p<br>ning voltage ir<br>2.9.2 for more<br>nust not be ap | in acts as the nput V <sub>PP</sub> . See details. High |  |

| 42     | 39     | 21     | 24     | RESET                   | I/O  | $C_T$                     |        |       |     |     |     |     |      | Top prior                                 | ity non maska                                                                            | ble interrupt.                                          |  |

| 43     | 40     | 22     | 25     | V <sub>SS_2</sub>       | S    |                           |        |       |     |     |     |     |      | Digital G                                 | round Voltage <sup>t</sup>                                                               | 5)                                                      |  |

| 44     | 41     | 23     | 26     | OSC2                    | 0    |                           |        |       |     |     |     |     |      | Resonate                                  | or oscillator inv                                                                        | verter output                                           |  |

| 45     | 42     | 24     | 27     | OSC1                    | I    |                           |        |       |     |     |     |     |      |                                           | clock input or l<br>verter input                                                         | Resonator os-                                           |  |

| 46     | 43     | 25     | 28     | V <sub>DD_2</sub>       | S    |                           |        |       |     |     |     |     |      | Digital Main Supply Voltage <sup>5)</sup> |                                                                                          |                                                         |  |

| 47     | 44     | 26     | 29     | PE0/TDO                 | I/O  | $C_T$                     |        | Х     | Х   |     |     | Х   | Х    | Port E0                                   |                                                                                          |                                                         |  |

| 48     | 1      | 27     | 30     | PE1/RDI                 | I/O  | $C_T$                     |        | Х     | Х   |     |     | Х   | Х    | Port E1                                   |                                                                                          |                                                         |  |

| 3      | 2      | 28     | 31     | PB0                     | I/O  | $C_T$                     |        | х     | е   | i2  |     | Х   | Х    | Port B0                                   |                                                                                          |                                                         |  |

| 4      | 3      |        |        | PB1                     | I/O  | $C_T$                     |        | Х     | е   | i2  |     | Х   | Х    | Port B1                                   |                                                                                          |                                                         |  |

| 5      | 4      |        |        | PB2                     | I/O  | $C_T$                     |        | Х     | е   | i2  |     | Х   | Х    | Port B2                                   |                                                                                          |                                                         |  |

| 6      | 5      | 29     | 32     | PB3                     | I/O  | $C_T$                     |        | Χ     |     | ei2 |     | Х   | Х    | Port B3                                   |                                                                                          |                                                         |  |

## Notes:

1. In the interrupt input column, "eiX" defines the associated external interrupt vector. If the weak pull-up column (wpu) is merged with the interrupt column (int), then the I/O configuration is pull-up interrupt input, else the configuration is floating interrupt input.

2. In the open drain output column, "T" defines a true open drain I/O (P-Buffer and protection diode to V<sub>DD</sub>

| Address                                                                                                                                      | Block   | Register<br>Label                                                                                                                                              | Register Name                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Reset<br>Status                                                                                       | Remarks                                                                                                                                                                                                                                        |

|----------------------------------------------------------------------------------------------------------------------------------------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0031h<br>0032h<br>0033h<br>0034h<br>0035h<br>0036h<br>0037h<br>0038h<br>0039h<br>003Ah<br>003Ah<br>003Bh<br>003Ch<br>003Dh<br>003Eh<br>003Fh | TIMER A | TACR2<br>TACR1<br>TACSR<br>TAIC1HR<br>TAIC1LR<br>TAOC1HR<br>TAOC1LR<br>TACHR<br>TACHR<br>TACLR<br>TAACHR<br>TAACLR<br>TAIC2HR<br>TAIC2LR<br>TAIC2LR<br>TAOC2LR | Timer A Control Register 2<br>Timer A Control Register 1<br>Timer A Control/Status Register <sup>3)4)</sup><br>Timer A Input Capture 1 High Register<br>Timer A Input Capture 1 Low Register<br>Timer A Output Compare 1 High Register<br>Timer A Output Compare 1 Low Register<br>Timer A Counter High Register<br>Timer A Counter Low Register<br>Timer A Alternate Counter High Register<br>Timer A Alternate Counter Low Register<br>Timer A Input Capture 2 High Register <sup>3)</sup><br>Timer A Input Capture 2 Low Register <sup>4)</sup><br>Timer A Output Compare 2 Low Register <sup>4)</sup> | 00h<br>00h<br>xxxx x0xxb<br>xxh<br>80h<br>00h<br>FFh<br>FCh<br>FCh<br>FCh<br>xxh<br>xxh<br>80h<br>00h | R/W<br>R/W<br>Read Only<br>Read Only<br>R/W<br>Read Only<br>Read Only |

| 0040h                                                                                                                                        |         | 4                                                                                                                                                              | Reserved Area (1 Byte)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                       |                                                                                                                                                                                                                                                |

| 0041h<br>0042h<br>0043h<br>0044h<br>0045h<br>0046h<br>0047h<br>0048h<br>0049h<br>004Ah<br>004Bh<br>004Ch<br>004Ch<br>004Ch<br>004Fh          | TIMER B | TBCR2<br>TBCR1<br>TBCSR<br>TBIC1HR<br>TBIC1LR<br>TBOC1HR<br>TBOC1LR<br>TBCHR<br>TBCLR<br>TBACHR<br>TBACLR<br>TBIC2HR<br>TBIC2LR<br>TBIC2LR                     | Timer B Control Register 2<br>Timer B Control Register 1<br>Timer B Control/Status Register<br>Timer B Input Capture 1 High Register<br>Timer B Input Capture 1 Low Register<br>Timer B Output Compare 1 High Register<br>Timer B Output Compare 1 Low Register<br>Timer B Counter High Register<br>Timer B Counter High Register<br>Timer B Alternate Counter High Register<br>Timer B Alternate Counter Low Register<br>Timer B Input Capture 2 High Register<br>Timer B Input Capture 2 Low Register<br>Timer B Output Compare 2 High Register<br>Timer B Output Compare 2 Low Register                | 00h<br>00h<br>xxxx x0xxb<br>xxh<br>80h<br>00h<br>FFh<br>FCh<br>FCh<br>FCh<br>xxh<br>xxh<br>80h<br>00h | R/W<br>R/W<br>Read Only<br>Read Only<br>R/W<br>R/W<br>Read Only<br>Read Only<br>Read Only<br>Read Only<br>Read Only<br>Read Only<br>Read Only<br>Read Only<br>Read Only<br>Read Only<br>R/W                                                    |

| 0050h<br>0051h<br>0052h<br>0053h<br>0054h<br>0055h<br>0056h<br>0057h                                                                         | SCI     | SCISR<br>SCIDR<br>SCIBRR<br>SCICR1<br>SCICR2<br>SCIERPR<br>SCIETPR                                                                                             | SCI Status Register<br>SCI Data Register<br>SCI Baud Rate Register<br>SCI Control Register 1<br>SCI Control Register 2<br>SCI Extended Receive Prescaler Register<br>Reserved area<br>SCI Extended Transmit Prescaler Register                                                                                                                                                                                                                                                                                                                                                                            | C0h<br>xxh<br>00h<br>x000 0000h<br>00h<br><br>00h                                                     | Read Only<br>R/W<br>R/W<br>R/W<br>R/W<br>R/W                                                                                                                                                                                                   |

| 0058h<br>to<br>006Fh                                                                                                                         |         |                                                                                                                                                                | Reserved Area (24 Bytes)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                       |                                                                                                                                                                                                                                                |

| 0070h<br>0071h<br>0072h                                                                                                                      | ADC     | ADCCSR<br>ADCDRH<br>ADCDRL                                                                                                                                     | Control/Status Register<br>Data High Register<br>Data Low Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 00h<br>00h<br>00h                                                                                     | R/W<br>Read Only<br>Read Only                                                                                                                                                                                                                  |

| 0073h<br>007Fh                                                                                                                               |         |                                                                                                                                                                | Reserved Area (13 Bytes)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                       |                                                                                                                                                                                                                                                |

57

## CENTRAL PROCESSING UNIT (Cont'd)

Stack Pointer (SP)

Read/Write

Reset Value: 01 FFh

| 15  |     |     |     |     |     |     | 8   |

|-----|-----|-----|-----|-----|-----|-----|-----|

| 0   | 0   | 0   | 0   | 0   | 0   | 0   | 1   |

| 7   |     |     |     |     |     |     | 0   |

| SP7 | SP6 | SP5 | SP4 | SP3 | SP2 | SP1 | SP0 |

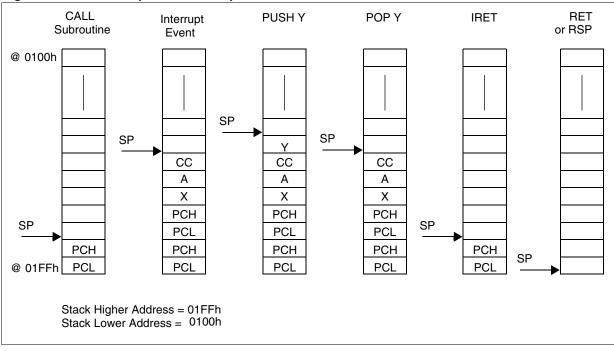

The Stack Pointer is a 16-bit register which is always pointing to the next free location in the stack. It is then decremented after data has been pushed onto the stack and incremented before data is popped from the stack (see Figure 10).

Since the stack is 256 bytes deep, the 8 most significant bits are forced by hardware. Following an MCU Reset, or after a Reset Stack Pointer instruction (RSP), the Stack Pointer contains its reset value (the SP7 to SP0 bits are set) which is the stack higher address.

Figure 10. Stack Manipulation Example

The least significant byte of the Stack Pointer (called S) can be directly accessed by a LD instruction.

**Note:** When the lower limit is exceeded, the Stack Pointer wraps around to the stack upper limit, without indicating the stack overflow. The previously stored information is then overwritten and therefore lost. The stack also wraps in case of an underflow.

The stack is used to save the return address during a subroutine call and the CPU context during an interrupt. The user may also directly manipulate the stack by means of the PUSH and POP instructions. In the case of an interrupt, the PCL is stored at the first location pointed to by the SP. Then the other registers are stored in the next locations as shown in Figure 10.

- When an interrupt is received, the SP is decremented and the context is pushed on the stack.

- On return from interrupt, the SP is incremented and the context is popped from the stack.

A subroutine call occupies two locations and an interrupt five locations in the stack area.

## **7 INTERRUPTS**

## 7.1 INTRODUCTION

The ST7 enhanced interrupt management provides the following features:

- Hardware interrupts

- Software interrupt (TRAP)

- Nested or concurrent interrupt management with flexible interrupt priority and level management:

- Up to 4 software programmable nesting levels

- Up to 16 interrupt vectors fixed by hardware

- 2 non maskable events: RESET, TRAP

This interrupt management is based on:

- Bit 5 and bit 3 of the CPU CC register (I1:0),

- Interrupt software priority registers (ISPRx),

- Fixed interrupt vector addresses located at the high addresses of the memory map (FFE0h to FFFFh) sorted by hardware priority order.

This enhanced interrupt controller guarantees full upward compatibility with the standard (not nested) ST7 interrupt controller.

## 7.2 MASKING AND PROCESSING FLOW

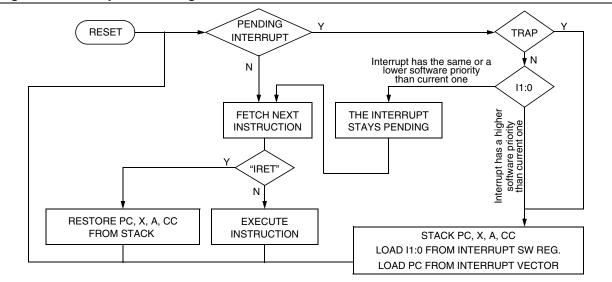

The interrupt masking is managed by the I1 and I0 bits of the CC register and the ISPRx registers which give the interrupt software priority level of each interrupt vector (see Table 7). The processing flow is shown in Figure 14

## Figure 14. Interrupt Processing Flowchart

When an interrupt request has to be serviced:

- Normal processing is suspended at the end of the current instruction execution.

- The PC, X, A and CC registers are saved onto the stack.

- I1 and I0 bits of CC register are set according to the corresponding values in the ISPRx registers of the serviced interrupt vector.

- The PC is then loaded with the interrupt vector of the interrupt to service and the first instruction of the interrupt service routine is fetched (refer to "Interrupt Mapping" table for vector addresses).

The interrupt service routine should end with the IRET instruction which causes the contents of the saved registers to be recovered from the stack.

**Note**: As a consequence of the IRET instruction, the I1 and I0 bits will be restored from the stack and the program in the previous level will resume.

## Table 7. Interrupt Software Priority Levels

| Interrupt software priority   | Level | l1 | 10 |

|-------------------------------|-------|----|----|

| Level 0 (main)                | Low   | 1  | 0  |

| Level 1                       |       | 0  | 1  |

| Level 2                       | ▼     | 0  | 0  |

| Level 3 (= interrupt disable) | High  | 1  | 1  |

## INTERRUPTS (Cont'd)

| Instruction | New Description                 | Function/Example      | 11 | Н | 10 | Ν | Z | С |

|-------------|---------------------------------|-----------------------|----|---|----|---|---|---|

| HALT        | Entering Halt mode              |                       | 1  |   | 0  |   |   |   |

| IRET        | Interrupt routine return        | Pop CC, A, X, PC      | 11 | Н | 10 | Ν | Z | С |

| JRM         | Jump if I1:0=11 (level 3)       | l1:0=11 ?             |    |   |    |   |   |   |

| JRNM        | Jump if I1:0<>11                | 11:0<>11 ?            |    |   |    |   |   |   |

| POP CC      | Pop CC from the Stack           | Mem => CC             | 11 | Н | 10 | Ν | Z | С |

| RIM         | Enable interrupt (level 0 set)  | Load 10 in I1:0 of CC | 1  |   | 0  |   |   |   |

| SIM         | Disable interrupt (level 3 set) | Load 11 in I1:0 of CC | 1  |   | 1  |   |   |   |

| TRAP        | Software trap                   | Software NMI          | 1  |   | 1  |   |   |   |

| WFI         | Wait for interrupt              |                       | 1  |   | 0  |   |   |   |

## **Table 8. Dedicated Interrupt Instruction Set**

Note: During the execution of an interrupt routine, the HALT, POPCC, RIM, SIM and WFI instructions change the current software priority up to the next IRET instruction or one of the previously mentioned instructions.

## 16-BIT TIMER (Cont'd)

57

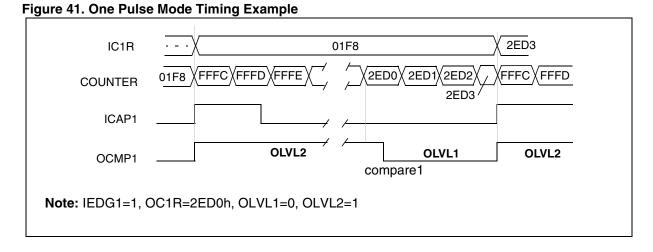

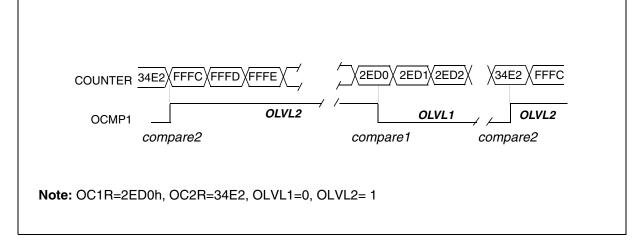

Figure 42. Pulse Width Modulation Mode Timing Example with 2 Output Compare Functions

## SERIAL COMMUNICATIONS INTERFACE (Cont'd)

## 10.5.7 Register Description STATUS REGISTER (SCISR)

Read Only

Reset Value: 1100 0000 (C0h)

| /    |    |      |      |    |    |    | 0  |

|------|----|------|------|----|----|----|----|

| TDRE | тс | RDRF | IDLE | OR | NF | FE | PE |

#### Bit 7 = **TDRE** *Transmit data register empty.*

This bit is set by hardware when the content of the TDR register has been transferred into the shift register. An interrupt is generated if the TIE bit = 1 in the SCICR2 register. It is cleared by a software sequence (an access to the SCISR register followed by a write to the SCIDR register).

0: Data is not transferred to the shift register

1: Data is transferred to the shift register

**Note:** Data is not transferred to the shift register unless the TDRE bit is cleared.

#### Bit 6 = TC Transmission complete.

This bit is set by hardware when transmission of a frame containing Data is complete. An interrupt is generated if TCIE = 1 in the SCICR2 register. It is cleared by a software sequence (an access to the SCISR register followed by a write to the SCIDR register).

0: Transmission is not complete

1: Transmission is complete

**Note:** TC is not set after the transmission of a Preamble or a Break.

#### Bit 5 = **RDRF** *Received data ready flag.*

This bit is set by hardware when the content of the RDR register has been transferred to the SCIDR register. An interrupt is generated if RIE = 1 in the SCICR2 register. It is cleared by a software sequence (an access to the SCISR register followed by a read to the SCIDR register).

0: Data is not received

1: Received data is ready to be read

#### Bit 4 = **IDLE** *Idle line detect.*

This bit is set by hardware when a Idle Line is detected. An interrupt is generated if the ILIE = 1 in the SCICR2 register. It is cleared by a software sequence (an access to the SCISR register followed by a read to the SCIDR register).

0: No Idle Line is detected

1: Idle Line is detected

**Note:** The IDLE bit is not set again until the RDRF bit has been set itself (that is, a new idle line occurs).

## Bit 3 = **OR** Overrun error.

This bit is set by hardware when the word currently being received in the shift register is ready to be transferred into the RDR register while RDRF = 1. An interrupt is generated if RIE = 1 in the SCICR2 register. It is cleared by a software sequence (an access to the SCISR register followed by a read to the SCIDR register).

0: No Overrun error

1: Overrun error is detected

**Note:** When this bit is set RDR register content is not lost but the shift register is overwritten.

#### Bit 2 = NF Noise flag.

This bit is set by hardware when noise is detected on a received frame. It is cleared by a software sequence (an access to the SCISR register followed by a read to the SCIDR register).

0: No noise is detected

1: Noise is detected

**Note:** This bit does not generate interrupt as it appears at the same time as the RDRF bit which itself generates an interrupt.

#### Bit 1 = **FE** Framing error.

This bit is set by hardware when a de-synchronization, excessive noise or a break character is detected. It is cleared by a software sequence (an access to the SCISR register followed by a read to the SCIDR register).

0: No Framing error is detected

1: Framing error or break character is detected

**Note:** This bit does not generate interrupt as it appears at the same time as the RDRF bit which itself generates an interrupt. If the word currently being transferred causes both frame error and overrun error, it will be transferred and only the OR bit will be set.

#### Bit 0 = PE Parity error.

This bit is set by hardware when a parity error occurs in receiver mode. It is cleared by a software sequence (a read to the status register followed by an access to the SCIDR data register). An interrupt is generated if PIE = 1 in the SCICR1 register. 0: No parity error

1: Parity error

## SERIAL COMMUNICATIONS INTERFACE (Cont'd) **CONTROL REGISTER 1 (SCICR1)**

### Read/Write

Reset Value: x000 0000 (x0h)

| 7  |    |      |   |      |     |    | 0   |

|----|----|------|---|------|-----|----|-----|

| R8 | Т8 | SCID | М | WAKE | PCE | PS | PIE |

#### Bit 7 = **R8** Receive data bit 8.

This bit is used to store the 9th bit of the received word when M = 1.

#### Bit 6 = T8 Transmit data bit 8.

This bit is used to store the 9th bit of the transmitted word when M = 1.

Bit 5 = **SCID** Disabled for low power consumption When this bit is set the SCI prescalers and outputs are stopped and the end of the current byte transfer in order to reduce power consumption. This bit is set and cleared by software.

0: SCI enabled

1: SCI prescaler and outputs disabled

Bit 4 = **M** Word length. This bit determines the word length. It is set or

cleared by software. 0: 1 Start bit, 8 Data bits, 1 Stop bit

1: 1 Start bit, 9 Data bits, 1 Stop bit

Note: The M bit must not be modified during a data transfer (both transmission and reception).

#### Bit 3 = WAKE Wake-Up method.

This bit determines the SCI Wake-Up method, it is set or cleared by software. 0: Idle Line

1: Address Mark

### Bit 2 = **PCE** Parity control enable.

This bit selects the hardware parity control (generation and detection). When the parity control is enabled, the computed parity is inserted at the MSB position (9th bit if M = 1; 8th bit if M = 0) and parity is checked on the received data. This bit is set and cleared by software. Once it is set, PCE is active after the current byte (in reception and in transmission).

0: Parity control disabled

1: Parity control enabled

#### Bit 1 = **PS** Parity selection.

This bit selects the odd or even parity when the parity generation/detection is enabled (PCE bit set). It is set and cleared by software. The parity is selected after the current byte.

0: Even parity

1: Odd parity

#### Bit 0 = **PIE** Parity interrupt enable.

This bit enables the interrupt capability of the hardware parity control when a parity error is detected (PE bit set). It is set and cleared by software.

0: Parity error interrupt disabled

1: Parity error interrupt enabled.

## 10-BIT A/D CONVERTER (ADC) (Cont'd)

#### **10.6.3 Functional Description**

The conversion is monotonic, meaning that the result never decreases if the analog input does not and never increases if the analog input does not.

If the input voltage ( $V_{AIN}$ ) is greater than  $V_{AREF}$  (high-level voltage reference) then the conversion result is FFh in the ADCDRH register and 03h in the ADCDRL register (without overflow indication).

If the input voltage ( $V_{AIN}$ ) is lower than  $V_{SSA}$  (low-level voltage reference) then the conversion result in the ADCDRH and ADCDRL registers is 00 00h.

The A/D converter is linear and the digital result of the conversion is stored in the ADCDRH and AD-CDRL registers. The accuracy of the conversion is described in the Electrical Characteristics Section.

$R_{AIN}$  is the maximum recommended impedance for an analog input signal. If the impedance is too high, this will result in a loss of accuracy due to leakage and sampling not being completed in the alloted time.

#### 10.6.3.1 A/D Converter Configuration

The analog input ports must be configured as input, no pull-up, no interrupt. Refer to the «I/O ports» chapter. Using these pins as analog inputs does not affect the ability of the port to be read as a logic input.

In the ADCCSR register:

- Select the CS[3:0] bits to assign the analog channel to convert.

#### 10.6.3.2 Starting the Conversion

In the ADCCSR register:

Set the ADON bit to enable the A/D converter and to start the conversion. From this time on, the ADC performs a continuous conversion of the selected channel.

When a conversion is complete:

- The EOC bit is set by hardware.

- The result is in the ADCDR registers.

A read to the ADCDRH resets the EOC bit.

To read the 10 bits, perform the following steps:

- 1. Poll the EOC bit

- 2. Read the ADCDRL register

- 3. Read the ADCDRH register. This clears EOC automatically.

**Note:** The data is not latched, so both the low and the high data register must be read before the next conversion is complete, so it is recommended to disable interrupts while reading the conversion result.

To read only 8 bits, perform the following steps:

- 1. Poll the EOC bit

- 2. Read the ADCDRH register. This clears EOC automatically.

#### 10.6.3.3 Changing the conversion channel

The application can change channels during conversion. When software modifies the CH[3:0] bits in the ADCCSR register, the current conversion is stopped, the EOC bit is cleared, and the A/D converter starts converting the newly selected channel.

#### 10.6.4 Low Power Modes

**Note:** The A/D converter may be disabled by resetting the ADON bit. This feature allows reduced power consumption when no conversion is needed.

| Mode | Description                                                                                                                                                                               |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WAIT | No effect on A/D Converter                                                                                                                                                                |

|      | A/D Converter disabled.                                                                                                                                                                   |

| HALT | After wakeup from Halt mode, the A/D<br>Converter requires a stabilization time<br>t <sub>STAB</sub> (see Electrical Characteristics)<br>before accurate conversions can be<br>performed. |

#### 10.6.5 Interrupts

None.

## 10-BIT A/D CONVERTER (ADC) (Cont'd)

## **10.6.6 Register Description**

## **CONTROL/STATUS REGISTER (ADCCSR)**

Read/Write (Except bit 7 read only)

Reset Value: 0000 0000 (00h)

| 7   |       |      |   |     |     |     | 0   |

|-----|-------|------|---|-----|-----|-----|-----|

| EOC | SPEED | ADON | 0 | СНЗ | CH2 | CH1 | CH0 |

Bit 7 = **EOC** End of Conversion This bit is set by hardware. It is cleared by hardware when software reads the ADCDRH register or writes to any bit of the ADCCSR register. 0: Conversion is not complete 1: Conversion complete

Bit 6 = **SPEED** ADC clock selection This bit is set and cleared by software. 0:  $f_{ADC} = f_{CPU}/4$ 1:  $f_{ADC} = f_{CPU}/2$

Bit 5 = **ADON** *A/D Converter on* This bit is set and cleared by software. 0: Disable ADC and stop conversion 1: Enable ADC and start conversion

Bit 4 = **Reserved.** Must be kept cleared.

## Bit 3:0 = CH[3:0] Channel Selection

These bits are set and cleared by software. They select the analog input to convert.

| Channel Pin* | CH3 | CH2 | CH1 | CH0 |

|--------------|-----|-----|-----|-----|

| AINO         | 0   | 0   | 0   | 0   |

| AIN1         | 0   | 0   | 0   | 1   |

| AIN2         | 0   | 0   | 1   | 0   |

| AIN3         | 0   | 0   | 1   | 1   |

| AIN4         | 0   | 1   | 0   | 0   |

| AIN5         | 0   | 1   | 0   | 1   |

| AIN6         | 0   | 1   | 1   | 0   |

| AIN7         | 0   | 1   | 1   | 1   |

| AIN8         | 1   | 0   | 0   | 0   |

| AIN9         | 1   | 0   | 0   | 1   |

| AIN10        | 1   | 0   | 1   | 0   |

| AIN11        | 1   | 0   | 1   | 1   |

| AIN12        | 1   | 1   | 0   | 0   |

| AIN13        | 1   | 1   | 0   | 1   |

| AIN14        | 1   | 1   | 1   | 0   |

| AIN15        | 1   | 1   | 1   | 1   |

\*The number of channels is device dependent. Refer to the device pinout description.

## DATA REGISTER (ADCDRH)

Read Only Reset Value: 0000 0000 (00h)

7

|    |    | l. | l. | l. | r. | r. | r. |

|----|----|----|----|----|----|----|----|

|    |    |    |    |    |    |    |    |

| D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 |

|    |    |    |    |    |    |    |    |

0

Bit 7:0 = D[9:2] MSB of Converted Analog Value

## DATA REGISTER (ADCDRL)

Read Only Reset Value: 0000 0000 (00h)

| 7 |   |   |   |   |   |    | 0  |

|---|---|---|---|---|---|----|----|

| 0 | 0 | 0 | 0 | 0 | 0 | D1 | D0 |

Bit 7:2 = Reserved. Forced by hardware to 0.

Bit 1:0 = **D**[1:0] *LSB of Converted Analog Value*

## 10-BIT A/D CONVERTER (Cont'd)

57

| Address<br>(Hex.) | Register<br>Label     | 7        | 6          | 5         | 4       | 3        | 2        | 1        | 0        |

|-------------------|-----------------------|----------|------------|-----------|---------|----------|----------|----------|----------|

| 0070h             | ADCCSR<br>Reset Value | EOC<br>0 | SPEED<br>0 | ADON<br>0 | 0       | CH3<br>0 | CH2<br>0 | CH1<br>0 | CH0<br>0 |

| 0071h             | ADCDRH<br>Reset Value | D9<br>0  | D8<br>0    | D7<br>0   | D6<br>0 | D5<br>0  | D4<br>0  | D3<br>0  | D2<br>0  |

| 0072h             | ADCDRL<br>Reset Value | 0        | 0          | 0         | 0       | 0        | 0        | D1<br>0  | D0<br>0  |

## INSTRUCTION SET OVERVIEW (Cont'd)

### **11.2 INSTRUCTION GROUPS**

The ST7 family devices use an Instruction Set consisting of 63 instructions. The instructions may

be subdivided into 13 main groups as illustrated in the following table:

| Load and Transfer                | LD   | CLR  |      |      |      |       |     |     |

|----------------------------------|------|------|------|------|------|-------|-----|-----|

| Stack operation                  | PUSH | POP  | RSP  |      |      |       |     |     |

| Increment/Decrement              | INC  | DEC  |      |      |      |       |     |     |

| Compare and Tests                | CP   | TNZ  | BCP  |      |      |       |     |     |

| Logical operations               | AND  | OR   | XOR  | CPL  | NEG  |       |     |     |

| Bit Operation                    | BSET | BRES |      |      |      |       |     |     |

| Conditional Bit Test and Branch  | BTJT | BTJF |      |      |      |       |     |     |

| Arithmetic operations            | ADC  | ADD  | SUB  | SBC  | MUL  |       |     |     |

| Shift and Rotates                | SLL  | SRL  | SRA  | RLC  | RRC  | SWAP  | SLA |     |

| Unconditional Jump or Call       | JRA  | JRT  | JRF  | JP   | CALL | CALLR | NOP | RET |

| Conditional Branch               | JRxx |      |      |      |      |       |     |     |

| Interruption management          | TRAP | WFI  | HALT | IRET |      |       |     |     |

| Condition Code Flag modification | SIM  | RIM  | SCF  | RCF  |      |       |     |     |

#### Using a prebyte

The instructions are described with one to four opcodes.

In order to extend the number of available opcodes for an 8-bit CPU (256 opcodes), three different prebyte opcodes are defined. These prebytes modify the meaning of the instruction they precede.

The whole instruction becomes:

- PC-2 End of previous instruction

- PC-1 Prebyte

- PC Opcode

5/

PC+1 Additional word (0 to 2) according to the number of bytes required to compute the effective address These prebytes enable instruction in Y as well as indirect addressing modes to be implemented. They precede the opcode of the instruction in X or the instruction using direct addressing mode. The prebytes are:

PDY 90 Replace an X based instruction using immediate, direct, indexed, or inherent addressing mode by a Y one.

PIX 92 Replace an instruction using direct, direct bit, or direct relative addressing mode to an instruction using the corresponding indirect addressing mode.

It also changes an instruction using X indexed addressing mode to an instruction using indirect X indexed addressing mode.

PIY 91 Replace an instruction using X indirect indexed addressing mode by a Y one.

## **12.5 CLOCK AND TIMING CHARACTERISTICS**

Subject to general operating conditions for  $V_{DD}$ ,  $f_{CPU}$ , and  $T_A$ .

## 12.5.1 General Timings

| Symbol               | Parameter                             | Conditions             | Min  | <b>Typ</b> <sup>1)</sup> | Max  | Unit             |

|----------------------|---------------------------------------|------------------------|------|--------------------------|------|------------------|

| +                    | Instruction cycle time                |                        | 2    | 3                        | 12   | t <sub>CPU</sub> |

| <sup>L</sup> c(INST) |                                       | f <sub>CPU</sub> =8MHz | 250  | 375                      | 1500 | ns               |

| +                    | Interrupt reaction time 2)            |                        | 10   |                          | 22   | t <sub>CPU</sub> |

| τ <sub>v(IT)</sub>   | $t_{v(IT)} = \Delta t_{c(INST)} + 10$ | f <sub>CPU</sub> =8MHz | 1.25 |                          | 2.75 | μs               |

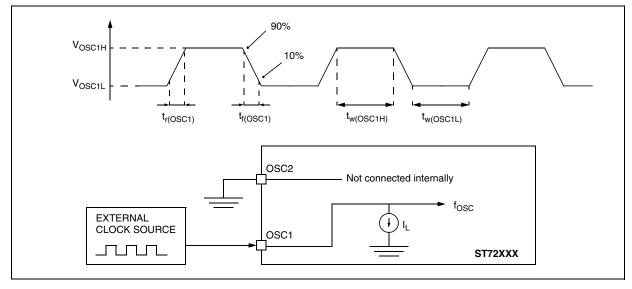

### 12.5.2 External Clock Source

| Symbol                                         | Parameter                            | Conditions                       | Min                 | Тур | Max                             | Unit |

|------------------------------------------------|--------------------------------------|----------------------------------|---------------------|-----|---------------------------------|------|

| V <sub>OSC1H</sub>                             | OSC1 input pin high level voltage    |                                  | 0.9xV <sub>DD</sub> |     | V <sub>DD</sub>                 | V    |

| V <sub>OSC1L</sub>                             | OSC1 input pin low level voltage     |                                  | V <sub>SS</sub>     |     | $0.1 \mathrm{xV}_{\mathrm{DD}}$ | v    |

| t <sub>w(OSC1H)</sub><br>t <sub>w(OSC1L)</sub> | OSC1 high or low time <sup>3)</sup>  | see Figure 62                    | 5                   |     |                                 | ns   |

| t <sub>r(OSC1)</sub><br>t <sub>f(OSC1)</sub>   | OSC1 rise or fall time <sup>3)</sup> |                                  |                     |     | 15                              | 15   |

| ١L                                             | OSC1 Input leakage current           | $V_{SS} \leq V_{IN} \leq V_{DD}$ |                     |     | ±1                              | μA   |

## Figure 62. Typical Application with an External Clock Source

#### Notes:

1. Data based on typical application software.

2. Time measured between interrupt event and interrupt vector fetch.  $\Delta t_{c(INST)}$  is the number of  $t_{CPU}$  cycles needed to finish the current instruction execution.

3. Data based on design simulation and/or technology characteristics, not tested in production.

## CLOCK AND TIMING CHARACTERISTICS (Cont'd)

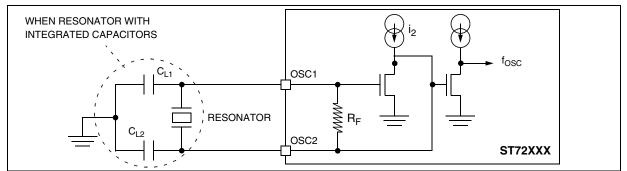

## 12.5.3 Crystal and Ceramic Resonator Oscillators

The ST7 internal clock can be supplied with four different Crystal/Ceramic resonator oscillators. All the information given in this paragraph are based on characterization results with specified typical external components. In the application, the resonator and the load capacitors have to be placed as

close as possible to the oscillator pins in order to minimize output distortion and start-up stabilization time. Refer to the crystal/ceramic resonator manufacturer for more details (frequency, package, accuracy...).

| Symbol           | Parameter                                      | (                    | Conditions                               |          | Max | Unit |

|------------------|------------------------------------------------|----------------------|------------------------------------------|----------|-----|------|

|                  |                                                |                      | wer oscillator                           | 1        | 2   |      |

| f <sub>OSC</sub> | Oscillator Frequency 1)                        |                      | m power oscillator<br>m speed oscillator | >2<br>>4 | 4   | MHz  |

|                  |                                                | HS: High s           | peed oscillator                          | >8       | 16  |      |

| R <sub>F</sub>   | Feedback resistor                              |                      |                                          | 20       |     | kΩ   |

|                  | Recommended load capacitance ver-              | R <sub>S</sub> =200Ω | LP osc. (1-2 MHz)                        | 22       | 56  |      |

| C <sub>L1</sub>  | sus equivalent serial resistance of the        |                      | MP osc. (2-4 MHz)                        | 22       | 46  | pF   |

| C <sub>L2</sub>  | crystal or ceramic resonator (R <sub>S</sub> ) | R <sub>S</sub> =200Ω | MS osc. (4-8 MHz)                        | 18       | 33  | p    |

|                  |                                                | R <sub>S</sub> =100Ω | HS osc. (8-16 MHz)                       | 15       | 33  |      |

| Symbol         | Parameter            | Conditions                       |                    | Тур | Max | Unit |

|----------------|----------------------|----------------------------------|--------------------|-----|-----|------|

|                |                      | V <sub>IN</sub> =V <sub>SS</sub> | LP osc. (1-2 MHz)  | 80  | 150 |      |

|                | OSC2 driving current |                                  | MP osc. (2-4 MHz)  | 160 | 250 | ۸    |

| <sup>1</sup> 2 |                      |                                  | MS osc. (4-8 MHz)  | 310 | 460 | μA   |

|                |                      |                                  | HS osc. (8-16 MHz) | 610 | 910 |      |

## Figure 63. Typical Application with a Crystal or Ceramic Resonator

Notes:

1. The oscillator selection can be optimized in terms of supply current using an high quality resonator with small R<sub>S</sub> value. Refer to crystal/ceramic resonator manufacturer for more details.

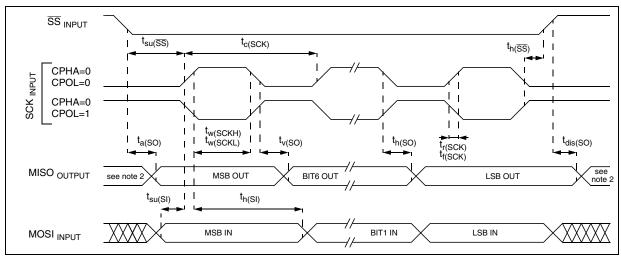

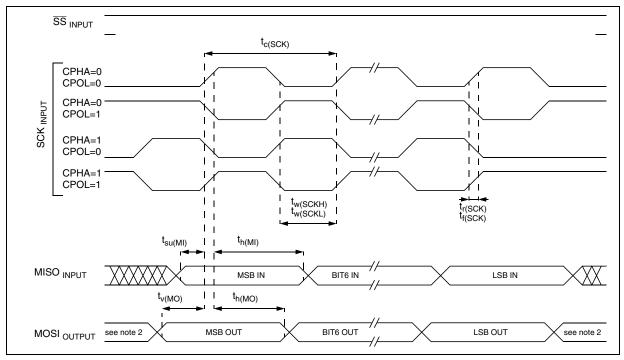

## **12.11 COMMUNICATION INTERFACE CHARACTERISTICS**

## 12.11.1 SPI - Serial Peripheral Interface

Subject to general operating conditions for  $V_{DD}, f_{CPU},$  and  $T_A$  unless otherwise specified.

Refer to I/O port characteristics for more details on the input/output alternate function characteristics (SS, SCK, MOSI, MISO).

| Symbol                                       | Parameter                    | Conditions                       | Min                             | Max                      | Unit             |

|----------------------------------------------|------------------------------|----------------------------------|---------------------------------|--------------------------|------------------|

| f <sub>scк</sub>                             | SPI clock frequency          | Master<br>f <sub>CPU</sub> =8MHz | f <sub>CPU</sub> /128<br>0.0625 | f <sub>CPU</sub> /4<br>2 | MHz              |

| 1/t <sub>c(SCK)</sub>                        |                              | Slave<br>f <sub>CPU</sub> =8MHz  | 0                               | f <sub>CPU</sub> /2<br>4 | IVITIZ           |

| t <sub>r(SCK)</sub><br>t <sub>f(SCK)</sub>   | SPI clock rise and fall time |                                  | see I/O p                       | oort pin de              | scription        |

| t <sub>su(SS)</sub>                          | SS setup time                | Slave                            | 120                             |                          |                  |

| t <sub>h(SS)</sub>                           | SS hold time                 | Slave                            | 120                             |                          |                  |

| t <sub>w(SCKH)</sub><br>t <sub>w(SCKL)</sub> | SCK high and low time        | Master<br>Slave                  | 100<br>90                       |                          |                  |

| t <sub>su(MI)</sub><br>t <sub>su(SI)</sub>   | Data input setup time        | Master<br>Slave                  | 100<br>100                      |                          |                  |

| t <sub>h(MI)</sub><br>t <sub>h(SI)</sub>     | Data input hold time         | Master<br>Slave                  | 100<br>100                      |                          | ns               |

| t <sub>a(SO)</sub>                           | Data output access time      | Slave                            | 0                               | 120                      |                  |

| t <sub>dis(SO)</sub>                         | Data output disable time     | Slave                            |                                 | 240                      |                  |

| t <sub>v(SO)</sub>                           | Data output valid time       | - Slave (after enable edge)      |                                 | 90                       |                  |

| t <sub>h(SO)</sub>                           | Data output hold time        | - Slave (allel ellable euge)     | 0                               |                          |                  |

| t <sub>v(MO)</sub>                           | Data output valid time       | – Master (before capture edge)   | 0.25                            |                          | tanu             |

| t <sub>h(MO)</sub>                           | Data output hold time        | masier (before capture edge)     | 0.25                            |                          | t <sub>CPU</sub> |

## Figure 75. SPI Slave Timing Diagram with CPHA=0<sup>3)</sup>

#### Notes:

1. Data based on design simulation and/or characterisation results, not tested in production.

2. When no communication is on-going the data output line of the SPI (MOSI in master mode, MISO in slave mode) has its alternate function capability released. In this case, the pin status depends on the I/O port configuration.

3. Measurement points are done at CMOS levels:  $0.3 x V_{\text{DD}}$  and  $0.7 x V_{\text{DD}}.$

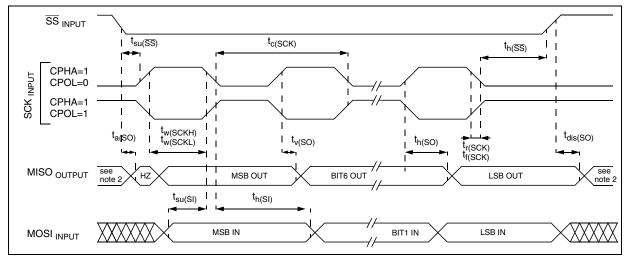

## COMMUNICATION INTERFACE CHARACTERISTICS (Cont'd)

### Figure 76. SPI Slave Timing Diagram with CPHA=1<sup>1)</sup>

## Figure 77. SPI Master Timing Diagram 1)

### Notes:

<u>ل</u>حک

1. Measurement points are done at CMOS levels:  $0.3 x V_{DD}$  and  $0.7 x V_{DD}.$

2. When no communication is on-going the data output line of the SPI (MOSI in master mode, MISO in slave mode) has its alternate function capability released. In this case, the pin status depends of the I/O port configuration.

# 14.3.4 Socket and Emulator Adapter Information

For information on the type of socket that is supplied with the emulator, refer to the suggested list of sockets in Table 29.

**Note:** Before designing the board layout, it is recommended to check the overall dimensions of the

#### Note:

1. Flash Programming interface for FLASH devices.

#### Table 29. Suggested List of Socket Types

socket as they may be greater than the dimensions of the device.

For footprint and other mechanical information about these sockets and adapters, refer to the manufacturer's datasheet (www.yamaichi.de for LQFP44 10 x 10 and www.ironwoodelectronics.com for LQFP32 7 x 7).

| Device        | Socket (supplied with<br>ST7MDT20J-EMU3) | Emulator Adapter (supplied with<br>ST7MDT20J-EMU3) |

|---------------|------------------------------------------|----------------------------------------------------|

| LQFP32 7 X 7  | IRONWOOD SF-QFE32SA-L-01                 | IRONWOOD SK-UGA06/32A-01                           |

| LQFP44 10 X10 | YAMAICHI IC149-044-*52-*5                | YAMAICHI ICP-044-5                                 |

| LQFP48 7 X7   | CAB 3303238                              | CAB 3303333                                        |

## **15 KNOWN LIMITATIONS**

## **15.1 ALL FLASH AND ROM DEVICES**

#### 15.1.1 Safe Connection of OSC1/OSC2 Pins

The OSC1 and/or OSC2 pins must not be left unconnected otherwise the ST7 main oscillator may start and, in this configuration, could generate an  $f_{OSC}$  clock frequency in excess of the allowed maximum (>16MHz.), putting the ST7 in an unsafe/undefined state. Refer to Section 6.2 on page 24.

#### 15.1.2 Unexpected Reset Fetch

If an interrupt request occurs while a "POP CC" instruction is executed, the interrupt controller does not recognise the source of the interrupt and, by default, passes the RESET vector address to the CPU.

#### Workaround

To solve this issue, a "POP CC" instruction must always be preceded by a "SIM" instruction.

# 15.1.3 Clearing active interrupts outside interrupt routine

When an active interrupt request occurs at the same time as the related flag is being cleared, an unwanted reset may occur.

**Note:** clearing the related interrupt mask will not generate an unwanted reset

#### Concurrent interrupt context

The symptom does not occur when the interrupts are handled normally, i.e.

when:

57

- The interrupt flag is cleared within its own interrupt routine

- The interrupt flag is cleared within any interrupt routine

- The interrupt flag is cleared in any part of the code while this interrupt is disabled

If these conditions are not met, the symptom can be avoided by implementing the following sequence:

Perform SIM and RIM operation before and after resetting an active interrupt request.

Example:

SIM

reset interrupt flag

RIM

#### Nested interrupt context:

The symptom does not occur when the interrupts are handled normally, i.e.

when:

- The interrupt flag is cleared within its own interrupt routine

- The interrupt flag is cleared within any interrupt routine with higher or identical priority level

- The interrupt flag is cleared in any part of the code while this interrupt is disabled

If these conditions are not met, the symptom can be avoided by implementing the following sequence:

PUSH CC

SIM

reset interrupt flag POP CC

#### 15.1.4 16-bit Timer PWM Mode

In PWM mode, the first PWM pulse is missed after writing the value FFFCh in the OC1R register (OC1HR, OC1LR). It leads to either full or no PWM during a period, depending on the OLVL1 and OLVL2 settings.

#### **15.1.5 ADC Conversion Spurious Results**

Spurious conversions occur with a rate lower than 50 per million. Such conversions happen when the measured voltage is just between 2 consecutive digital values.

#### Workaround

A software filter should be implemented to remove erratic conversion results whenever they may cause unwanted consequences.

In order to have the accuracy specified in the datasheet, the first conversion after a ADC switch-on has to be ignored.

## **16 REVISION HISTORY**

## Table 31. Revision History

57

| Date         | Revision | Description of Changes                                                                              |

|--------------|----------|-----------------------------------------------------------------------------------------------------|

| 01-Oct-2003  | 1.0      | First release.                                                                                      |

|              |          | Changed Flash & ROM voltage range 2.85 to 3.6V in Section 12.3 on page 112                          |

|              |          | Changed OSC1 high & low level in Section 12.5.1 on page 116                                         |

|              |          | Updated "EMC CHARACTERISTICS" on page 121                                                           |

| 01-Jan-2004  | 1.1      | Changed I/O Port: V <sub>OL</sub> /V <sub>OH</sub> values in Section 12.8.2 on page 125.            |

| 01-5411-2004 | 1.1      | Changed Reset pin: tw(RSTL)out & VOL in Section 12.9.1 on page 127.                                 |

|              |          | Changed ADC Varef & Ilkg in Section 12.12 on page 132 and ADC accuracy Section 12.12.3 on page 135. |

|              |          | Removed SDIP42 package                                                                              |

|              |          | Max. values TBD in Section 12.12.3 on page 135                                                      |

| 01-Feb-2004  | 1.2      | Removed 10pf cap. in Figure 81 on page 134                                                          |

|              |          | Added Section 15.1.5 on page 149                                                                    |

|              |          | Revision number incremented from 1.2 to 3 due to Internal Document Management System change         |

|              |          | Modified I/O V <sub>IL</sub> in Section 12.8 on page 124                                            |

| 14-Jan-2005  | 3        | Modified R <sub>ON</sub> in Section 12.9.1 on page 127                                              |

|              |          | Added Clearing active interrupts in Section 15.1.3 on page 149                                      |

|              |          | Modified Figure 8 and note 4 in "FLASH PROGRAM MEMORY" on page 17                                   |

|              |          | Added limitation on ICC entry mode with 39 pulses to "KNOWN LIMITATIONS" on page 149                |

| 05-Mar-2007  | 4        | Added LQFP48 package devices.                                                                       |

| 12-Sep-2007  | 5        | Added footnote 5 to Table 2 on page 10                                                              |

| 12-06p-2007  | 5        | Updated LQFP48 device ordering information in Table 27 on page 143.                                 |