#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                              |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ST7                                                                   |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 8MHz                                                                  |

| Connectivity               | SCI, SPI                                                              |

| Peripherals                | POR, PWM, WDT                                                         |

| Number of I/O              | 24                                                                    |

| Program Memory Size        | 8KB (8K x 8)                                                          |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 384 x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 2.85V ~ 3.6V                                                          |

| Data Converters            | A/D 8x10b                                                             |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 32-LQFP                                                               |

| Supplier Device Package    | -                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st72f324lk2t6 |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **2 PIN DESCRIPTION**

57

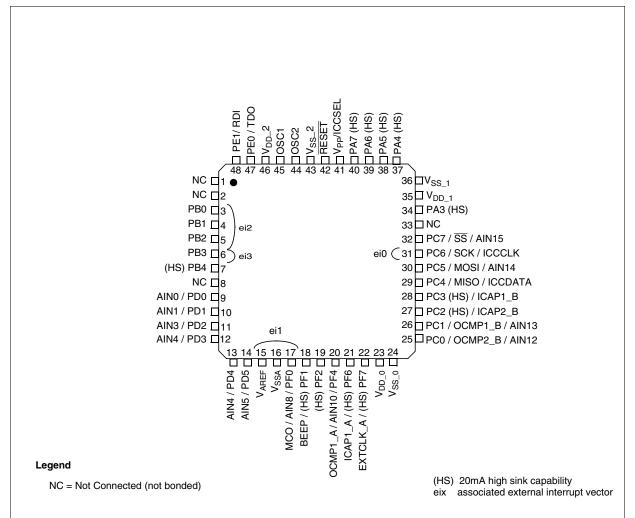

## Figure 2. 48-Pin LQFP 7x7 Device Pinout

| Address                                                                                                                                      | Block   | Register<br>Label                                                                                                                                              | Register Name                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Reset<br>Status                                                                                       | Remarks                                                                                                                                                                                                                                        |

|----------------------------------------------------------------------------------------------------------------------------------------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0031h<br>0032h<br>0033h<br>0034h<br>0035h<br>0036h<br>0037h<br>0038h<br>0039h<br>003Ah<br>003Ah<br>003Bh<br>003Ch<br>003Dh<br>003Eh<br>003Fh | TIMER A | TACR2<br>TACR1<br>TACSR<br>TAIC1HR<br>TAIC1LR<br>TAOC1HR<br>TAOC1LR<br>TACHR<br>TACHR<br>TACLR<br>TAACHR<br>TAACLR<br>TAIC2HR<br>TAIC2LR<br>TAIC2LR<br>TAOC2LR | Timer A Control Register 2<br>Timer A Control Register 1<br>Timer A Control/Status Register <sup>3)4)</sup><br>Timer A Input Capture 1 High Register<br>Timer A Input Capture 1 Low Register<br>Timer A Output Compare 1 High Register<br>Timer A Output Compare 1 Low Register<br>Timer A Counter High Register<br>Timer A Counter Low Register<br>Timer A Alternate Counter High Register<br>Timer A Alternate Counter Low Register<br>Timer A Input Capture 2 High Register <sup>3)</sup><br>Timer A Input Capture 2 Low Register <sup>4)</sup><br>Timer A Output Compare 2 Low Register <sup>4)</sup> | 00h<br>00h<br>xxxx x0xxb<br>xxh<br>80h<br>00h<br>FFh<br>FCh<br>FCh<br>FCh<br>xxh<br>xxh<br>80h<br>00h | R/W<br>R/W<br>Read Only<br>Read Only<br>R/W<br>Read Only<br>Read Only |

| 0040h                                                                                                                                        |         | 4                                                                                                                                                              | Reserved Area (1 Byte)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                       |                                                                                                                                                                                                                                                |

| 0041h<br>0042h<br>0043h<br>0044h<br>0045h<br>0046h<br>0047h<br>0048h<br>0049h<br>004Ah<br>004Bh<br>004Ch<br>004Ch<br>004Ch<br>004Fh          | TIMER B | TBCR2<br>TBCR1<br>TBCSR<br>TBIC1HR<br>TBIC1LR<br>TBOC1HR<br>TBOC1LR<br>TBCHR<br>TBCLR<br>TBACHR<br>TBACLR<br>TBIC2HR<br>TBIC2LR<br>TBIC2LR                     | Timer B Control Register 2<br>Timer B Control Register 1<br>Timer B Control/Status Register<br>Timer B Input Capture 1 High Register<br>Timer B Input Capture 1 Low Register<br>Timer B Output Compare 1 High Register<br>Timer B Output Compare 1 Low Register<br>Timer B Counter High Register<br>Timer B Counter High Register<br>Timer B Alternate Counter High Register<br>Timer B Alternate Counter Low Register<br>Timer B Input Capture 2 High Register<br>Timer B Input Capture 2 Low Register<br>Timer B Output Compare 2 High Register<br>Timer B Output Compare 2 Low Register                | 00h<br>00h<br>xxxx x0xxb<br>xxh<br>80h<br>00h<br>FFh<br>FCh<br>FCh<br>FCh<br>xxh<br>xxh<br>80h<br>00h | R/W<br>R/W<br>Read Only<br>Read Only<br>R/W<br>R/W<br>Read Only<br>Read Only<br>Read Only<br>Read Only<br>Read Only<br>Read Only<br>Read Only<br>Read Only<br>Read Only<br>Read Only<br>R/W                                                    |

| 0050h<br>0051h<br>0052h<br>0053h<br>0054h<br>0055h<br>0056h<br>0057h                                                                         | SCI     | SCISR<br>SCIDR<br>SCIBRR<br>SCICR1<br>SCICR2<br>SCIERPR<br>SCIETPR                                                                                             | SCI Status Register<br>SCI Data Register<br>SCI Baud Rate Register<br>SCI Control Register 1<br>SCI Control Register 2<br>SCI Extended Receive Prescaler Register<br>Reserved area<br>SCI Extended Transmit Prescaler Register                                                                                                                                                                                                                                                                                                                                                                            | C0h<br>xxh<br>00h<br>x000 0000h<br>00h<br><br>00h                                                     | Read Only<br>R/W<br>R/W<br>R/W<br>R/W<br>R/W                                                                                                                                                                                                   |

| 0058h<br>to<br>006Fh                                                                                                                         |         |                                                                                                                                                                | Reserved Area (24 Bytes)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                       |                                                                                                                                                                                                                                                |

| 0070h<br>0071h<br>0072h                                                                                                                      | ADC     | ADCCSR<br>ADCDRH<br>ADCDRL                                                                                                                                     | Control/Status Register<br>Data High Register<br>Data Low Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 00h<br>00h<br>00h                                                                                     | R/W<br>Read Only<br>Read Only                                                                                                                                                                                                                  |

| 0073h<br>007Fh                                                                                                                               |         |                                                                                                                                                                | Reserved Area (13 Bytes)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                       |                                                                                                                                                                                                                                                |

57

## FLASH PROGRAM MEMORY (Cont'd)

## 4.5 ICP (In-Circuit Programming)

To perform ICP the microcontroller must be switched to ICC (In-Circuit Communication) mode by an external controller or programming tool using 36-pulse mode.

Depending on the ICP code downloaded in RAM, Flash memory programming can be fully customized (number of bytes to program, program locations, or selection serial communication interface for downloading).

When using an STMicroelectronics or third-party programming tool that supports ICP and the specific microcontroller device, the user needs only to implement the ICP hardware interface on the application board (see Figure 8). For more details on the pin locations, refer to the device pinout description.

## 4.6 IAP (In-Application Programming)

57/

This mode uses a BootLoader program previously stored in Sector 0 by the user (in ICP mode or by plugging the device in a programming tool).

This mode is fully controlled by user software. This allows it to be adapted to the user application, (user-defined strategy for entering programming mode, choice of communications protocol used to fetch the data to be stored, etc.). For example, it is possible to download code from the SPI, SCI, USB or CAN interface and program it in the Flash. IAP mode can be used to program any of the Flash sectors except Sector 0, which is write/erase protected to allow recovery in case errors occur during the programming operation.

### 4.7 Related Documentation

For details on Flash programming and ICC protocol, refer to the ST7 Flash Programming Reference Manual and to the ST7 ICC Protocol Reference Manual.

# 4.7.1 Register Description FLASH CONTROL/STATUS REGISTER (FCSR)

Read/Write

Reset Value: 0000 0000 (00h)

| 7 |   |   |   |   |   |   | 0 |

|---|---|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

This register is reserved for use by Programming Tool software. It controls the Flash programming and erasing operations.

## Table 5. Flash Control/Status Register Address and Reset Value

| Address<br>(Hex.) | Register<br>Label   | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------------------|---------------------|---|---|---|---|---|---|---|---|

| 0029h             | FCSR<br>Reset Value | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

## INTERRUPTS (Cont'd)

## 7.5 INTERRUPT REGISTER DESCRIPTION

## **CPU CC REGISTER INTERRUPT BITS**

Read/Write

Reset Value: 111x 1010 (xAh)

| 7 |   |    |   |    |   |   | 0 |

|---|---|----|---|----|---|---|---|

| 1 | 1 | 11 | н | 10 | Ν | z | С |

Bit 5, 3 = 11, 10 Software Interrupt Priority

These two bits indicate the current interrupt software priority.

| Interrupt Software Priority    | Level | l1 | 10 |

|--------------------------------|-------|----|----|

| Level 0 (main)                 | Low   | 1  | 0  |

| Level 1                        |       | 0  | 1  |

| Level 2                        | ★     | 0  | 0  |

| Level 3 (= interrupt disable*) | High  | 1  | 1  |

These two bits are set/cleared by hardware when entering in interrupt. The loaded value is given by the corresponding bits in the interrupt software priority registers (ISPRx).

They can be also set/cleared by software with the RIM, SIM, HALT, WFI, IRET and PUSH/POP instructions (see "Interrupt Dedicated Instruction Set" table).

\*Note: TRAP and RESET events can interrupt a level 3 program.

# INTERRUPT SOFTWARE PRIORITY REGISTERS (ISPRX)

Read/Write (bit 7:4 of **ISPR3** are read only) Reset Value: 1111 1111 (FFh)

|       | 7     |       |       |       |       |       |       | 0     |

|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| ISPR0 | l1_3  | 10_3  | l1_2  | 10_2  | 11_1  | 10_1  | l1_0  | 10_0  |

| ISPR1 | 11_7  | 10_7  | l1_6  | 10_6  | l1_5  | 10_5  | 11_4  | 10_4  |

| ISPR2 | 11_11 | 10_11 | 11_10 | 10_10 | l1_9  | 10_9  | l1_8  | 10_8  |

| ISPR3 | 1     | 1     | 1     | 1     | 11_13 | 10_13 | 11_12 | 10_12 |

These four registers contain the interrupt software priority of each interrupt vector.

Each interrupt vector (except RESET and TRAP) has corresponding bits in these registers where its own software priority is stored. This correspondance is shown in the following table.

| Vector address | ISPRx bits           |

|----------------|----------------------|

| FFFBh-FFFAh    | I1_0 and I0_0 bits*  |

| FFF9h-FFF8h    | I1_1 and I0_1 bits   |

|                |                      |

| FFE1h-FFE0h    | I1_13 and I0_13 bits |

Each I1\_x and I0\_x bit value in the ISPRx registers has the same meaning as the I1 and I0 bits in the CC register.

Level 0 can not be written (l1\_x=1, l0\_x=0). In this case, the previously stored value is kept. (example: previous=CFh, write=64h, result=44h)

The RESET, and TRAP vectors have no software priorities. When one is serviced, the I1 and I0 bits of the CC register are both set.

**Caution**: If the  $I1_x$  and  $I0_x$  bits are modified while the interrupt x is executed the following behaviour has to be considered: If the interrupt x is still pending (new interrupt or flag not cleared) and the new software priority is higher than the previous one, the interrupt x is re-entered. Otherwise, the software priority stays unchanged up to the next interrupt request (after the IRET of the interrupt x).

## POWER SAVING MODES (Cont'd)

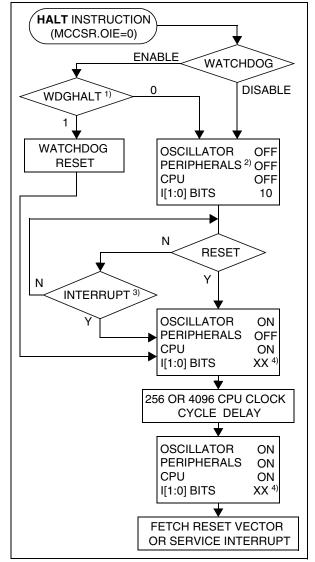

## 8.4.2 HALT MODE

The HALT mode is the lowest power consumption mode of the MCU. It is entered by executing the 'HALT' instruction when the OIE bit of the Main Clock Controller Status register (MCCSR) is cleared (see Section 10.2 on page 50 for more details on the MCCSR register).

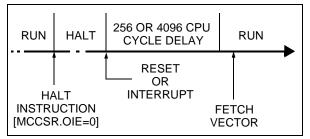

The MCU can exit HALT mode on reception of either a specific interrupt (see Table 9, "Interrupt Mapping," on page 31) or a RESET. When exiting HALT mode by means of a RESET or an interrupt, the oscillator is immediately turned on and the 256 or 4096 CPU cycle delay is used to stabilize the oscillator. After the start up delay, the CPU resumes operation by servicing the interrupt or by fetching the reset vector which woke it up (see Figure 25).

When entering HALT mode, the I[1:0] bits in the CC register are forced to '10b'to enable interrupts. Therefore, if an interrupt is pending, the MCU wakes up immediately.

In HALT mode, the main oscillator is turned off causing all internal processing to be stopped, including the operation of the on-chip peripherals. All peripherals are not clocked except the ones which get their clock supply from another clock generator (such as an external or auxiliary oscillator).

The compatibility of Watchdog operation with HALT mode is configured by the "WDGHALT" option bit of the option byte. The HALT instruction when executed while the Watchdog system is enabled, can generate a Watchdog RESET (see Section 14.1 on page 140 for more details).

## Notes:

1. WDGHALT is an option bit. See option byte section for more details.

2. Peripheral clocked with an external clock source can still be active.

3. Only some specific interrupts can exit the MCU from HALT mode (such as external interrupt). Refer to Table 9, "Interrupt Mapping," on page 31 for more details.

4. Before servicing an interrupt, the CC register is pushed on the stack. The I[1:0] bits of the CC register are set to the current software priority level of the interrupt routine and recovered when the CC register is popped.

## Figure 25. HALT Mode Flow-chart

## 16-BIT TIMER (Cont'd)

### 10.3.3.3 Input Capture

In this section, the index, *i*, may be 1 or 2 because there are 2 input capture functions in the 16-bit timer.

The two 16-bit input capture registers (IC1R and IC2R) are used to latch the value of the free running counter after a transition is detected on the ICAP*i* pin (see figure 5).

|      | MS Byte        | LS Byte        |

|------|----------------|----------------|

| ICiR | IC <i>i</i> HR | IC <i>i</i> LR |

ICiR register is a read-only register.

The active transition is software programmable through the IEDG*i* bit of Control Registers (CR*i*).

Timing resolution is one count of the free running counter:  $(f_{CPU}/CC[1:0])$ .

### **Procedure:**

To use the input capture function select the following in the CR2 register:

- Select the timer clock (CC[1:0]) (see Table 17 Clock Control Bits).

- Select the edge of the active transition on the ICAP2 pin with the IEDG2 bit (the ICAP2 pin must be configured as floating input or input with pull-up without interrupt if this configuration is available).

And select the following in the CR1 register:

- Set the ICIE bit to generate an interrupt after an input capture coming from either the ICAP1 pin or the ICAP2 pin

- Select the edge of the active transition on the ICAP1 pin with the IEDG1 bit (the ICAP1pin must be configured as floating input or input with pullup without interrupt if this configuration is available).

When an input capture occurs:

- ICF*i* bit is set.

- The IC*i*R register contains the value of the free running counter on the active transition on the ICAP*i* pin (see Figure 37).

- A timer interrupt is generated if the ICIE bit is set and the I bit is cleared in the CC register. Otherwise, the interrupt remains pending until both conditions become true.

Clearing the Input Capture interrupt request (i.e. clearing the ICF*i* bit) is done in two steps:

- 1. Reading the SR register while the ICF*i* bit is set.

- 2. An access (read or write) to the ICiLR register.

#### Notes:

- 1. After reading the IC*i*HR register, transfer of input capture data is inhibited and ICF*i* will never be set until the IC*i*LR register is also read.

- 2. The IC*i*R register contains the free running counter value which corresponds to the most recent input capture.

- 3. The 2 input capture functions can be used together even if the timer also uses the 2 output compare functions.

- 4. In One pulse Mode and PWM mode only Input Capture 2 can be used.

- 5. The alternate inputs (ICAP1 & ICAP2) are always directly connected to the timer. So any transitions on these pins activates the input capture function. Moreover if one of the ICAP*i* pins is configured as an input and the second one as an output, an interrupt can be generated if the user toggles the output pin and if the ICIE bit is set. This can be avoided if the input capture function *i* is disabled by reading the IC*i*HR (see note 1).

- 6. The TOF bit can be used with interrupt generation in order to measure events that go beyond the timer range (FFFFh).

- 7. In Flash devices, the ICAP2 registers (TAIC2HR, TAIC2LR) are not available on Timer A. The corresponding interrupts cannot be used (ICF2 is forced by hardware to 0).

## **16-BIT TIMER** (Cont'd)

## 10.3.3.4 Output Compare

In this section, the index, *i*, may be 1 or 2 because there are 2 output compare functions in the 16-bit timer.

This function can be used to control an output waveform or indicate when a period of time has elapsed.

When a match is found between the Output Compare register and the free running counter, the output compare function:

- Assigns pins with a programmable value if the OCiE bit is set

- Sets a flag in the status register

- Generates an interrupt if enabled

Two 16-bit registers Output Compare Register 1 (OC1R) and Output Compare Register 2 (OC2R) contain the value to be compared to the counter register each timer clock cycle.

|               | MS Byte        | LS Byte        |

|---------------|----------------|----------------|

| OC <i>i</i> R | OC <i>i</i> HR | OC <i>i</i> LR |

These registers are readable and writable and are not affected by the timer hardware. A reset event changes the OC*i*R value to 8000h.

Timing resolution is one count of the free running counter:  $(f_{CPU/CC[1:0]})$ .

## **Procedure:**

To use the output compare function, select the following in the CR2 register:

- Set the OC*i*E bit if an output is needed then the OCMP*i* pin is dedicated to the output compare *i* signal.

- Select the timer clock (CC[1:0]) (see Table 17 Clock Control Bits).

And select the following in the CR1 register:

- Select the OLVL*i* bit to applied to the OCMP*i* pins after the match occurs.

- Set the OCIE bit to generate an interrupt if it is needed.

When a match is found between OCRi register and CR register:

- OCF*i* bit is set.

- The OCMP*i* pin takes OLVL*i* bit value (OCMP*i* pin latch is forced low during reset).

- A timer interrupt is generated if the OCIE bit is set in the CR1 register and the I bit is cleared in the CC register (CC).

The OC*i*R register value required for a specific timing application can be calculated using the following formula:

$$\Delta \operatorname{OC}_{iR} = \frac{\Delta t * f_{CPU}}{PRESC}$$

Where:

- $\Delta t$  = Output compare period (in seconds)

- f<sub>CPU</sub> = CPU clock frequency (in hertz)

- PRESC = Timer prescaler factor (2, 4 or 8 depending on CC[1:0] bits, see Table 17 Clock Control Bits)

If the timer clock is an external clock, the formula is:

$$\Delta \text{ OC} i \text{R} = \Delta t * f_{\text{EXT}}$$

Where:

$\Delta t$  = Output compare period (in seconds)

f<sub>EXT</sub> = External timer clock frequency (in hertz)

Clearing the output compare interrupt request (i.e. clearing the OCF*i* bit) is done by:

- 1. Reading the SR register while the OCF*i* bit is set.

- 2. An access (read or write) to the OCiLR register.

The following procedure is recommended to prevent the OCF*i* bit from being set between the time it is read and the write to the OC*i*R register:

- Write to the OC*i*HR register (further compares are inhibited).

- Read the SR register (first step of the clearance of the OCF*i* bit, which may be already set).

- Write to the OC*i*LR register (enables the output compare function and clears the OCF*i* bit).

## 16-BIT TIMER (Cont'd)

## **10.3.7 Register Description**

Each Timer is associated with three control and status registers, and with six pairs of data registers (16-bit values) relating to the two input captures, the two output compares, the counter and the alternate counter.

## **CONTROL REGISTER 1 (CR1)**

#### Read/Write

Reset Value: 0000 0000 (00h)

| 7    |      |      |       |       |       |       | 0     |

|------|------|------|-------|-------|-------|-------|-------|

| ICIE | OCIE | TOIE | FOLV2 | FOLV1 | OLVL2 | IEDG1 | OLVL1 |

Bit 7 = ICIE Input Capture Interrupt Enable.

- 0: Interrupt is inhibited.

- 1: A timer interrupt is generated whenever the ICF1 or ICF2 bit of the SR register is set.

Bit 6 = **OCIE** *Output Compare Interrupt Enable.* 0: Interrupt is inhibited.

1: A timer interrupt is generated whenever the OCF1 or OCF2 bit of the SR register is set.

Bit 5 = **TOIE** *Timer Overflow Interrupt Enable.*

0: Interrupt is inhibited.

1: A timer interrupt is enabled whenever the TOF bit of the SR register is set.

## Bit 4 = FOLV2 Forced Output Compare 2.

This bit is set and cleared by software.

- 0: No effect on the OCMP2 pin.

- 1: Forces the OLVL2 bit to be copied to the OCMP2 pin, if the OC2E bit is set and even if there is no successful comparison.

## Bit 3 = FOLV1 Forced Output Compare 1.

This bit is set and cleared by software.

- 0: No effect on the OCMP1 pin.

- 1: Forces OLVL1 to be copied to the OCMP1 pin, if the OC1E bit is set and even if there is no successful comparison.

### Bit 2 = OLVL2 Output Level 2.

This bit is copied to the OCMP2 pin whenever a successful comparison occurs with the OC2R register and OCxE is set in the CR2 register. This value is copied to the OCMP1 pin in One Pulse Mode and Pulse Width Modulation mode.

### Bit 1 = IEDG1 Input Edge 1.

This bit determines which type of level transition on the ICAP1 pin will trigger the capture.

0: A falling edge triggers the capture.

1: A rising edge triggers the capture.

## Bit 0 = **OLVL1** *Output Level 1.*

The OLVL1 bit is copied to the OCMP1 pin whenever a successful comparison occurs with the OC1R register and the OC1E bit is set in the CR2 register.

## **10.4 SERIAL PERIPHERAL INTERFACE (SPI)**

## 10.4.1 Introduction

The Serial Peripheral Interface (SPI) allows fullduplex, synchronous, serial communication with external devices. An SPI system may consist of a master and one or more slaves however the SPI interface can not be a master in a multi-master system.

## 10.4.2 Main Features

- Full duplex synchronous transfers (on 3 lines)

- Simplex synchronous transfers (on 2 lines)

- Master or slave operation

- Six master mode frequencies (f<sub>CPU</sub>/4 max.)

- f<sub>CPU</sub>/2 max. slave mode frequency (see note)

- SS Management by software or hardware

- Programmable clock polarity and phase

- End of transfer interrupt flag

57

Write collision, Master Mode Fault and Overrun flags

Note: In slave mode, continuous transmission is not possible at maximum frequency due to the

software overhead for clearing status flags and to initiate the next transmission sequence.

## **10.4.3 General Description**

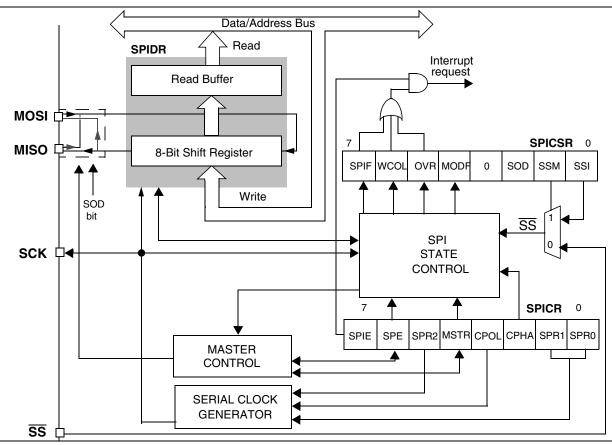

Figure 43 shows the serial peripheral interface (SPI) block diagram. There are 3 registers:

- SPI Control Register (SPICR)

- SPI Control/Status Register (SPICSR)

- SPI Data Register (SPIDR)

The SPI is connected to external devices through 3 pins:

- MISO: Master In / Slave Out data

- MOSI: Master Out / Slave In data

- SCK: Serial Clock out by SPI masters and input by SPI slaves

- SS: Slave select:

This input signal acts as a 'chip select' to let the SPI master communicate with slaves individually and to avoid contention on the data lines. Slave SS inputs can be driven by standard I/O ports on the master MCU.

## SERIAL PERIPHERAL INTERFACE (Cont'd)

## 10.4.3.2 Slave Select Management

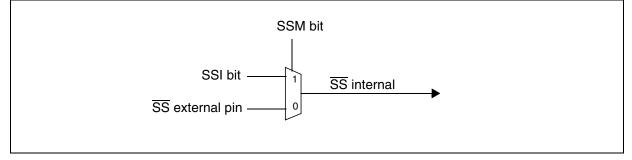

As an alternative to using the  $\overline{SS}$  pin to control the Slave Select signal, the application can choose to manage the Slave Select signal by software. This is configured by the SSM bit in the SPICSR register (see Figure 46)

In software management, the external SS pin is free for other application uses and the internal SS signal level is driven by writing to the SSI bit in the SPICSR register.

#### In Master mode:

57/

- SS internal must be held high continuously

## In Slave Mode:

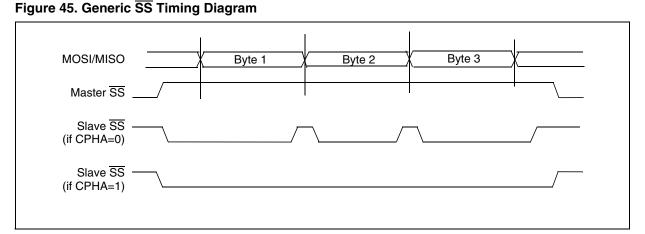

There are two cases depending on the data/clock timing relationship (see Figure 45):

- If CPHA=1 (data latched on 2nd clock edge):

- $\overline{SS}$  internal must be held low during the entire transmission. This implies that in single slave applications the SS pin either can be tied to V<sub>SS</sub>, or <u>made</u> free for standard I/O by managing the SS function by software (SSM= 1 and SSI=0 in the in the SPICSR register)

If CPHA=0 (data latched on 1st clock edge):

$-\overline{SS}$  internal must be held low during byte transmission and pulled high between each byte to allow the slave to write to the shift register. If SS is not pulled high, a Write Collision error will occur when the slave writes to the shift register (see Section 10.4.5.3).

## Figure 46. Hardware/Software Slave Select Management

## SERIAL PERIPHERAL INTERFACE (Cont'd)

57

## Table 20. SPI Register Map and Reset Values

| Address<br>(Hex.) | Register<br>Label | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|-------------------|-------------------|------|------|------|------|------|------|------|------|

| 0021h             | SPIDR             | MSB  |      |      |      |      |      |      | LSB  |

| 002111            | Reset Value       | х    | х    | х    | х    | х    | х    | х    | x    |

| 0022h             | SPICR             | SPIE | SPE  | SPR2 | MSTR | CPOL | CPHA | SPR1 | SPR0 |

| 002211            | Reset Value       | 0    | 0    | 0    | 0    | х    | х    | х    | х    |

| 0023h             | SPICSR            | SPIF | WCOL | OR   | MODF |      | SOD  | SSM  | SSI  |

| 002311            | Reset Value       | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

## **10.5 SERIAL COMMUNICATIONS INTERFACE (SCI)**

## 10.5.1 Introduction

The Serial Communications Interface (SCI) offers a flexible means of full-duplex data exchange with external equipment requiring an industry standard NRZ asynchronous serial data format. The SCI offers a very wide range of baud rates using two baud rate generator systems.

#### 10.5.2 Main Features

- Full duplex, asynchronous communications

- NRZ standard format (Mark/Space)

- Dual baud rate generator systems

- Independently programmable transmit and receive baud rates up to 500K baud

- Programmable data word length (8 or 9 bits)

- Receive buffer full, Transmit buffer empty and End of Transmission flags

- Two receiver wake-up modes:

- Address bit (MSB)

- Idle line

- Muting function for multiprocessor configurations

- Separate enable bits for Transmitter and Receiver

- Four error detection flags:

- Overrun error

- Noise error

- Frame error

- Parity error

- Five interrupt sources with flags:

- Transmit data register empty

- Transmission complete

- Receive data register full

- Idle line received

- Overrun error detected

- Parity control:

- Transmits parity bit

- Checks parity of received data byte

- Reduced power consumption mode

## **10.5.3 General Description**

The interface is externally connected to another device by two pins (see Figure 51):

- TDO: Transmit Data Output. When the transmitter and the receiver are disabled, the output pin returns to its I/O port configuration. When the transmitter and/or the receiver are enabled and nothing is to be transmitted, the TDO pin is at high level.

- RDI: Receive Data Input is the serial data input. Oversampling techniques are used for data recovery by discriminating between valid incoming data and noise.

Through these pins, serial data is transmitted and received as frames comprising:

- An Idle Line prior to transmission or reception

- A start bit

- A data word (8 or 9 bits) least significant bit first

- A Stop bit indicating that the frame is complete

- This interface uses two types of baud rate generator:

- A conventional type for commonly-used baud rates

- An extended type with a prescaler offering a very wide range of baud rates even with non-standard oscillator frequencies

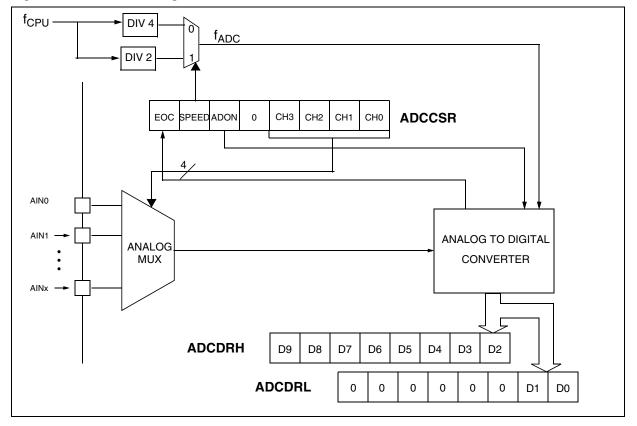

## 10.6 10-BIT A/D CONVERTER (ADC)

## 10.6.1 Introduction

The on-chip Analog to Digital Converter (ADC) peripheral is a 10-bit, successive approximation converter with internal sample and hold circuitry. This peripheral has up to 16 multiplexed analog input channels (refer to device pin out description) that allow the peripheral to convert the analog voltage levels from up to 16 different sources.

The result of the conversion is stored in a 10-bit Data Register. The A/D converter is controlled through a Control/Status Register.

## 10.6.2 Main Features

- 10-bit conversion

- Up to 16 channels with multiplexed input

- Linear successive approximation

- Data register (DR) which contains the results

**47**/

- Conversion complete status flag

- On/off bit (to reduce consumption)

The block diagram is shown in Figure 54.

## Figure 54. ADC Block Diagram

## 10-BIT A/D CONVERTER (ADC) (Cont'd)

## **10.6.3 Functional Description**

The conversion is monotonic, meaning that the result never decreases if the analog input does not and never increases if the analog input does not.

If the input voltage ( $V_{AIN}$ ) is greater than  $V_{AREF}$  (high-level voltage reference) then the conversion result is FFh in the ADCDRH register and 03h in the ADCDRL register (without overflow indication).

If the input voltage ( $V_{AIN}$ ) is lower than  $V_{SSA}$  (low-level voltage reference) then the conversion result in the ADCDRH and ADCDRL registers is 00 00h.

The A/D converter is linear and the digital result of the conversion is stored in the ADCDRH and AD-CDRL registers. The accuracy of the conversion is described in the Electrical Characteristics Section.

$R_{AIN}$  is the maximum recommended impedance for an analog input signal. If the impedance is too high, this will result in a loss of accuracy due to leakage and sampling not being completed in the alloted time.

## 10.6.3.1 A/D Converter Configuration

The analog input ports must be configured as input, no pull-up, no interrupt. Refer to the «I/O ports» chapter. Using these pins as analog inputs does not affect the ability of the port to be read as a logic input.

In the ADCCSR register:

- Select the CS[3:0] bits to assign the analog channel to convert.

#### 10.6.3.2 Starting the Conversion

In the ADCCSR register:

Set the ADON bit to enable the A/D converter and to start the conversion. From this time on, the ADC performs a continuous conversion of the selected channel.

When a conversion is complete:

- The EOC bit is set by hardware.

- The result is in the ADCDR registers.

A read to the ADCDRH resets the EOC bit.

To read the 10 bits, perform the following steps:

- 1. Poll the EOC bit

- 2. Read the ADCDRL register

- 3. Read the ADCDRH register. This clears EOC automatically.

**Note:** The data is not latched, so both the low and the high data register must be read before the next conversion is complete, so it is recommended to disable interrupts while reading the conversion result.

To read only 8 bits, perform the following steps:

- 1. Poll the EOC bit

- 2. Read the ADCDRH register. This clears EOC automatically.

#### 10.6.3.3 Changing the conversion channel

The application can change channels during conversion. When software modifies the CH[3:0] bits in the ADCCSR register, the current conversion is stopped, the EOC bit is cleared, and the A/D converter starts converting the newly selected channel.

#### 10.6.4 Low Power Modes

**Note:** The A/D converter may be disabled by resetting the ADON bit. This feature allows reduced power consumption when no conversion is needed.

| Mode | Description                                                                                                                                                                               |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WAIT | No effect on A/D Converter                                                                                                                                                                |

|      | A/D Converter disabled.                                                                                                                                                                   |

| HALT | After wakeup from Halt mode, the A/D<br>Converter requires a stabilization time<br>t <sub>STAB</sub> (see Electrical Characteristics)<br>before accurate conversions can be<br>performed. |

#### 10.6.5 Interrupts

None.

## INSTRUCTION SET OVERVIEW (Cont'd)

## 11.1.1 Inherent

All Inherent instructions consist of a single byte. The opcode fully specifies all the required information for the CPU to process the operation.

| Inherent Instruction       | Function                                 |

|----------------------------|------------------------------------------|

| NOP                        | No operation                             |

| TRAP                       | S/W Interrupt                            |

| WFI                        | Wait For Interrupt (Low Pow-<br>er Mode) |

| HALT                       | Halt Oscillator (Lowest Power<br>Mode)   |

| RET                        | Sub-routine Return                       |

| IRET                       | Interrupt Sub-routine Return             |

| SIM                        | Set Interrupt Mask (level 3)             |

| RIM                        | Reset Interrupt Mask (level 0)           |

| SCF                        | Set Carry Flag                           |

| RCF                        | Reset Carry Flag                         |

| RSP                        | Reset Stack Pointer                      |

| LD                         | Load                                     |

| CLR                        | Clear                                    |

| PUSH/POP                   | Push/Pop to/from the stack               |

| INC/DEC                    | Increment/Decrement                      |

| TNZ                        | Test Negative or Zero                    |

| CPL, NEG                   | 1 or 2 Complement                        |

| MUL                        | Byte Multiplication                      |

| SLL, SRL, SRA, RLC,<br>RRC | Shift and Rotate Operations              |

| SWAP                       | Swap Nibbles                             |

## 11.1.2 Immediate

5/

Immediate instructions have 2 bytes, the first byte contains the opcode, the second byte contains the operand value.

| Immediate Instruction | Function              |

|-----------------------|-----------------------|

| LD                    | Load                  |

| CP                    | Compare               |

| BCP                   | Bit Compare           |

| AND, OR, XOR          | Logical Operations    |

| ADC, ADD, SUB, SBC    | Arithmetic Operations |

## 11.1.3 Direct

In Direct instructions, the operands are referenced by their memory address.

The direct addressing mode consists of two submodes:

## **Direct (short)**

The address is a byte, thus requires only one byte after the opcode, but only allows 00 - FF addressing space.

## Direct (long)

The address is a word, thus allowing 64 Kbyte addressing space, but requires 2 bytes after the opcode.

## 11.1.4 Indexed (No Offset, Short, Long)

In this mode, the operand is referenced by its memory address, which is defined by the unsigned addition of an index register (X or Y) with an offset.

The indirect addressing mode consists of three submodes:

### Indexed (No Offset)

There is no offset, (no extra byte after the opcode), and allows 00 - FF addressing space.

## Indexed (Short)

The offset is a byte, thus requires only one byte after the opcode and allows 00 - 1FE addressing space.

## Indexed (long)

The offset is a word, thus allowing 64 Kbyte addressing space and requires 2 bytes after the opcode.

## 11.1.5 Indirect (Short, Long)

The required data byte to do the operation is found by its memory address, located in memory (pointer).

The pointer address follows the opcode. The indirect addressing mode consists of two submodes:

#### Indirect (short)

The pointer address is a byte, the pointer size is a byte, thus allowing 00 - FF addressing space, and requires 1 byte after the opcode.

#### Indirect (long)

The pointer address is a byte, the pointer size is a word, thus allowing 64 Kbyte addressing space, and requires 1 byte after the opcode.

## **12.2 ABSOLUTE MAXIMUM RATINGS**

Stresses above those listed as "absolute maximum ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device under these condi-

12.2.1 Voltage Characteristics

tions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

| Symbol                                    | Ratings                                             | Maximum value                  | Unit     |

|-------------------------------------------|-----------------------------------------------------|--------------------------------|----------|

| V <sub>DD</sub> - V <sub>SS</sub>         | Supply voltage                                      | 6.5                            |          |

| V <sub>PP</sub> - V <sub>SS</sub>         | Programming Voltage                                 | 13                             | v        |

| V <sub>IN</sub> <sup>1) &amp; 2)</sup>    | Input Voltage on true open drain pin                | V <sub>SS</sub> -0.3 to 5.5    |          |

|                                           | Input voltage on any other pin                      | $V_{SS}$ -0.3 to $V_{DD}$ +0.3 |          |

| $ \Delta V_{DDx} $ and $ \Delta V_{SSx} $ | Variations between different digital power pins     | 50                             | mV       |

| IV <sub>SSA</sub> - V <sub>SSx</sub> I    | Variations between digital and analog ground pins   | 50                             | IIIV     |

| V <sub>ESD(HBM)</sub>                     | Electro-static discharge voltage (Human Body Model) | see Section 12.7.3.1 on        | nago 123 |

| V <sub>ESD(MM)</sub>                      | Electro-static discharge voltage (Machine Model)    | See Section 12.7.3.1 011       | paye 123 |

#### **12.2.2 Current Characteristics**

| Symbol                                       | Ratings                                                  |                                | Maximum value | Unit |

|----------------------------------------------|----------------------------------------------------------|--------------------------------|---------------|------|

|                                              | Total current into V <sub>DD</sub> power lines           | 32-pin devices                 | 75            | mA   |

| IVDD                                         | (source) <sup>3)</sup>                                   | 44-pin devices                 | 150           | IIIA |

| h in a                                       | Total current out of V <sub>SS</sub> ground lines        | 32-pin devices                 | 75            | mA   |

| I <sub>VSS</sub>                             | (sink) for <sup>3)</sup>                                 | 44-pin devices                 | 150           | IIIA |

|                                              | Output current sunk by any standard I/                   | O and control pin              | 25            |      |

| I <sub>IO</sub>                              | Output current sunk by any high sink I/O pin             |                                | 50            |      |

|                                              | Output current source by any I/Os and                    | control pin                    | - 25          |      |

|                                              | Injected current on VPP pin                              |                                | ± 5           |      |

| 2) & 4)                                      | Injected current on RESET pin when not driver ternally   | ot driven low in-              | ± 2           | mA   |

| I <sub>INJ(PIN)</sub> <sup>2) &amp; 4)</sup> | Injected current on flash device pin PB0                 |                                | + 5           |      |

|                                              | Injected current on OSC1 and OSC2 pins                   |                                | ± 5           |      |

|                                              | Injected current on any other pin <sup>5) &amp; 6)</sup> |                                | ± 5           |      |

| ΣI <sub>INJ(PIN)</sub> <sup>2)</sup>         | Total injected current (sum of all I/O ar                | nd control pins) <sup>5)</sup> | ± 25          |      |

#### Notes:

1. Directly connecting the RESET and I/O pins to V<sub>DD</sub> or V<sub>SS</sub> could damage the device if an unintentional internal reset is generated or an unexpected change of the I/O configuration occurs (for example, due to a corrupted program counter). To guarantee safe operation, this connection has to be done through a pull-up or pull-down resistor (typical:  $4.7k\Omega$  for RESET,  $10k\Omega$  for I/Os). For the same reason, unused I/O pins must not be directly tied to V<sub>DD</sub> or V<sub>SS</sub>.

2. I<sub>INJ(PIN)</sub> must never be exceeded. This is implicitly insured if V<sub>IN</sub> maximum is respected. If V<sub>IN</sub> maximum cannot be respected, the injection current must be limited externally to the I<sub>INJ(PIN)</sub> value. A positive injection is induced by V<sub>IN</sub>>V<sub>DD</sub> while a negative injection is induced by V<sub>IN</sub><V<sub>SS</sub>. For true open-drain pads, there is no positive injection current, and the corresponding V<sub>IN</sub> maximum must always be respected

3. All power ( $V_{DD}$ ) and ground ( $V_{SS}$ ) lines must always be connected to the external supply.

4. Negative injection disturbs the analog performance of the device. See note in "ADC Accuracy" on page 135.

5. When several inputs are submitted to a current injection, the maximum  $\Sigma I_{INJ(PIN)}$  is the absolute sum of the positive and negative injected currents (instantaneous values). These results are based on characterisation with  $\Sigma I_{INJ(PIN)}$  maximum current injection on four I/O port pins of the device.

6. True open drain I/O port pins do not accept positive injection.

## **12.2.3 Thermal Characteristics**

| Symbol           | Ratings                                             | Value              | Unit |

|------------------|-----------------------------------------------------|--------------------|------|

| T <sub>STG</sub> | Storage temperature range                           | -65 to +150        | °C   |

| TJ               | Maximum junction temperature (see Section 13.2 THER | MAL CHARACTERISTIC | S)   |

## **12.3 OPERATING CONDITIONS**

| Symbol           | Parameter                          | Conditions                                                      | Min  | Max | Unit   |

|------------------|------------------------------------|-----------------------------------------------------------------|------|-----|--------|

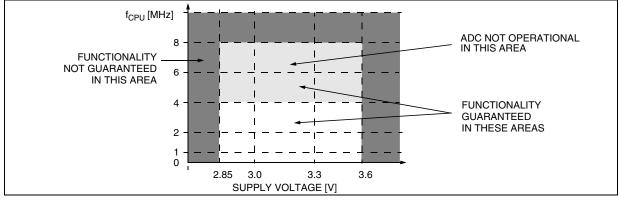

| f                | Internal clock frequency           | ADC not used                                                    | 0    | 8   | MHz    |

| f <sub>CPU</sub> | Internal clock frequency           | f <sub>ADC</sub> max = 1 MHz.                                   | 0    | 4   | IVITIZ |

|                  | Operating Voltage (ROM versions)   |                                                                 | 2.85 | 3.6 | V      |

| $V_{DD}$         | Operating Voltage (Flash versions) | V <sub>PP</sub> = 11.4 to 12.6V (for Write/<br>Erase operation) | 2.85 | 3.6 | v      |

|                  |                                    | 1 Suffix Version                                                | 0    | 70  |        |

| T <sub>A</sub>   | Ambient temperature range          | 5 Suffix Version                                                | -10  | 85  | °C     |

|                  |                                    | 6 Suffix Version                                                | -40  | 85  |        |

**Warning**: Do not connect 12V to  $V_{PP}$  before  $V_{DD}$  is powered on, as this may damage the device.

# Figure 57. f<sub>CPU</sub> Max Versus $V_{\text{DD}}$

<u>ل</u>حک

## DEVICE CONFIGURATION AND ORDERING INFORMATION (Cont'd)

## 14.2 DEVICE ORDERING INFORMATION AND TRANSFER OF CUSTOMER CODE

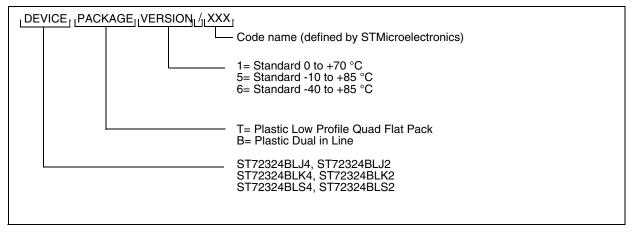

ROM devices can be ordered in any combination of memory size and temperature range with the types given in Figure 87 and by completing the option list on the next page. Flash devices are available only in the types listed in Table 27.

ROM customer code is made up of the ROM contents and the list of the selected options (if any). The ROM contents are to be sent with the S19 hexadecimal file generated by the development tool. All unused bytes must be set to FFh.

### Figure 87. ROM Factory Coded Device Types

Refer to application note AN1635 for information on the counter listing returned by ST after code has been transferred.

The STMicroelectronics Sales Organization will be pleased to provide detailed information on contractual points.

**Caution:** The Readout Protection binary value is inverted between ROM and FLASH products. The option byte checksum will differ between ROM and FLASH.

## DEVICE CONFIGURATION AND ORDERING INFORMATION (Cont'd)

## Table 27. Orderable Flash Device Types

57

| Part Number   | Package | Flash<br>Memory<br>(KBytes) | Temp. Range |

|---------------|---------|-----------------------------|-------------|

| ST72F324LK2T6 |         | 8                           |             |

| ST72F324LK4T6 |         | 16                          | -40°C +85°C |

| ST72F324LK6T6 | LQFP32  | 32                          | _           |

| ST72F324LK2T5 | LQFF32  | 8                           |             |

| ST72F324LK4T5 |         | 16                          | -10°C +85°C |

| ST72F324LK6T5 |         | 32                          | -10 C +65 C |

| ST72F324LK6B5 | SDIP32  | 32                          | _           |

| ST72F324LJ2T6 |         | 8                           |             |

| ST72F324LJ4T6 |         | 16                          | -40°C +85°C |

| ST72F324LJ6T6 | LQFP44  | 32                          | _           |

| ST72F324LJ2T5 |         | 8                           |             |

| ST72F324LJ4T5 |         | 16                          | -10°C +85°C |

| ST72F324LJ6T5 |         | 32                          |             |

| ST72F324LS2T6 | LQFP48  | 8                           | -40°C +85°C |

| ST72F324LS4T6 |         | 16                          | -40 0 +03 0 |

|                                                                                                                                                                                                                                            | 9                                                            | ST72324BL MICROCO                                                                                                                                                                                                                                                  |                                                                                                     |                                                                                                                                                                                 |          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| Customer:                                                                                                                                                                                                                                  |                                                              | (Last update:                                                                                                                                                                                                                                                      |                                                                                                     | er 2007)                                                                                                                                                                        |          |

| Address:                                                                                                                                                                                                                                   |                                                              |                                                                                                                                                                                                                                                                    |                                                                                                     |                                                                                                                                                                                 |          |

|                                                                                                                                                                                                                                            |                                                              |                                                                                                                                                                                                                                                                    |                                                                                                     |                                                                                                                                                                                 |          |

| Contact:                                                                                                                                                                                                                                   |                                                              | •••••                                                                                                                                                                                                                                                              | • •                                                                                                 |                                                                                                                                                                                 |          |

| Reference/ROM Code*                                                                                                                                                                                                                        |                                                              |                                                                                                                                                                                                                                                                    |                                                                                                     |                                                                                                                                                                                 |          |

| *The ROM code name is<br>ROM code must be sen                                                                                                                                                                                              | s assigne                                                    | d by STMicroelectronic                                                                                                                                                                                                                                             | <br>S.                                                                                              |                                                                                                                                                                                 |          |

| ROM code must be sen                                                                                                                                                                                                                       | t in .S19 f                                                  | ormatHex extension of                                                                                                                                                                                                                                              | cannot be                                                                                           | processed.                                                                                                                                                                      |          |

| Device Type/Memory Si                                                                                                                                                                                                                      |                                                              |                                                                                                                                                                                                                                                                    |                                                                                                     |                                                                                                                                                                                 |          |

| ROM DEVICE:                                                                                                                                                                                                                                |                                                              | 16K                                                                                                                                                                                                                                                                |                                                                                                     | 8K                                                                                                                                                                              |          |

| LQFP32:                                                                                                                                                                                                                                    | Ι                                                            | [ ] ST72324BLK4T<br>[ ] ST72324BLJ4T<br>[ ] ST72324BLS4T                                                                                                                                                                                                           | I                                                                                                   | [] ST72324BLK2T                                                                                                                                                                 |          |

| LQFP44:                                                                                                                                                                                                                                    | I                                                            | [] ST72324BLJ4T                                                                                                                                                                                                                                                    | l I                                                                                                 | [] ST72324BLJ2T                                                                                                                                                                 |          |

| LQFP48:                                                                                                                                                                                                                                    | I                                                            | [] ST72324BLS4T                                                                                                                                                                                                                                                    | I                                                                                                   | [] ST72324BLS2T                                                                                                                                                                 |          |

| DIE FORM:                                                                                                                                                                                                                                  |                                                              | 16K                                                                                                                                                                                                                                                                |                                                                                                     | 8K                                                                                                                                                                              |          |

| 32-pin:                                                                                                                                                                                                                                    | I                                                            | []<br>[]<br>[]                                                                                                                                                                                                                                                     | I                                                                                                   | []                                                                                                                                                                              |          |

| 44-pin:                                                                                                                                                                                                                                    | Ι                                                            | []                                                                                                                                                                                                                                                                 | I.                                                                                                  | []                                                                                                                                                                              |          |

| 48-pin:                                                                                                                                                                                                                                    | Ι                                                            | []                                                                                                                                                                                                                                                                 | I                                                                                                   | []                                                                                                                                                                              |          |

| Conditioning (check onl                                                                                                                                                                                                                    |                                                              |                                                                                                                                                                                                                                                                    |                                                                                                     |                                                                                                                                                                                 |          |

| Packag                                                                                                                                                                                                                                     | ged Prod                                                     | uct                                                                                                                                                                                                                                                                | Die Pro                                                                                             | oduct (dice tested at 25°C only)                                                                                                                                                |          |

| [] Tape & Reel                                                                                                                                                                                                                             |                                                              |                                                                                                                                                                                                                                                                    | [] Tape                                                                                             |                                                                                                                                                                                 |          |

|                                                                                                                                                                                                                                            | []                                                           |                                                                                                                                                                                                                                                                    | [] Inked                                                                                            |                                                                                                                                                                                 |          |

|                                                                                                                                                                                                                                            |                                                              | · · ·                                                                                                                                                                                                                                                              |                                                                                                     | n wafer on sticky foil                                                                                                                                                          |          |

|                                                                                                                                                                                                                                            |                                                              |                                                                                                                                                                                                                                                                    | [] Waff                                                                                             |                                                                                                                                                                                 |          |

| wer Supply Range:                                                                                                                                                                                                                          | [12 85 tr                                                    | 3.61/                                                                                                                                                                                                                                                              |                                                                                                     |                                                                                                                                                                                 |          |