Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| D.1.11-                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Details                    |                                                                            |

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PSMC, PWM, WDT                                |

| Number of I/O              | 24                                                                         |

| Program Memory Size        | 3.5KB (2K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 256 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 11x12b; D/A 1x8b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                             |

| Supplier Device Package    | 28-SSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1782-e-ss |

# 2.1 Automatic Interrupt Context Saving

During interrupts, certain registers are automatically saved in shadow registers and restored when returning from the interrupt. This saves stack space and user code. See **8.5** "Automatic Context Saving", for more information.

## 2.2 16-level Stack with Overflow and Underflow

These devices have an external stack memory 15 bits wide and 16 words deep. A Stack Overflow or Underflow will set the appropriate bit (STKOVF or STKUNF) in the PCON register, and if enabled will cause a software Reset. See Section 3.5 "Stack" for more details.

### 2.3 File Select Registers

There are two 16-bit File Select Registers (FSR). FSRs can access all file registers and program memory, which allows one Data Pointer for all memory. When an FSR points to program memory, there is one additional instruction cycle in instructions using INDF to allow the data to be fetched. General purpose memory can now also be addressed linearly, providing the ability to access contiguous data larger than 80 bytes. There are also new instructions to support the FSRs. See Section 3.6 "Indirect Addressing" for more details.

#### 2.4 Instruction Set

There are 49 instructions for the enhanced mid-range CPU to support the features of the CPU. See Section 29.0 "Instruction Set Summary" for more details.

| TABLE 3-8: | SPECIAL  | FUNCTION REGISTER SUMMARY |

|------------|----------|---------------------------|

| IADEL 3-0. | OI LUIAL |                           |

| Addr               | Name       | Bit 7          | Bit 6                                                                    | Bit 5           | Bit 4          | Bit 3            | Bit 2  | Bit 1    | Bit 0    | Value on POR, BOR | Value on<br>all other<br>Resets |

|--------------------|------------|----------------|--------------------------------------------------------------------------|-----------------|----------------|------------------|--------|----------|----------|-------------------|---------------------------------|

| Bank               | ( 0        |                |                                                                          |                 |                |                  |        |          |          |                   |                                 |

| 00Ch               | PORTA      | PORTA Data L   | atch when wr                                                             | itten: PORTA p  | ins when read  |                  |        |          |          | xxxx xxxx         | uuuu uuuu                       |

| 00Dh               | PORTB      | PORTB Data L   | atch when wi                                                             | ritten: PORTB p | ins when read  |                  |        |          |          | xxxx xxxx         | uuuu uuuu                       |

| 00Eh               | PORTC      | PORTC Data L   | atch when w                                                              | ritten: PORTC p | oins when read |                  |        |          |          | xxxx xxxx         | uuuu uuuu                       |

| 00Fh               | _          | Unimplemente   | d                                                                        |                 |                |                  |        |          |          | _                 | _                               |

| 010h               | PORTE      | _              | _                                                                        | _               | _              | RE3              | _      | _        | _        | x                 | u                               |

| 011h               | PIR1       | TMR1GIF        | ADIF                                                                     | RCIF            | TXIF           | SSP1IF           | CCP1IF | TMR2IF   | TMR1IF   | 0000 0000         | 0000 0000                       |

| 012h               | PIR2       | OSFIF          | C2IF                                                                     | C1IF            | EEIF           | BCL1IF           | _      | C3IF     | CCP2IF   | 0000 0-00         | 0000 0-00                       |

| 013h               | _          | Unimplemente   | d                                                                        |                 |                |                  |        |          | •        | _                 | _                               |

| 014h               | PIR4       | _              | _                                                                        | PSMC2TIF        | PSMC1TIF       | _                | _      | PSMC2SIF | PSMC1SIF | 0000              | 0000                            |

| 015h               | TMR0       | Timer0 Module  | Register                                                                 |                 |                |                  | •      | •        | •        | xxxx xxxx         | uuuu uuuu                       |

| 016h               | TMR1L      | Holding Regist | ling Register for the Least Significant Byte of the 16-bit TMR1 Register |                 |                |                  |        |          |          | xxxx xxxx         | uuuu uuuu                       |

| 017h               | TMR1H      | Holding Regist | ling Register for the Most Significant Byte of the 16-bit TMR1 Register  |                 |                |                  |        |          |          |                   | uuuu uuuu                       |

| 018h               | T1CON      | TMR1CS1        | TMR1CS0                                                                  | T1CKPS1         | T1CKPS0        | T10SCEN          | T1SYNC | _        | TMR10N   | 0000 00-0         | uuuu uu-u                       |

| 019h               | T1GCON     | TMR1GE         | T1GPOL                                                                   | T1GTM           | T1GSPM         | T1GGO/<br>DONE   | T1GVAL | T1GS     | S<1:0>   | 0000 0x00         | uuuu uxuu                       |

| 016h               | TMR2       | Holding Regist | ling Register for the Least Significant Byte of the 16-bit TMR2 Register |                 |                |                  |        |          |          |                   | uuuu uuuu                       |

| 017h               | PR2        | Holding Regist | Iding Register for the Most Significant Byte of the 16-bit TMR2 Register |                 |                |                  |        |          |          | xxxx xxxx         | uuuu uuuu                       |

| 018h               | T2CON      | _              |                                                                          | T2OUT           | PS<3:0>        |                  | TMR2ON | T2CKP    | 'S<1:0>  | -000 0000         | -000 0000                       |

| 01Dh<br>to<br>01Fh |            | Unimplemente   | Jnimplemented                                                            |                 |                |                  |        |          |          | _                 | _                               |

| Banl               | k 1        |                |                                                                          |                 |                |                  |        |          |          |                   |                                 |

| 08Ch               | TRISA      | PORTA Data D   | irection Regi                                                            | ster            |                |                  |        |          |          | 1111 1111         | 1111 1111                       |

| 08Dh               | TRISB      | PORTB Data D   | Direction Regi                                                           | ster            |                |                  |        |          |          | 1111 1111         | 1111 1111                       |

| 08Eh               | TRISC      | PORTC Data [   | Direction Regi                                                           | ster            |                |                  |        |          |          | 1111 1111         | 1111 1111                       |

| 08Fh               | _          | Unimplemente   | d                                                                        |                 |                |                  |        |          |          | _                 | _                               |

| 090h               | TRISE      | _              | _                                                                        | -               | -              | (2)              | _      | _        | _        | 1                 | 1                               |

| 091h               | PIE1       | TMR1GIE        | ADIE                                                                     | RCIE            | TXIE           | SSP1IE           | CCP1IE | TMR2IE   | TMR1IE   | 0000 0000         | 0000 0000                       |

| 092h               | PIE2       | OSEIE          | C2IE                                                                     | C1IE            | EEIE           | BCL1IE           | _      | C3IE     | CCP2IE   | 0000 0-00         | 0000 0-00                       |

| 093h               |            | Unimplemente   | d                                                                        |                 |                |                  |        |          |          | _                 | _                               |

| 094h               | PIE4       | _              |                                                                          | PSMC2TIE        | PSMC1TIE       | ı                | _      | PSMC2SIE | PSMC1SIE | 0000              | 0000                            |

| 095h               | OPTION_REG | WPUEN          | INTEDG                                                                   | TMR0CS          | TMR0SE         | PSA              |        | PS<2:0>  |          | 1111 1111         | 1111 1111                       |

| 096h               | PCON       | STKOVF         | STKUNF                                                                   | _               | RWDT           | RMCLR            | RI     | POR      | BOR      | 00-1 11qq         | qq-q qquu                       |

| 097h               | WDTCON     | _              | _                                                                        |                 | 1              | WDTPS<4:0>       |        |          | SWDTEN   | 01 0110           | 01 0110                         |

| 098h               | OSCTUNE    | _              | TUN<5:0>                                                                 |                 |                |                  |        |          |          | 00 0000           | 00 0000                         |

| 099h               | OSCCON     | SPLLEN         | IRCF<3:0> SCS<1:0>                                                       |                 |                |                  |        |          |          | 0011 1-00         | 0011 1-00                       |

| 09Ah               | OSCSTAT    | T10SCR         | PLLR                                                                     | OSTS            | HFIOFR         | HFIOFL           | MFIOFR | LFIOFR   | HFIOFS   | 00q000            | qqqq0q                          |

| 09Bh               | ADRESL     | A/D Result Reg | gister Low                                                               |                 |                |                  |        | •        | •        | xxxx xxxx         | uuuu uuuu                       |

| 09Ch               | ADRESH     | A/D Result Reg | gister High                                                              |                 |                |                  |        |          |          | xxxx xxxx         | uuuu uuuu                       |

| 09Dh               | ADCON0     | ADRMD          |                                                                          |                 | CHS<4:0>       |                  |        | GO/DONE  | ADON     | 0000 0000         | 0000 0000                       |

| 09Eh               | ADCON1     | ADFM           |                                                                          | ADCS<2:0>       |                | _                | ADNREF | ADPRE    | F<1:0>   |                   | 0000 -000                       |

|                    | ADCON2     |                | TRIGS                                                                    | EL<3:0>         |                |                  | CHSN   |          |          |                   | 000000                          |

|                    |            |                |                                                                          |                 | condition -= ı | unimonlo monto d |        |          |          |                   | 1                               |

x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'. These registers can be addressed from any bank. Unimplemented, read as '1'. PIC16F1782/3 only. Legend:

Note

**TABLE 3-8:** SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

| Addr              | Name      | Bit 7           | Bit 6                         | Bit 5     | Bit 4     | Bit 3       | Bit 2          | Bit 1          | Bit 0   | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|-------------------|-----------|-----------------|-------------------------------|-----------|-----------|-------------|----------------|----------------|---------|----------------------|---------------------------------|

| Banl              | k 16      |                 |                               |           |           |             |                |                |         |                      |                                 |

| 80Ch<br>—<br>810h | _         | Unimplemente    | d                             |           |           |             |                |                |         | _                    | _                               |

| 811h              | PSMC1CON  | PSMC1EN         | PSMC1LD                       | PSMC1DBFE | PSMC1DBRE |             | P1MOD          | )E<3:0>        |         | 0000 0000            | 0000 0000                       |

| 812h              | PSMC1MDL  | P1MDLEN         | P1MDLPOL                      | P1MDLBIT  | _         |             | P1MSR          | C<3:0>         |         | 000- 0000            | 000- 0000                       |

| 813h              | PSMC1SYNC | _               | _                             | _         | _         | P1SYNC<1:0> |                |                | C<1:0>  | 00                   | 00                              |

| 814h              | PSMC1CLK  | _               | ı                             | P1CPF     | RE<1:0>   | ı           | _              | P1CSR          | :C<1:0> | 0000                 | 0000                            |

| 815h              | PSMC10EN  | _               | _                             | P10EF     | P10EE     | P10ED       | P10EC          | P10EB          | P10EA   | 00 0000              | 00 0000                         |

| 816h              | PSMC1POL  | _               | P1INPOL                       | P1POLF    | P1POLE    | P1POLD      | P1POLC         | P1POLB         | P1POLA  | -000 0000            | -000 0000                       |

| 817h              | PSMC1BLNK | _               | _                             | P1FEB     | M<1:0>    | _           | _              | P1REB          | M<1:0>  | 0000                 | 0000                            |

| 818h              | PSMC1REBS | P1REBIN         | _                             | _         | _         | P1REBSC3    | P1REBSC2       | P1REBSC1       | _       | 0 000-               | 0 000-                          |

| 819h              | PSMC1FEBS | P1FEBIN         | _                             | _         | _         | P1FEBSC3    | P1FEBSC2       | P1FEBSC1       | _       | 0 000-               | 0 000-                          |

| 81Ah              | PSMC1PHS  | P1PHSIN         | ı                             | _         | ı         | P1PHSC3     | P1PHSC2        | P1PHSC1        | P1PHST  | 0 0000               | 0 0000                          |

| 81Bh              | PSMC1DCS  | P1DCSIN         | ı                             | _         | 1         | P1DCSC3     | P1DCSC2        | P1DCSC1        | P1DCST  | 0 0000               | 0 0000                          |

| 81Ch              | PSMC1PRS  | P1PRSIN         | ı                             | _         | 1         | P1PRSC3     | P1PRSC2        | P1PRSC1        | P1PRST  | 0 0000               | 0 0000                          |

| 81Dh              | PSMC1ASDC | P1ASE           | P1ASDEN                       | P1ARSEN   | 1         | ı           | _              | _              | P1ASDOV | 0000                 | 0000                            |

| 81Eh              | PSMC1ASDL | _               | ı                             | P1ASDLF   | P1ASDLE   | P1ASDLD     | P1ASDLC        | P1ASDLB        | P1ASDLA | 00 0000              | 00 0000                         |

| 81Fh              | PSMC1ASDS | P1ASDSIN        | ı                             | _         | 1         | P1ASDSC3    | P1ASDSC2       | P1ASDSC1       | ı       | 0 000-               | 0 000-                          |

| 820h              | PSMC1INT  | P1TOVIE         | P1TPHIE                       | P1TDCIE   | P1TPRIE   | P1TOVIF     | P1TPHIF        | P1TDCIF        | P1TPRIF | 0000 0000            | 0000 0000                       |

| 821h              | PSMC1PHL  | Phase Low Cor   | unt                           |           |           |             |                |                |         | 0000 0000            | 0000 0000                       |

| 822h              | PSMC1PHH  | Phase High Co   | ount                          |           |           |             |                |                |         | 0000 0000            | 0000 0000                       |

| 823h              | PSMC1DCL  | Duty Cycle Lov  | w Count                       |           |           |             |                |                |         | 0000 0000            | 0000 0000                       |

| 824h              | PSMC1DCH  | Duty Cycle Hig  | h Count                       |           |           |             |                |                |         | 0000 0000            | 0000 0000                       |

| 825h              | PSMC1PRL  | Period Low Co   | unt                           |           |           |             |                |                |         | 0000 0000            | 0000 0000                       |

| 826h              | PSMC1PRH  | Period High Co  | ount                          |           |           |             |                |                |         | 0000 0000            | 0000 0000                       |

| 827h              | PSMC1TMRL | Time base Lov   | V Counter                     |           |           |             |                |                |         | 0000 0001            | 0000 0001                       |

| 828h              | PSMC1TMRH | Time base Hig   | h Counter                     |           |           |             |                |                |         | 0000 0000            | 0000 0000                       |

| 829h              | PSMC1DBR  | rising Edge De  | ad-band Cou                   | nter      |           |             |                |                |         | 0000 0000            | 0000 0000                       |

| 82Ah              | PSMC1DBF  | Falling Edge D  | alling Edge Dead-band Counter |           |           |             |                |                |         | 0000 0000            | 0000 0000                       |

| 82Bh              | PSMC1BLKR | rising Edge Bla | sing Edge Blanking Counter    |           |           |             |                |                |         | 0000 0000            | 0000 0000                       |

| 82Ch              | PSMC1BLKF | Falling Edge B  | lanking Coun                  | ter       |           |             |                |                |         | 0000 0000            | 0000 0000                       |

| 82Dh              | PSMC1FFA  | _               | _                             | _         | _         | Frac        | tional Frequer | ncy Adjust Reg | ister   | 0000                 | 0000                            |

| 82Eh              | PSMC1STR0 | _               | _                             | P1STRF    | P1STRE    | P1STRD      | P1STRC         | P1STRB         | P1STRA  | 00 0001              | 00 0001                         |

| 82Fh              | PSMC1STR1 | P1SYNC          | _                             | _         | _         | _           | _              | P1LSMEN        | P1HSMEN | 000                  | 000                             |

| 830h              | _         | Unimplemente    | d                             |           |           |             |                |                |         | _                    | _                               |

x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'. Legend:

Note

These registers can be addressed from any bank. Unimplemented, read as '1'. PIC16F1782/3 only. 1: 2:

3:

TABLE 5-5: SUMMARY OF REGISTERS ASSOCIATED WITH RESETS

| Name   | Bit 7  | Bit 6  | Bit 5      | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0  | Register on Page |

|--------|--------|--------|------------|-------|-------|-------|-------|--------|------------------|

| BORCON | SBOREN | BORFS  |            | -     | _     |       | -     | BORRDY | 47               |

| PCON   | STKOVF | STKUNF | _          | RWDT  | RMCLR | RI    | POR   | BOR    | 51               |

| STATUS | _      | _      | _          | TO    | PD    | Z     | DC    | С      | 18               |

| WDTCON | _      | _      | WDTPS<4:0> |       |       |       |       | SWDTEN | 94               |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by Resets.

#### 8.1 Operation

Interrupts are disabled upon any device Reset. They are enabled by setting the following bits:

- · GIE bit of the INTCON register

- Interrupt Enable bit(s) for the specific interrupt event(s)

- PEIE bit of the INTCON register (if the Interrupt Enable bit of the interrupt event is contained in the PIE1 or PIE2 registers)

The INTCON, PIR1 and PIR2 registers record individual interrupts via interrupt flag bits. Interrupt flag bits will be set, regardless of the status of the GIE, PEIE and individual interrupt enable bits.

The following events happen when an interrupt event occurs while the GIE bit is set:

- · Current prefetched instruction is flushed

- · GIE bit is cleared

- Current Program Counter (PC) is pushed onto the stack

- Critical registers are automatically saved to the shadow registers (See "Section 8.5 "Automatic Context Saving".")

- · PC is loaded with the interrupt vector 0004h

The firmware within the Interrupt Service Routine (ISR) should determine the source of the interrupt by polling the interrupt flag bits. The interrupt flag bits must be cleared before exiting the ISR to avoid repeated interrupts. Because the GIE bit is cleared, any interrupt that occurs while executing the ISR will be recorded through its interrupt flag, but will not cause the processor to redirect to the interrupt vector.

The RETFIE instruction exits the ISR by popping the previous address from the stack, restoring the saved context from the shadow registers and setting the GIE bit.

For additional information on a specific interrupt's operation, refer to its peripheral chapter.

- Note 1: Individual interrupt flag bits are set, regardless of the state of any other enable bits.

- 2: All interrupts will be ignored while the GIE bit is cleared. Any interrupt occurring while the GIE bit is clear will be serviced when the GIE bit is set again.

#### 8.2 Interrupt Latency

Interrupt latency is defined as the time from when the interrupt event occurs to the time code execution at the interrupt vector begins. The latency for synchronous interrupts is three or four instruction cycles. For asynchronous interrupts, the latency is three to five instruction cycles, depending on when the interrupt occurs. See Figure 8-2 and Figure 8.3 for more details.

#### REGISTER 13-5: ANSELA: PORTA ANALOG SELECT REGISTER

| R/W-1/1 | U-0 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 |

|---------|-----|---------|---------|---------|---------|---------|---------|

| ANSA7   | _   | ANSA5   | ANSA4   | ANSA3   | ANSA2   | ANSA1   | ANSA0   |

| bit 7   |     |         |         |         |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown

'1' = Bit is set '0' = Bit is cleared

U = Unimplemented bit, read as '0'

-n/n = Value at POR and BOR/Value at all other Resets

bit 5 ANSA7: Analog Select between Analog or Digital Function on pins RA7, respectively

0 = Digital I/O. Pin is assigned to port or digital special function.

1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital input buffer disabled.

bit 6 **Unimplemented:** Read as '0'

bit 5-0 ANSA<5:0>: Analog Select between Analog or Digital Function on pins RA<5:0>, respectively

0 = Digital I/O. Pin is assigned to port or digital special function.

1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital input buffer disabled.

**Note 1:** When setting a pin to an analog input, the corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

#### REGISTER 13-6: WPUA: WEAK PULL-UP PORTA REGISTER

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| WPUA7   | WPUA6   | WPUA5   | WPUA4   | WPUA3   | WPUA2   | WPUA1   | WPUA0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'u = Bit is unchangedx = Bit is unknown-n/n = Value at POR and BOR/Value at all other Resets'1' = Bit is set'0' = Bit is cleared

bit 7-0 WPUA<7:0>: Weak Pull-up Register bits

1 = Pull-up enabled0 = Pull-up disabled

Note 1: Global WPUEN bit of the OPTION\_REG register must be cleared for individual pull-ups to be enabled.

2: The weak pull-up device is automatically disabled if the pin is in configured as an output.

### 13.8 Register Definitions: PORTC

#### **REGISTER 13-18: PORTC: PORTC REGISTER**

| R/W-x/u |

|---------|---------|---------|---------|---------|---------|---------|---------|

| RC7     | RC6     | RC5     | RC4     | RC3     | RC2     | RC1     | RC0     |

| bit 7   |         |         |         |         |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-0 RC<7:0>: PORTC General Purpose I/O Pin bits<sup>(1)</sup>

1 = Port pin is  $\geq$  VIH 0 = Port pin is  $\leq$  VIL

**Note 1:** Writes to PORTC are actually written to corresponding LATC register. Reads from PORTC register is return of actual I/O pin values.

#### **REGISTER 13-19: TRISC: PORTC TRI-STATE REGISTER**

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| TRISC7  | TRISC6  | TRISC5  | TRISC4  | TRISC3  | TRISC2  | TRISC1  | TRISC0  |

| bit 7   |         |         |         |         |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-0 TRISC<7:0>: PORTC Tri-State Control bits

1 = PORTC pin configured as an input (tri-stated)

0 = PORTC pin configured as an output

#### **REGISTER 13-20: LATC: PORTC DATA LATCH REGISTER**

| R/W-x/u |

|---------|---------|---------|---------|---------|---------|---------|---------|

| LATC7   | LATC6   | LATC5   | LATC4   | LATC3   | LATC2   | LATC1   | LATC0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-0 LATC<7:0>: PORTC Output Latch Value bits<sup>(1)</sup>

**Note 1:** Writes to PORTC are actually written to corresponding LATC register. Reads from PORTC register is return of actual I/O pin values.

## 15.4 Register Definitions: FVR Control

#### REGISTER 15-1: FVRCON: FIXED VOLTAGE REFERENCE CONTROL REGISTER

| R/W-0/0 | R-q/q                 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|---------|-----------------------|---------|---------|---------|---------|---------|---------|

| FVREN   | FVRRDY <sup>(1)</sup> | TSEN    | TSRNG   | CDAF\   | √R<1:0> | ADFV    | R<1:0>  |

| bit 7   |                       |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = Value depends on condition                        |

| bit 7   | <b>FVREN:</b> Fixed Voltage Reference Enable bit  1 = Fixed Voltage Reference is enabled  0 = Fixed Voltage Reference is disabled                                                                                                                                                                                                                                                                                                  |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6   | FVRRDY: Fixed Voltage Reference Ready Flag bit <sup>(1)</sup> 1 = Fixed Voltage Reference output is ready for use  0 = Fixed Voltage Reference output is not ready or not enabled                                                                                                                                                                                                                                                  |

| bit 5   | TSEN: Temperature Indicator Enable bit <sup>(3)</sup> 1 = Temperature Indicator is enabled  0 = Temperature Indicator is disabled                                                                                                                                                                                                                                                                                                  |

| bit 4   | TSRNG: Temperature Indicator Range Selection bit <sup>(3)</sup> 1 = Vout = Vdd - 4Vt (High Range)  0 = Vout = Vdd - 2Vt (Low Range)                                                                                                                                                                                                                                                                                                |

| bit 3-2 | CDAFVR<1:0>: Comparator and DAC Fixed Voltage Reference Selection bit  11 = Comparator and DAC Fixed Voltage Reference Peripheral output is 4x (4.096V) <sup>(2)</sup> 10 = Comparator and DAC Fixed Voltage Reference Peripheral output is 2x (2.048V) <sup>(2)</sup> 01 = Comparator and DAC Fixed Voltage Reference Peripheral output is 1x (1.024V)  00 = Comparator and DAC Fixed Voltage Reference Peripheral output is off. |

| bit 1-0 | ADFVR<1:0>: ADC Fixed Voltage Reference Selection bit  11 = ADC Fixed Voltage Reference Peripheral output is 4x (4.096V) <sup>(2)</sup> 10 = ADC Fixed Voltage Reference Peripheral output is 2x (2.048V) <sup>(2)</sup> 01 = ADC Fixed Voltage Reference Peripheral output is 1x (1.024V)  00 = ADC Fixed Voltage Reference Peripheral output is off.                                                                             |

Note 1: FVRRDY is always '1' on "F" devices only.

2: Fixed Voltage Reference output cannot exceed VDD.

3: See Section 16.0 "Temperature Indicator Module" for additional information.

#### TABLE 15-2: SUMMARY OF REGISTERS ASSOCIATED WITH FIXED VOLTAGE REFERENCE

| Name   | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3       | Bit 2 | Bit 1 | Bit 0  | Register on page |

|--------|-------|--------|-------|-------|-------------|-------|-------|--------|------------------|

| FVRCON | FVREN | FVRRDY | TSEN  | TSRNG | CDAFVR<1:0> |       | ADFVF | R<1:0> | 137              |

**Legend:** Shaded cells are not used with the Fixed Voltage Reference.

# 19.0 DIGITAL-TO-ANALOG CONVERTER (DAC) MODULE

The Digital-to-Analog Converter supplies a variable voltage reference, ratiometric with the input source, with 256 selectable output levels.

The input of the DAC can be connected to:

- · External VREF pins

- VDD supply voltage

- FVR (Fixed Voltage Reference)

The output of the DAC can be configured to supply a reference voltage to the following:

- · Comparator positive input

- · Op amp positive input

- · ADC input channel

- DACOUT1 pin

- · DACOUT2 pin

The Digital-to-Analog Converter (DAC) is enabled by setting the DACEN bit of the DACCON0 register.

### 19.1 Output Voltage Selection

The DAC has 256 voltage level ranges. The 256 levels are set with the DACR<7:0> bits of the DACCON1 register.

The DAC output voltage is determined by Equation 19-1:

#### **EQUATION 19-1: DAC OUTPUT VOLTAGE**

$$\frac{IF\ DACxEN = 1}{VOUT} = \left( (VSOURCE+ - VSOURCE-) \times \frac{DACxR[7:0]}{2^8} \right) + VSOURCE-$$

$$VSOURCE+ = VDD,\ VREF,\ or\ FVR\ BUFFER\ 2$$

$$VSOURCE- = VSS$$

### 19.2 Ratiometric Output Level

The DAC output value is derived using a resistor ladder with each end of the ladder tied to a positive and negative voltage reference input source. If the voltage of either input source fluctuates, a similar fluctuation will result in the DAC output value.

The value of the individual resistors within the ladder can be found in Section 30.0 "Electrical Specifications".

#### 19.3 DAC Voltage Reference Output

The DAC voltage can be output to the DACOUT1 and DACOUT2 pins by setting the respective DACOE1 and DACOE2 pins of the DACCON0 register. Selecting the DAC reference voltage for output on either DACOUTx pin automatically overrides the digital output buffer and digital input threshold detector functions of that pin. Reading the DACOUTx pin when it has been configured for DAC reference voltage output will always return a '0'.

Due to the limited current drive capability, a buffer must be used on the DAC voltage reference output for external connections to either DACOUTx pin. Figure 19-2 shows an example buffering technique.

#### REGISTER 24-23: PSMCxPRL: PSMC PERIOD COUNT LOW BYTE REGISTER

| R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0  | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|---------|---------|---------|---------|----------|---------|---------|---------|

|         |         |         | PSMCxF  | PRL<7:0> |         |         |         |

| bit 7   |         |         |         |          |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets '1' = Bit is set '0' = Bit is cleared

bit 7-0 **PSMCxPRL<7:0>:** 16-bit Period Time Least Significant bits

= PSMCxPR<7:0>

#### REGISTER 24-24: PSMCxPRH: PSMC PERIOD COUNT HIGH BYTE REGISTER

| R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0  | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|---------|---------|---------|---------|----------|---------|---------|---------|

|         |         |         | PSMCxP  | PRH<7:0> |         |         |         |

| bit 7   |         |         |         |          |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-0 **PSMCxPRH<7:0>:** 16-bit Period Time Most Significant bits

= PSMCxPR<15:8>

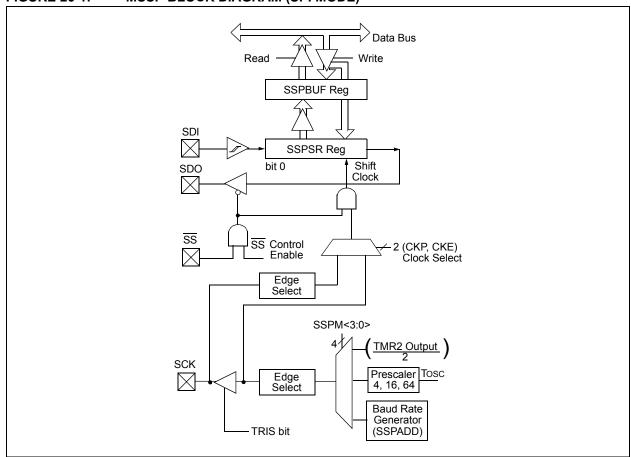

### 26.0 MASTER SYNCHRONOUS SERIAL PORT (MSSP) MODULE

### 26.1 Master SSP (MSSP) Module Overview

The Master Synchronous Serial Port (MSSP) module is a serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be serial EEPROMs, shift registers, display drivers, A/D converters, etc. The MSSP module can operate in one of two modes:

- Serial Peripheral Interface (SPI)

- Inter-Integrated Circuit (I<sup>2</sup>C™)

The SPI interface supports the following modes and features:

- · Master mode

- · Slave mode

- · Clock Parity

- Slave Select Synchronization (Slave mode only)

- · Daisy-chain connection of slave devices

Figure 26-1 is a block diagram of the SPI interface module.

FIGURE 26-1: MSSP BLOCK DIAGRAM (SPI MODE)

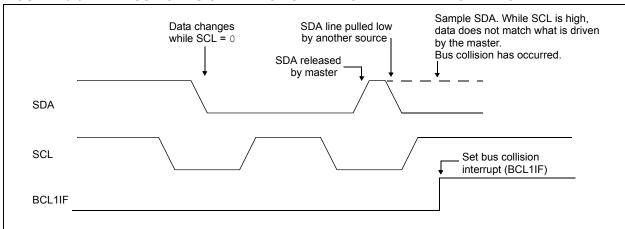

### FIGURE 26-32: BUS COLLISION TIMING FOR TRANSMIT AND ACKNOWLEDGE

TABLE 27-2: SUMMARY OF REGISTERS ASSOCIATED WITH ASYNCHRONOUS RECEPTION

| Name    | Bit 7     | Bit 6   | Bit 5  | Bit 4       | Bit 3        | Bit 2  | Bit 1  | Bit 0   | Register<br>on Page |

|---------|-----------|---------|--------|-------------|--------------|--------|--------|---------|---------------------|

| APFCON  | C2OUTSEL  | CC1PSEL | SDOSEL | SCKSEL      | SDISEL       | TXSEL  | RXSEL  | CCP2SEL | 111                 |

| BAUDCON | ABDOVF    | RCIDL   | _      | SCKP        | BRG16        | -      | WUE    | ABDEN   | 322                 |

| INTCON  | GIE       | PEIE    | TMR0IE | INTE        | IOCIE        | TMR0IF | INTF   | IOCIF   | 79                  |

| PIE1    | TMR1GIE   | ADIE    | RCIE   | TXIE        | SSP1IE       | CCP1IE | TMR2IE | TMR1IE  | 80                  |

| PIR1    | TMR1GIF   | ADIF    | RCIF   | TXIF        | SSP1IF       | CCP1IF | TMR2IF | TMR1IF  | 83                  |

| RCREG   |           |         | EUS    | SART Receiv | e Data Regis | ter    |        |         | 315*                |

| RCSTA   | SPEN      | RX9     | SREN   | CREN        | ADDEN        | FERR   | OERR   | RX9D    | 321                 |

| SPBRGL  |           |         |        | BRG<        | 7:0>         |        |        |         | 323                 |

| SPBRGH  | BRG<15:8> |         |        |             |              |        |        |         | 323                 |

| TRISC   | TRISC7    | TRISC6  | TRISC5 | TRISC4      | TRISC3       | TRISC2 | TRISC1 | TRISC0  | 125                 |

| TXSTA   | CSRC      | TX9     | TXEN   | SYNC        | SENDB        | BRGH   | TRMT   | TX9D    | 320                 |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used for asynchronous reception.

<sup>\*</sup> Page provides register information.

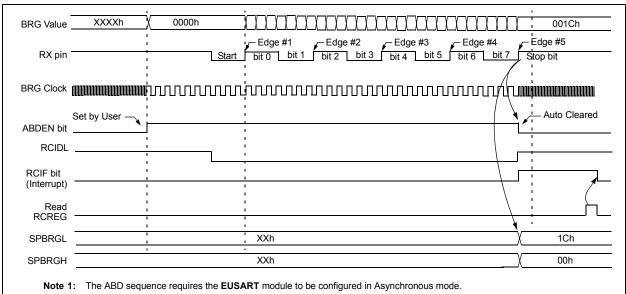

#### 27.4.1 AUTO-BAUD DETECT

The EUSART module supports automatic detection and calibration of the baud rate.

In the Auto-Baud Detect (ABD) mode, the clock to the BRG is reversed. Rather than the BRG clocking the incoming RX signal, the RX signal is timing the BRG. The Baud Rate Generator is used to time the period of a received 55h (ASCII "U") which is the Sync character for the LIN bus. The unique feature of this character is that it has five rising edges including the Stop bit edge.

Setting the ABDEN bit of the BAUDCON register starts the auto-baud calibration sequence (Figure 27-6). While the ABD sequence takes place, the EUSART state machine is held in idle. On the first rising edge of the receive line, after the Start bit, the SPBRG begins counting up using the BRG counter clock as shown in Table 27-6. The fifth rising edge will occur on the RX pin at the end of the eighth bit period. At that time, an accumulated value totaling the proper BRG period is left in the SPBRGH, SPBRGL register pair, the ABDEN bit is automatically cleared and the RCIF interrupt flag is set. The value in the RCREG needs to be read to clear the RCIF interrupt. RCREG content should be discarded. When calibrating for modes that do not use the SPBRGH register the user can verify that the SPBRGL register did not overflow by checking for 00h in the SPBRGH register.

The BRG auto-baud clock is determined by the BRG16 and BRGH bits as shown in Table 27-6. During ABD, both the SPBRGH and SPBRGL registers are used as a 16-bit counter, independent of the BRG16 bit setting. While calibrating the baud rate period, the SPBRGH

and SPBRGL registers are clocked at 1/8th the BRG base clock rate. The resulting byte measurement is the average bit time when clocked at full speed.

- Note 1: If the WUE bit is set with the ABDEN bit, auto-baud detection will occur on the byte following the Break character (see Section 27.4.3 "Auto-Wake-up on Break").

- 2: It is up to the user to determine that the incoming character baud rate is within the range of the selected BRG clock source. Some combinations of oscillator frequency and EUSART baud rates are not possible.

- 3: During the auto-baud process, the auto-baud counter starts counting at 1. Upon completion of the auto-baud sequence, to achieve maximum accuracy, subtract 1 from the SPBRGH:SPBRGL register pair.

TABLE 27-6: BRG COUNTER CLOCK RATES

| BRG16 | BRGH | BRG Base<br>Clock | BRG ABD<br>Clock |

|-------|------|-------------------|------------------|

| 0     | 0    | Fosc/64           | Fosc/512         |

| 0     | 1    | Fosc/16           | Fosc/128         |

| 1     | 0    | Fosc/16           | Fosc/128         |

| 1     | 1    | Fosc/4            | Fosc/32          |

Note: During the ABD sequence, SPBRGL and SPBRGH registers are both used as a 16-bit counter, independent of BRG16 setting.

FIGURE 27-6: AUTOMATIC BAUD RATE CALIBRATION

#### 29.0 INSTRUCTION SET SUMMARY

Each instruction is a 14-bit word containing the operation code (opcode) and all required operands. The opcodes are broken into three broad categories.

- · Byte Oriented

- · Bit Oriented

- · Literal and Control

The literal and control category contains the most varied instruction word format.

Table 29-3 lists the instructions recognized by the MPASM $^{\text{TM}}$  assembler.

All instructions are executed within a single instruction cycle, with the following exceptions, which may take two or three cycles:

- Subroutine takes two cycles (CALL, CALLW)

- Returns from interrupts or subroutines take two cycles (RETURN, RETLW, RETFIE)

- Program branching takes two cycles (GOTO, BRA, BRW, BTFSS, BTFSC, DECFSZ, INCSFZ)

- One additional instruction cycle will be used when any instruction references an indirect file register and the file select register is pointing to program memory.

One instruction cycle consists of 4 oscillator cycles; for an oscillator frequency of 4 MHz, this gives a nominal instruction execution rate of 1 MHz.

All instruction examples use the format '0xhh' to represent a hexadecimal number, where 'h' signifies a hexadecimal digit.

### 29.1 Read-Modify-Write Operations

Any instruction that specifies a file register as part of the instruction performs a Read-Modify-Write (R-M-W) operation. The register is read, the data is modified, and the result is stored according to either the instruction, or the destination designator 'd'. A read operation is performed on a register even if the instruction writes to that register.

TABLE 29-1: OPCODE FIELD DESCRIPTIONS

| Field | Description                                                                                                                                                         |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f     | Register file address (0x00 to 0x7F)                                                                                                                                |

| W     | Working register (accumulator)                                                                                                                                      |

| b     | Bit address within an 8-bit file register                                                                                                                           |

| k     | Literal field, constant data or label                                                                                                                               |

| х     | Don't care location (= 0 or 1). The assembler will generate code with x = 0. It is the recommended form of use for compatibility with all Microchip software tools. |

| d     | Destination select; d = 0: store result in W,<br>d = 1: store result in file register f.<br>Default is d = 1.                                                       |

| n     | FSR or INDF number. (0-1)                                                                                                                                           |

| mm    | Pre-post increment-decrement mode selection                                                                                                                         |

## TABLE 29-2: ABBREVIATION DESCRIPTIONS

| Field | Description     |  |  |  |  |  |  |

|-------|-----------------|--|--|--|--|--|--|

| PC    | Program Counter |  |  |  |  |  |  |

| TO    | Time-out bit    |  |  |  |  |  |  |

| С     | Carry bit       |  |  |  |  |  |  |

| DC    | Digit carry bit |  |  |  |  |  |  |

| Z     | Zero bit        |  |  |  |  |  |  |

| PD    | Power-down bit  |  |  |  |  |  |  |

#### 30.3 DC Characteristics

**TABLE 30-1: SUPPLY VOLTAGE**

| PIC16L         | F1782/3 |                                                        | Standard   | d Opera | ting Cond  | ditions ( | unless otherwise stated)                            |  |  |  |

|----------------|---------|--------------------------------------------------------|------------|---------|------------|-----------|-----------------------------------------------------|--|--|--|

| PIC16F         | 1782/3  |                                                        |            |         |            |           |                                                     |  |  |  |

| Param<br>. No. | Sym.    | Characteristic                                         | Min.       | Typ†    | Max.       | Units     | Conditions                                          |  |  |  |

| D001           | VDD     | Supply Voltage (VDDMIN, VDDMAX)                        |            |         |            |           |                                                     |  |  |  |

|                |         |                                                        | 1.8<br>2.7 |         | 3.6<br>3.6 | V<br>V    | Fosc ≤ 16 MHz:<br>Fosc ≤ 32 MHz ( <b>Note 2</b> )   |  |  |  |

| D001           |         |                                                        | 2.3<br>2.7 | _       | 5.5<br>5.5 | V<br>V    | Fosc ≤ 16 MHz:<br>Fosc ≤ 32 MHz ( <b>Note 2</b> )   |  |  |  |

| D002*          | VDR     | RAM Data Retention Voltage <sup>(1)</sup>              |            |         |            |           |                                                     |  |  |  |

|                |         |                                                        | 1.5        | _       | _          | V         | Device in Sleep mode                                |  |  |  |

| D002*          |         |                                                        | 1.7        | _       | _          | V         | Device in Sleep mode                                |  |  |  |

|                | VPOR*   | Power-on Reset Release Voltage                         | _          | 1.6     | _          | V         |                                                     |  |  |  |

|                | VPORR*  | Power-on Reset Rearm Voltage                           |            |         |            |           |                                                     |  |  |  |

|                |         |                                                        | _          | 0.8     | _          | V         | Device in Sleep mode                                |  |  |  |

|                |         |                                                        | _          | 1.5     |            | V         | Device in Sleep mode                                |  |  |  |

| D003           | VFVR    | Fixed Voltage Reference                                | -4         | _       | 4          | %         | $1.024V$ , $VDD \ge 2.5V$                           |  |  |  |

|                |         | Voltage <sup>(3)</sup>                                 | -4         | _       | 4          | %         | 2.048V, VDD ≥ 2.5V                                  |  |  |  |

|                |         |                                                        | -5         | _       | 5          | %         | 4.096V, VDD ≥ 4.75V                                 |  |  |  |

| D004*          | SVDD    | VDD Rise Rate to ensure internal Power-on Reset signal | 0.05       | _       | _          | V/ms      | See Section 5.1 "Power-On Reset (POR)" for details. |  |  |  |

<sup>\*</sup> These parameters are characterized but not tested.

<sup>†</sup> Data in "Typ" column is at 3.3V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered in Sleep mode without losing RAM data.

<sup>2:</sup> PLL required for 32 MHz operation.

<sup>3:</sup> Industrial temperature range only.

TABLE 30-2: SUPPLY VOLTAGE (IDD)<sup>(1,2)</sup>

| PIC16LF  | 1782/3          | Standard | Standard Operating Conditions (unless otherwise stated) |      |       |             |                                                                                    |  |  |  |

|----------|-----------------|----------|---------------------------------------------------------|------|-------|-------------|------------------------------------------------------------------------------------|--|--|--|

| PIC16F17 | 782/3           |          |                                                         |      |       |             |                                                                                    |  |  |  |

| Param    | Device          | Min      | Tomat                                                   | May  | Unite |             | Conditions                                                                         |  |  |  |

| No.      | Characteristics | Min.     | Тур†                                                    | Max. | Units | <b>V</b> DD | Note                                                                               |  |  |  |

| D009     | LDO Regulator   | _        | 75                                                      | _    | μΑ    | _           | High-Power mode, normal operation                                                  |  |  |  |

|          |                 | _        | 15                                                      | _    | μΑ    | _           | Sleep VREGCON<1> = 0                                                               |  |  |  |

|          |                 | _        | 0.3                                                     | _    | μΑ    | _           | Sleep VREGCON<1> = 1                                                               |  |  |  |

| D010     |                 | _        | 8                                                       | 20   | μА    | 1.8         | Fosc = 32 kHz                                                                      |  |  |  |

|          |                 | _        | 12                                                      | 24   | μА    | 3.0         | LP Oscillator mode (Note 4),<br>- $40^{\circ}$ C $\leq$ Ta $\leq$ + $85^{\circ}$ C |  |  |  |

| D010     |                 | _        | 18                                                      | 63   | μА    | 2.3         | Fosc = 32 kHz                                                                      |  |  |  |

|          |                 | _        | 20                                                      | 74   | μΑ    | 3.0         | LP Oscillator mode (Note 4, 5),<br>-40°C $\leq$ TA $\leq$ +85°C                    |  |  |  |

|          |                 | _        | 22                                                      | 79   | μΑ    | 5.0         | -40 C \( \text{IA} \( \text{ + 65} \) C                                            |  |  |  |

| D012     |                 | _        | 160                                                     | 650  | μΑ    | 1.8         | Fosc = 4 MHz                                                                       |  |  |  |

|          |                 | _        | 320                                                     | 1000 | μΑ    | 3.0         | XT Oscillator mode                                                                 |  |  |  |

| D012     |                 |          | 260                                                     | 700  | μΑ    | 2.3         | Fosc = 4 MHz                                                                       |  |  |  |

|          |                 | _        | 330                                                     | 1100 | μΑ    | 3.0         | XT Oscillator mode (Note 5)                                                        |  |  |  |

|          |                 | _        | 380                                                     | 1300 | μΑ    | 5.0         |                                                                                    |  |  |  |

- Note 1: The test conditions for all IDD measurements in active operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD; MCLR = VDD; WDT disabled.

- 2: The supply current is mainly a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption.

- 3: For RC oscillator configurations, current through REXT is not included. The current through the resistor can be extended by the formula IR = VDD/2REXT (mA) with REXT in  $k\Omega$ .

- 4: FVR and BOR are disabled.

- 5:  $0.1 \mu F$  capacitor on VCAP.

- 6: 8 MHz crystal oscillator with 4x PLL enabled.

TABLE 30-2: SUPPLY VOLTAGE (IDD)<sup>(1,2)</sup> (CONTINUED)

| PIC16LF17 | 782/3           |      | Standard | d Operati | ng Condit | ions (un | less otherwise stated)                  |

|-----------|-----------------|------|----------|-----------|-----------|----------|-----------------------------------------|

| PIC16F178 | 32/3            |      |          |           |           |          |                                         |

| Param     | Device          | Min. | Typ†     | Max.      | Units     |          | Conditions                              |

| No.       | Characteristics |      | -761     |           |           | VDD      | Note                                    |

| D014      |                 | _    | 125      | 550       | μА        | 1.8      | Fosc = 4 MHz                            |

|           |                 | _    | 280      | 1100      | μА        | 3.0      | EC Oscillator mode<br>Medium-Power mode |

| D014      |                 | _    | 220      | 650       | μА        | 2.3      | Fosc = 4 MHz                            |

|           |                 | _    | 290      | 1000      | μА        | 3.0      | EC Oscillator mode (Note 5)             |

|           |                 | _    | 350      | 1200      | μА        | 5.0      | Medium-Power mode                       |

| D015      |                 | _    | 2.1      | 6.2       | mA        | 3.0      | Fosc = 32 MHz                           |

|           |                 | _    | 2.5      | 7.5       | mA        | 3.6      | EC Oscillator High-Power mode           |

| D015      |                 | _    | 2.1      | 6.5       | mA        | 3.0      | Fosc = 32 MHz                           |

|           |                 | _    | 2.2      | 7.5       | mA        | 5.0      | EC Oscillator High-Power mode (Note 5)  |

| D017      |                 | _    | 130      | 180       | μΑ        | 1.8      | Fosc = 500 kHz                          |

|           |                 | _    | 150      | 250       | μА        | 3.0      | MFINTOSC mode                           |

| D017      |                 | _    | 150      | 250       | μА        | 2.3      | Fosc = 500 kHz                          |

|           |                 | _    | 170      | 330       | μА        | 3.0      | MFINTOSC mode (Note 5)                  |

|           |                 | _    | 220      | 430       | μА        | 5.0      |                                         |

| D019      |                 | _    | 0.8      | 2.2       | mA        | 1.8      | Fosc = 16 MHz                           |

|           |                 |      | 1.2      | 3.7       | mA        | 3.0      | HFINTOSC mode                           |

| D019      |                 | _    | 1.0      | 2.3       | mA        | 2.3      | Fosc = 16 MHz                           |

|           |                 | _    | 1.3      | 3.9       | mA        | 3.0      | HFINTOSC mode (Note 5)                  |

|           |                 | _    | 1.4      | 4.1       | mA        | 5.0      |                                         |

| D020      |                 | _    | 2.1      | 6.2       | mA        | 3.0      | Fosc = 32 MHz                           |

|           |                 | _    | 2.5      | 7.5       | mA        | 3.6      | HFINTOSC mode                           |

| D020      |                 | _    | 2.1      | 6.5       | mA        | 3.0      | Fosc = 32 MHz                           |

|           |                 |      | 2.2      | 7.5       | mA        | 5.0      | HFINTOSC mode                           |

| D022      |                 |      | 2.1      | 6.2       | mA        | 3.0      | Fosc = 32 MHz                           |

|           |                 | _    | 2.5      | 7.5       | mA        | 3.6      | HS Oscillator mode (Note 6)             |

| D022      |                 |      | 2.1      | 6.5       | mA        | 3.0      | Fosc = 32 MHz                           |

|           |                 | _    | 2.2      | 7.5       | mA        | 5.0      | HS Oscillator mode (Note 5, 6)          |

Note 1: The test conditions for all IDD measurements in active operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD; MCLR = VDD; WDT disabled.

- 2: The supply current is mainly a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption.

- 3: For RC oscillator configurations, current through Rext is not included. The current through the resistor can be extended by the formula IR = VDD/2Rext (mA) with Rext in  $k\Omega$ .

- 4: FVR and BOR are disabled.

- 5:  $0.1 \mu F$  capacitor on VCAP.

- **6:** 8 MHz crystal oscillator with 4x PLL enabled.

### TABLE 30-22: I<sup>2</sup>C™ BUS DATA REQUIREMENTS

**Standard Operating Conditions (unless otherwise stated)**

| Param.<br>No. | Symbol  | Characte              | eristic      | Min.       | Max. | Units | Conditions                                  |

|---------------|---------|-----------------------|--------------|------------|------|-------|---------------------------------------------|

| SP100*        | THIGH   | Clock high time       | 100 kHz mode | 4.0        |      | μS    | Device must operate at a minimum of 1.5 MHz |

|               |         |                       | 400 kHz mode | 0.6        | 1    | μS    | Device must operate at a minimum of 10 MHz  |

|               |         |                       | SSP module   | 1.5TcY     | -    |       |                                             |

| SP101*        | TLOW    | Clock low time        | 100 kHz mode | 4.7        | _    | μS    | Device must operate at a minimum of 1.5 MHz |

|               |         |                       | 400 kHz mode | 1.3        | _    | μS    | Device must operate at a minimum of 10 MHz  |

|               |         |                       | SSP module   | 1.5Tcy     | _    |       |                                             |

| SP102*        | TR      | SDA and SCL rise time | 100 kHz mode | _          | 1000 | ns    |                                             |

|               |         |                       | 400 kHz mode | 20 + 0.1CB | 300  | ns    | CB is specified to be from 10-400 pF        |

| SP103*        | TF      | SDA and SCL fall      | 100 kHz mode | _          | 250  | ns    |                                             |

|               |         | time                  | 400 kHz mode | 20 + 0.1CB | 250  | ns    | CB is specified to be from 10-400 pF        |

| SP106*        | THD:DAT | Data input hold time  | 100 kHz mode | 0          | _    | ns    |                                             |

|               |         |                       | 400 kHz mode | 0          | 0.9  | μS    |                                             |

| SP107*        | TSU:DAT | Data input setup      | 100 kHz mode | 250        |      | ns    | (Note 2)                                    |

|               |         | time                  | 400 kHz mode | 100        | _    | ns    |                                             |

| SP109*        | TAA     | Output valid from     | 100 kHz mode | _          | 3500 | ns    | (Note 1)                                    |

|               |         | clock                 | 400 kHz mode | _          | _    | ns    |                                             |

| SP110*        | TBUF    | Bus free time         | 100 kHz mode | 4.7        |      | μS    | Time the bus must be free                   |

|               |         |                       | 400 kHz mode | 1.3        |      | μS    | before a new transmission can start         |

| SP111         | Св      | Bus capacitive loadir | ng           | _          | 400  | pF    |                                             |

<sup>\*</sup> These parameters are characterized but not tested.

- **Note 1:** As a transmitter, the device must provide this internal minimum delay time to bridge the undefined region (min. 300 ns) of the falling edge of SCL to avoid unintended generation of Start or Stop conditions.

- 2: A Fast mode (400 kHz) I<sup>2</sup>C™ bus device can be used in a Standard mode (100 kHz) I<sup>2</sup>C bus system, but the requirement Tsu:DAT ≥ 250 ns must then be met. This will automatically be the case if the device does not stretch the low period of the SCL signal. If such a device does stretch the low period of the SCL signal, it must output the next data bit to the SDA line TR max. + Tsu:DAT = 1000 + 250 = 1250 ns (according to the Standard mode I<sup>2</sup>C bus specification), before the SCL line is released.

NOTES: