Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PSMC, PWM, WDT                                |

| Number of I/O              | 24                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 512 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 11x12b; D/A 1x8b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

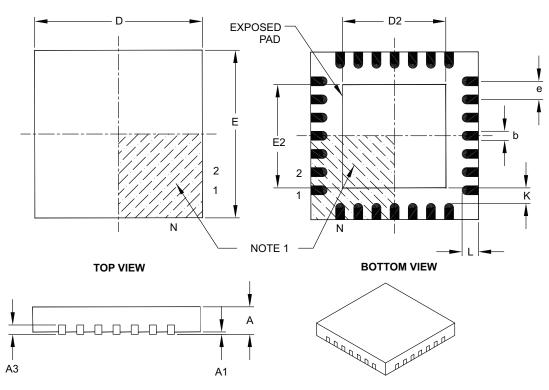

| Package / Case             | 28-VQFN Exposed Pad                                                        |

| Supplier Device Package    | 28-QFN (6x6)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1783-e-ml |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 4.2 Register Definitions: Configuration Words

## REGISTER 4-1: CONFIG1: CONFIGURATION WORD 1

|                 |                                                                                                                                           | R/P-1                                                              | R/P-1                                                        | R/P-1                                                               | R/P-1           | R/P-1             | R/P-1        |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|--------------------------------------------------------------|---------------------------------------------------------------------|-----------------|-------------------|--------------|

|                 |                                                                                                                                           | FCMEN                                                              | IESO                                                         | CLKOUTEN                                                            | BORE            | N<1:0>            | CPD          |

|                 |                                                                                                                                           | bit 13                                                             |                                                              |                                                                     |                 |                   | bit 8        |

|                 |                                                                                                                                           |                                                                    |                                                              |                                                                     |                 |                   |              |

| R/P-1           | R/P-1                                                                                                                                     | R/P-1                                                              | R/P-1                                                        | R/P-1                                                               | R/P-1           | R/P-1             | R/P-1        |

| CP              | MCLRE                                                                                                                                     | PWRTE                                                              | WD.                                                          | TE<1:0>                                                             |                 | FOSC<2:0>         |              |

| bit 7           |                                                                                                                                           |                                                                    |                                                              |                                                                     |                 |                   | bit 0        |

| Legend:         |                                                                                                                                           |                                                                    |                                                              |                                                                     |                 |                   |              |

| R = Readab      | le bit                                                                                                                                    | P = Programm                                                       | able bit                                                     | U = Unimplem                                                        | nented bit. rea | d as '1'          |              |

| '0' = Bit is cl |                                                                                                                                           | '1' = Bit is set                                                   |                                                              | -n = Value who                                                      |                 |                   |              |

| 0 Bitlo di      | curcu                                                                                                                                     | 1 Dit lo det                                                       |                                                              |                                                                     |                 |                   |              |

| bit 13          | 1 = Fail-Safe                                                                                                                             | I-Safe Clock Mor<br>Clock Monitor a<br>Clock Monitor is            | nd internal/e                                                | bit<br>external switchov                                            | er are both er  | nabled.           |              |

| bit 12          | 1 = Internal/E                                                                                                                            | al External Switc<br>External Switchov                             | ver mode is                                                  |                                                                     |                 |                   |              |

| bit 11          | CLKOUTEN<br>If FOSC cont<br>This bit is<br>All other FOS<br>1 = CLK                                                                       | SC modes:                                                          | e bit<br><u>set to LP, )</u><br>UT function<br>disabled. I/C | ( <u>T, HS modes</u> :<br>is disabled. Oscil<br>) function on the ( |                 | on the CLKOUT     | pin.         |

| bit 10-9        | BOREN<1:0<br>11 = BOR er<br>10 = BOR er                                                                                                   | >: Brown-out Re<br>nabled<br>nabled during ope<br>ontrolled by SBO | set Enable I                                                 | •                                                                   |                 |                   |              |

| bit 8           | CPD: Data Code Protection bit <sup>(1)</sup><br>1 = Data memory code protection is disabled<br>0 = Data memory code protection is enabled |                                                                    |                                                              |                                                                     |                 |                   |              |

| bit 7           |                                                                                                                                           | otection bit<br>memory code pr<br>memory code pr                   |                                                              |                                                                     |                 |                   |              |

| bit 6           | $\frac{\text{If LVP bit} = 1}{\text{This bit is}}$ $\frac{\text{If LVP bit} = 0}{1 = \text{MCLF}}$ $0 = \text{MCLF}$                      | s ignored.<br><u>::</u><br>R/VPP pin functior                      | n is MCLR; V                                                 | bit<br>Vea <u>k pull-u</u> p enab<br>put; MCLR interna              |                 | /eak pull-up unde | r control of |

| bit 5           | <b>PWRTE</b> : Pov<br>1 = PWRT d<br>0 = PWRT e                                                                                            |                                                                    | able bit                                                     |                                                                     |                 |                   |              |

| bit 4-3         | 11 = WDT er<br>10 = WDT er                                                                                                                | nabled while runr<br>ontrolled by the S                            | ing and dis                                                  |                                                                     | register        |                   |              |

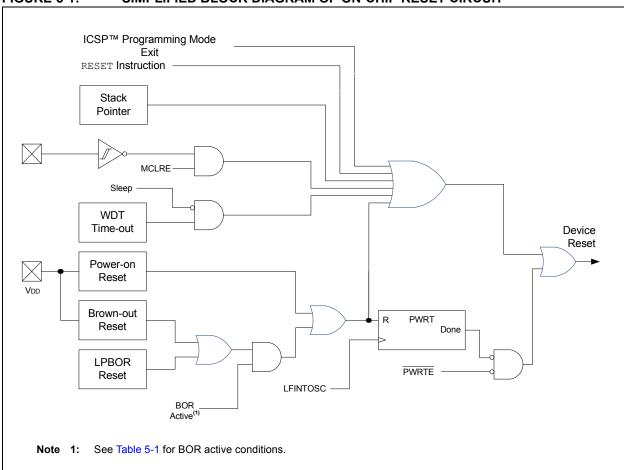

A simplified block diagram of the On-Chip Reset Circuit

is shown in Figure 5-1.

## 5.0 RESETS

There are multiple ways to reset this device:

- Power-On Reset (POR)

- Brown-Out Reset (BOR)

- Low-Power Brown-Out Reset (LPBOR)

- MCLR Reset

- WDT Reset

- RESET instruction

- Stack Overflow

- Stack Underflow

- · Programming mode exit

To allow VDD to stabilize, an optional Power-up Timer can be enabled to extend the Reset time after a BOR or POR event.

#### FIGURE 5-1: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

## 13.9 PORTE Registers

RE3 is input only, and also functions as  $\overline{\text{MCLR}}$ . The  $\overline{\text{MCLR}}$  feature can be disabled via a configuration fuse. RE3 also supplies the programming voltage. The TRIS bit for RE3 (TRISE3) always reads '1'.

13.9.1 INPUT THRESHOLD CONTROL

The INLVLE register (Register 13-28) controls the input voltage threshold for each of the available PORTE input pins. A selection between the Schmitt Trigger CMOS or the TTL Compatible thresholds is available. The input threshold is important in determining the value of a read of the PORTE register and also the level at which an interrupt-on-change occurs, if that feature is enabled. See Section TABLE 30-1: "Supply Voltage" for more information on threshold levels.

**Note:** Changing the input threshold selection should be performed while all peripheral modules are disabled. Changing the threshold level during the time a module is active may inadvertently generate a transition associated with an input pin, regardless of the actual voltage level on that pin.

#### 13.9.2 PORTE FUNCTIONS AND OUTPUT PRIORITIES

No output priorities. RE3 is an input-only pin.

## 24.2.9 OUTPUT WAVEFORM GENERATION

The PSMC PWM output waveform is generated based upon the different input events. However, there are several other factors that affect the PWM waveshapes:

- Output Control

- Output Enable

- Output Polarity

- · Waveform Mode Selection

- Dead-band Control

- · Steering control

### 24.2.10 OUTPUT CONTROL

#### 24.2.10.1 Output Pin Enable

Each PSMC PWM output pin has individual output enable control.

When the PSMC output enable control is disabled, the module asserts no control over the pin. In this state, the pin can be used for general purpose I/O or other associate peripheral use.

When the PSMC output enable is enabled, the active PWM waveform is applied to the pin per the port priority selection.

PSMC output enable selections are made with the PSMC Output Enable Control (PSMCxOEN) register (Register 24-6).

#### 24.2.10.2 Output Steering

PWM output will be presented only on pins for which output steering is enabled. The PSMC has up to six PWM outputs. The PWM signal in some modes can be steered to one or more of these outputs.

Steering differs from output enable in the following manner: When the output is enabled but the PWM steering to the corresponding output is not enabled, then general purpose output to the pin is disabled and the pin level will remain constantly in the inactive PWM state. Output steering is controlled with the PSMCS Steering Control 0 (PSMCxSTR0) register (Register 24-30).

Steering operates only in the following modes:

- · Single-phase

- Complementary Single-phase

- · 3-phase 6-step PWM

#### 24.2.10.3 Polarity Control

Each PSMC output has individual output polarity control. Polarity is set with the PSMC Polarity Control (PSMCxPOL) register (Register 24-7).

### 24.3 Modes of Operation

All modes of operation use the period, rising edge, and falling edge events to generate the various PWM output waveforms.

The 3-phase 6-step PWM mode makes special use of the software controlled steering to generate the required waveform.

Modes of operation are selected with the PSMC Control (PSMCxCON) register (Register 24-1).

#### 24.3.1 SINGLE-PHASE MODE

The single PWM is the most basic of all the waveshapes generated by the PSMC module. It consists of a single output that uses all three events (rising edge, falling edge and period events) to generate the waveform.

#### 24.3.1.1 Mode Features

- No dead-band control available

- PWM can be steered to any combination of the following PSMC outputs:

- PSMCxA

- PSMCxB

- PSMCxC

- PSMCxD

- PSMCxE

- PSMCxF

- Identical PWM waveform is presented to all pins for which steering is enabled.

#### 24.3.1.2 Waveform Generation

#### Rising Edge Event

All outputs with PxSTR enabled are set to the active state

#### Falling Edge Event

• All outputs with PxSTR enabled are set to the inactive state

Code for setting up the PSMC generate the single-phase waveform shown in Figure 24-4, and given in Example 24-1.

#### 24.3.11 VARIABLE FREQUENCY - FIXED DUTY CYCLE PWM WITH COMPLEMENTARY OUTPUTS

This mode is the same as the single output Fixed Duty Cycle mode except a complementary output with dead-band control is generated.

The rising edge and falling edge events are unused in this mode. Therefore, a different triggering mechanism is required for the dead-band counters.

A period events that generate a rising edge on PSMCxA use the rising edge dead-band counters.

A period events that generate a falling edge on PSMCxA use the falling edge dead-band counters.

#### 24.3.11.1 Mode Features

- · Dead-band control is available

- No steering control available

- Fractional Frequency Adjust

- Fine period adjustments are made with the PSMC Fractional Frequency Adjust (PSMCxFFA) register (Register 24-27)

- Primary PWM is output to the following pin:

- PSMCxA

- Complementary PWM is output to the following pin:

- PSMCxB

## 24.3.11.2 Waveform Generation

#### Period Event

When output is going inactive to active:

- · Complementary output is set inactive

- FFA counter is incremented by the 4-bit value in PSMCFFA register.

- · Dead-band rising is activated (if enabled)

- · Primary output is set active

When output is going active to inactive:

- · Primary output is set inactive

- FFA counter is incremented by the 4-bit value in PSMCFFA register

- Dead-band falling is activated (if enabled)

- · Complementary output is set active

## FIGURE 24-14: VARIABLE FREQUENCY – FIXED DUTY CYCLE PWM WITH COMPLEMENTARY OUTPUTS WAVEFORM

| PWM Period Number  | 12                    | 34                  | 5-6                    | 7         | 8 |

|--------------------|-----------------------|---------------------|------------------------|-----------|---|

| period_event       |                       |                     | <u> </u>               |           |   |

| Rising Edge Event  |                       |                     | Unused in <sup>1</sup> | this mode |   |

| Falling Edge Event | Unused in this mode   |                     |                        |           |   |

| PSMCxA             |                       |                     |                        |           |   |

|                    | → <del>-</del> Rising | ►<br>Edge Dead Band | - Falling Edge D       | ead Band  |   |

| PSMCxB             |                       |                     |                        |           |   |

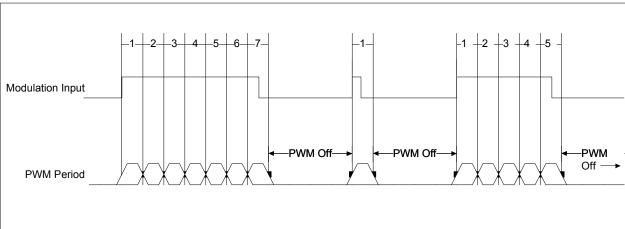

## 24.6 **PSMC Modulation (Burst Mode)**

PSMC modulation is a method to stop/start PWM operation of the PSMC without having to disable the module. It also allows other modules to control the operational period of the PSMC. This is also referred to as Burst mode.

This is a method to implement PWM dimming.

#### 24.6.1 MODULATION ENABLE

The modulation function is enabled by setting the PxMDLEN bit of PSMC Modulation Control (PSMCxMDL) register (Register 24-2).

When modulation is enabled, the modulation source controls when the PWM signals are active and inactive.

When modulation is disabled, the PWM signals operate continuously, regardless of the selected modulation source.

#### 24.6.2 MODULATION SOURCES

There are multiple sources that can be used for modulating the PSMC. However, unlike the PSMC input sources, only one modulation source can be selected at a time. Modulation sources include:

- PSMCxIN pin

- Any CCP output

- Any Comparator output

- PxMDLBIT of the PSMCxMDL register

## FIGURE 24-19: PSMC MODULATION WAVEFORM

## 24.6.2.1 PxMDLBIT Bit

The PxMDLBIT bit of the PSMC Modulation Control (PSMCxMDL) register (Register 24-2) allows for software modulation control without having to enable/disable other module functions.

## 24.6.3 MODULATION EFFECT ON PWM SIGNALS

When modulation starts, the PSMC begins operation on a new period, just as if it had rolled over from one period to another during continuous operation.

When modulation stops, its operation depends on the type of waveform being generated.

In operation modes other than Fixed Duty Cycle, the PSMC completes its current PWM period and then freezes the module. The PSMC output pins are forced into the default inactive state ready for use when modulation starts.

In Fixed Duty Cycle mode operation, the PSMC continues to operate until the period event changes the PWM to its inactive state, at which point the PSMC module is frozen. The PSMC output pins are forced into the default inactive state ready for use when modulation starts.

| FFA number | Output Frequency (kHz) | Step Size (Hz) |

|------------|------------------------|----------------|

| 0          | 125.000                | 0              |

| 1          | 124.970                | -30.4          |

| 2          | 124.939                | -60.8          |

| 3          | 124.909                | -91.2          |

| 4          | 124.878                | -121.6         |

| 5          | 124.848                | -152.0         |

| 6          | 124.818                | -182.4         |

| 7          | 124.787                | -212.8         |

| 8          | 124.757                | -243.2         |

| 9          | 124.726                | -273.6         |

| 10         | 124.696                | -304.0         |

| 11         | 124.666                | -334.4         |

| 12         | 124.635                | -364.8         |

| 13         | 124.605                | -395.2         |

| 14         | 124.574                | -425.6         |

| 15         | 124.544                | -456.0         |

## TABLE 24-4: SAMPLE FFA OUTPUT PERIODS/FREQUENCIES

| R/W-0/0              | R/W-0/0                                                                                                                                                | R/W-0/0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | U-0          | R/W-0/0                                               | R/W-0/0          | R/W-0/0           | R/W-0/0    |  |  |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-------------------------------------------------------|------------------|-------------------|------------|--|--|

| PxMDLEN              | PxMDLPOL                                                                                                                                               | PxMDLBIT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |              |                                                       | PxMSR            | C<3:0>            |            |  |  |

| bit 7                |                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              |                                                       |                  |                   | bit (      |  |  |

|                      |                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              |                                                       |                  |                   |            |  |  |

| Legend:              |                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              |                                                       |                  |                   |            |  |  |

| R = Readable         |                                                                                                                                                        | W = Writable b                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |              | •                                                     | nented bit, read |                   |            |  |  |

| u = Bit is unchanged |                                                                                                                                                        | x = Bit is unknown                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |              | -n/n = Value at POR and BOR/Value at all other Resets |                  |                   |            |  |  |

| '1' = Bit is set     |                                                                                                                                                        | '0' = Bit is clea                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | red          |                                                       |                  |                   |            |  |  |

| bit 7                | PxMDLEN: P                                                                                                                                             | SMC Periodic N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | lodulation I | Mode Enable bit                                       |                  |                   |            |  |  |

|                      |                                                                                                                                                        | is active when in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |              | elected by PxMS                                       | SRC<3:0> is in i | ts active state ( | see PxMPOL |  |  |

|                      |                                                                                                                                                        | module is alway                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              |                                                       |                  |                   |            |  |  |

| bit 6                |                                                                                                                                                        | PSMC Periodic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |              | ,                                                     |                  |                   |            |  |  |

|                      |                                                                                                                                                        | is active when the sactive |              |                                                       |                  |                   |            |  |  |

| bit 5                |                                                                                                                                                        | SMC Periodic N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |              |                                                       |                  | <b>U</b> (        | 0,         |  |  |

|                      | PxMDLEN = 1 AND PxMSRC<3:0> = 0000                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              |                                                       |                  |                   |            |  |  |

|                      | 1 = PSMCx is active when the PxMDLPOL equals logic '0'                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              |                                                       |                  |                   |            |  |  |

|                      | <ul> <li>0 = PSMCx is active when the PxMDLPOL equals logic '1'</li> <li>PxMDLEN = 0 OR (PxMDLEN = 1 and PxMSRC&lt;3:0&gt; &lt;&gt; '0000')</li> </ul> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              |                                                       |                  |                   |            |  |  |

|                      |                                                                                                                                                        | ct module opera                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              |                                                       |                  |                   |            |  |  |

| bit 4                | Unimplemented: Read as '0'                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              |                                                       |                  |                   |            |  |  |

| bit 3-0              | PxMSRC<3:0> PSMC Periodic Modulation Source Selection bits                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              |                                                       |                  |                   |            |  |  |

|                      | 1111 = Reserved                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              |                                                       |                  |                   |            |  |  |

|                      | 1110 = Rese                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              |                                                       |                  |                   |            |  |  |

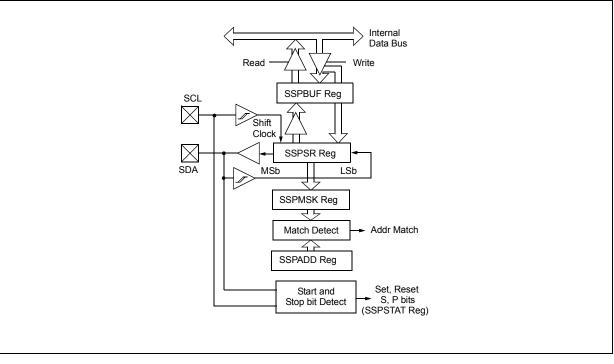

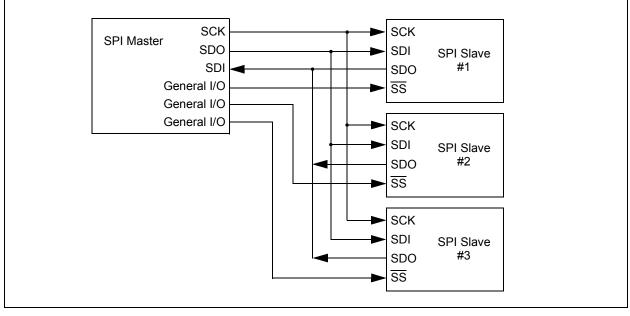

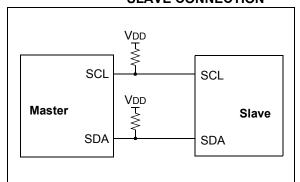

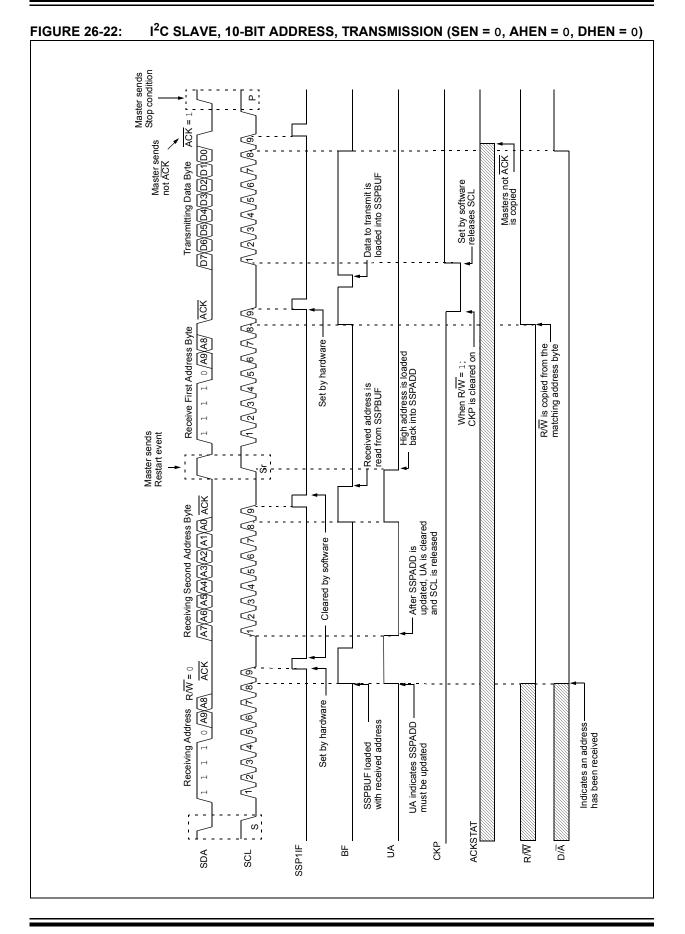

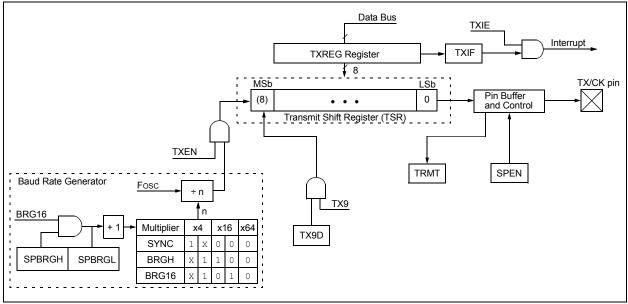

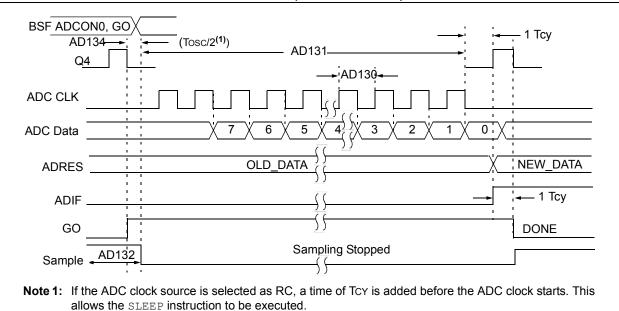

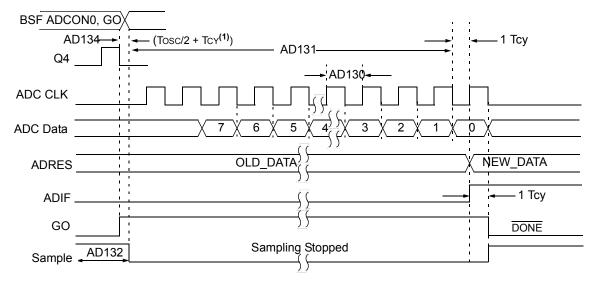

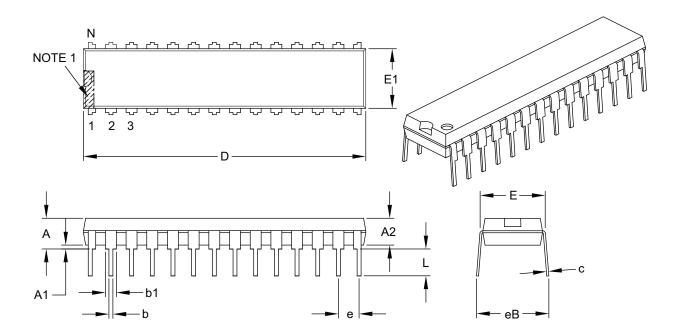

|                      | 1101 = Reserved<br>1100 = Reserved                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              |                                                       |                  |                   |            |  |  |