Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                   |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PSMC, PWM, WDT                                |

| Number of I/O              | 24                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 512 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 11x12b; D/A 1x8b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-UFQFN Exposed Pad                                                       |

| Supplier Device Package    | 28-UQFN (4x4)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1783-e-mv |

# 3.1.1 READING PROGRAM MEMORY AS DATA

There are two methods of accessing constants in program memory. The first method is to use tables of RETLW instructions. The second method is to set an FSR to point to the program memory.

#### 3.1.1.1 RETLW Instruction

The RETLW instruction can be used to provide access to tables of constants. The recommended way to create such a table is shown in Example 3-1.

#### EXAMPLE 3-1: RETLW INSTRUCTION

```

constants

BRW

;Add Index in W to

;program counter to

;select data

RETLW DATAO

;Index0 data

RETLW DATA1

;Index1 data

RETLW DATA2

RETLW DATA3

my function

;... LOTS OF CODE ...

MOVLW DATA INDEX

call constants

;... THE CONSTANT IS IN W

```

The BRW instruction makes this type of table very simple to implement. If your code must remain portable with previous generations of microcontrollers, then the BRW instruction is not available so the older table read method must be used.

#### 3.1.1.2 Indirect Read with FSR

The program memory can be accessed as data by setting bit 7 of the FSRxH register and reading the matching INDFx register. The MOVIW instruction will place the lower 8 bits of the addressed word in the W register. Writes to the program memory cannot be performed via the INDF registers. Instructions that access the program memory via the FSR require one extra instruction cycle to complete. Example 3-2 demonstrates accessing the program memory via an FSR.

The high directive will set bit<7> if a label points to a location in program memory.

# EXAMPLE 3-2: ACCESSING PROGRAM MEMORY VIA FSR

```

constants

RETLW DATA0

;Index0 data

RETLW DATA1

;Index1 data

RETIW DATA2

RETLW DATA3

my function

; ... LOTS OF CODE ...

MOVLW LOW constants

MOVWF FSR1L

MOVLW

HIGH constants

MOVWF

FSR1H

MOVIW

0[FSR1]

; THE PROGRAM MEMORY IS IN W

```

**TABLE 3-8:** SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

| Addr | Name                                   | Bit 7                                   | Bit 6     | Bit 5     | Bit 4     | Bit 3    | Bit 2          | Bit 1         | Bit 0     | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|------|----------------------------------------|-----------------------------------------|-----------|-----------|-----------|----------|----------------|---------------|-----------|----------------------|---------------------------------|

| Ban  | k 16                                   |                                         |           |           |           |          |                |               |           |                      |                                 |

| 80Ch |                                        |                                         |           |           |           |          |                |               |           |                      |                                 |

| 810h | _                                      | Unimplemente                            | d         |           |           |          |                |               |           | _                    | _                               |

| 811h | PSMC1CON                               | PSMC1EN                                 | PSMC1LD   | PSMC1DBFE | PSMC1DBRE |          | P1MOD          | E<3:0>        |           | 0000 0000            | 0000 0000                       |

| 812h | PSMC1MDL                               | P1MDLEN                                 | P1MDLPOL  | P1MDLBIT  | _         |          | P1MSR          | C<3:0>        |           | 000- 0000            | 000- 0000                       |

| 813h | PSMC1SYNC                              | _                                       | _         | -         | _         | -        | _              | P1SYN         | C<1:0>    | 00                   | 00                              |

| 814h | PSMC1CLK                               | _                                       | _         | P1CPF     | RE<1:0>   | _        | _              | P1CSR         | C<1:0>    | 0000                 | 0000                            |

| 815h | PSMC10EN                               | _                                       | _         | P10EF     | P10EE     | P10ED    | P10EC          | P10EB         | P10EA     | 00 0000              | 00 0000                         |

| 816h | PSMC1POL                               | _                                       | P1INPOL   | P1POLF    | P1POLE    | P1POLD   | P1POLC         | P1POLB        | P1POLA    | -000 0000            | -000 0000                       |

| 817h | PSMC1BLNK                              | _                                       | _         | P1FEB     | M<1:0>    | _        | _              | P1REB         | M<1:0>    | 0000                 | 0000                            |

| 818h | PSMC1REBS                              | P1REBIN                                 | _         | _         | _         | P1REBSC3 | P1REBSC2       | P1REBSC1      | _         | 0 000-               | 0 000-                          |

| 819h | PSMC1FEBS                              | P1FEBIN                                 | _         | _         | _         | P1FEBSC3 | P1FEBSC2       | P1FEBSC1      | _         | 0 000-               | 0 000-                          |

| 81Ah | PSMC1PHS                               | P1PHSIN                                 | _         | _         | _         | P1PHSC3  | P1PHSC2        | P1PHSC1       | P1PHST    | 0 0000               | 0 0000                          |

| 81Bh | PSMC1DCS                               | P1DCSIN                                 | _         | _         | _         | P1DCSC3  | P1DCSC2        | P1DCSC1       | P1DCST    | 0 0000               | 0 0000                          |

| 81Ch | PSMC1PRS                               | P1PRSIN                                 | _         | _         | _         | P1PRSC3  | P1PRSC2        | P1PRSC1       | P1PRST    | 0 0000               | 0 0000                          |

| 81Dh | PSMC1ASDC                              | P1ASE                                   | P1ASDEN   | P1ARSEN   | _         | _        | _              | _             | P1ASDOV   | 0000                 | 0000                            |

| 81Eh | PSMC1ASDL                              | _                                       | _         | P1ASDLF   | P1ASDLE   | P1ASDLD  | P1ASDLC        | P1ASDLB       | P1ASDLA   | 00 0000              | 00 0000                         |

| 81Fh | PSMC1ASDS                              | P1ASDSIN                                | _         | _         | _         | P1ASDSC3 | P1ASDSC2       | P1ASDSC1      | _         | 0 000-               | 0 000-                          |

| 820h | PSMC1INT                               | P1TOVIE                                 | P1TPHIE   | P1TDCIE   | P1TPRIE   | P1TOVIF  | P1TPHIF        | P1TDCIF       | P1TPRIF   | 0000 0000            | 0000 0000                       |

| 821h | PSMC1PHL                               | Phase Low Cor                           | unt       |           |           |          |                |               |           | 0000 0000            | 0000 0000                       |

| 822h | PSMC1PHH                               | Phase High Co                           | ount      |           |           |          |                |               |           | 0000 0000            | 0000 0000                       |

| 823h | PSMC1DCL                               | Duty Cycle Lov                          | w Count   |           |           |          |                |               |           | 0000 0000            | 0000 0000                       |

| 824h | PSMC1DCH                               | Duty Cycle Hig                          | h Count   |           |           |          |                |               |           | 0000 0000            | 0000 0000                       |

| 825h | PSMC1PRL                               | Period Low Co                           | unt       |           |           |          |                |               |           | 0000 0000            | 0000 0000                       |

| 826h | PSMC1PRH                               | Period High Co                          | ount      |           |           |          |                |               |           | 0000 0000            | 0000 0000                       |

| 827h | PSMC1TMRL                              | Time base Lov                           | v Counter |           |           |          |                |               |           | 0000 0001            | 0000 0001                       |

| 828h | PSMC1TMRH                              | Time base Hig                           | h Counter |           |           |          |                |               |           | 0000 0000            | 0000 0000                       |

| 829h | PSMC1DBR rising Edge Dead-band Counter |                                         |           |           |           |          |                |               | 0000 0000 | 0000 0000            |                                 |

| 82Ah | PSMC1DBF                               | 3 3 3 3 3 3 3 3 3 3 3 3 3 3 3 3 3 3 3 3 |           |           |           |          |                |               | 0000 0000 | 0000 0000            |                                 |

| 82Bh | PSMC1BLKR                              | rising Edge Blanking Counter            |           |           |           |          |                | 0000 0000     | 0000 0000 |                      |                                 |

| 82Ch | PSMC1BLKF                              | Falling Edge Blanking Counter           |           |           |           |          |                | 0000 0000     | 0000 0000 |                      |                                 |

| 82Dh | PSMC1FFA                               | _                                       | _         | _         | _         | Frac     | tional Frequen | cy Adjust Reg | ister     | 0000                 | 0000                            |

| 82Eh | PSMC1STR0                              | _                                       | _         | P1STRF    | P1STRE    | P1STRD   | P1STRC         | P1STRB        | P1STRA    | 00 0001              | 00 0001                         |

| 82Fh | PSMC1STR1                              | P1SYNC                                  | _         | _         | _         | _        | _              | P1LSMEN       | P1HSMEN   | 000                  | 000                             |

| 830h | _                                      | Unimplemente                            | d         |           |           |          |                |               |           | _                    | _                               |

x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'. Legend:

These registers can be addressed from any bank. Unimplemented, read as '1'. PIC16F1782/3 only. Note

1: 2:

3:

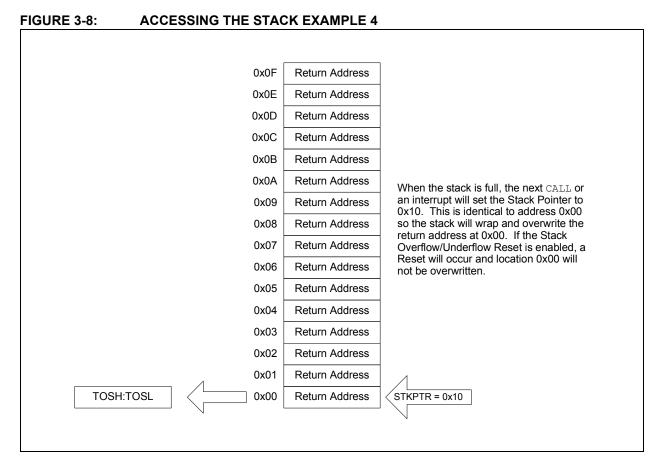

## 3.5.2 OVERFLOW/UNDERFLOW RESET

If the STVREN bit in Configuration Words is programmed to '1', the device will be reset if the stack is PUSHed beyond the sixteenth level or POPed beyond the first level, setting the appropriate bits (STKOVF or STKUNF, respectively) in the PCON register.

## 3.6 Indirect Addressing

The INDFn registers are not physical registers. Any instruction that accesses an INDFn register actually accesses the register at the address specified by the File Select Registers (FSR). If the FSRn address specifies one of the two INDFn registers, the read will return '0' and the write will not occur (though Status bits may be affected). The FSRn register value is created by the pair FSRnH and FSRnL.

The FSR registers form a 16-bit address that allows an addressing space with 65536 locations. These locations are divided into three memory regions:

- · Traditional Data Memory

- · Linear Data Memory

- · Program Flash Memory

## 6.6 Register Definitions: Oscillator Control

#### REGISTER 6-1: OSCCON: OSCILLATOR CONTROL REGISTER

| R/W-0/0 | R/W-0/0 | R/W-1/1 | R/W-1/1 | R/W-1/1 | U-0 | R/W-0/0 | R/W-0/0 |

|---------|---------|---------|---------|---------|-----|---------|---------|

| SPLLEN  |         | IRCF    | <3:0>   |         | _   | SCS-    | <1:0>   |

| bit 7   |         |         |         |         |     |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7 SPLLEN: Software PLL Enable bit

If PLLEN in Configuration Words = 1:

SPLLEN bit is ignored. 4x PLL is always enabled (subject to oscillator requirements)

If PLLEN in Configuration Words = 0:

1 = 4x PLL Is enabled 0 = 4x PLL is disabled

bit 6-3 IRCF<3:0>: Internal Oscillator Frequency Select bits

$1111 = 16 \text{ MHz HF or } 32 \text{ MHz HF}^{(2)}$

$1110 = 8 \text{ MHz or } 32 \text{ MHz HF}^{(2)}$

1101 = 4 MHz HF

1100 = 2 MHz HF

1011 = 1 MHz HF

$1010 = 500 \text{ kHz HF}^{(1)}$

1001 = 250 kHz HF<sup>(1)</sup>

$1000 = 125 \text{ kHz HF}^{(1)}$

0111 = 500 kHz MF (default upon Reset)

0110 = 250 kHz MF

0101 = **125** kHz MF

0100 = 62.5 kHz MF

0011 = 31.25 kHz HF<sup>(1)</sup>

0010 = 31.25 kHz MF

000x = 31 kHz LF

bit 2 **Unimplemented:** Read as '0'

bit 1-0 SCS<1:0>: System Clock Select bits

1x = Internal oscillator block

01 = Timer1 oscillator

00 = Clock determined by FOSC<2:0> in Configuration Words.

Note 1: Duplicate frequency derived from HFINTOSC.

2: 32 MHz when SPLLEN bit is set. Refer to Section 6.2.2.6 "32 MHz Internal Oscillator Frequency Selection".

#### **REGISTER 8-4:** PIE4: PERIPHERAL INTERRUPT ENABLE REGISTER 4

| U-0   | U-0 | R/W-0/0  | R/W-0/0  | U-0 | U-0 | R/W-0/0  | R/W-0/0  |

|-------|-----|----------|----------|-----|-----|----------|----------|

| _     | _   | PSMC2TIE | PSMC1TIE | _   | _   | PSMC2SIE | PSMC1SIE |

| bit 7 |     |          |          |     |     |          | bit 0    |

Legend: R = Readable bit

W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set

'0' = Bit is cleared

bit 7-6 Unimplemented: Read as '0'

bit 5 PSMC2TIE: PSMC2 Time Base Interrupt Enable bit

> 1 = Enables PSMC2 time base generated interrupts 0 = Disables PSMC2 time base generated interrupts

bit 4 PSMC1TIE: PSMC1 Time Base Interrupt Enable bit

1 = Enables PSMC1 time base generated interrupts

0 = Disables PSMC1 time base generated interrupts

bit 3-2 Unimplemented: Read as '0'

bit 1 PSMC2SIE: PSMC2 Auto-Shutdown Interrupt Enable bit

> 1 = Enables PSMC2 auto-shutdown interrupts 0 = Disables PSMC2 auto-shutdown interrupts

PSMC1SIE: PSMC1 Auto-Shutdown Interrupt Enable bit bit 0

> 1 = Enables PSMC1 auto-shutdown interrupts 0 = Disables PSMC1 auto-shutdown interrupts

Note: Bit PEIE of the INTCON register must be

set to enable any peripheral interrupt.

# 9.0 POWER-DOWN MODE (SLEEP)

The Power-down mode is entered by executing a SLEEP instruction.

Upon entering Sleep mode, the following conditions exist:

- WDT will be cleared but keeps running, if enabled for operation during Sleep.

- 2. PD bit of the STATUS register is cleared.

- 3. TO bit of the STATUS register is set.

- 4. CPU clock is disabled.

- 5. 31 kHz LFINTOSC is unaffected and peripherals that operate from it may continue operation in Sleep.

- Timer1 and peripherals that operate from Timer1 continue operation in Sleep when the Timer1 clock source selected is:

- LFINTOSC

- T1CKI

- Timer1 oscillator

- ADC is unaffected, if the dedicated FRC oscillator is selected.

- 8. I/O ports maintain the status they had before SLEEP was executed (driving high, low or high-impedance).

- Resets other than WDT are not affected by Sleep mode.

Refer to individual chapters for more details on peripheral operation during Sleep.

To minimize current consumption, the following conditions should be considered:

- · I/O pins should not be floating

- External circuitry sinking current from I/O pins

- Internal circuitry sourcing current from I/O pins

- · Current draw from pins with internal weak pull-ups

- · Modules using 31 kHz LFINTOSC

- · Modules using Timer1 oscillator

I/O pins that are high-impedance inputs should be pulled to VDD or Vss externally to avoid switching currents caused by floating inputs.

Examples of internal circuitry that might be sourcing current include modules such as the DAC and FVR modules. See Section 19.0 "Digital-to-Analog Converter (DAC) Module" and Section 15.0 "Fixed Voltage Reference (FVR)" for more information on these modules.

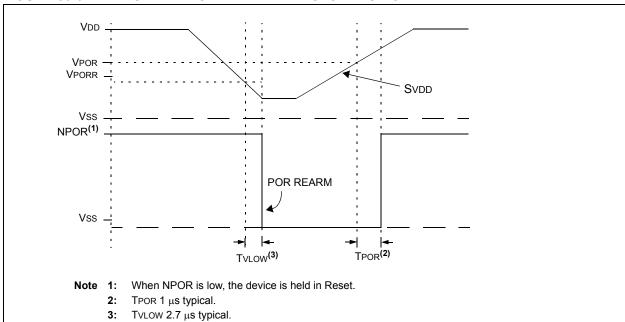

### 9.1 Wake-up from Sleep

The device can wake-up from Sleep through one of the following events:

- 1. External Reset input on MCLR pin, if enabled

- 2. BOR Reset, if enabled

- 3. POR Reset

- 4. Watchdog Timer, if enabled

- 5. Any external interrupt

- Interrupts by peripherals capable of running during Sleep (see individual peripheral for more information)

The first three events will cause a device Reset. The last three events are considered a continuation of program execution. To determine whether a device Reset or wake-up event occurred, refer to Section 5.12 "Determining the Cause of a Reset".

When the SLEEP instruction is being executed, the next instruction (PC + 1) is prefetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be enabled. Wake-up will occur regardless of the state of the GIE bit. If the GIE bit is disabled, the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is enabled, the device executes the instruction after the SLEEP instruction, the device will then call the Interrupt Service Routine. In cases where the execution of the instruction following SLEEP is not desirable, the user should have a NOP after the SLEEP instruction.

The WDT is cleared when the device wakes up from Sleep, regardless of the source of wake-up.

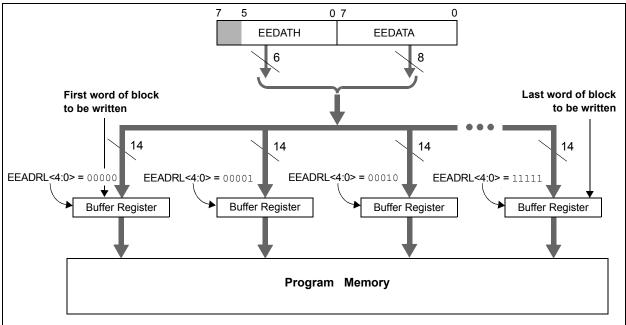

### FIGURE 12-2: BLOCK WRITES TO FLASH PROGRAM MEMORY WITH 32 WRITE LATCHES

#### **EXAMPLE 12-4: ERASING ONE ROW OF PROGRAM MEMORY**

```

; This row erase routine assumes the following:

; 1. A valid address within the erase block is loaded in ADDRH:ADDRL

; 2. ADDRH and ADDRL are located in shared data memory 0x70 - 0x7F (common RAM)

BCF

INTCON, GIE ; Disable ints so required sequences will execute properly

BANKSEL

EEADRL

ADDRL, W

MOVF

; Load lower 8 bits of erase address boundary

MOVWF

EEADRL

MOVF

ADDRH,W

; Load upper 6 bits of erase address boundary

MOVWF

EEADRH

BSF

EECON1, EEPGD ; Point to program memory

EECON1, CFGS

; Not configuration space

BCF

BSF

EECON1, FREE

; Specify an erase operation

EECON1, WREN

; Enable writes

BSF

M.TVOM

55h

; Start of required sequence to initiate erase

MOVWF

EECON2

; Write 55h

MOVLW

0AAh

MOVWF

EECON2

; Write AAh

BSF

EECON1, WR

; Set WR bit to begin erase

NOP

; Any instructions here are ignored as processor

; halts to begin erase sequence

NOP

; Processor will stop here and wait for erase complete.

; after erase processor continues with 3rd instruction

BCF

EECON1, WREN

; Disable writes

BSF

INTCON, GIE

; Enable interrupts

```

#### REGISTER 13-21: WPUC: WEAK PULL-UP PORTC REGISTER

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| WPUC7   | WPUC6   | WPUC5   | WPUC4   | WPUC3   | WPUC2   | WPUC1   | WPUC0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-0 WPUC<7:0>: Weak Pull-up Register bits

1 = Pull-up enabled0 = Pull-up disabled

Note 1: Global WPUEN bit of the OPTION\_REG register must be cleared for individual pull-ups to be enabled.

2: The weak pull-up device is automatically disabled if the pin is in configured as an output.

#### REGISTER 13-22: ODCONC: PORTC OPEN DRAIN CONTROL REGISTER

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| ODC7    | ODC6    | ODC5    | ODC4    | ODC3    | ODC2    | ODC1    | ODC0    |

| bit 7   |         |         |         |         |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-0 ODC<7:0>: PORTC Open Drain Enable bits

For RC<7:0> pins, respectively

1 = Port pin operates as open-drain drive (sink current only)

0 = Port pin operates as standard push-pull drive (source and sink current)

#### REGISTER 13-23: SLRCONC: PORTC SLEW RATE CONTROL REGISTER

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| SLRC7   | SLRC6   | SLRC5   | SLRC4   | SLRC3   | SLRC2   | SLRC1   | SLRC0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-0 SLRC<7:0>: PORTC Slew Rate Enable bits

For RC<7:0> pins, respectively 1 = Port pin slew rate is limited

0 = Port pin slews at maximum rate

# 20.10 Analog Input Connection Considerations

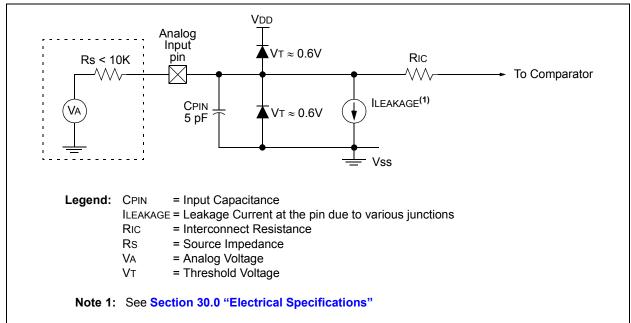

A simplified circuit for an analog input is shown in Figure 20-4. Since the analog input pins share their connection with a digital input, they have reverse biased ESD protection diodes to VDD and Vss. The analog input, therefore, must be between Vss and VDD. If the input voltage deviates from this range by more than 0.6V in either direction, one of the diodes is forward biased and a latch-up may occur.

A maximum source impedance of 10 k $\Omega$  is recommended for the analog sources. Also, any external component connected to an analog input pin, such as a capacitor or a Zener diode, should have very little leakage current to minimize inaccuracies introduced.

- Note 1: When reading a PORT register, all pins configured as analog inputs will read as a '0'. Pins configured as digital inputs will convert as an analog input, according to the input specification.

- Analog levels on any pin defined as a digital input, may cause the input buffer to consume more current than is specified.

#### 20.10.1 ALTERNATE PIN LOCATIONS

This module incorporates I/O pins that can be moved to other locations with the use of the alternate pin function register APFCON. To determine which pins can be moved and what their default locations are upon a Reset, see Section 13.1 "Alternate Pin Function" for more information.

## FIGURE 20-4: ANALOG INPUT MODEL

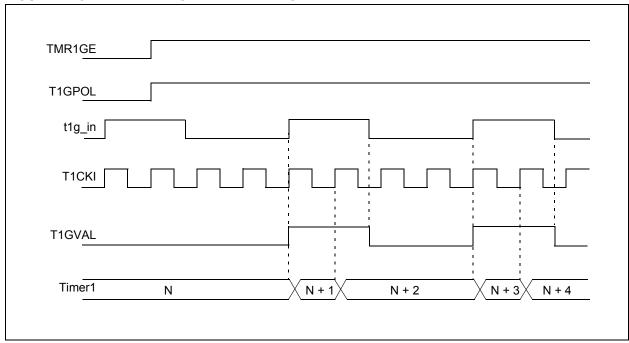

FIGURE 22-3: TIMER1 GATE ENABLE MODE

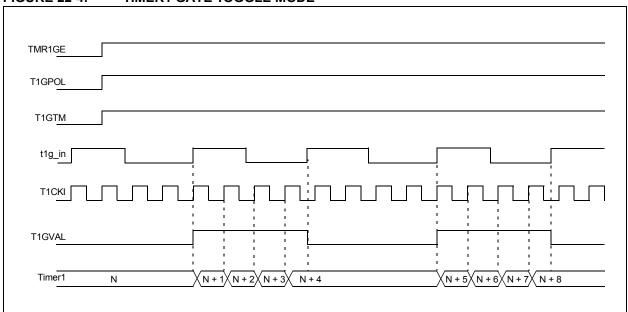

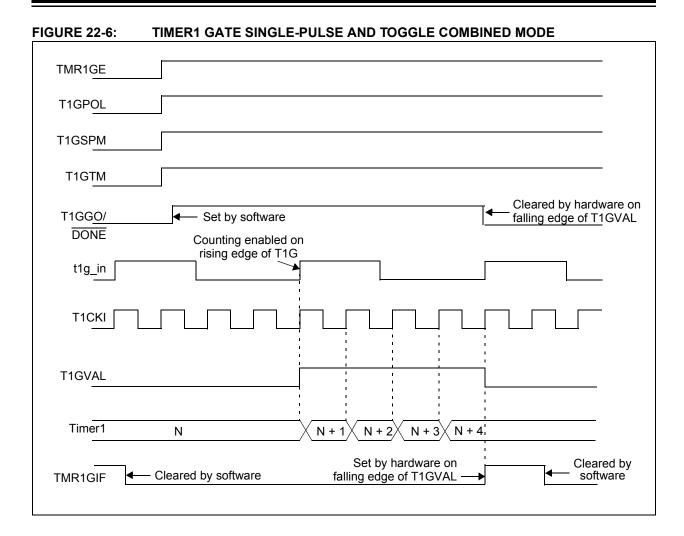

FIGURE 22-4: TIMER1 GATE TOGGLE MODE

### 26.6 I<sup>2</sup>C Master Mode

Master mode is enabled by setting and clearing the appropriate SSPM bits in the SSPCON1 register and by setting the SSPEN bit. In Master mode, the SDA and SCK pins must be configured as inputs. The MSSP peripheral hardware will override the output driver TRIS controls when necessary to drive the pins low.

Master mode of operation is supported by interrupt generation on the detection of the Start and Stop conditions. The Stop (P) and Start (S) bits are cleared from a Reset or when the MSSP module is disabled. Control of the  $\rm I^2C$  bus may be taken when the P bit is set, or the bus is Idle.

In Firmware Controlled Master mode, user code conducts all I<sup>2</sup>C bus operations based on Start and Stop bit condition detection. Start and Stop condition detection is the only active circuitry in this mode. All other communication is done by the user software directly manipulating the SDA and SCL lines.

The following events will cause the SSP Interrupt Flag bit, SSP1IF, to be set (SSP interrupt, if enabled):

- · Start condition detected

- · Stop condition detected

- · Data transfer byte transmitted/received

- · Acknowledge transmitted/received

- · Repeated Start generated

- Note 1: The MSSP module, when configured in I<sup>2</sup>C Master mode, does not allow queueing of events. For instance, the user is not allowed to initiate a Start condition and immediately write the SSPBUF register to initiate transmission before the Start condition is complete. In this case, the SSPBUF will not be written to and the WCOL bit will be set, indicating that a write to the SSPBUF did not occur

- 2: When in Master mode, Start/Stop detection is masked and an interrupt is generated when the SEN/PEN bit is cleared and the generation is complete.

#### 26.6.1 I<sup>2</sup>C MASTER MODE OPERATION

The master device generates all of the serial clock pulses and the Start and Stop conditions. A transfer is ended with a Stop condition or with a Repeated Start condition. Since the Repeated Start condition is also the beginning of the next serial transfer, the I<sup>2</sup>C bus will not be released.

In Master Transmitter mode, serial data is output through SDA, while SCL outputs the serial clock. The first byte transmitted contains the slave <u>address</u> of the receiving device (7 bits) and the Read/Write (R/W) bit. In this case, the R/W bit will be logic '0'. Serial data is transmitted 8 bits at a time. After each byte is transmitted, an Acknowledge bit is received. Start and Stop conditions are output to indicate the beginning and the end of a serial transfer.

In Master Receive mode, the first byte transmitted contains the slave address of the transmitting device (7 bits) and the R/W bit. In this case, the R/W bit will be logic '1'. Thus, the first byte transmitted is a 7-bit slave address followed by a '1' to indicate the receive bit. Serial data is received via SDA, while SCL outputs the serial clock. Serial data is received 8 bits at a time. After each byte is received, an Acknowledge bit is transmitted. Start and Stop conditions indicate the beginning and end of transmission.

A Baud Rate Generator is used to set the clock frequency output on SCL. See Section 26.7 "Baud Rate Generator" for more detail.

#### 27.1.1.5 TSR Status

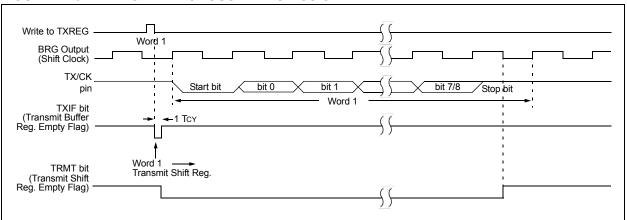

The TRMT bit of the TXSTA register indicates the status of the TSR register. This is a read-only bit. The TRMT bit is set when the TSR register is empty and is cleared when a character is transferred to the TSR register from the TXREG. The TRMT bit remains clear until all bits have been shifted out of the TSR register. No interrupt logic is tied to this bit, so the user has to poll this bit to determine the TSR status.

**Note:** The TSR register is not mapped in data memory, so it is not available to the user.

### 27.1.1.6 Transmitting 9-Bit Characters

The EUSART supports 9-bit character transmissions. When the TX9 bit of the TXSTA register is set, the EUSART will shift 9 bits out for each character transmitted. The TX9D bit of the TXSTA register is the ninth, and Most Significant, data bit. When transmitting 9-bit data, the TX9D data bit must be written before writing the eight Least Significant bits into the TXREG. All 9 bits of data will be transferred to the TSR shift register immediately after the TXREG is written.

A special 9-bit Address mode is available for use with multiple receivers. See **Section 27.1.2.7 "Address Detection"** for more information on the address mode.

#### 27.1.1.7 Asynchronous Transmission Set-up:

- Initialize the SPBRGH, SPBRGL register pair and the BRGH and BRG16 bits to achieve the desired baud rate (see Section 27.4 "EUSART Baud Rate Generator (BRG)").

- Enable the asynchronous serial port by clearing the SYNC bit and setting the SPEN bit.

- If 9-bit transmission is desired, set the TX9 control bit. A set ninth data bit will indicate that the 8 Least Significant data bits are an address when the receiver is set for address detection.

- Set SCKP bit if inverted transmit is desired.

- Enable the transmission by setting the TXEN control bit. This will cause the TXIF interrupt bit to be set.

- If interrupts are desired, set the TXIE interrupt enable bit of the PIE1 register. An interrupt will occur immediately provided that the GIE and PEIE bits of the INTCON register are also set.

- 7. If 9-bit transmission is selected, the ninth bit should be loaded into the TX9D data bit.

- Load 8-bit data into the TXREG register. This will start the transmission.

#### FIGURE 27-3: ASYNCHRONOUS TRANSMISSION

TABLE 29-3: INSTRUCTION SET (CONTINUED)

| Mnemonic,<br>Operands |      | Description                                   | Cycles |     | 14-Bit | Opcode | )    | Status   | Notes |

|-----------------------|------|-----------------------------------------------|--------|-----|--------|--------|------|----------|-------|

|                       |      | Description                                   | Cycles | MSb |        |        | LSb  | Affected | Notes |

|                       |      | CONTROL OPERA                                 | TIONS  |     |        |        |      |          |       |

| BRA                   | k    | Relative Branch                               | 2      | 11  | 001k   | kkkk   | kkkk |          |       |

| BRW                   | _    | Relative Branch with W                        | 2      | 00  | 0000   | 0000   | 1011 |          |       |

| CALL                  | k    | Call Subroutine                               | 2      | 10  | 0kkk   | kkkk   | kkkk |          |       |

| CALLW                 | _    | Call Subroutine with W                        | 2      | 00  | 0000   | 0000   | 1010 |          |       |

| GOTO                  | k    | Go to address                                 | 2      | 10  | 1kkk   | kkkk   | kkkk |          |       |

| RETFIE                | k    | Return from interrupt                         | 2      | 00  | 0000   | 0000   | 1001 |          |       |

| RETLW                 | k    | Return with literal in W                      | 2      | 11  | 0100   | kkkk   | kkkk |          |       |

| RETURN                | _    | Return from Subroutine                        | 2      | 00  | 0000   | 0000   | 1000 |          |       |

|                       |      | INHERENT OPERA                                | TIONS  |     |        |        |      | •        |       |

| CLRWDT                | _    | Clear Watchdog Timer                          | 1      | 00  | 0000   | 0110   | 0100 | TO, PD   |       |

| NOP                   | _    | No Operation                                  | 1      | 00  | 0000   | 0000   | 0000 |          |       |

| OPTION                | _    | Load OPTION_REG register with W               | 1      | 00  | 0000   | 0110   | 0010 |          |       |

| RESET                 | _    | Software device Reset                         | 1      | 00  | 0000   | 0000   | 0001 |          |       |

| SLEEP                 | _    | Go into Standby mode                          | 1      | 00  | 0000   | 0110   | 0011 | TO, PD   |       |

| TRIS                  | f    | Load TRIS register with W                     | 1      | 00  | 0000   | 0110   | Offf |          |       |

|                       |      | C-COMPILER OPT                                | IMIZED |     |        |        |      | •        |       |

| ADDFSR                | n, k | Add Literal k to FSRn                         | 1      | 11  | 0001   | 0nkk   | kkkk |          |       |

| MOVIW                 | n mm | Move Indirect FSRn to W with pre/post inc/dec | 1      | 0.0 | 0000   | 0001   | 0nmm | Z        | 2, 3  |

|                       |      | modifier, mm                                  |        |     |        |        |      |          |       |

|                       | k[n] | Move INDFn to W, Indexed Indirect.            | 1      | 11  | 1111   | 0nkk   | kkkk | Z        | 2     |

| MOVWI                 | n mm | Move W to Indirect FSRn with pre/post inc/dec | 1      | 00  | 0000   | 0001   | 1nmm |          | 2, 3  |

|                       |      | modifier, mm                                  |        |     |        |        |      |          |       |

|                       | k[n] | Move W to INDFn, Indexed Indirect.            | 1      | 11  | 1111   | 1nkk   | kkkk |          | 2     |

Note 1: If the Program Counter (PC) is modified, or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

<sup>2:</sup> If this instruction addresses an INDF register and the MSb of the corresponding FSR is set, this instruction will require one additional instruction cycle.

<sup>3:</sup> See Table in the MOVIW and MOVWI instruction descriptions.

**TABLE 30-9: CLKOUT AND I/O TIMING PARAMETERS**

| Standa       | rd Operating | g Conditions (unless otherwise stated)                    |               |          |          |       |                              |

|--------------|--------------|-----------------------------------------------------------|---------------|----------|----------|-------|------------------------------|

| Param<br>No. | Sym.         | Characteristic                                            | Min.          | Тур†     | Max.     | Units | Conditions                   |

| OS11         | TosH2ckL     | Fosc↑ to CLKOUT↓ (1)                                      | _             | _        | 70       | ns    | VDD = 3.3-5.0V               |

| OS12         | TosH2ckH     | Fosc↑ to CLKOUT↑ (1)                                      | _             | _        | 72       | ns    | VDD = 3.3-5.0V               |

| OS13         | TckL2ioV     | CLKOUT↓ to Port out valid <sup>(1)</sup>                  | _             | _        | 20       | ns    |                              |

| OS14         | TioV2ckH     | Port input valid before CLKOUT <sup>(1)</sup>             | Tosc + 200 ns | _        | _        | ns    |                              |

| OS15         | TosH2ioV     | Fosc↑ (Q1 cycle) to Port out valid                        | _             | 50       | 70*      | ns    | VDD = 3.3-5.0V               |

| OS16         | TosH2ioI     | Fosc↑ (Q2 cycle) to Port input invalid (I/O in hold time) | 50            | _        | _        | ns    | VDD = 3.3-5.0V               |

| OS17         | TioV2osH     | Port input valid to Fosc↑ (Q2 cycle) (I/O in setup time)  | 20            | _        | _        | ns    |                              |

| OS18*        | TioR         | Port output rise time                                     |               | 40<br>15 | 72<br>32 | ns    | VDD = 1.8V<br>VDD = 3.3-5.0V |

| OS19*        | TioF         | Port output fall time                                     | _             | 28<br>15 | 55<br>30 | ns    | VDD = 1.8V<br>VDD = 3.3-5.0V |

| OS20*        | Tinp         | INT pin input high or low time                            | 25            | _        | _        | ns    |                              |

| OS21*        | Tioc         | Interrupt-on-change new input level time                  | 25            | _        | _        | ns    |                              |

**Note 1:** Measurements are taken in RC mode where CLKOUT output is 4 x Tosc.

<sup>\*</sup> These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated.

**Note:** Unless otherwise noted, VIN = 5V, FOSC = 300 kHz, CIN = 0.1  $\mu F$ , TA = 25°C.

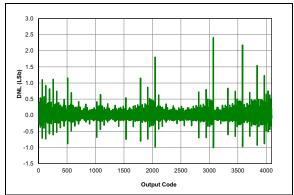

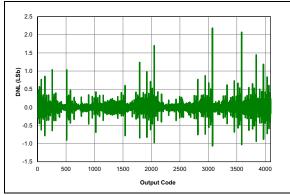

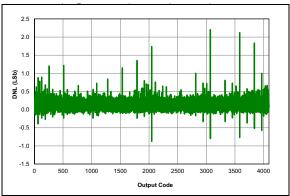

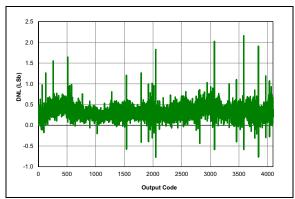

**FIGURE 31-85:** ADC 12-bit Mode, Single-Ended DNL, VDD = 3.0V,  $TAD = 1 \mu S$ ,  $25^{\circ}C$ .

FIGURE 31-86: ADC 12-bit Mode, Single-Ended DNL, VDD = 3.0V, TAD = 4  $\mu$ S, 25°C.

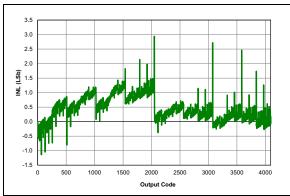

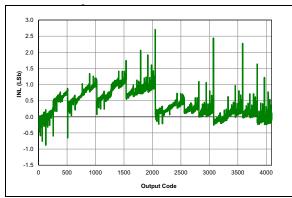

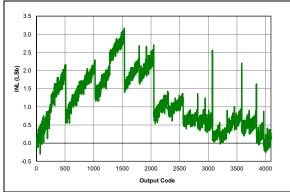

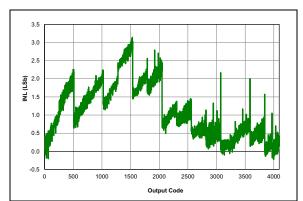

FIGURE 31-87: ADC 12-bit Mode, Single-Ended INL, VDD = 3.0V, TAD = 1  $\mu$ S, 25°C.

FIGURE 31-88: ADC 12-bit Mode, Single-Ended INL, VDD = 3.0V, TAD =  $4 \mu$ S, 25°C.

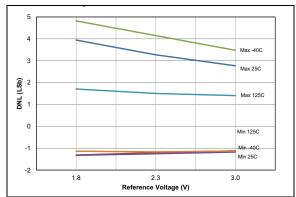

FIGURE 31-89: ADC 12-bit Mode, Single-Ended DNL, VDD = 3.0V, VREF = 3.0V.

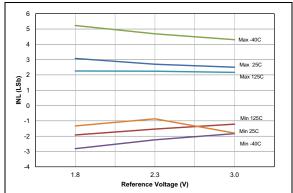

FIGURE 31-90: ADC 12-bit Mode, Single-Ended INL, VDD = 3.0V, VREF = 3.0V.

**Note:** Unless otherwise noted, VIN = 5V, FOSC = 300 kHz, CIN = 0.1  $\mu F$ , TA = 25°C.

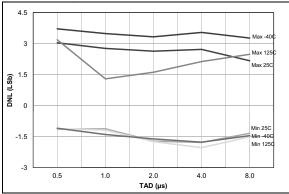

**FIGURE 31-91:** ADC 12-bit Mode, Single-Ended DNL, VDD = 3.0V, TAD = 1  $\mu$ S.

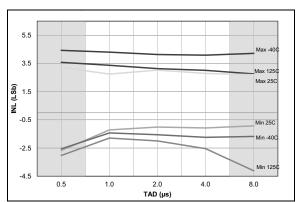

**FIGURE 31-92:** ADC 12-bit Mode, Single-Ended INL, VDD = 3.0V, TAD = 1  $\mu$ S.

FIGURE 31-93: ADC 12-bit Mode, Single-Ended DNL, VDD = 5.5V,  $TAD = 1 \mu S$ ,  $25^{\circ}C$ .

**FIGURE 31-94:** ADC 12-bit Mode, Single-Ended DNL, VDD = 5.5V,  $TAD = 4 \mu S$ ,  $25^{\circ}C$ .

**FIGURE 31-95:** ADC 12-bit Mode, Single-Ended INL, VDD = 5.5V, TAD = 1  $\mu$ S, 25°C.

**FIGURE 31-96:** ADC 12-bit Mode, Single-Ended INL, VDD = 5.5V, TAD =  $4 \mu S$ ,  $25^{\circ}C$ .

## 33.0 PACKAGING INFORMATION

# 33.1 Package Marking Information

28-Lead SPDIP (.300")

Example

28-Lead SOIC (7.50 mm)

Example

28-Lead SSOP (5.30 mm)

Example

**Legend:** XX...X Customer-specific information

Y Year code (last digit of calendar year)

YY Year code (last 2 digits of calendar year)

WW Week code (week of January 1 is week '01')

NNN Alphanumeric traceability code

(e3) Pb-free JEDEC® designator for Matte Tin (Sn)

This package is Pb-free. The Pb-free JEDEC designator (e3) can be found on the outer packaging for this package.

**Note**: In the event the full Microchip part number cannot be marked on one line, it will be carried over to the next line, thus limiting the number of available characters for customer-specific information.

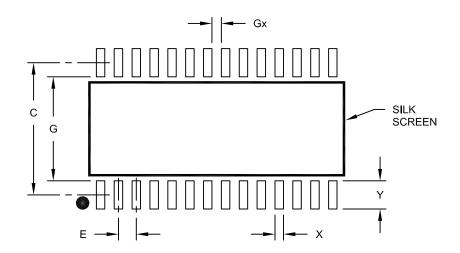

# 28-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

## RECOMMENDED LAND PATTERN

|                          | N   | <b>II</b> LLIMETER | S    |      |

|--------------------------|-----|--------------------|------|------|

| Dimension                | MIN | NOM                | MAX  |      |

| Contact Pitch            |     | 1.27 BSC           |      |      |

| Contact Pad Spacing      | С   |                    | 9.40 |      |

| Contact Pad Width (X28)  | Х   |                    |      | 0.60 |

| Contact Pad Length (X28) | Υ   |                    |      | 2.00 |

| Distance Between Pads    | Gx  | 0.67               |      |      |

| Distance Between Pads    | G   | 7.40               |      |      |

#### Notes:

Note:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2052A