Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PSMC, PWM, WDT                                |

| Number of I/O              | 24                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 512 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 11x12b; D/A 1x8b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 28-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1783-e-so |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 3.1.1 READING PROGRAM MEMORY AS DATA

There are two methods of accessing constants in program memory. The first method is to use tables of RETLW instructions. The second method is to set an FSR to point to the program memory.

#### 3.1.1.1 RETLW Instruction

The RETLW instruction can be used to provide access to tables of constants. The recommended way to create such a table is shown in Example 3-1.

EXAMPLE 3-1: RETLW INSTRUCTION

| constants         |                     |

|-------------------|---------------------|

| BRW               | ;Add Index in W to  |

|                   | ;program counter to |

|                   | ;select data        |

| RETLW DATA0       | ;Index0 data        |

| RETLW DATA1       | ;Index1 data        |

| RETLW DATA2       |                     |

| RETLW DATA3       |                     |

|                   |                     |

|                   |                     |

| my_function       |                     |

| ; LOTS OF CODE    |                     |

| MOVLW DATA_IN     | DEX                 |

| call constants    |                     |

| ; THE CONSTANT IS | IN W                |

| L                 |                     |

The BRW instruction makes this type of table very simple to implement. If your code must remain portable with previous generations of microcontrollers, then the BRW instruction is not available so the older table read method must be used.

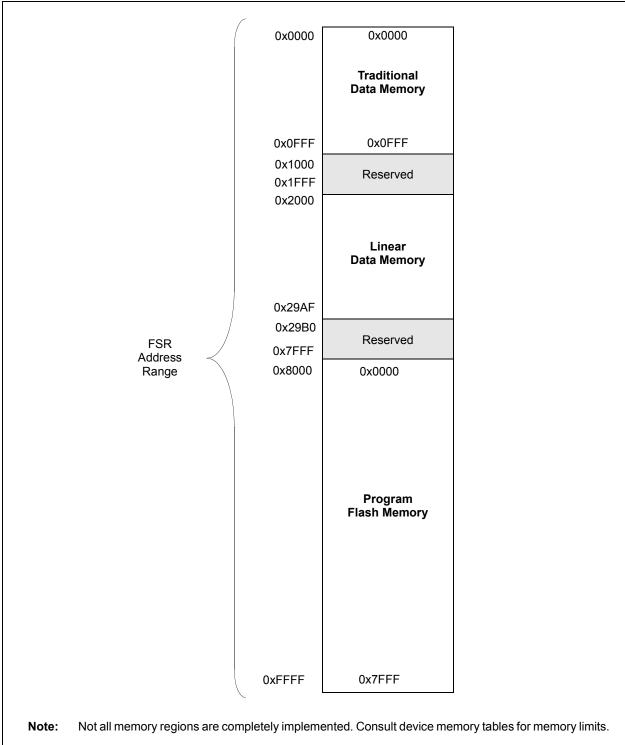

#### 3.1.1.2 Indirect Read with FSR

The program memory can be accessed as data by setting bit 7 of the FSRxH register and reading the matching INDFx register. The MOVIW instruction will place the lower 8 bits of the addressed word in the W register. Writes to the program memory cannot be performed via the INDF registers. Instructions that access the program memory via the FSR require one extra instruction cycle to complete. Example 3-2 demonstrates accessing the program memory via an FSR.

The high directive will set bit<7> if a label points to a location in program memory.

#### EXAMPLE 3-2: ACCESSING PROGRAM MEMORY VIA FSR

| constants  |                  |            |

|------------|------------------|------------|

| RETLW      | DATAO ;I         | ndex0 data |

| RETLW      | DATA1 ;I         | ndex1 data |

| RETLW      | DATA2            |            |

| RETLW      | data3            |            |

| my_functi  | on               |            |

| ; LO       | IS OF CODE       |            |

| MOVLW      | LOW constants    |            |

| MOVWF      | FSR1L            |            |

| MOVLW      | HIGH constant    | S          |

| MOVWF      | FSR1H            |            |

| MOVIW      | 0[FSR1]          |            |

| ; THE PROG | RAM MEMORY IS IN | 4 W        |

## 3.3.4 DEVICE MEMORY MAPS

The memory maps for Bank 0 through Bank 31 are shown in the tables in this section.

## TABLE 3-3: PIC16(L)F1782/3 MEMORY MAP (BANKS 0-7)

|      | BANK 0                        | •    | ,<br>BANK 1                   |      | BANK 2                        |      | ,<br>BANK 3                         |      | BANK 4                              |      | BANK 5                              |      | BANK 6                              |      | BANK 7                        |

|------|-------------------------------|------|-------------------------------|------|-------------------------------|------|-------------------------------------|------|-------------------------------------|------|-------------------------------------|------|-------------------------------------|------|-------------------------------|

| 000h |                               | 080h |                               | 100h |                               | 180h |                                     | 200h |                                     | 280h |                                     | 300h |                                     | 380h |                               |

|      | Core Registers<br>(Table 3-2)       |      | Core Registers<br>(Table 3-2)       |      | Core Registers<br>(Table 3-2)       |      | Core Registers<br>(Table 3-2)       |      | Core Registers<br>(Table 3-2) |

| 00Bh |                               | 08Bh |                               | 10Bh |                               | 18Bh |                                     | 20Bh |                                     | 28Bh |                                     | 30Bh |                                     | 38Bh |                               |

| 00Ch | PORTA                         | 08Ch | TRISA                         | 10Ch | LATA                          | 18Ch | ANSELA                              | 20Ch | WPUA                                | 28Ch | ODCONA                              | 30Ch | SLRCONA                             | 38Ch | INLVLA                        |

| 00Dh | PORTB                         | 08Dh | TRISB                         | 10Dh | LATB                          | 18Dh | ANSELB                              | 20Dh | WPUB                                | 28Dh | ODCONB                              | 30Dh | SLRCONB                             | 38Dh | INLVLB                        |

| 00Eh | PORTC                         | 08Eh | TRISC                         | 10Eh | LATC                          | 18Eh |                                     | 20Eh | WPUC                                | 28Eh | ODCONC                              | 30Eh | SLRCONC                             | 38Eh | INLVLC                        |

| 00Fh | _                             | 08Fh | —                             | 10Fh | —                             | 18Fh |                                     | 20Fh |                                     | 28Fh | —                                   | 30Fh | —                                   | 38Fh | _                             |

| 010h | PORTE                         | 090h | TRISE                         | 110h | —                             | 190h | _                                   | 210h | WPUE                                | 290h | —                                   | 310h | —                                   | 390h | INLVLE                        |

| 011h | PIR1                          | 091h | PIE1                          | 111h | CM1CON0                       | 191h | EEADRL                              | 211h | SSP1BUF                             | 291h | CCPR1L                              | 311h | —                                   | 391h | IOCAP                         |

| 012h | PIR2                          | 092h | PIE2                          | 112h | CM1CON1                       | 192h | EEADRH                              | 212h | SSP1ADD                             | 292h | CCPR1H                              | 312h | —                                   | 392h | IOCAN                         |

| 013h | —                             | 093h | _                             | 113h | CM2CON0                       | 193h | EEDATL                              | 213h | SSP1MSK                             | 293h | CCP1CON                             | 313h | —                                   | 393h | IOCAF                         |

| 014h | PIR4                          | 094h | PIE4                          | 114h | CM2CON1                       | 194h | EEDATH                              | 214h | SSP1STAT                            | 294h | —                                   | 314h |                                     | 394h | IOCBP                         |

| 015h | TMR0                          | 095h | OPTION_REG                    | 115h | CMOUT                         | 195h | EECON1                              | 215h | SSP1CON1                            | 295h | —                                   | 315h | —                                   | 395h | IOCBN                         |

| 016h | TMR1L                         | 096h | PCON                          | 116h | BORCON                        | 196h | EECON2                              | 216h | SSP1CON2                            | 296h | —                                   | 316h |                                     | 396h | IOCBF                         |

| 017h | TMR1H                         | 097h | WDTCON                        | 117h | FVRCON                        | 197h | VREGCON <sup>(2)</sup>              | 217h | SSP1CON3                            | 297h | —                                   | 317h | —                                   | 397h | IOCCP                         |

| 018h | T1CON                         | 098h | OSCTUNE                       | 118h | DACCON0                       | 198h |                                     | 218h |                                     | 298h | CCPR2L                              | 318h | —                                   | 398h | IOCCN                         |

| 019h | T1GCON                        | 099h | OSCCON                        | 119h | DACCON1                       | 199h | RCREG                               | 219h | _                                   | 299h | CCPR2H                              | 319h | _                                   | 399h | IOCCF                         |

| 01Ah | TMR2                          | 09Ah | OSCSTAT                       | 11Ah | _                             | 19Ah | TXREG                               | 21Ah | _                                   | 29Ah | CCP2CON                             | 31Ah | _                                   | 39Ah | _                             |

| 01Bh | PR2                           | 09Bh | ADRESL                        | 11Bh |                               | 19Bh | SPBRG                               | 21Bh |                                     | 29Bh | —                                   | 31Bh | —                                   | 39Bh | _                             |

| 01Ch | T2CON                         | 09Ch | ADRESH                        | 11Ch | —                             | 19Ch | SPBRGH                              | 21Ch |                                     | 29Ch | —                                   | 31Ch | —                                   | 39Ch | _                             |

| 01Dh | —                             | 09Dh | ADCON0                        | 11Dh | APFCON                        | 19Dh | RCSTA                               | 21Dh |                                     | 29Dh | —                                   | 31Dh | —                                   | 39Dh | IOCEP                         |

| 01Eh | —                             | 09Eh | ADCON1                        | 11Eh | CM3CON0                       | 19Eh | TXSTA                               | 21Eh | —                                   | 29Eh | —                                   | 31Eh | —                                   | 39Eh | IOCEN                         |

| 01Fh | —                             | 09Fh | ADCON2                        | 11Fh | CM3CON1                       | 19Fh | BAUDCON                             | 21Fh | _                                   | 29Fh | —                                   | 31Fh | —                                   | 39Fh | IOCEF                         |

| 020h |                               | 0A0h |                               | 120h |                               | 1A0h |                                     | 220h |                                     | 2A0h |                                     | 320h | General Purpose                     | 3A0h |                               |

|      | General<br>Purpose            |      | General<br>Purpose            | 13Fh | General<br>Purpose            |      | General<br>Purpose                  |      | General<br>Purpose                  |      | General<br>Purpose                  | 32Fh | Register<br>16 Bytes <sup>(1)</sup> |      | Unimplemented                 |

|      | Register<br>80 Bytes          |      | Register<br>80 Bytes          | 140h | Register<br>80 Bytes          |      | Register<br>80 Bytes <sup>(1)</sup> |      | Register<br>80 Bytes <sup>(1)</sup> |      | Register<br>80 Bytes <sup>(1)</sup> | 330h | Unimplemented                       |      | Read as '0'                   |

| 06Fh |                               | 0EFh |                               | 16Fh |                               | 1EFh |                                     | 26Fh |                                     | 2EFh |                                     | 36Fh | Read as '0'                         | 3EFh |                               |

| 070h |                               | 0F0h |                               | 170h |                               | 1F0h |                                     | 270h |                                     | 2F0h |                                     | 370h |                                     | 3F0h |                               |

|      | Common RAM<br>70h – 7Fh       |      | Accesses<br>70h – 7Fh         |      | Accesses<br>70h – 7Fh         |      | Accesses<br>70h – 7Fh               |      | Accesses<br>70h – 7Fh               |      | Accesses<br>70h – 7Fh               |      | Accesses<br>70h – 7Fh               |      | Accesses<br>70h – 7Fh         |

| 07Fh |                               | 0FFh |                               | 17Fh |                               | 1FFh |                                     | 27Fh |                                     | 2FFh |                                     | 37Fh |                                     | 3FFh |                               |

**Legend:** = Unimplemented data memory locations, read as '0'.

Note 1: PIC16(L)F1783 only.

2: PIC16F1782/3 only.

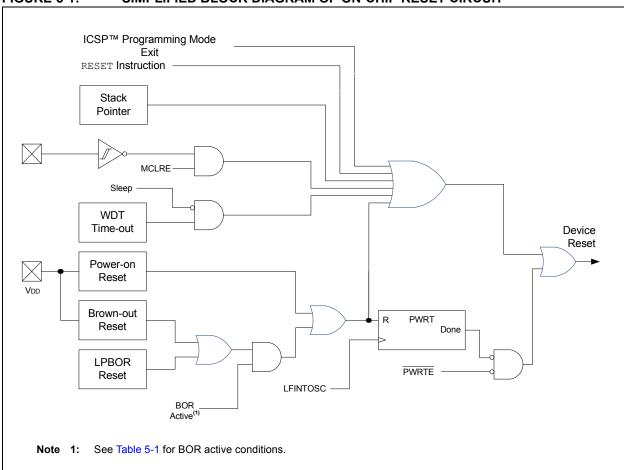

A simplified block diagram of the On-Chip Reset Circuit

is shown in Figure 5-1.

## 5.0 RESETS

There are multiple ways to reset this device:

- Power-On Reset (POR)

- Brown-Out Reset (BOR)

- Low-Power Brown-Out Reset (LPBOR)

- MCLR Reset

- WDT Reset

- RESET instruction

- Stack Overflow

- Stack Underflow

- · Programming mode exit

To allow VDD to stabilize, an optional Power-up Timer can be enabled to extend the Reset time after a BOR or POR event.

### FIGURE 5-1: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

| FIGURE 6-7:            | INTERNAL OSCILLATOR SWITCH TIMING                |

|------------------------|--------------------------------------------------|

|                        | LFINTOSC (FSCM and WDT disabled)                 |

| MFINTOSC               |                                                  |

| HFINTOSC/<br>MFINTOSC  | Start-up Time 2-cycle Sync Running               |

| LFINTOSC               |                                                  |

| IRCF <3:0>             | $\neq 0$ $\chi = 0$                              |

| System Clock           |                                                  |

|                        |                                                  |

| HFINTOSC/→<br>MFINTOSC | LFINTOSC (Either FSCM or WDT enabled)            |

| HFINTOSC/<br>MFINTOSC  |                                                  |

| LFINTOSC               |                                                  |

| IRCF <3:0>             | $\neq 0$ $X = 0$                                 |

| System Clock           |                                                  |

|                        |                                                  |

| LFINTOSC →             | HFINTOSC/MFINTOSC                                |

|                        | LFINTOSC turns off unless WDT or FSCM is enabled |

| LFINTOSC               |                                                  |

|                        | Start-up Time 2-cycle Sync Running               |

| HFINTOSC/<br>MFINTOSC  |                                                  |

| IRCF <3:0>             | = 0 X ≠ 0                                        |

| System Clock           |                                                  |

|                        |                                                  |

|                        |                                                  |

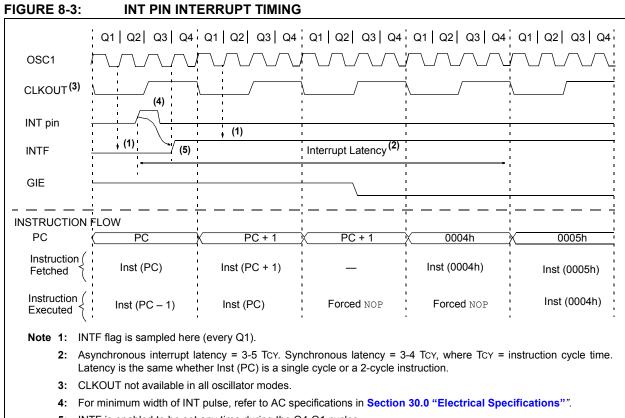

5: INTF is enabled to be set any time during the Q4-Q1 cycles.

## 10.0 LOW DROPOUT (LDO) VOLTAGE REGULATOR

The "F" devices have an internal Low Dropout Regulator (LDO) which provide operation above 3.6V. The LDO regulates a voltage for the internal device logic while permitting the VDD and I/O pins to operate at a higher voltage. There is no user enable/disable control available for the LDO, it is always active. The "LF" devices operate at a maximum VDD of 3.6V and does not incorporate an LDO.

A device I/O pin may be configured as the LDO voltage output, identified as the VCAP pin. Although not required, an external low-ESR capacitor may be connected to the VCAP pin for additional regulator stability.

The  $\overline{\text{VCAPEN}}$  bit of Configuration Words determines if which pin is assigned as the VCAP pin. Refer to Table 10-1.

| VCAPEN | Pin     |  |  |  |  |  |

|--------|---------|--|--|--|--|--|

| 1      | No VCAP |  |  |  |  |  |

| 0      | RA6     |  |  |  |  |  |

## TABLE 10-1: VCAPEN SELECT BIT

On power-up, the external capacitor will load the LDO voltage regulator. To prevent erroneous operation, the device is held in Reset while a constant current source charges the external capacitor. After the cap is fully charged, the device is released from Reset. For more information on the constant current rate, refer to the LDO Regulator Characteristics Table in Section 30.0 "Electrical Specifications".

### TABLE 10-2: SUMMARY OF CONFIGURATION WORD WITH LDO

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5              | Bit 12/4 | Bit 11/3 | Bit 10/2 | Bit 9/1 | Bit 8/0 | Register<br>on Page |

|---------|------|---------|---------|-----------------------|----------|----------|----------|---------|---------|---------------------|

|         | 13:8 |         | —       | LVP                   | DEBUG    | LPBOR    | BORV     | STVREN  | PLLEN   | 10                  |

| CONFIG2 | 7:0  |         | _       | VCAPEN <sup>(1)</sup> | _        | _        |          | WRT     | <1:0>   | 42                  |

**Legend:** — = unimplemented locations read as '0'. Shaded cells are not used by LDO.

Note 1: "F" devices only.

#### EXAMPLE 12-2: DATA EEPROM WRITE

|                      | MOVWF<br>MOVLW<br>MOVWF<br>BCF<br>BCF | DATA_EE_AD<br>EEADRL<br>DATA_EE_DA<br>EEDATL<br>EECON1, CF<br>EECON1, EE   | IA<br>GS<br>PGD | ;Data Memory Address to write<br>; |

|----------------------|---------------------------------------|----------------------------------------------------------------------------|-----------------|------------------------------------|

| Required<br>Sequence | MOVLW<br>MOVWF<br>BSF<br>BSF<br>BCF   | 55h<br>EECON2<br>0AAh<br>EECON2<br>EECON1, WR<br>INTCON, GII<br>EECON1, WR | E<br>EN         |                                    |

| Q1 Q2 Q3 Q4                    | Q1 Q2 Q3 Q4 0                  | Q1 Q2 Q3 Q4                                 | Q1 Q2 Q3 Q4                                                                                                                           | Q1 Q2 Q3 Q4                                                                                                                                                                      | Q1 Q2 Q3 Q4                                                                                                                                        |

|--------------------------------|--------------------------------|---------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| PC                             | <br>  PC + 1  <br>             | EEADRH,EEADRL                               | PC + 3                                                                                                                                | PC + 4                                                                                                                                                                           | PC + 5                                                                                                                                             |

|                                | L L<br>STR (PC) INSTR          | (PC + 1) EEDAT                              | H,EEDATL INST                                                                                                                         | R (PC + 3) INST                                                                                                                                                                  | R (PC + 4)                                                                                                                                         |

| INSTR(PC - 1)<br>executed here | BSF PMCON1,RD<br>executed here | INSTR(PC + 1)<br>executed here              | Forced NOP<br>executed here                                                                                                           | INSTR(PC + 3)<br>executed here                                                                                                                                                   | INSTR(PC + 4)<br>executed here                                                                                                                     |

| <br>                           | <br>                           | <u>ا</u> ا                                  |                                                                                                                                       | <br><del>   </del>                                                                                                                                                               | <br>                                                                                                                                               |

| <br>                           |                                | <br>                                        | Χ                                                                                                                                     |                                                                                                                                                                                  | <br> <br>                                                                                                                                          |

|                                |                                | PC PC + 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 | PC     PC + 1     EEADRH,EEADRL       INSTR (PC)     INSTR (PC + 1)     EEDAT       INSTR(PC - 1)     BSF PMCON1,RD     INSTR(PC + 1) | PC     PC + 1     EEADRH,EEADRL     PC + 3       INSTR (PC)     INSTR (PC + 1)     EEDATH,EEDATL     INST       INSTR(PC - 1)     BSF PMCON1,RD     INSTR(PC + 1)     Forced NOP | INSTR (PC) / INSTR (PC + 1) / EEDATH,EEDATL / INSTR (PC + 3) / INST<br>INSTR (PC - 1)   BSF PMCON1,RD   INSTR(PC + 1)   Forced NOP   INSTR(PC + 3) |

## 13.8 Register Definitions: PORTC

### REGISTER 13-18: PORTC: PORTC REGISTER

| R/W-x/u                               | R/W-x/u                               | R/W-x/u | R/W-x/u                            | R/W-x/u                                               | R/W-x/u | R/W-x/u | R/W-x/u |  |

|---------------------------------------|---------------------------------------|---------|------------------------------------|-------------------------------------------------------|---------|---------|---------|--|

| RC7                                   | RC6                                   | RC5     | RC4                                | RC3                                                   | RC2     | RC1     | RC0     |  |

| bit 7                                 |                                       |         | •                                  |                                                       |         | •       | bit 0   |  |

|                                       |                                       |         |                                    |                                                       |         |         |         |  |

| Legend:                               |                                       |         |                                    |                                                       |         |         |         |  |

| R = Readable bit W = Writable bit     |                                       |         | U = Unimplemented bit, read as '0' |                                                       |         |         |         |  |

| u = Bit is unch                       | = Bit is unchanged x = Bit is unknown |         |                                    | -n/n = Value at POR and BOR/Value at all other Resets |         |         |         |  |

| '1' = Bit is set '0' = Bit is cleared |                                       |         |                                    |                                                       |         |         |         |  |

bit 7-0 RC<7:0>: PORTC General Purpose I/O Pin bits<sup>(1)</sup> 1 = Port pin is ≥ VIH 0 = Port pin is ≤ VIL

**Note 1:** Writes to PORTC are actually written to corresponding LATC register. Reads from PORTC register is return of actual I/O pin values.

#### REGISTER 13-19: TRISC: PORTC TRI-STATE REGISTER

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| TRISC7  | TRISC6  | TRISC5  | TRISC4  | TRISC3  | TRISC2  | TRISC1  | TRISC0  |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0

TRISC<7:0>: PORTC Tri-State Control bits

$\ensuremath{\mathtt{1}}$  = PORTC pin configured as an input (tri-stated)

0 = PORTC pin configured as an output

#### REGISTER 13-20: LATC: PORTC DATA LATCH REGISTER

| R/W-x/u |

|---------|---------|---------|---------|---------|---------|---------|---------|

| LATC7   | LATC6   | LATC5   | LATC4   | LATC3   | LATC2   | LATC1   | LATC0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

### bit 7-0 LATC<7:0>: PORTC Output Latch Value bits<sup>(1)</sup>

**Note 1:** Writes to PORTC are actually written to corresponding LATC register. Reads from PORTC register is return of actual I/O pin values.

## 19.0 DIGITAL-TO-ANALOG CONVERTER (DAC) MODULE

The Digital-to-Analog Converter supplies a variable voltage reference, ratiometric with the input source, with 256 selectable output levels.

The input of the DAC can be connected to:

- External VREF pins

- VDD supply voltage

- FVR (Fixed Voltage Reference)

The output of the DAC can be configured to supply a reference voltage to the following:

- Comparator positive input

- · Op amp positive input

- ADC input channel

- DACOUT1 pin

- DACOUT2 pin

The Digital-to-Analog Converter (DAC) is enabled by setting the DACEN bit of the DACCON0 register.

## 19.1 Output Voltage Selection

The DAC has 256 voltage level ranges. The 256 levels are set with the DACR<7:0> bits of the DACCON1 register.

The DAC output voltage is determined by Equation 19-1:

## EQUATION 19-1: DAC OUTPUT VOLTAGE

$$\frac{IF \ DACxEN = 1}{VOUT} = \left( (VSOURCE+ - VSOURCE-) \times \frac{DACxR[7:0]}{2^8} \right) + VSOURCE-$$

$$VSOURCE+ = VDD, \ VREF, \ or \ FVR \ BUFFER \ 2$$

$$VSOURCE- = VSS$$

## 19.2 Ratiometric Output Level

The DAC output value is derived using a resistor ladder with each end of the ladder tied to a positive and negative voltage reference input source. If the voltage of either input source fluctuates, a similar fluctuation will result in the DAC output value.

The value of the individual resistors within the ladder can be found in **Section 30.0** "Electrical **Specifications**".

## **19.3 DAC Voltage Reference Output**

The DAC voltage can be output to the DACOUT1 and DACOUT2 pins by setting the respective DACOE1 and DACOE2 pins of the DACCON0 register. Selecting the DAC reference voltage for output on either DACOUTx pin automatically overrides the digital output buffer and digital input threshold detector functions of that pin. Reading the DACOUTx pin when it has been configured for DAC reference voltage output will always return a '0'.

Due to the limited current drive capability, a buffer must be used on the DAC voltage reference output for external connections to either DACOUTx pin. Figure 19-2 shows an example buffering technique.

| R/W-0/0          | R/W-0/0                                                                                                                                                                                                                                                                       | R/W-0/0          | R/W-0/0                                                   | R/W-0/0          | R/W-0/0                               | R/W-0/0  | R/W-0/0 |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------------------------------------------------|------------------|---------------------------------------|----------|---------|

| CxINTP           | CxINTN CxPCH<2:0>                                                                                                                                                                                                                                                             |                  |                                                           |                  | CxNCH<2:0>                            |          |         |

| bit 7            |                                                                                                                                                                                                                                                                               |                  |                                                           |                  |                                       |          | bit     |

|                  |                                                                                                                                                                                                                                                                               |                  |                                                           |                  |                                       |          |         |

| Legend:          |                                                                                                                                                                                                                                                                               |                  |                                                           |                  |                                       |          |         |

| R = Readable     | bit                                                                                                                                                                                                                                                                           | W = Writable     | bit                                                       | U = Unimpler     | mented bit, read                      | d as '0' |         |

| u = Bit is unch  | nanged                                                                                                                                                                                                                                                                        | x = Bit is unkr  | is unknown -n/n = Value at POR and BOR/Value at all other |                  | other Resets                          |          |         |

| '1' = Bit is set |                                                                                                                                                                                                                                                                               | '0' = Bit is cle | ared                                                      |                  |                                       |          |         |

| bit 7            | CxINTP: Con                                                                                                                                                                                                                                                                   | nparator Interru | ıpt on Positive                                           | Going Edge E     | nable bits                            |          |         |

|                  | 1 = The CxIF                                                                                                                                                                                                                                                                  | interrupt flag   | will be set upo                                           | n a positive goi | ing edge of the of the of the CxOUT I |          |         |

| bit 6            | <ul> <li>CxINTN: Comparator Interrupt on Negative Going Edge Enable bits</li> <li>1 = The CxIF interrupt flag will be set upon a negative going edge of the CxOUT bit</li> <li>0 = No interrupt flag will be set on a negative going edge of the CxOUT bit</li> </ul>         |                  |                                                           |                  |                                       |          |         |

| bit 5-3          | <b>CxPCH&lt;2:0&gt;:</b> Comparator Positive Input Channel Select bits                                                                                                                                                                                                        |                  |                                                           |                  |                                       |          |         |

|                  | <pre>111 = CxVP connects to AGND 110 = CxVP connects to FVR Buffer 2 101 = CxVP connects to DAC_output 100 = Reserved, input floating 011 = Reserved, input floating 010 = Reserved, input floating 001 = CxVP connects to CxIN1+ pin 000 = CxVP connects to CxIN0+ pin</pre> |                  |                                                           |                  |                                       |          |         |

| bit 2-0          | •                                                                                                                                                                                                                                                                             |                  |                                                           |                  |                                       |          |         |

### REGISTER 20-2: CMxCON1: COMPARATOR Cx CONTROL REGISTER 1

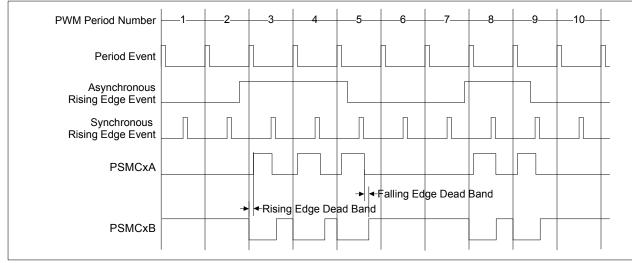

### 24.3.8 PULSE-SKIPPING PWM WITH COMPLEMENTARY OUTPUTS

The pulse-skipping PWM is used to generate a series of fixed-length pulses that may or not be triggered at each period event. If any of the sources enabled to generate a rising edge event are high when a period event occurs, a pulse will be generated. If the rising edge sources are low at the period event, no pulse will be generated.

The rising edge occurs based upon the value in the PSMCxPH register pair.

The falling edge event always occurs according to the enabled event inputs without qualification between any two inputs.

#### 24.3.8.1 Mode Features

- · Dead-band control is available

- · No steering control available

- · Primary PWM is output on only PSMCxA.

- · Complementary PWM is output on only PSMCxB.

## 24.3.8.2 Waveform Generation

### Rising Edge Event

If any enabled asynchronous rising edge event = 1 when there is a period event, then upon the next synchronous rising edge event:

- · Complementary output is set inactive

- Dead-band rising is activated (if enabled)

- · Primary output is set active

#### Falling Edge Event

- · Primary output is set inactive

- Dead-band falling is activated (if enabled)

- · Complementary output is set active

**Note:** To use this mode, an external source must be used for the determination of whether or not to generate the set pulse. If the phase time base is used, it will either always generate a pulse or never generate a pulse based on the PSMCxPH value.

### FIGURE 24-11: PULSE-SKIPPING WITH COMPLEMENTARY OUTPUT PWM WAVEFORM

© 2011-2014 Microchip Technology Inc.

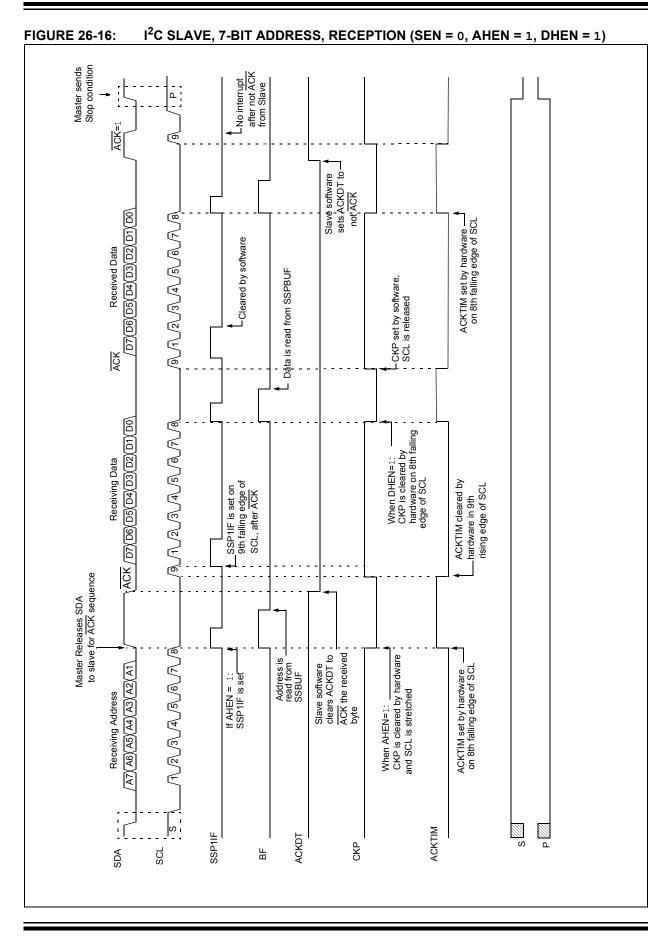

#### 26.5.4 SLAVE MODE 10-BIT ADDRESS RECEPTION

This section describes a standard sequence of events for the MSSP module configured as an  $I^2C$  slave in 10-bit Addressing mode.

Figure 26-19 is used as a visual reference for this description.

This is a step by step process of what must be done by slave software to accomplish  $I^2C$  communication.

- 1. Bus starts Idle.

- Master sends Start condition; S bit of SSPSTAT is set; SSP1IF is set if interrupt on Start detect is enabled.

- 3. Master sends matching high address with  $R/\overline{W}$  bit clear; UA bit of the SSPSTAT register is set.

- 4. Slave sends ACK and SSP1IF is set.

- 5. Software clears the SSP1IF bit.

- 6. Software reads received address from SSPBUF clearing the BF flag.

- 7. Slave loads low address into SSPADD, releasing SCL.

- 8. Master sends matching low address byte to the slave; UA bit is set.

**Note:** Updates to the SSPADD register are not allowed until after the ACK sequence.

9. Slave sends ACK and SSP1IF is set.

**Note:** If the low address does not match, SSP1IF and UA are still set so that the slave software can set SSPADD back to the high address. BF is not set because there is no match. CKP is unaffected.

- 10. Slave clears SSP1IF.

- 11. Slave reads the received matching address from SSPBUF clearing BF.

- 12. Slave loads high address into SSPADD.

- Master clocks a data byte to the slave and clocks out the slaves ACK on the 9th SCL pulse; SSP1IF is set.

- 14. If SEN bit of SSPCON2 is set, CKP is cleared by hardware and the clock is stretched.

- 15. Slave clears SSP1IF.

- 16. Slave reads the received byte from SSPBUF clearing BF.

- 17. If SEN is set the slave sets CKP to release the SCL.

- 18. Steps 13-17 repeat for each received byte.

- 19. Master sends Stop to end the transmission.

## 26.5.5 10-BIT ADDRESSING WITH ADDRESS OR DATA HOLD

Reception using 10-bit addressing with AHEN or DHEN set is the same as with 7-bit modes. The only difference is the need to update the SSPADD register using the UA bit. All functionality, specifically when the CKP bit is cleared and SCL line is held low are the same. Figure 26-20 can be used as a reference of a slave in 10-bit addressing with AHEN set.

Figure 26-21 shows a standard waveform for a slave transmitter in 10-bit Addressing mode.

| CALL             | Call Subroutine                                                                                                                                                                                                                               |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] CALL k                                                                                                                                                                                                                       |

| Operands:        | $0 \leq k \leq 2047$                                                                                                                                                                                                                          |

| Operation:       | (PC)+ 1 $\rightarrow$ TOS,<br>k $\rightarrow$ PC<10:0>,<br>(PCLATH<6:3>) $\rightarrow$ PC<14:11>                                                                                                                                              |

| Status Affected: | None                                                                                                                                                                                                                                          |

| Description:     | Call Subroutine. First, return address<br>(PC + 1) is pushed onto the stack.<br>The eleven-bit immediate address is<br>loaded into PC bits <10:0>. The upper<br>bits of the PC are loaded from<br>PCLATH. CALL is a 2-cycle instruc-<br>tion. |

| CLRWDT           | Clear Watchdog Timer                                                                                                                  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] CLRWDT                                                                                                                        |

| Operands:        | None                                                                                                                                  |

| Operation:       | $00h \rightarrow WDT$ $0 \rightarrow \underline{WDT} \text{ prescaler,}$ $1 \rightarrow \underline{TO}$ $1 \rightarrow \overline{PD}$ |

| Status Affected: | TO, PD                                                                                                                                |

| Description:     | CLRWDT instruction resets the Watch-<br>dog Timer. It also resets the prescaler<br>of the WDT.<br>Status bits TO and PD are set.      |

| CALLW                            | Subroutine Call With W                                                                                                                                                                                                                            | COMF             | Complement f                                                                                                                                                  |

|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                          | [ label ] CALLW                                                                                                                                                                                                                                   | Syntax:          | [ <i>label</i> ] COMF f,d                                                                                                                                     |

| Operands:                        | None                                                                                                                                                                                                                                              | Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                            |

| Operation:                       | $\begin{array}{l} (PC) +1 \rightarrow TOS, \\ (W) \rightarrow PC < 7:0 >, \end{array}$                                                                                                                                                            | Operation:       | $(\overline{f}) \rightarrow (destination)$                                                                                                                    |

|                                  | $(PCLATH < 6:0>) \rightarrow PC < 14:8>$                                                                                                                                                                                                          | Status Affected: | Z                                                                                                                                                             |

| Status Affected:<br>Description: | None<br>Subroutine call with W. First, the<br>return address (PC + 1) is pushed<br>onto the return stack. Then, the con-<br>tents of W is loaded into PC<7:0>,<br>and the contents of PCLATH into<br>PC<14:8>. CALLW is a 2-cycle<br>instruction. | Description:     | The contents of register 'f' are com-<br>plemented. If 'd' is '0', the result is<br>stored in W. If 'd' is '1', the result is<br>stored back in register 'f'. |

| CLRF             | Clear f                                                               |

|------------------|-----------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] CLRF f                                               |

| Operands:        | $0 \leq f \leq 127$                                                   |

| Operation:       | $\begin{array}{l} 00h \rightarrow (f) \\ 1 \rightarrow Z \end{array}$ |

| Status Affected: | Z                                                                     |

| Description:     | The contents of register 'f' are cleared and the Z bit is set.        |

| CLRW             | Clear W                                                                                    |

|------------------|--------------------------------------------------------------------------------------------|

| Syntax:          | [label] CLRW                                                                               |

| Operands:        | None                                                                                       |

| Operation:       | $\begin{array}{l} \text{O0h} \rightarrow (\text{W}) \\ 1 \rightarrow \text{Z} \end{array}$ |

| Status Affected: | Z                                                                                          |

| Description:     | W register is cleared. Zero bit (Z) is set.                                                |

| DECF             | Decrement f                                                                                                                                      |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] DECF f,d                                                                                                                        |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                               |

| Operation:       | (f) - 1 $\rightarrow$ (destination)                                                                                                              |

| Status Affected: | Z                                                                                                                                                |

| Description:     | Decrement register 'f'. If 'd' is ' $0$ ', the result is stored in the W register. If 'd' is ' $1$ ', the result is stored back in register 'f'. |

| ΜΟΥΙΨ            | Move INDFn to W                                                                                                                                                                                                                                                                                                                                                                 |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] MOVIW ++FSRn<br>[ <i>label</i> ] MOVIWFSRn<br>[ <i>label</i> ] MOVIW FSRn++<br>[ <i>label</i> ] MOVIW FSRn<br>[ <i>label</i> ] MOVIW k[FSRn]                                                                                                                                                                                                                   |

| Operands:        | n ∈ [0,1]<br>mm ∈ [00,01, 10, 11]<br>-32 ≤ k ≤ 31                                                                                                                                                                                                                                                                                                                               |

| Operation:       | $\begin{split} &\text{INDFn} \rightarrow W \\ &\text{Effective address is determined by} \\ &\text{FSR + 1 (preincrement)} \\ &\text{FSR - 1 (predecrement)} \\ &\text{FSR + k (relative offset)} \\ &\text{After the Move, the FSR value will be} \\ &\text{either:} \\ &\text{FSR + 1 (all increments)} \\ &\text{FSR - 1 (all decrements)} \\ &\text{Unchanged} \end{split}$ |

| Status Affected: | Z                                                                                                                                                                                                                                                                                                                                                                               |

| Mode          | Syntax | mm |

|---------------|--------|----|

| Preincrement  | ++FSRn | 00 |

| Predecrement  | FSRn   | 01 |

| Postincrement | FSRn++ | 10 |

| Postdecrement | FSRn   | 11 |

Description:

This instruction is used to move data between W and one of the indirect registers (INDFn). Before/after this move, the pointer (FSRn) is updated by pre/post incrementing/decrementing it.

Note: The INDFn registers are not physical registers. Any instruction that accesses an INDFn register actually accesses the register at the address specified by the FSRn.

FSRn is limited to the range 0000h -FFFFh. Incrementing/decrementing it beyond these bounds will cause it to wrap-around.

| Syntax:          | [ <i>label</i> ]MOVLB k                                              |  |

|------------------|----------------------------------------------------------------------|--|

| Operands:        | $0 \leq k \leq 31$                                                   |  |

| Operation:       | $k \rightarrow BSR$                                                  |  |

| Status Affected: | None                                                                 |  |

| Description:     | The 5-bit literal 'k' is loaded into the Bank Select Register (BSR). |  |

| MOVLP            | Move literal to PCLATH                                                                         |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ]MOVLP k                                                                        |  |  |  |  |

| Operands:        | $0 \le k \le 127$                                                                              |  |  |  |  |

| Operation:       | $k \rightarrow PCLATH$                                                                         |  |  |  |  |

| Status Affected: | None                                                                                           |  |  |  |  |

| Description:     | The 7-bit literal 'k' is loaded into the PCLATH register.                                      |  |  |  |  |

| MOVLW            | Move literal to W                                                                              |  |  |  |  |

| Syntax:          | [ <i>label</i> ] MOVLW k                                                                       |  |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                              |  |  |  |  |

| Operation:       | $k \rightarrow (W)$                                                                            |  |  |  |  |

| Status Affected: | None                                                                                           |  |  |  |  |

| Description:     | The 8-bit literal 'k' is loaded into W reg-<br>ister. The "don't cares" will assemble as '0's. |  |  |  |  |

| Words:           | 4                                                                                              |  |  |  |  |

| word5.           | 1                                                                                              |  |  |  |  |

| Cycles:          | 1                                                                                              |  |  |  |  |

| MOVLW             | 0x5A |  |  |  |  |

|-------------------|------|--|--|--|--|

| After Instruction |      |  |  |  |  |

```

W

=

0x5A

```

| MOVWF            | Move W to f                                                                                               |

|------------------|-----------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] MOVWF f                                                                                  |

| Operands:        | $0 \leq f \leq 127$                                                                                       |

| Operation:       | $(W) \rightarrow (f)$                                                                                     |

| Status Affected: | None                                                                                                      |

| Description:     | Move data from W register to register 'f'.                                                                |

| Words:           | 1                                                                                                         |

| Cycles:          | 1                                                                                                         |

| Example:         | MOVWF OPTION_REG                                                                                          |

|                  | Before Instruction<br>OPTION_REG = 0xFF<br>W = 0x4F<br>After Instruction<br>OPTION_REG = 0x4F<br>W = 0x4F |

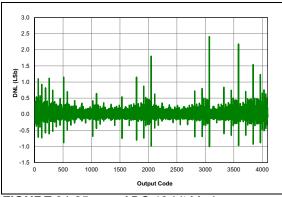

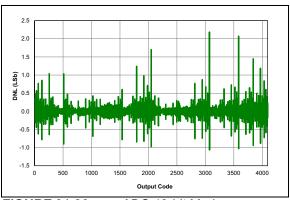

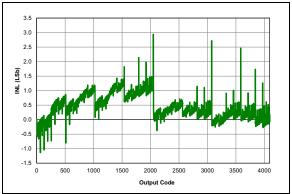

Note: Unless otherwise noted, VIN = 5V, Fosc = 300 kHz, CIN = 0.1  $\mu$ F, TA = 25°C.

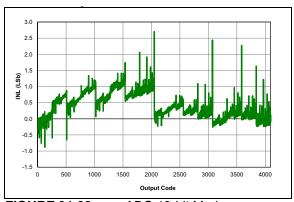

**FIGURE 31-85:** ADC 12-bit Mode, Single-Ended DNL, VDD = 3.0V, TAD =  $1 \mu$ S,  $25^{\circ}$ C.

**FIGURE 31-86:** ADC 12-bit Mode, Single-Ended DNL, VDD = 3.0V, TAD =  $4 \mu$ S,  $25^{\circ}$ C.

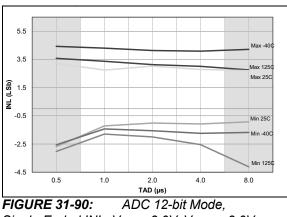

**FIGURE 31-87:** ADC 12-bit Mode, Single-Ended INL, VDD = 3.0V, TAD =  $1 \mu$ S,  $25^{\circ}$ C.

**FIGURE 31-88:** ADC 12-bit Mode, Single-Ended INL, VDD = 3.0V, TAD =  $4 \mu$ S,  $25^{\circ}$ C.

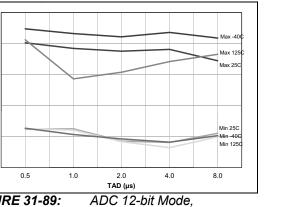

FIGURE 31-89: ADC 12-bit Mode, Single-Ended DNL, VDD = 3.0V, VREF = 3.0V.

4.5

3

(qs 1.5

-1.5

-3

## 32.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers (MCU) and dsPIC<sup>®</sup> digital signal controllers (DSC) are supported with a full range of software and hardware development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> X IDE Software

Compilers/Assemblers/Linkers

- Compliers/Assemblers/Link

- MPLAB XC Compiler

- MPASM<sup>™</sup> Assembler

- MPLINK<sup>™</sup> Object Linker/ MPLIB<sup>™</sup> Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- Simulators

- MPLAB X SIM Software Simulator

- Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debuggers/Programmers

- MPLAB ICD 3

- PICkit™ 3

- Device Programmers

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits and Starter Kits

- Third-party development tools

## 32.1 MPLAB X Integrated Development Environment Software

The MPLAB X IDE is a single, unified graphical user interface for Microchip and third-party software, and hardware development tool that runs on Windows<sup>®</sup>, Linux and Mac OS<sup>®</sup> X. Based on the NetBeans IDE, MPLAB X IDE is an entirely new IDE with a host of free software components and plug-ins for high-performance application development and debugging. Moving between tools and upgrading from software simulators to hardware debugging and programming tools is simple with the seamless user interface.

With complete project management, visual call graphs, a configurable watch window and a feature-rich editor that includes code completion and context menus, MPLAB X IDE is flexible and friendly enough for new users. With the ability to support multiple tools on multiple projects with simultaneous debugging, MPLAB X IDE is also suitable for the needs of experienced users.

Feature-Rich Editor:

- Color syntax highlighting

- Smart code completion makes suggestions and provides hints as you type

- Automatic code formatting based on user-defined rules

- · Live parsing

User-Friendly, Customizable Interface:

- Fully customizable interface: toolbars, toolbar buttons, windows, window placement, etc.

- Call graph window

- Project-Based Workspaces:

- Multiple projects

- Multiple tools

- · Multiple configurations

- · Simultaneous debugging sessions

- File History and Bug Tracking:

- Local file history feature

- · Built-in support for Bugzilla issue tracker

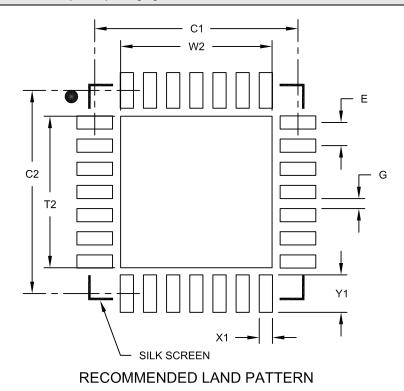

## 28-Lead Plastic Quad Flat, No Lead Package (ML) – 6x6 mm Body [QFN] with 0.55 mm Contact Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| Units                      |    | MILLIMETERS |      |      |

|----------------------------|----|-------------|------|------|

| Dimension Limits           |    | MIN         | NOM  | MAX  |

| Contact Pitch              | E  | 0.65 BSC    |      |      |

| Optional Center Pad Width  | W2 |             |      | 4.25 |

| Optional Center Pad Length | T2 |             |      | 4.25 |

| Contact Pad Spacing        | C1 |             | 5.70 |      |

| Contact Pad Spacing        | C2 |             | 5.70 |      |

| Contact Pad Width (X28)    | X1 |             |      | 0.37 |

| Contact Pad Length (X28)   | Y1 |             |      | 1.00 |

| Distance Between Pads      | G  | 0.20        |      |      |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2105A

#### Note the following details of the code protection feature on Microchip devices:

- · Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

## QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV = ISO/TS 16949=

#### Trademarks

The Microchip name and logo, the Microchip logo, dsPIC, FlashFlex, KEELOQ, KEELOQ logo, MPLAB, PIC, PICmicro, PICSTART, PIC<sup>32</sup> logo, rfPIC, SST, SST Logo, SuperFlash and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, Hampshire, HI-TECH C, Linear Active Thermistor, MTP, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Silicon Storage Technology is a registered trademark of Microchip Technology Inc. in other countries.

Analog-for-the-Digital Age, Application Maestro, BodyCom, chipKIT, chipKIT logo, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, HI-TIDE, In-Circuit Serial Programming, ICSP, Mindi, MiWi, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, mTouch, Omniscient Code Generation, PICC, PICC-18, PICDEM, PICDEM.net, PICkit, PICtail, REAL ICE, rfLAB, Select Mode, SQI, Serial Quad I/O, Total Endurance, TSHARC, UniWinDriver, WiperLock, ZENA and Z-Scale are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

GestIC and ULPP are registered trademarks of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2011-2014, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Printed on recycled paper.

ISBN: 978-1-63276-249-8

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and mulfacture of development systems is ISO 9001:2000 certified.