Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PSMC, PWM, WDT                                |

| Number of I/O              | 24                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 512 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 11x12b; D/A 1x8b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 28-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1783-i-so |

#### 3.2.1.1 STATUS Register

The STATUS register, shown in Register 3-1, contains:

- · the arithmetic status of the ALU

- · the Reset status

The STATUS register can be the destination for any instruction, like any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

For example, CLRF STATUS will clear the upper three bits and set the Z bit. This leaves the STATUS register as '000u uluu' (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS register, because these instructions do not affect any Status bits. For other instructions not affecting any Status bits (Refer to Section 29.0 "Instruction Set Summary").

Note: The C and DC bits operate as Borrow and Digit Borrow out bits, respectively, in subtraction.

### 3.3 Register Definitions: Status

#### REGISTER 3-1: STATUS: STATUS REGISTER

| U-0   | U-0 | U-0 | R-1/q | R-1/q | R/W-0/u | R/W-0/u           | R/W-0/u          |

|-------|-----|-----|-------|-------|---------|-------------------|------------------|

| _     | _   | _   | TO    | PD    | Z       | DC <sup>(1)</sup> | C <sup>(1)</sup> |

| bit 7 |     |     |       |       |         |                   | bit 0            |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = Value depends on condition                        |

| bit 7-5 | Unimplemented: Read as '0'                                                                                                                                           |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 4   | TO: Time-Out bit                                                                                                                                                     |

|         | 1 = After power-up, CLRWDT instruction or SLEEP instruction 0 = A WDT time-out occurred                                                                              |

| bit 3   | PD: Power-Down bit                                                                                                                                                   |

|         | <ul><li>1 = After power-up or by the CLRWDT instruction</li><li>0 = By execution of the SLEEP instruction</li></ul>                                                  |

| bit 2   | <b>Z</b> : Zero bit                                                                                                                                                  |

|         | <ul><li>1 = The result of an arithmetic or logic operation is zero</li><li>0 = The result of an arithmetic or logic operation is not zero</li></ul>                  |

| bit 1   | DC: Digit Carry/Digit Borrow bit (ADDWF, ADDLW, SUBLW, SUBWF instructions)(1)                                                                                        |

|         | <ul><li>1 = A carry-out from the 4th low-order bit of the result occurred</li><li>0 = No carry-out from the 4th low-order bit of the result</li></ul>                |

| bit 0   | C: Carry/Borrow bit <sup>(1)</sup> (ADDWF, ADDLW, SUBLW, SUBWF instructions) <sup>(1)</sup>                                                                          |

|         | <ul><li>1 = A carry-out from the Most Significant bit of the result occurred</li><li>0 = No carry-out from the Most Significant bit of the result occurred</li></ul> |

**Note 1:** For Borrow, the polarity is reversed. A subtraction is executed by adding the two's complement of the second operand.

### 3.3.1 SPECIAL FUNCTION REGISTER

The Special Function Registers are registers used by the application to control the desired operation of peripheral functions in the device. The Special Function Registers occupy the 20 bytes after the core registers of every data memory bank (addresses x0Ch/x8Ch through x1Fh/x9Fh). The registers associated with the operation of the peripherals are described in the appropriate peripheral chapter of this data sheet.

#### 3.3.2 GENERAL PURPOSE RAM

There are up to 80 bytes of GPR in each data memory bank. The Special Function Registers occupy the 20 bytes after the core registers of every data memory bank (addresses x0Ch/x8Ch through x1Fh/x9Fh).

#### 3.3.2.1 Linear Access to GPR

The general purpose RAM can be accessed in a non-banked method via the FSRs. This can simplify access to large memory structures. See **Section 3.6.2** "Linear Data Memory" for more information.

#### 3.3.3 COMMON RAM

There are 16 bytes of common RAM accessible from all banks.

# FIGURE 3-3: BANKED MEMORY PARTITIONING

| 7-bit Bank Offset | Memory Region                                 |

|-------------------|-----------------------------------------------|

| 00h<br>0Bh        | Core Registers<br>(12 bytes)                  |

| 0Ch               | Special Function Registers (20 bytes maximum) |

| 1Fh<br>20h        |                                               |

| 6Fh               | General Purpose RAM<br>(80 bytes maximum)     |

| 70h               | Common RAM<br>(16 bytes)                      |

| 7Fh               |                                               |

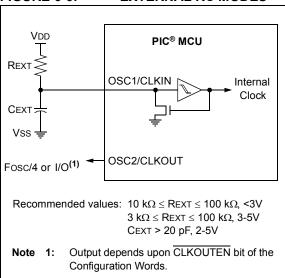

### 6.2.1.6 External RC Mode

The external Resistor-Capacitor (RC) modes support the use of an external RC circuit. This allows the designer maximum flexibility in frequency choice while keeping costs to a minimum when clock accuracy is not required.

The RC circuit connects to OSC1. OSC2/CLKOUT is available for general purpose I/O or CLKOUT. The function of the OSC2/CLKOUT pin is determined by the CLKOUTEN bit in Configuration Words.

Figure 6-6 shows the external RC mode connections.

#### FIGURE 6-6: EXTERNAL RC MODES

The RC oscillator frequency is a function of the supply voltage, the resistor (REXT) and capacitor (CEXT) values and the operating temperature. Other factors affecting the oscillator frequency are:

- · threshold voltage variation

- · component tolerances

- · packaging variations in capacitance

The user also needs to take into account variation due to tolerance of external RC components used.

#### 6.2.2 INTERNAL CLOCK SOURCES

The device may be configured to use the internal oscillator block as the system clock by performing one of the following actions:

- Program the FOSC<2:0> bits in Configuration

Words to select the INTOSC clock source, which

will be used as the default system clock upon a

device Reset.

- Write the SCS<1:0> bits in the OSCCON register to switch the system clock source to the internal oscillator during run-time. See Section 6.3 "Clock Switching"for more information.

In **INTOSC** mode, OSC1/CLKIN is available for general purpose I/O. OSC2/CLKOUT is available for general purpose I/O or CLKOUT.

The function of the OSC2/CLKOUT pin is determined by the CLKOUTEN bit in Configuration Words.

The internal oscillator block has two independent oscillators and a dedicated Phase-Lock Loop, HFPLL that can produce one of three internal system clock sources.

- The HFINTOSC (High-Frequency Internal Oscillator) is factory calibrated and operates at 16 MHz. The HFINTOSC source is generated from the 500 kHz MFINTOSC source and the dedicated Phase-Lock Loop, HFPLL. The frequency of the HFINTOSC can be user-adjusted via software using the OSCTUNE register (Register 6-3).

- The MFINTOSC (Medium-Frequency Internal Oscillator) is factory calibrated and operates at 500 kHz. The frequency of the MFINTOSC can be user-adjusted via software using the OSCTUNE register (Register 6-3).

- The LFINTOSC (Low-Frequency Internal Oscillator) is uncalibrated and operates at 31 kHz.

#### REGISTER 8-6: PIR2: PERIPHERAL INTERRUPT REQUEST REGISTER 2

| R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | U-0 | R/W-0/0 | R/W-0/0 |

|---------|---------|---------|---------|---------|-----|---------|---------|

| OSFIF   | C2IF    | C1IF    | EEIF    | BCL1IF  | _   | C3IF    | CCP2IF  |

| bit 7   |         |         |         |         |     |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7 OSFIF: Oscillator Fail Interrupt Flag bit

1 = Interrupt is pending0 = Interrupt is not pending

bit 6 C2IF: Comparator C2 Interrupt Flag bit

1 = Interrupt is pending0 = Interrupt is not pending

bit 5 C1IF: Comparator C1 Interrupt Flag bit

1 = Interrupt is pending0 = Interrupt is not pending

bit 4 **EEIF:** EEPROM Write Completion Interrupt Flag bit

1 = Interrupt is pending0 = Interrupt is not pending

bit 3 BCL1IF: MSSP Bus Collision Interrupt Flag bit

1 = Interrupt is pending0 = Interrupt is not pending

bit 2 Unimplemented: Read as '0'

bit 1 C3IF: Comparator C3 Interrupt Flag bit

1 = Interrupt is pending0 = Interrupt is not pending

bit 0 CCP2IF: CCP2 Interrupt Flag bit

1 = Interrupt is pending0 = Interrupt is not pending

Note: Interrupt flag bits are set when an interrupt

condition occurs, regardless of the state of its corresponding enable bit or the Global Enable bit, GIE, of the INTCON register. User software should ensure the appropriate interrupt flag bits are clear

prior to enabling an interrupt.

TABLE 8-1: SUMMARY OF REGISTERS ASSOCIATED WITH INTERRUPTS

| Name       | Bit 7         | Bit 6  | Bit 5    | Bit 4    | Bit 3  | Bit 2   | Bit 1    | Bit 0    | Register<br>on Page |

|------------|---------------|--------|----------|----------|--------|---------|----------|----------|---------------------|

| INTCON     | GIE           | PEIE   | TMR0IE   | INTE     | IOCIE  | TMR0IF  | INTF     | IOCIF    | 79                  |

| OPTION_REG | WPUEN         | INTEDG | TMR0CS   | TMR0SE   | PSA    | PS<2:0> |          |          | 174                 |

| PIE1       | TMR1GIE       | ADIE   | RCIE     | TXIE     | SSP1IE | CCP1IE  | TMR2IE   | TMR1IE   | 80                  |

| PIE2       | OSEIE         | C2IE   | C1IE     | EEIE     | BCL1IE | _       | C3IE     | CCP2IE   | 81                  |

| _          | Unimplement   | ted    |          |          |        |         |          |          | _                   |

| PIE4       | _             | _      | PSMC2TIE | PSMC1TIE | _      | _       | PSMC2SIE | PSMC1SIE | 82                  |

| PIR1       | TMR1GIF       | ADIF   | RCIF     | TXIF     | SSP1IF | CCP1IF  | TMR2IF   | TMR1IF   | 83                  |

| PIR2       | OSFIF         | C2IF   | C1IF     | EEIF     | BCL1IF | _       | C3IF     | CCP2IF   | 84                  |

| _          | Unimplemented |        |          |          |        |         |          |          |                     |

| PIR4       | _             | _      | PSMC2TIF | PSMC1TIF | _      | _       | PSMC2SIF | PSMC1SIF | 85                  |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by interrupts.

### 13.2 Register Definitions: Alternate Pin Function Control

### REGISTER 13-1: APFCON: ALTERNATE PIN FUNCTION CONTROL REGISTER

| R/W-0/0  | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|----------|---------|---------|---------|---------|---------|---------|---------|

| C2OUTSEL | CCP1SEL | SDOSEL  | SCKSEL  | SDISEL  | TXSEL   | RXSEL   | CCP2SEL |

| bit 7    |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7 | C2OUTSEL: C2OUT Pin Selection bit                           |

|-------|-------------------------------------------------------------|

|       | 1 = C2OUT is on pin RA6                                     |

|       | 0 = C2OUT is on pin RA5                                     |

| bit 6 | CCP1SEL: CCP1 Input/Output Pin Selection bit                |

|       | 1 = CCP1 is on pin RB0                                      |

|       | 0 = CCP1 is on pin RC2                                      |

| bit 5 | SDOSEL: MSSP SDO Pin Selection bit                          |

|       | 1 = SDO is on pin RB5                                       |

|       | 0 = SDO is on pin RC5                                       |

| bit 4 | SCKSEL: MSSP Serial Clock (SCL/SCK) Pin Selection bit       |

|       | 1 = SCL/SCK is on pin RB7                                   |

|       | 0 = SCL/SCK is on pin RC3                                   |

| bit 3 | SDISEL: MSSP Serial Data (SDA/SDI) Output Pin Selection bit |

|       | 1 = SDA/SDI is on pin RB6                                   |

|       | 0 = SDA/SDI is on pin RC4                                   |

| bit 2 | TXSEL: TX Pin Selection bit                                 |

|       | 1 = TX is on pin RB6                                        |

|       | 0 = TX is on pin RC6                                        |

| bit 1 | RXSEL: RX Pin Selection bit                                 |

|       | 1 = RX is on pin RB7                                        |

|       | 0 = RX is on pin RC7                                        |

| bit 0 | CCP2SEL: CCP2 Input/Output Pin Selection bit                |

|       | 1 = CCP2 is on pin RB3                                      |

|       | 0 = CCP2 is on pin RC1                                      |

|       |                                                             |

#### REGISTER 13-7: ODCONA: PORTA OPEN DRAIN CONTROL REGISTER

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| ODA7    | ODA6    | ODA5    | ODA4    | ODA3    | ODA2    | ODA1    | ODA0    |

| bit 7   |         |         |         |         |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-0 ODA<7:0>: PORTA Open Drain Enable bits

For RA<7:0> pins, respectively

1 = Port pin operates as open-drain drive (sink current only)

0 = Port pin operates as standard push-pull drive (source and sink current)

#### REGISTER 13-8: SLRCONA: PORTA SLEW RATE CONTROL REGISTER

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| SLRA7   | SLRA6   | SLRA5   | SLRA4   | SLRA3   | SLRA2   | SLRA1   | SLRA0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-0 SLRA<7:0>: PORTA Slew Rate Enable bits

For RA<7:0> pins, respectively

1 = Port pin slew rate is limited

0 = Port pin slews at maximum rate

### REGISTER 13-9: INLVLA: PORTA INPUT LEVEL CONTROL REGISTER

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| INLVLA7 | INLVLA6 | INLVLA5 | INLVLA4 | INLVLA3 | INLVLA2 | INLVLA1 | INLVLA0 |

| bit 7   |         |         |         |         |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-0 INLVLA<7:0>: PORTA Input Level Select bits

For RA<7:0> pins, respectively

1 = ST input used for PORT reads and interrupt-on-change

0 = TTL input used for PORT reads and interrupt-on-change

#### 17.2.6 A/D CONVERSION PROCEDURE

This is an example procedure for using the ADC to perform an Analog-to-Digital conversion:

- 1. Configure Port:

- Disable pin output driver (Refer to the TRIS register)

- Configure pin as analog (Refer to the ANSEL register)

- 2. Configure the ADC module:

- · Select ADC conversion clock

- · Configure voltage reference

- · Select ADC input channel

- · Turn on ADC module

- 3. Configure ADC interrupt (optional):

- · Clear ADC interrupt flag

- · Enable ADC interrupt

- · Enable peripheral interrupt

- Enable global interrupt<sup>(1)</sup>

- 4. Wait the required acquisition time<sup>(2)</sup>.

- 5. Start conversion by setting the GO/DONE bit.

- Wait for ADC conversion to complete by one of the following:

- Polling the GO/DONE bit

- Waiting for the ADC interrupt (interrupts enabled)

- 7. Read ADC Result.

- 8. Clear the ADC interrupt flag (required if interrupt is enabled).

- **Note 1:** The global interrupt can be disabled if the user is attempting to wake-up from Sleep and resume in-line code execution.

- 2: Refer to Section 17.4 "ADC Acquisition Requirements".

#### **EXAMPLE 17-1: A/D CONVERSION**

```

; This code block configures the ADC

; for polling, Vdd and Vss references, Frc

; clock and ANO input.

;Conversion start & polling for completion

; are included.

BANKSEL ADCON1

MOVLW B'11110000' ;2's complement, Frc

:clock

MOVWF ADCON1

;Vdd and Vss Vref

MOVLW B'00001111'; set negative input

MOVWF ADCON2

;to negative

;reference

BANKSEL TRISA

TRISA,0

;Set RAO to input

BANKSEL ANSEL

ANSEL, 0

BSF

;Set RAO to analog

BANKSEL ADCON0

B'00000001' ;Select channel ANO

MOVLW

MOVWF

ADCONO ; Turn ADC On

CALL

SampleTime ; Acquisiton delay

BSF

ADCON0, ADGO ; Start conversion

ADCONO, ADGO ; Is conversion done?

BTFSC

;No, test again

GOTO

$-1

BANKSEL

ADRESH

ADRESH, W

MOVF

;Read upper 2 bits

RESULTHI ; store in GPR space

MOVWF

```

### 21.2 Register Definitions: Option Register

### REGISTER 21-1: OPTION\_REG: OPTION REGISTER

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| WPUEN   | INTEDG  | TMR0CS  | TMR0SE  | PSA     |         |         |         |

| bit 7   |         |         |         |         |         |         | bit 0   |

Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'u = Bit is unchangedx = Bit is unknown-n/n = Value at POR and BOR/Value at all other Resets'1' = Bit is set'0' = Bit is cleared

bit 7 WPUEN: Weak Pull-Up Enable bit

1 = All weak pull-ups are disabled (except  $\overline{MCLR}$ , if it is enabled) 0 = Weak pull-ups are enabled by individual WPUx latch values

bit 6 INTEDG: Interrupt Edge Select bit

1 = Interrupt on rising edge of INT pin0 = Interrupt on falling edge of INT pin

bit 5 TMR0CS: Timer0 Clock Source Select bit

1 = Transition on T0CKI pin

0 = Internal instruction cycle clock (Fosc/4)

bit 4 TMR0SE: Timer0 Source Edge Select bit

1 = Increment on high-to-low transition on T0CKI pin 0 = Increment on low-to-high transition on T0CKI pin

bit 3 **PSA:** Prescaler Assignment bit

1 = Prescaler is not assigned to the Timer0 module0 = Prescaler is assigned to the Timer0 module

bit 2-0 **PS<2:0>:** Prescaler Rate Select bits

Bit Value Timer0 Rate 000 1:2 001 1:4 1:8 010 011 1:16 100 1:32 1:64 101 1:128 110 1:256 111

### TABLE 21-1: SUMMARY OF REGISTERS ASSOCIATED WITH TIMERO

| Name       | Bit 7                  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register on Page |

|------------|------------------------|--------|--------|--------|--------|--------|--------|--------|------------------|

| INTCON     | GIE                    | PEIE   | TMR0IE | INTE   | IOCIE  | TMR0IF | INTF   | IOCIF  | 79               |

| OPTION_REG | WPUEN                  | INTEDG | TMR0CS | TMR0SE | PSA    |        | 174    |        |                  |

| TMR0       | Timer0 Module Register |        |        |        |        |        |        |        | 172*             |

| TRISA      | TRISA7                 | TRISA6 | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 114              |

**Legend:** — = Unimplemented location, read as '0'. Shaded cells are not used by the Timer0 module.

<sup>\*</sup> Page provides register information.

#### 22.1 Timer1 Operation

The Timer1 module is a 16-bit incrementing counter which is accessed through the TMR1H:TMR1L register pair. Writes to TMR1H or TMR1L directly update the counter.

When used with an internal clock source, the module is a timer and increments on every instruction cycle. When used with an external clock source, the module can be used as either a timer or counter and increments on every selected edge of the external source.

Timer1 is enabled by configuring the TMR1ON and TMR1GE bits in the T1CON and T1GCON registers, respectively. Table 22-1 displays the Timer1 enable selections.

TABLE 22-1: TIMER1 ENABLE SELECTIONS

| TMR10N | TMR1GE | Timer1<br>Operation |

|--------|--------|---------------------|

| 0      | 0      | Off                 |

| 0      | 1      | Off                 |

| 1      | 0      | Always On           |

| 1      | 1      | Count Enabled       |

#### 22.2 Clock Source Selection

The TMR1CS<1:0> and T1OSCEN bits of the T1CON register are used to select the clock source for Timer1. Table 22-2 displays the clock source selections.

#### 22.2.1 INTERNAL CLOCK SOURCE

When the internal clock source is selected, the TMR1H:TMR1L register pair will increment on multiples of Fosc as determined by the Timer1 prescaler.

When the Fosc internal clock source is selected, the Timer1 register value will increment by four counts every instruction clock cycle. Due to this condition, a 2 LSB error in resolution will occur when reading the Timer1 value. To utilize the full resolution of Timer1, an asynchronous input signal must be used to gate the Timer1 clock input.

The following asynchronous sources may be used:

- Asynchronous event on the T1G pin to Timer1 gate

- · C1 or C2 comparator input to Timer1 gate

#### 22.2.2 EXTERNAL CLOCK SOURCE

When the external clock source is selected, the Timer1 module may work as a timer or a counter.

When enabled to count, Timer1 is incremented on the rising edge of the external clock input T1CKI, which can be synchronized to the microcontroller system clock or can run asynchronously.

When used as a timer with a clock oscillator, an external 32.768 kHz crystal can be used in conjunction with the dedicated internal oscillator circuit.

Note:

In Counter mode, a falling edge must be registered by the counter prior to the first incrementing rising edge after any one or more of the following conditions:

- · Timer1 enabled after POR

- Write to TMR1H or TMR1L

- · Timer1 is disabled

- Timer1 is disabled (TMR1ON = 0) when T1CKI is high then Timer1 is enabled (TMR1ON=1) when T1CKI is low

TABLE 22-2: CLOCK SOURCE SELECTIONS

| TMR1CS<1:0> | T10SCEN | Clock Source                 |  |  |  |  |  |

|-------------|---------|------------------------------|--|--|--|--|--|

| 11          | Х       | Reserved                     |  |  |  |  |  |

| 10          | 1       | Timer1 Oscillator            |  |  |  |  |  |

| 10          | 0       | ternal Clocking on T1CKI Pin |  |  |  |  |  |

| 01          | Х       | System Clock (Fosc)          |  |  |  |  |  |

| 00          | Х       | Instruction Clock (Fosc/4)   |  |  |  |  |  |

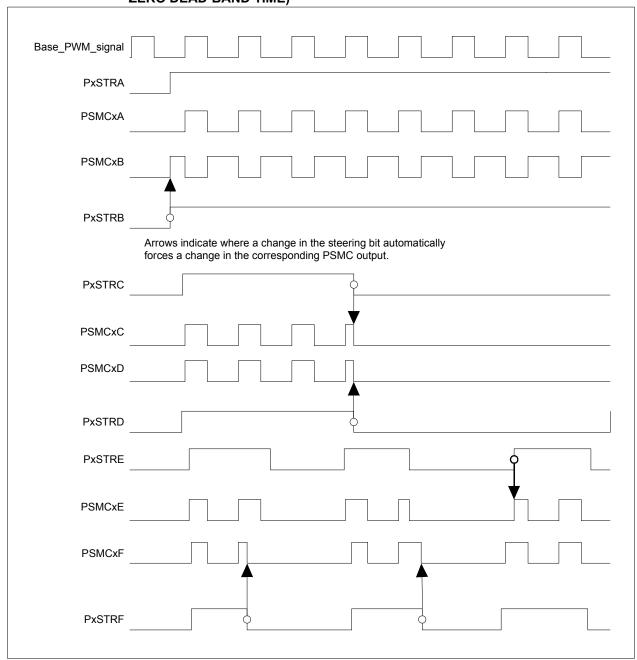

# 24.5.3 COMPLEMENTARY PWM STEERING

In Complementary PWM Steering mode, the primary PWM signal (non-complementary) and complementary signal can be steered according to their respective type.

Primary PWM signal can be steered to any of the following outputs:

- PSMCxA

- PSMCxC

- PSMCxE

The complementary PWM signal can be steered to any of the following outputs:

- PSMCxB

- PSMCxD

- PSMCxE

Examples of unsynchronized complementary steering are shown in Figure 24-17.

FIGURE 24-17: COMPLEMENTARY PWM STEERING WAVEFORM (NO SYNCHRONIZATION, ZERO DEAD-BAND TIME)

#### REGISTER 24-2: PSMCxMDL: PSMC MODULATION CONTROL REGISTER

| R/W-0/0 | R/W-0/0  | R/W-0/0  | U-0 | R/W-0/0     | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |

|---------|----------|----------|-----|-------------|---------|---------|---------|--|

| PxMDLEN | PxMDLPOL | PxMDLBIT | _   | PxMSRC<3:0> |         |         |         |  |

| bit 7   |          |          |     |             |         |         | bit 0   |  |

Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'u = Bit is unchangedx = Bit is unknown-n/n = Value at POR and BOR/Value at all other Resets'1' = Bit is set'0' = Bit is cleared

bit 7 PxMDLEN: PSMC Periodic Modulation Mode Enable bit

1 = PSMCx is active when input signal selected by PxMSRC<3:0> is in its active state (see PxMPOL)

0 = PSMCx module is always active

bit 6 PxMDLPOL: PSMC Periodic Modulation Polarity bit

1 = PSMCx is active when the PSMCx Modulation source output equals logic '0' (active-low)

0 = PSMCx is active when the PSMCx Modulation source output equals logic '1' (active-high)

bit 5 PxMDLBIT: PSMC Periodic Modulation Software Control bit

PxMDLEN = 1 AND PxMSRC<3:0> = 0000

1 = PSMCx is active when the PxMDLPOL equals logic '0'

0 = PSMCx is active when the PxMDLPOL equals logic '1'

PxMDLEN = 0 OR (PxMDLEN = 1 and PxMSRC<3:0> <> '0000')

Does not affect module operation

bit 4 **Unimplemented:** Read as '0'

bit 3-0 PxMSRC<3:0> PSMC Periodic Modulation Source Selection bits

1111 = Reserved

1110 = Reserved

1101 = Reserved

1100 = Reserved 1011 = Reserved

1011 - Neserveu

1010 = Reserved

1001 = Reserved

1000 = PSMCx Modulation Source is PSMCxIN pin

0111 = Reserved

0110 = PSMCx Modulation Source is CCP2

0101 = PSMCx Modulation Source is CCP1

0100 = Reserved

0011 = PSMCx Modulation Source is sync\_C3OUT

0010 = PSMCx Modulation Source is sync\_C2OUT

0001 = PSMCx Modulation Source is sync\_C1OUT

0000 = PSMCx Modulation Source is PxMDLBIT register bit

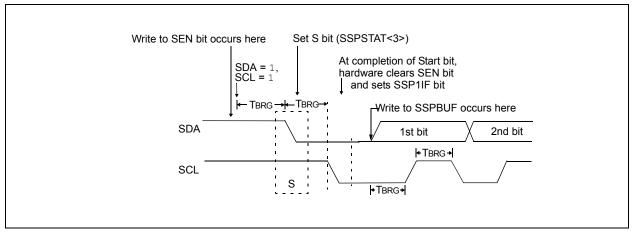

# 26.6.4 I<sup>2</sup>C MASTER MODE START CONDITION TIMING

To initiate a Start condition, the user sets the Start Enable bit, SEN bit of the SSPCON2 register. If the SDA and SCL pins are sampled high, the Baud Rate Generator is reloaded with the contents of SSPADD<7:0> and starts its count. If SCL and SDA are both sampled high when the Baud Rate Generator times out (TBRG), the SDA pin is driven low. The action of the SDA being driven low while SCL is high is the Start condition and causes the S bit of the SSPSTAT1 register to be set. Following this, the Baud Rate Generator is reloaded with the contents of SSPADD<7:0> and resumes its count. When the Baud Rate Generator times out (TBRG), the SEN bit of the SSPCON2 register will be automatically cleared by hardware; the Baud Rate Generator is suspended, leaving the SDA line held low and the Start condition is complete.

- Note 1: If at the beginning of the Start condition, the SDA and SCL pins are already sampled low, or if during the Start condition, the SCL line is sampled low before the SDA line is driven low, a bus collision occurs, the Bus Collision Interrupt Flag, BCL1IF, is set, the Start condition is aborted and the I<sup>2</sup>C module is reset into its Idle state.

- **2:** The Philips I<sup>2</sup>C specification states that a bus collision cannot occur on a Start.

FIGURE 26-26: FIRST START BIT TIMING

### 27.1 EUSART Asynchronous Mode

The EUSART transmits and receives data using the standard non-return-to-zero (NRZ) format. NRZ is implemented with two levels: a VoH mark state which represents a '1' data bit, and a Vol space state which represents a '0' data bit. NRZ refers to the fact that consecutively transmitted data bits of the same value stay at the output level of that bit without returning to a neutral level between each bit transmission. An NRZ transmission port idles in the Mark state. Each character transmission consists of one Start bit followed by eight or nine data bits and is always terminated by one or more Stop bits. The Start bit is always a space and the Stop bits are always marks. The most common data format is 8 bits. Each transmitted bit persists for a period of 1/(Baud Rate). An on-chip dedicated 8-bit/16-bit Baud Rate Generator is used to derive standard baud rate frequencies from the system oscillator. See Table 27-5 for examples of baud rate configurations.

The EUSART transmits and receives the LSb first. The EUSART's transmitter and receiver are functionally independent, but share the same data format and baud rate. Parity is not supported by the hardware, but can be implemented in software and stored as the ninth data bit.

### 27.1.1 EUSART ASYNCHRONOUS TRANSMITTER

The EUSART transmitter block diagram is shown in Figure 27-1. The heart of the transmitter is the serial Transmit Shift Register (TSR), which is not directly accessible by software. The TSR obtains its data from the transmit buffer, which is the TXREG register.

#### 27.1.1.1 Enabling the Transmitter

The EUSART transmitter is enabled for asynchronous operations by configuring the following three control bits:

- TXEN = 1

- SYNC = 0

- SPEN = 1

All other EUSART control bits are assumed to be in their default state.

Setting the TXEN bit of the TXSTA register enables the transmitter circuitry of the EUSART. Clearing the SYNC bit of the TXSTA register configures the EUSART for asynchronous operation. Setting the SPEN bit of the RCSTA register enables the EUSART and automatically configures the TX/CK I/O pin as an output. If the TX/CK pin is shared with an analog peripheral, the analog I/O function must be disabled by clearing the corresponding ANSEL bit.

**Note:** The TXIF Transmitter Interrupt flag is set when the TXEN enable bit is set.

#### 27.1.1.2 Transmitting Data

A transmission is initiated by writing a character to the TXREG register. If this is the first character, or the previous character has been completely flushed from the TSR, the data in the TXREG is immediately transferred to the TSR register. If the TSR still contains all or part of a previous character, the new character data is held in the TXREG until the Stop bit of the previous character has been transmitted. The pending character in the TXREG is then transferred to the TSR in one Tcy immediately following the Stop bit transmission. The transmission of the Start bit, data bits and Stop bit sequence commences immediately following the transfer of the data to the TSR from the TXREG.

#### 27.1.1.3 Transmit Data Polarity

The polarity of the transmit data can be controlled with the SCKP bit of the BAUDxCON register. The default state of this bit is '0' which selects high true transmit idle and data bits. Setting the SCKP bit to '1' will invert the transmit data resulting in low true idle and data bits. The SCKP bit controls transmit data polarity in Asynchronous mode only. In Synchronous mode, the SCKP bit has a different function. See Section 27.5.1.2 "Clock Polarity".

#### 27.1.1.4 Transmit Interrupt Flag

The TXIF interrupt flag bit of the PIR1 register is set whenever the EUSART transmitter is enabled and no character is being held for transmission in the TXREG. In other words, the TXIF bit is only clear when the TSR is busy with a character and a new character has been queued for transmission in the TXREG. The TXIF flag bit is not cleared immediately upon writing TXREG. TXIF becomes valid in the second instruction cycle following the write execution. Polling TXIF immediately following the TXREG write will return invalid results. The TXIF bit is read-only, it cannot be set or cleared by software.

The TXIF interrupt can be enabled by setting the TXIE interrupt enable bit of the PIE1 register. However, the TXIF flag bit will be set whenever the TXREG is empty, regardless of the state of TXIE enable bit.

To use interrupts when transmitting data, set the TXIE bit only when there is more data to send. Clear the TXIE interrupt enable bit upon writing the last character of the transmission to the TXREG.

# 27.5.2.3 EUSART Synchronous Slave Reception

The operation of the Synchronous Master and Slave modes is identical (Section 27.5.1.5 "Synchronous Master Reception"), with the following exceptions:

- Sleep

- CREN bit is always set, therefore the receiver is never idle

- · SREN bit, which is a "don't care" in Slave mode

A character may be received while in Sleep mode by setting the CREN bit prior to entering Sleep. Once the word is received, the RSR register will transfer the data to the RCREG register. If the RCIE enable bit is set, the interrupt generated will wake the device from Sleep and execute the next instruction. If the GIE bit is also set, the program will branch to the interrupt vector.

# 27.5.2.4 Synchronous Slave Reception Set-up:

- Set the SYNC and SPEN bits and clear the CSRC bit.

- Clear the ANSEL bit for both the CK and DT pins (if applicable).

- If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 4. If 9-bit reception is desired, set the RX9 bit.

- 5. Set the CREN bit to enable reception.

- The RCIF bit will be set when reception is complete. An interrupt will be generated if the RCIE bit was set.

- 7. If 9-bit mode is enabled, retrieve the Most Significant bit from the RX9D bit of the RCSTA register.

- Retrieve the eight Least Significant bits from the receive FIFO by reading the RCREG register.

- If an overrun error occurs, clear the error by either clearing the CREN bit of the RCSTA register or by clearing the SPEN bit which resets the EUSART.

TABLE 27-10: SUMMARY OF REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE RECEPTION

| Name    | Bit 7                        | Bit 6   | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0   | Register<br>on Page |

|---------|------------------------------|---------|--------|--------|--------|--------|--------|---------|---------------------|

| APFCON  | C2OUTSEL                     | CC1PSEL | SDOSEL | SCKSEL | SDISEL | TXSEL  | RXSEL  | CCP2SEL | 111                 |

| BAUDCON | ABDOVF                       | RCIDL   | _      | SCKP   | BRG16  | _      | WUE    | ABDEN   | 322                 |

| INTCON  | GIE                          | PEIE    | TMR0IE | INTE   | IOCIE  | TMR0IF | INTF   | IOCIF   | 79                  |

| PIE1    | TMR1GIE                      | ADIE    | RCIE   | TXIE   | SSP1IE | CCP1IE | TMR2IE | TMR1IE  | 80                  |

| PIR1    | TMR1GIF                      | ADIF    | RCIF   | TXIF   | SSP1IF | CCP1IF | TMR2IF | TMR1IF  | 83                  |

| RCREG   | EUSART Receive Data Register |         |        |        |        |        |        |         | 315*                |

| RCSTA   | SPEN                         | RX9     | SREN   | CREN   | ADDEN  | FERR   | OERR   | RX9D    | 321                 |

| TRISC   | TRISC7                       | TRISC6  | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0  | 125                 |

| TXSTA   | CSRC                         | TX9     | TXEN   | SYNC   | SENDB  | BRGH   | TRMT   | TX9D    | 320                 |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used for synchronous slave reception.

<sup>\*</sup> Page provides register information.

### 27.6 EUSART Operation During Sleep

The EUSART will remain active during Sleep only in the Synchronous Slave mode. All other modes require the system clock and therefore cannot generate the necessary signals to run the Transmit or Receive Shift registers during Sleep.

Synchronous Slave mode uses an externally generated clock to run the Transmit and Receive Shift registers.

### 27.6.1 SYNCHRONOUS RECEIVE DURING SLEEP

To receive during Sleep, all the following conditions must be met before entering Sleep mode:

- RCSTA and TXSTA Control registers must be configured for Synchronous Slave Reception (see Section 27.5.2.4 "Synchronous Slave Reception Set-up:").

- If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- The RCIF interrupt flag must be cleared by reading RCREG to unload any pending characters in the receive buffer.

Upon entering Sleep mode, the device will be ready to accept data and clocks on the RX/DT and TX/CK pins, respectively. When the data word has been completely clocked in by the external device, the RCIF interrupt flag bit of the PIR1 register will be set. Thereby, waking the processor from Sleep.

Upon waking from Sleep, the instruction following the SLEEP instruction will be executed. If the Global Interrupt Enable (GIE) bit of the INTCON register is also set, then the Interrupt Service Routine at address 004h will be called.

### 27.6.2 SYNCHRONOUS TRANSMIT DURING SLEEP

To transmit during Sleep, all the following conditions must be met before entering Sleep mode:

- RCSTA and TXSTA Control registers must be configured for synchronous slave transmission (see Section 27.5.2.2 "Synchronous Slave Transmission Set-up:").

- The TXIF interrupt flag must be cleared by writing the output data to the TXREG, thereby filling the TSR and transmit buffer.

- If interrupts are desired, set the TXIE bit of the PIE1 register and the PEIE bit of the INTCON register

- Interrupt enable bits TXIE of the PIE1 register and PEIE of the INTCON register must set.

Upon entering Sleep mode, the device will be ready to accept clocks on TX/CK pin and transmit data on the RX/DT pin. When the data word in the TSR has been completely clocked out by the external device, the pending byte in the TXREG will transfer to the TSR and the TXIF flag will be set. Thereby, waking the processor from Sleep. At this point, the TXREG is available to accept another character for transmission, which will clear the TXIF flag.

Upon waking from Sleep, the instruction following the SLEEP instruction will be executed. If the Global Interrupt Enable (GIE) bit is also set then the Interrupt Service Routine at address 0004h will be called.

#### 27.6.3 ALTERNATE PIN LOCATIONS

This module incorporates I/O pins that can be moved to other locations with the use of the alternate pin function register, APFCON. To determine which pins can be moved and what their default locations are upon a Reset, see Section 13.1 "Alternate Pin Function" for more information.

**Note:** Unless otherwise noted, VIN = 5V, FOSC = 300 kHz, CIN = 0.1  $\mu$ F, TA = 25°C.

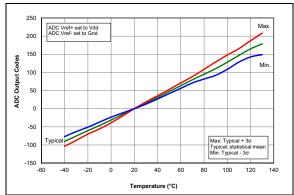

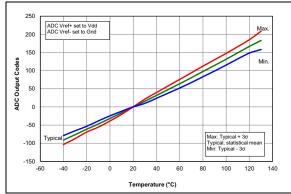

FIGURE 31-103: Temp. Indicator Slope

Normalized to 20°C, High Range, VDD = 3.6V,

PIC16F1782/3 Only.

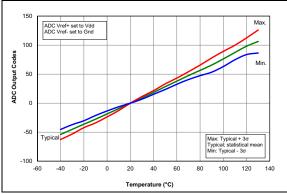

FIGURE 31-104: Temp. Indicator Slope

Normalized to 20°C, Low Range, VDD = 3.0V,

PIC16F1782/3 Only.

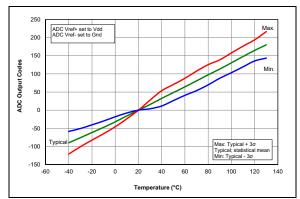

FIGURE 31-105: Temp. Indicator Slope

Normalized to 20°C, Low Range, VDD = 1.8V,

PIC16LF1782/3 Only.

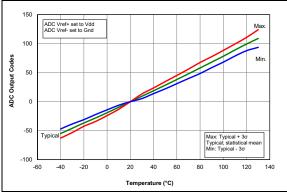

FIGURE 31-106: Temp. Indicator Slope

Normalized to 20°C, Low Range, VDD = 3.0V,

PIC16LF1782/3 Only.

FIGURE 31-107: Temp. Indicator Slope Normalized to 20°C, High Range, VDD = 3.6V, PIC16LF1782/3 Only.

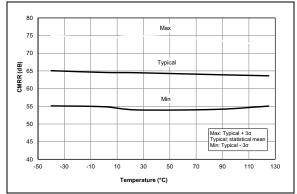

**FIGURE 31-108:** Op Amp, Common Mode Rejection Ratio (CMRR), VDD = 3.0V.

#### 32.2 MPLAB XC Compilers

The MPLAB XC Compilers are complete ANSI C compilers for all of Microchip's 8, 16, and 32-bit MCU and DSC devices. These compilers provide powerful integration capabilities, superior code optimization and ease of use. MPLAB XC Compilers run on Windows, Linux or MAC OS X.

For easy source level debugging, the compilers provide debug information that is optimized to the MPLAB X IDE.

The free MPLAB XC Compiler editions support all devices and commands, with no time or memory restrictions, and offer sufficient code optimization for most applications.

MPLAB XC Compilers include an assembler, linker and utilities. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. MPLAB XC Compiler uses the assembler to produce its object file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- · Command-line interface

- · Rich directive set

- · Flexible macro language

- · MPLAB X IDE compatibility

#### 32.3 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel® standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code, and COFF files for debugging.

The MPASM Assembler features include:

- Integration into MPLAB X IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multipurpose source files

- Directives that allow complete control over the assembly process

### 32.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

# 32.5 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC DSC devices. MPLAB XC Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- · Command-line interface

- · Rich directive set

- · Flexible macro language

- · MPLAB X IDE compatibility