#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PSMC, PWM, WDT                                 |

| Number of I/O              | 24                                                                          |

| Program Memory Size        | 7KB (4K x 14)                                                               |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 512 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 11x12b; D/A 1x8b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                              |

| Supplier Device Package    | 28-SOIC                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1783t-i-so |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

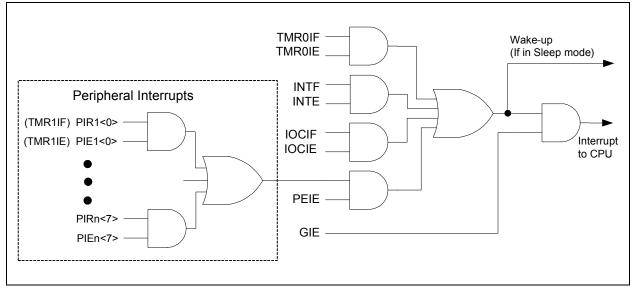

## 8.0 INTERRUPTS

The interrupt feature allows certain events to preempt normal program flow. Firmware is used to determine the source of the interrupt and act accordingly. Some interrupts can be configured to wake the MCU from Sleep mode.

This chapter contains the following information for Interrupts:

- · Operation

- Interrupt Latency

- · Interrupts During Sleep

- INT Pin

- · Automatic Context Saving

Many peripherals produce interrupts. Refer to the corresponding chapters for details.

A block diagram of the interrupt logic is shown in Figure 8-1.

#### FIGURE 8-1: INTERRUPT LOGIC

u = Bit is unchanged

'1' = Bit is set

| R/W/HS-0/0                               | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0   | R/W/HS-0/0       | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 |

|------------------------------------------|------------|------------|--------------|------------------|------------|------------|------------|

| IOCxF7                                   | IOCxF6     | IOCxF5     | IOCxF4       | IOCxF3           | IOCxF2     | IOCxF1     | IOCxF0     |

| bit 7                                    |            |            |              |                  |            |            | bit 0      |

|                                          |            |            |              |                  |            |            |            |

| Legend:                                  |            |            |              |                  |            |            |            |

| R = Readable bit W = Writable bit U = Ur |            |            | U = Unimplen | nented bit, read | as '0'     |            |            |

#### REGISTER 14-3: IOCxF: INTERRUPT-ON-CHANGE FLAG REGISTER

x = Bit is unknown

'0' = Bit is cleared

bit 7-0 IOCxF<7:0>: Interrupt-on-Change Flag bits<sup>(1)</sup>

1 = An enabled change was detected on the associated pin.

Set when IOCxPx = 1 and a rising edge was detected RBx, or when IOCxNx = 1 and a falling edge was detected on RBx.

HS - Bit is set in hardware

-n/n = Value at POR and BOR/Value at all other Resets

0 = No change was detected, or the user cleared the detected change.

**Note 1:** For IOCEF register, bit 3 (IOCEF3) is the only implemented bit in the register.

| Name   | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------------------|

| ANSELB | —      | _      | ANSB5  | ANSB4  | ANSB3  | ANSB2  | ANSB1  | ANSB0  | 121                 |

| INTCON | GIE    | PEIE   | TMR0IE | INTE   | IOCIE  | TMR0IF | INTF   | IOCIF  | 79                  |

| IOCAF  | IOCAF7 | IOCAF6 | IOCAF5 | IOCAF4 | IOCAF3 | IOCAF2 | IOCAF1 | IOCAF0 | 134                 |

| IOCAN  | IOCAN7 | IOCAN6 | IOCAN5 | IOCAN4 | IOCAN3 | IOCAN2 | IOCAN1 | IOCAN0 | 133                 |

| IOCAP  | IOCAP7 | IOCAP6 | IOCAP5 | IOCAP4 | IOCAP3 | IOCAP2 | IOCAP1 | IOCAP0 | 133                 |

| IOCBF  | IOCBF7 | IOCBF6 | IOCBF5 | IOCBF4 | IOCBF3 | IOCBF2 | IOCBF1 | IOCBF0 | 134                 |

| IOCBN  | IOCBN7 | IOCBN6 | IOCBN5 | IOCBN4 | IOCBN3 | IOCBN2 | IOCBN1 | IOCBN0 | 133                 |

| IOCBP  | IOCBP7 | IOCBP6 | IOCBP5 | IOCBP4 | IOCBP3 | IOCBP2 | IOCBP1 | IOCBP0 | 133                 |

| IOCCF  | IOCCF7 | IOCCF6 | IOCCF5 | IOCCF4 | IOCCF3 | IOCCF2 | IOCCF1 | IOCCF0 | 134                 |

| IOCCN  | IOCCN7 | IOCCN6 | IOCCN5 | IOCCN4 | IOCCN3 | IOCCN2 | IOCCN1 | IOCCN0 | 133                 |

| IOCCP  | IOCCP7 | IOCCP6 | IOCCP5 | IOCCP4 | IOCCP3 | IOCCP2 | IOCCP1 | IOCCP0 | 133                 |

| IOCEF  |        | _      | _      | _      | IOCEF3 | _      | _      |        | 134                 |

| IOCEN  | —      | _      | _      | —      | IOCEN3 | _      | —      | —      | 133                 |

| IOCEP  |        |        |        | _      | IOCEP3 |        | _      | —      | 133                 |

| TRISB  | TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 | 120                 |

TABLE 14-1: SUMMARY OF REGISTERS ASSOCIATED WITH INTERRUPT-ON-CHANGE

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by interrupt-on-change.

## 15.0 FIXED VOLTAGE REFERENCE (FVR)

The Fixed Voltage Reference, or FVR, is a stable voltage reference, independent of VDD, with 1.024V, 2.048V or 4.096V selectable output levels. The output of the FVR can be configured to supply a reference voltage to the following:

- · ADC input channel

- · ADC positive reference

- · Comparator positive input

- Digital-to-Analog Converter (DAC)

The FVR can be enabled by setting the FVREN bit of the FVRCON register.

## 15.1 Independent Gain Amplifiers

The output of the FVR supplied to the ADC, Comparators, and DAC is routed through two independent programmable gain amplifiers. Each amplifier can be programmed for a gain of 1x, 2x or 4x, to produce the three possible voltage levels.

The ADFVR<1:0> bits of the FVRCON register are used to enable and configure the gain amplifier settings for the reference supplied to the ADC module. Reference Section 17.0 "Analog-to-Digital Converter (ADC) Module" for additional information.

The CDAFVR<1:0> bits of the FVRCON register are used to enable and configure the gain amplifier settings for the reference supplied to the DAC and comparator module. Reference Section 19.0 "Digital-to-Analog Converter (DAC) Module" and Section 20.0 "Comparator Module" for additional information.

## 15.2 FVR Stabilization Period

When the Fixed Voltage Reference module is enabled, it requires time for the reference and amplifier circuits to stabilize. Once the circuits stabilize and are ready for use, the FVRRDY bit of the FVRCON register will be set. See **Section 30.0** "**Electrical Specifications**" for the minimum delay requirement.

## 15.3 FVR Buffer Stabilization Period

When either FVR Buffer1 or FVR Buffer 2 is enabled, the buffer amplifier circuits require 30  $\mu$ s to stabilize. This stabilization time is required even when the FVR is already operating and stable.

| Name   | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1      | Bit 0 | Register<br>on page |

|--------|-------|--------|-------|-------|-------|-------|------------|-------|---------------------|

| FVRCON | FVREN | FVRRDY | TSEN  | TSRNG |       |       | ADFVR<1:0> |       | 136                 |

Legend: Shaded cells are unused by the temperature indicator module.

## **17.1 ADC Configuration**

When configuring and using the ADC the following functions must be considered:

- Port configuration

- · Channel selection

- Single-ended

- Differential

- · ADC voltage reference selection

- ADC conversion clock source

- · Interrupt control

- Result formatting

#### 17.1.1 PORT CONFIGURATION

The ADC can be used to convert both analog and digital signals. When converting analog signals, the I/O pin should be configured for analog by setting the associated TRIS and ANSEL bits. Refer to **Section 13.0 "I/O Ports"** for more information.

| Note: | Analog voltages on any pin that is defined |  |  |  |  |  |  |  |

|-------|--------------------------------------------|--|--|--|--|--|--|--|

|       | as a digital input may cause the input     |  |  |  |  |  |  |  |

|       | buffer to conduct excess current.          |  |  |  |  |  |  |  |

#### 17.1.2 CHANNEL SELECTION

There are up to 14 channel selections available:

- AN<13:8, 4:0> pins

- Temperature Indicator

- DAC\_output

- FVR (Fixed Voltage Reference) Output

Refer to Section 15.0 "Fixed Voltage Reference (FVR)" and Section 16.0 "Temperature Indicator Module" for more information on these channel selections.

When converting differential signals, the negative input for the channel is selected with the CHSN<3:0> bits of the ADCON2 register. Any positive input can be paired with any negative input to determine the differential channel.

The CHS<4:0> bits of the ADCON0 register determine which positive channel is selected.

When CHSN<3:0> = 1111 then the ADC is effectively a single ended ADC converter.

When changing channels, a delay is required before starting the next conversion.

## 17.1.3 ADC VOLTAGE REFERENCE

The ADPREF bits of the ADCON1 register provide control of the positive voltage reference. The positive voltage reference can be:

- VREF+

- Vdd

- FVR Buffer1

The ADNREF bits of the ADCON1 register provide control of the negative voltage reference. The negative voltage reference can be:

- VREF- pin

- Vss

See **Section 15.0 "Fixed Voltage Reference (FVR)**" for more details on the Fixed Voltage Reference.

#### 17.1.4 CONVERSION CLOCK

The source of the conversion clock is software selectable via the ADCS bits of the ADCON1 register. There are seven possible clock options:

- Fosc/2

- · Fosc/4

- Fosc/8

- Fosc/16

- Fosc/32

- Fosc/64

- · FRC (dedicated internal FRC oscillator)

The time to complete one bit conversion is defined as TAD. One full 12-bit conversion requires 15 TAD periods as shown in Figure 17-2.

For correct conversion, the appropriate TAD specification must be met. Refer to the ADC conversion requirements in **Section 30.0 "Electrical Specifications"** for more information. Table 17-1 gives examples of appropriate ADC clock selections.

**Note:** Unless using the FRC, any changes in the system clock frequency will change the ADC clock frequency, which may adversely affect the ADC result.

## 19.6 Register Definitions: DAC Control

| R/W-0/0                                                            | U-0                                                                     | R/W-0/0                                                  | R/W-0/0         | R/W-0/0       | R/W-0/0          | U-0        | R/W-0/0 |

|--------------------------------------------------------------------|-------------------------------------------------------------------------|----------------------------------------------------------|-----------------|---------------|------------------|------------|---------|

| DACEN                                                              | _                                                                       | DACOE1                                                   | DACOE2          | DACP          | SS<1:0>          | _          | DACNSS  |

| bit 7                                                              |                                                                         | •                                                        | •               | •             |                  |            | bit 0   |

| Legend:                                                            |                                                                         |                                                          |                 |               |                  |            |         |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as 0 |                                                                         |                                                          |                 |               |                  | is '0'     |         |

| u = Bit is unchanged x = Bit is unknown -n/n = Value at POR a      |                                                                         |                                                          |                 | t POR and BOR | Value at all oth | ner Resets |         |

| '1' = Bit is set                                                   | t                                                                       | '0' = Bit is clea                                        | ared            |               |                  |            |         |

| bit 7                                                              | <b>DACEN:</b> DAC<br>1 = DAC is er<br>0 = DAC is dis                    | abled                                                    |                 |               |                  |            |         |

| bit 6                                                              | Unimplement                                                             | ed: Read as '0'                                          |                 |               |                  |            |         |

| bit 5                                                              | 1 = DAC volta                                                           | C Voltage Outp<br>age level is also<br>age level is disc | an output on t  |               |                  |            |         |

| bit 4                                                              | 1 = DAC volta                                                           | C Voltage Outp<br>age level is also<br>age level is disc | an output on t  |               |                  |            |         |

| bit 3-2                                                            | DACPSS<1:03<br>11 = Reserve<br>10 = FVR But<br>01 = VREF+ p<br>00 = VDD | ffer2 output                                             | Source Selec    | t bits        |                  |            |         |

| bit 1                                                              | Unimplement                                                             | ed: Read as '0'                                          |                 |               |                  |            |         |

| bit 0                                                              | <b>DACNSS:</b> DAG<br>1 = VREF- pin<br>0 = VSS                          | C Negative Sou                                           | rce Select bits |               |                  |            |         |

#### REGISTER 19-1: DACCON0: VOLTAGE REFERENCE CONTROL REGISTER 0

## REGISTER 19-2: DACCON1: VOLTAGE REFERENCE CONTROL REGISTER 1

| R/W-0/0          | R/W-0/0 | R/W-0/0           | R/W-0/0 | R/W-0/0        | R/W-0/0            | R/W-0/0            | R/W-0/0   |

|------------------|---------|-------------------|---------|----------------|--------------------|--------------------|-----------|

|                  |         |                   | DAC     | R<7:0>         |                    |                    |           |

| bit 7            |         |                   |         |                |                    |                    | bit 0     |

|                  |         |                   |         |                |                    |                    |           |

| Legend:          |         |                   |         |                |                    |                    |           |

| R = Readable b   | bit     | W = Writable b    | it      | U = Unimplem   | nented bit, read a | as 'O'             |           |

| u = Bit is uncha | inged   | x = Bit is unkno  | own     | -n/n = Value a | t POR and BOR      | /Value at all othe | er Resets |

| '1' = Bit is set |         | '0' = Bit is clea | red     |                |                    |                    |           |

bit 7-0 DACR<7:0>: DAC Voltage Output Select bits

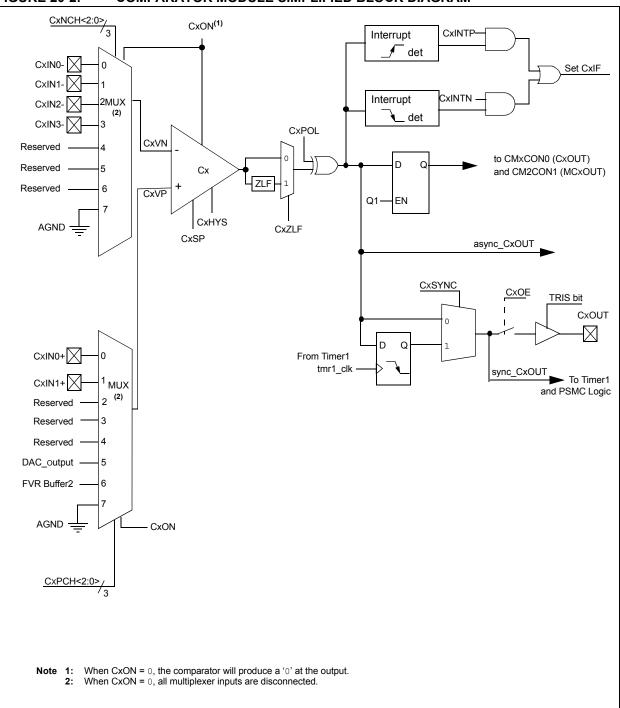

#### FIGURE 20-2: COMPARATOR MODULE SIMPLIFIED BLOCK DIAGRAM

## 22.3 Timer1 Prescaler

Timer1 has four prescaler options allowing 1, 2, 4 or 8 divisions of the clock input. The T1CKPS bits of the T1CON register control the prescale counter. The prescale counter is not directly readable or writable; however, the prescaler counter is cleared upon a write to TMR1H or TMR1L.

## 22.4 Timer1 Oscillator

A dedicated low-power 32.768 kHz oscillator circuit is built-in between pins T1OSI (input) and T1OSO (amplifier output). This internal circuit is to be used in conjunction with an external 32.768 kHz crystal.

The oscillator circuit is enabled by setting the T1OS-CEN bit of the T1CON register. The oscillator will continue to run during Sleep.

Note: The oscillator requires a start-up and stabilization time before use. Thus, T1OSCEN should be set and a suitable delay observed prior to using Timer1. A suitable delay similar to the OST delay can be implemented in software by clearing the TMR1IF bit then presetting the TMR1H:TMR1L register pair to FC00h. The TMR1IF flag will be set when 1024 clock cycles have elapsed, thereby indicating that the oscillator is running and reasonably stable.

## 22.5 Timer1 Operation in Asynchronous Counter Mode

If the control bit T1SYNC of the T1CON register is set, the external clock input is not synchronized. The timer increments asynchronously to the internal phase clocks. If the external clock source is selected then the timer will continue to run during Sleep and can generate an interrupt on overflow, which will wake-up the processor. However, special precautions in software are needed to read/write the timer (see Section 22.5.1 "Reading and Writing Timer1 in Asynchronous Counter Mode").

| Note: | When switching from synchronous to        |

|-------|-------------------------------------------|

|       | asynchronous operation, it is possible to |

|       | skip an increment. When switching from    |

|       | asynchronous to synchronous operation,    |

|       | it is possible to produce an additional   |

|       | increment.                                |

#### 22.5.1 READING AND WRITING TIMER1 IN ASYNCHRONOUS COUNTER MODE

Reading TMR1H or TMR1L while the timer is running from an external asynchronous clock will ensure a valid read (taken care of in hardware). However, the user should keep in mind that reading the 16-bit timer in two 8-bit values itself, poses certain problems, since the timer may overflow between the reads.

For writes, it is recommended that the user simply stop the timer and write the desired values. A write contention may occur by writing to the timer registers, while the register is incrementing. This may produce an unpredictable value in the TMR1H:TMR1L register pair.

## 22.6 Timer1 Gate

Timer1 can be configured to count freely or the count can be enabled and disabled using Timer1 gate circuitry. This is also referred to as Timer1 Gate Enable.

Timer1 gate can also be driven by multiple selectable sources.

## 22.6.1 TIMER1 GATE ENABLE

The Timer1 Gate Enable mode is enabled by setting the TMR1GE bit of the T1GCON register. The polarity of the Timer1 Gate Enable mode is configured using the T1GPOL bit of the T1GCON register.

When Timer1 Gate Enable mode is enabled, Timer1 will increment on the rising edge of the Timer1 clock source. When Timer1 Gate Enable mode is disabled, no incrementing will occur and Timer1 will hold the current count. See Figure 22-3 for timing details.

TABLE 22-3: TIMER1 GATE ENABLE SELECTIONS

| T1CLK      | T1GPOL | T1G Timer1 Operation |             |  |

|------------|--------|----------------------|-------------|--|

| $\uparrow$ | 0      | 0                    | Counts      |  |

| $\uparrow$ | 0      | 1                    | Holds Count |  |

| $\uparrow$ | 1      | 0                    | Holds Count |  |

| 1          | 1      | 1                    | Counts      |  |

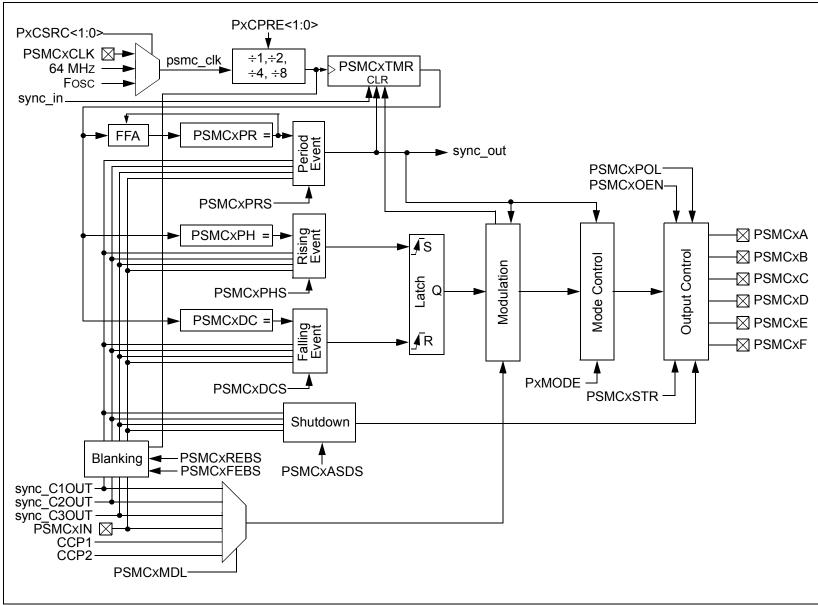

## 24.2 Event Sources

There are two main sources for the period, rising edge and falling edge events:

- · Synchronous input

- Time base

- Asynchronous Inputs

- Digital Inputs

- Analog inputs

#### 24.2.1 TIME BASE

The Time Base section consists of several smaller pieces.

- 16-bit time base counter

- 16-bit Period register

- 16-bit Phase register (rising edge event)

- 16-bit Duty Cycle register (falling edge event)

- · Clock control

- Interrupt Generator

An example of a fully synchronous PWM waveform generated with the time base is shown in Figure 24-2.

The PSMCxLD bit of the PSMCxCON register is provided to synchronize changes to the event Count registers. Changes are withheld from taking action until the first period event Reset after the PSMCxLD bit is set. For example, to change the PWM frequency, while maintaining the same effective duty cycle, the Period and Duty Cycle registers need to be changed. The changes to all four registers take effect simultaneously on the period event Reset after the PSMCxLD bit is set.

## 24.2.1.1 16-bit Counter (Time Base)

The PSMCxTMR is the counter used as a timing reference for each synchronous PWM period. The counter starts at 0000h and increments to FFFFh on the rising edge of the psmc\_clk signal.

When the counter rolls over from FFFFh to 0000h without a period event occurring, the overflow interrupt will be generated, thereby setting the PxTOVIF bit of the PSMC Time Base Interrupt Control (PSMCxINT) register (Register 24-32).

The PSMCxTMR counter is reset on both synchronous and asynchronous period events.

The PSMCxTMR is accessible to software as two 8-bit registers:

- PSMC Time Base Counter Low (PSMCxTMRL) register (Register 24-17)

- PSMC PSMC Time Base Counter High (PSMCxTMRH) register (Register 24-18)

PSMCxTMR is reset to the default POR value when the PSMCxEN bit is cleared.

#### 24.2.1.2 16-bit Period Register

The PSMCxPR Period register is used to determine a synchronous period event referenced to the 16-bit PSMCxTMR digital counter. A match between the PSMCxTMR and PSMCxPR register values will generate a period event.

The match will generate a period match interrupt, thereby setting the PxTPRIF bit of the PSMC Time Base Interrupt Control (PSMCxINT) register (Register 24-32).

The 16-bit period value is accessible to software as two 8-bit registers:

- PSMC Period Count Low Byte (PSMCxPRL) register (Register 24-23)

- PSMC Period Count High Byte (PSMCxPRH) register (Register 24-24)

The 16-bit period value is double-buffered before it is presented to the 16-bit time base for comparison. The buffered registers are updated on the first period event Reset after the PSMCxLD bit of the PSMCxCON register is set.

The synchronous PWM period time can be determined from Equation 24-1.

#### EQUATION 24-1: PWM PERIOD

$$Period = \frac{\text{PSMCxPR[15:0]} + 1}{F_{\text{psmc_clk}}}$$

## 24.2.1.3 16-bit Phase Register

The PSMCxPH Phase register is used to determine a synchronous rising edge event referenced to the 16-bit PSMCxTMR digital counter. A match between the PSMCxTMR and the PSMCxPH register values will generate a rising edge event.

The match will generate a phase match interrupt, thereby setting the PxTPHIF bit of the PSMC Time Base Interrupt Control (PSMCxINT) register (Register 24-32).

The 16-bit phase value is accessible to software as two 8-bit registers:

- PSMC Phase Count Low Byte (PSMCxPHL) register (Register 24-32)

- PSMC Phase Count High Byte (PSMCxPHH) register (Register 24-32)

The 16-bit phase value is double-buffered before it is presented to the 16-bit PSMCxTMR for comparison. The buffered registers are updated on the first period event Reset after the PSMCxLD bit of the PSMCxCON register is set.

## REGISTER 24-3: PSMC1SYNC: PSMC1 SYNCHRONIZATION CONTROL REGISTER

| U-0               | U-0                                                                                    | U-0              | U-0 | U-0                                | U-0             | R/W-0/0            | R/W-0/0 |  |

|-------------------|----------------------------------------------------------------------------------------|------------------|-----|------------------------------------|-----------------|--------------------|---------|--|

| —                 | —                                                                                      | —                | _   | _                                  | _               | P1SYNC<1:0>        |         |  |

| bit 7             |                                                                                        |                  |     |                                    |                 |                    | bit 0   |  |

|                   |                                                                                        |                  |     |                                    |                 |                    |         |  |

| Legend:           |                                                                                        |                  |     |                                    |                 |                    |         |  |

| R = Readable bi   | t                                                                                      | W = Writable bit |     | U = Unimplemented bit, read as '0' |                 |                    |         |  |

|                   | = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other R |                  |     |                                    | POR and BOR/Val | ue at all other Re | sets    |  |

| u = Bit is unchan |                                                                                        |                  |     |                                    |                 |                    |         |  |

| bit 1-0 | P1SYNC<1:0>: PSMC1 Period Synchronization Mode bits |

|---------|-----------------------------------------------------|

|         | 11 = Reserved – Do not use                          |

|         | 10 = PSMC1 is synchronized with the PSMC2 module    |

|         | 01 = Reserved – Do not use                          |

|         | 00 = PSMC1 is synchronized with period event        |

#### REGISTER 24-4: PSMC2SYNC: PSMC2 SYNCHRONIZATION CONTROL REGISTER

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0/0 | R/W-0/0 |

|-------|-----|-----|-----|-----|-----|---------|---------|

| —     | —   | —   | —   | —   | —   | P2SYN   | C<1:0>  |

| bit 7 |     |     |     |     |     |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

#### bit 7-2 Unimplemented: Read as '0'

bit 1-0

P2SYNC<1:0>: PSMC2 Period Synchronization Mode bits

11 = Reserved – Do not use

10 = Reserved – Do not use

- 01 = PSMC2 is synchronized with the PSMC1 module

- 00 = PSMC2 is synchronized with period event

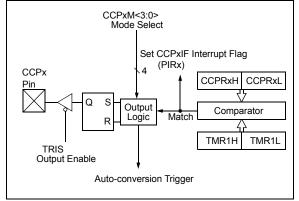

## 25.2 Compare Mode

The Compare mode function described in this section is available and identical for all CCP modules.

Compare mode makes use of the 16-bit Timer1 resource. The 16-bit value of the CCPRxH:CCPRxL register pair is constantly compared against the 16-bit value of the TMR1H:TMR1L register pair. When a match occurs, one of the following events can occur:

- · Toggle the CCPx output

- Set the CCPx output

- · Clear the CCPx output

- Generate an Auto-conversion Trigger

- · Generate a Software Interrupt

The action on the pin is based on the value of the CCPxM<3:0> control bits of the CCPxCON register. At the same time, the interrupt flag CCPxIF bit is set.

All Compare modes can generate an interrupt.

Figure 25-2 shows a simplified diagram of the compare operation.

## FIGURE 25-2: COMPARE MODE OPERATION BLOCK DIAGRAM

## 25.2.1 CCPX PIN CONFIGURATION

The user must configure the CCPx pin as an output by clearing the associated TRIS bit.

The CCP2 pin function can be moved to alternate pins using the APFCON register (Register 13-1). Refer to **Section 13.1 "Alternate Pin Function**" for more details.

| Note: | Clearing the CCPxCON register will force    |

|-------|---------------------------------------------|

|       | the CCPx compare output latch to the        |

|       | default low level. This is not the PORT I/O |

|       | data latch.                                 |

## 25.2.2 TIMER1 MODE RESOURCE

In Compare mode, Timer1 must be running in either Timer mode or Synchronized Counter mode. The compare operation may not work in Asynchronous Counter mode. See Section 22.0 "Timer1 Module with Gate Control" for more information on configuring Timer1.

Note: Clocking Timer1 from the system clock (Fosc) should not be used in Compare mode. In order for Compare mode to recognize the trigger event on the CCPx pin, TImer1 must be clocked from the instruction clock (Fosc/4) or from an external clock source.

## 25.2.3 SOFTWARE INTERRUPT MODE

When Generate Software Interrupt mode is chosen (CCPxM<3:0> = 1010), the CCPx module does not assert control of the CCPx pin (see the CCPxCON register).

## 25.2.4 AUTO-CONVERSION TRIGGER

When Auto-conversion Trigger mode is chosen (CCPxM<3:0> = 1011), the CCPx module does the following:

- Resets Timer1

- Starts an ADC conversion if ADC is enabled

The CCPx module does not assert control of the CCPx pin in this mode.

The Auto-conversion Trigger output of the CCP occurs immediately upon a match between the TMR1H, TMR1L register pair and the CCPRxH, CCPRxL register pair. The TMR1H, TMR1L register pair is not reset until the next rising edge of the Timer1 clock. The Auto-conversion Trigger output starts an ADC conversion (if the ADC module is enabled). This allows the CCPRxH, CCPRxL register pair to effectively provide a 16-bit programmable period register for Timer1.

Refer to Section 17.2.5 "Auto-Conversion Trigger" for more information.

- Note 1: The Auto-conversion Trigger from the CCP module does not set interrupt flag bit TMR1IF of the PIR1 register.

- 2: Removing the match condition by changing the contents of the CCPRxH and CCPRxL register pair, between the clock edge that generates the Auto-conversion Trigger and the clock edge that generates the Timer1 Reset, will preclude the Reset from occurring.

## 25.2.5 COMPARE DURING SLEEP

The Compare mode is dependent upon the system clock (Fosc) for proper operation. Since Fosc is shut down during Sleep mode, the Compare mode will not function properly during Sleep.

$\ensuremath{\textcircled{}^\circ}$  2011-2014 Microchip Technology Inc.

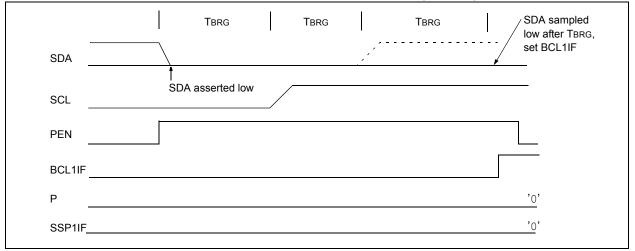

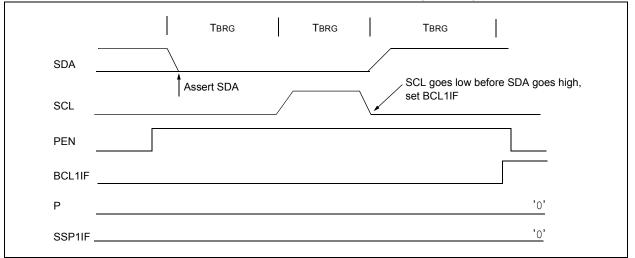

#### 26.6.13.3 Bus Collision During a Stop Condition

Bus collision occurs during a Stop condition if:

- a) After the SDA pin has been deasserted and allowed to float high, SDA is sampled low after the BRG has timed out.

- b) After the SCL pin is deasserted, SCL is sampled low before SDA goes high.

The Stop condition begins with SDA asserted low. When SDA is sampled low, the SCL pin is allowed to float. When the pin is sampled high (clock arbitration), the Baud Rate Generator is loaded with SSPADD and counts down to 0. After the BRG times out, SDA is sampled. If SDA is sampled low, a bus collision has occurred. This is due to another master attempting to drive a data '0' (Figure 26-37). If the SCL pin is sampled low before SDA is allowed to float high, a bus collision occurs. This is another case of another master attempting to drive a data '0' (Figure 26-38).

#### FIGURE 26-38: BUS COLLISION DURING A STOP CONDITION (CASE 1)

#### FIGURE 26-39: BUS COLLISION DURING A STOP CONDITION (CASE 2)

| R/W-1/1              | R/W-1/1                                                                                             | R/W-1/1              | R/W-1/1 | R/W-1/1                                               | R/W-1/1 | R/W-1/1 | R/W-1/1 |

|----------------------|-----------------------------------------------------------------------------------------------------|----------------------|---------|-------------------------------------------------------|---------|---------|---------|

|                      |                                                                                                     |                      | MSł     | <7:0>                                                 |         |         |         |

| bit 7                |                                                                                                     |                      |         |                                                       |         |         | bit 0   |

|                      |                                                                                                     |                      |         |                                                       |         |         |         |

| Legend:              |                                                                                                     |                      |         |                                                       |         |         |         |

| R = Readable bit     |                                                                                                     | W = Writable bit     |         | U = Unimplemented bit, read as '0'                    |         |         |         |

| u = Bit is unchanged |                                                                                                     | x = Bit is unknown   |         | -n/n = Value at POR and BOR/Value at all other Resets |         |         |         |

| '1' = Bit is set     |                                                                                                     | '0' = Bit is cleared |         |                                                       |         |         |         |

|                      |                                                                                                     |                      |         |                                                       |         |         |         |

| bit 7-1              | MSK<7:1>: Mask bits                                                                                 |                      |         |                                                       |         |         |         |

|                      | 1 = The received address bit n is compared to SSPADD <n> to detect I<sup>2</sup>C address match</n> |                      |         |                                                       | tch     |         |         |

|                      | 0 = The received address bit n is not used to detect I <sup>2</sup> C address match                 |                      |         |                                                       |         |         |         |

| bit 0                | MSK<0>: Mask bit for I <sup>2</sup> C Slave mode, 10-bit Address                                    |                      |         |                                                       |         |         |         |

#### REGISTER 26-5: SSPMSK: SSP MASK REGISTER

- I<sup>2</sup>C Slave mode, 10-bit address (SSPM<3:0> = 0111 or 1111): 1 = The received address bit 0 is compared to SSPADD<0> to detect  $I^2C$  address match

- 0 = The received address bit 0 is not used to detect I<sup>2</sup>C address match

- I<sup>2</sup>C Slave mode, 7-bit address, the bit is ignored

## **REGISTER 26-6:** SSPADD: MSSP ADDRESS AND BAUD RATE REGISTER (I<sup>2</sup>C MODE)

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

|         |         |         | ADD<    | <7:0>   |         |         |         |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

#### Master mode:

| bit 7-0 | ADD<7:0>: Baud Rate Clock Divider bits          |

|---------|-------------------------------------------------|

|         | SCL pin clock period = ((ADD<7:0> + 1) *4)/Fosc |

#### <u>10-Bit Slave mode — Most Significant Address Byte:</u>

- bit 7-3 Not used: Unused for Most Significant Address byte. Bit state of this register is a "don't care". Bit pattern sent by master is fixed by I<sup>2</sup>C specification and must be equal to '11110'. However, those bits are compared by hardware and are not affected by the value in this register.

- bit 2-1 ADD<2:1>: Two Most Significant bits of 10-bit address

- bit 0 Not used: Unused in this mode. Bit state is a "don't care".

#### <u>10-Bit Slave mode — Least Significant Address Byte:</u>

bit 7-0 ADD<7:0>: Eight Least Significant bits of 10-bit address

#### 7-Bit Slave mode:

| bit 7-1 | ADD<7:1>: 7-bit address |

|---------|-------------------------|

|         |                         |

bit 0 Not used: Unused in this mode. Bit state is a "don't care".

## 27.5.1.5 Synchronous Master Reception

Data is received at the RX/DT pin. The RX/DT pin output driver is automatically disabled when the EUSART is configured for synchronous master receive operation.

In Synchronous mode, reception is enabled by setting either the Single Receive Enable bit (SREN of the RCSTA register) or the Continuous Receive Enable bit (CREN of the RCSTA register).

When SREN is set and CREN is clear, only as many clock cycles are generated as there are data bits in a single character. The SREN bit is automatically cleared at the completion of one character. When CREN is set, clocks are continuously generated until CREN is cleared. If CREN is cleared in the middle of a character the CK clock stops immediately and the partial character is discarded. If SREN and CREN are both set, then SREN is cleared at the completion of the first character and CREN takes precedence.

To initiate reception, set either SREN or CREN. Data is sampled at the RX/DT pin on the trailing edge of the TX/CK clock pin and is shifted into the Receive Shift Register (RSR). When a complete character is received into the RSR, the RCIF bit is set and the character is automatically transferred to the two character receive FIFO. The Least Significant eight bits of the top character in the receive FIFO are available in RCREG. The RCIF bit remains set as long as there are unread characters in the receive FIFO.

| Note: | If the RX/DT function is on an analog pin, |

|-------|--------------------------------------------|

|       | the corresponding ANSEL bit must be        |

|       | cleared for the receiver to function.      |

## 27.5.1.6 Slave Clock

Synchronous data transfers use a separate clock line, which is synchronous with the data. A device configured as a slave receives the clock on the TX/CK line. The TX/CK pin output driver is automatically disabled when the device is configured for synchronous slave transmit or receive operation. Serial data bits change on the leading edge to ensure they are valid at the trailing edge of each clock. One data bit is transferred for each clock cycle. Only as many clock cycles should be received as there are data bits.

**Note:** If the device is configured as a slave and the TX/CK function is on an analog pin, the corresponding ANSEL bit must be cleared.

## 27.5.1.7 Receive Overrun Error

The receive FIFO buffer can hold two characters. An overrun error will be generated if a third character, in its entirety, is received before RCREG is read to access the FIFO. When this happens the OERR bit of the RCSTA register is set. Previous data in the FIFO will not be overwritten. The two characters in the FIFO buffer can be read, however, no additional characters

will be received until the error is cleared. The OERR bit can only be cleared by clearing the overrun condition. If the overrun error occurred when the SREN bit is set and CREN is clear then the error is cleared by reading RCREG. If the overrun occurred when the CREN bit is set then the error condition is cleared by either clearing the CREN bit of the RCSTA register or by clearing the SPEN bit which resets the EUSART.

#### 27.5.1.8 Receiving 9-bit Characters

The EUSART supports 9-bit character reception. When the RX9 bit of the RCSTA register is set the EUSART will shift 9-bits into the RSR for each character received. The RX9D bit of the RCSTA register is the ninth, and Most Significant, data bit of the top unread character in the receive FIFO. When reading 9-bit data from the receive FIFO buffer, the RX9D data bit must be read before reading the eight Least Significant bits from the RCREG.

## 27.5.1.9 Synchronous Master Reception Set-up:

- 1. Initialize the SPBRGH, SPBRGL register pair for the appropriate baud rate. Set or clear the BRGH and BRG16 bits, as required, to achieve the desired baud rate.

- 2. Clear the ANSEL bit for the RX pin (if applicable).

- 3. Enable the synchronous master serial port by setting bits SYNC, SPEN and CSRC.

- 4. Ensure bits CREN and SREN are clear.

- 5. If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 6. If 9-bit reception is desired, set bit RX9.

- 7. Start reception by setting the SREN bit or for continuous reception, set the CREN bit.

- 8. Interrupt flag bit RCIF will be set when reception of a character is complete. An interrupt will be generated if the enable bit RCIE was set.

- Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 10. Read the 8-bit received data by reading the RCREG register.

- 11. If an overrun error occurs, clear the error by either clearing the CREN bit of the RCSTA register or by clearing the SPEN bit which resets the EUSART.

# PIC16(L)F1782/3

| DECFSZ           | Decrement f, Skip if 0                                                                                                                                                                                                                                                                                                               |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] DECFSZ f,d                                                                                                                                                                                                                                                                                                          |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                                                                                                                                   |

| Operation:       | (f) - 1 $\rightarrow$ (destination);<br>skip if result = 0                                                                                                                                                                                                                                                                           |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                                 |

| Description:     | The contents of register 'f' are decre-<br>mented. If 'd' is '0', the result is placed<br>in the W register. If 'd' is '1', the result<br>is placed back in register 'f'.<br>If the result is '1', the next instruction is<br>executed. If the result is '0', then a<br>NOP is executed instead, making it a<br>2-cycle instruction. |

| GOTO             | Unconditional Branch                                                                                                                                                                    |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] GOTO k                                                                                                                                                                 |

| Operands:        | $0 \leq k \leq 2047$                                                                                                                                                                    |

| Operation:       | $k \rightarrow PC<10:0>$<br>PCLATH<6:3> $\rightarrow$ PC<14:11>                                                                                                                         |

| Status Affected: | None                                                                                                                                                                                    |

| Description:     | GOTO is an unconditional branch. The<br>11-bit immediate value is loaded into<br>PC bits <10:0>. The upper bits of PC<br>are loaded from PCLATH<4:3>. GOTO<br>is a 2-cycle instruction. |

| INCFSZ           | Increment f, Skip if 0                                                                                                                                                                                                                                                                                                          |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] INCFSZ f,d                                                                                                                                                                                                                                                                                                     |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                                                                                                                              |

| Operation:       | (f) + 1 $\rightarrow$ (destination),<br>skip if result = 0                                                                                                                                                                                                                                                                      |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                            |

| Description:     | The contents of register 'f' are incre-<br>mented. If 'd' is '0', the result is placed<br>in the W register. If 'd' is '1', the result<br>is placed back in register 'f'.<br>If the result is '1', the next instruction is<br>executed. If the result is '0', a NOP is<br>executed instead, making it a 2-cycle<br>instruction. |

| IORLW            | Inclusive OR literal with W                                                                                        |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] IORLW k                                                                                           |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                |  |  |  |  |

| Operation:       | (W) .OR. $k \rightarrow$ (W)                                                                                       |  |  |  |  |

| Status Affected: | Z                                                                                                                  |  |  |  |  |

| Description:     | The contents of the W register are<br>OR'ed with the 8-bit literal 'k'. The<br>result is placed in the W register. |  |  |  |  |

| INCF             | Increment f                                                                                                                                                               | IORWF            | Inclusive OR W with f                                                                                                                                                      |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] INCF f,d                                                                                                                                                 | Syntax:          | [ <i>label</i> ] IORWF f,d                                                                                                                                                 |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                        | Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                          |  |  |  |  |

| Operation:       | (f) + 1 $\rightarrow$ (destination)                                                                                                                                       | Operation:       | (W) .OR. (f) $\rightarrow$ (destination)                                                                                                                                   |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                         | Status Affected: | Z                                                                                                                                                                          |  |  |  |  |

| Description:     | The contents of register 'f' are incre-<br>mented. If 'd' is '0', the result is placed<br>in the W register. If 'd' is '1', the result<br>is placed back in register 'f'. | Description:     | Inclusive OR the W register with regis-<br>ter 'f'. If 'd' is '0', the result is placed in<br>the W register. If 'd' is '1', the result is<br>placed back in register 'f'. |  |  |  |  |

## TABLE 30-17: DIGITAL-TO-ANALOG CONVERTER (DAC) SPECIFICATIONS

| Operating Conditions: VDD = 3V, Temperature = 25°C (unless otherwise stated). |                                                   |                              |      |         |       |       |          |

|-------------------------------------------------------------------------------|---------------------------------------------------|------------------------------|------|---------|-------|-------|----------|

| Param.<br>No.                                                                 | Sym.                                              | Characteristics              | Min. | Тур.    | Max.  | Units | Comments |

| DAC01*                                                                        | CLSB                                              | Step Size                    |      | VDD/256 | _     | V     |          |

| DAC02*                                                                        | CACC                                              | Absolute Accuracy            | _    | —       | ± 1.5 | LSb   |          |

| DAC03*                                                                        | CR                                                | Unit Resistor Value (R)      | _    | 600     | _     | Ω     |          |

| DAC04*                                                                        | CST                                               | Settling Time <sup>(1)</sup> | _    | _       | 10    | μS    |          |

| *                                                                             | These parameters are characterized but not tested |                              |      |         |       |       |          |

These parameters are characterized but not tested.

Note 1: Settling time measured while DACR<7:0> transitions from '0x00' to '0xFF'.

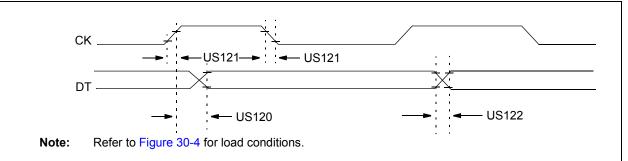

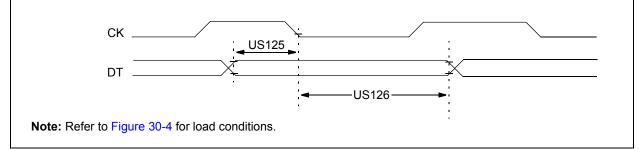

#### FIGURE 30-14: EUSART SYNCHRONOUS TRANSMISSION (MASTER/SLAVE) TIMING

#### TABLE 30-18: EUSART SYNCHRONOUS TRANSMISSION REQUIREMENTS

| Standard Operating Conditions (unless otherwise stated) |                                                    |                              |          |      |      |       |            |  |

|---------------------------------------------------------|----------------------------------------------------|------------------------------|----------|------|------|-------|------------|--|

| Param.<br>No.                                           | Symbol                                             | Characteristic               |          | Min. | Max. | Units | Conditions |  |

| US120                                                   | TCKH2DTV                                           | SYNC XMIT (Master and Slave) | 3.0-5.5V | —    | 80   | ns    |            |  |

|                                                         | Clock high to data-out valid                       | 1.8-5.5V                     | —        | 100  | ns   |       |            |  |

| US121 TCKRF                                             | Clock out rise time and fall time<br>(Master mode) | 3.0-5.5V                     | —        | 45   | ns   |       |            |  |

|                                                         |                                                    | 1.8-5.5V                     | —        | 50   | ns   |       |            |  |

| US122 TDTRF                                             | Data-out rise time and fall time                   | 3.0-5.5V                     | —        | 45   | ns   |       |            |  |

|                                                         |                                                    | 1.8-5.5V                     | _        | 50   | ns   |       |            |  |

#### FIGURE 30-15: EUSART SYNCHRONOUS RECEIVE (MASTER/SLAVE) TIMING

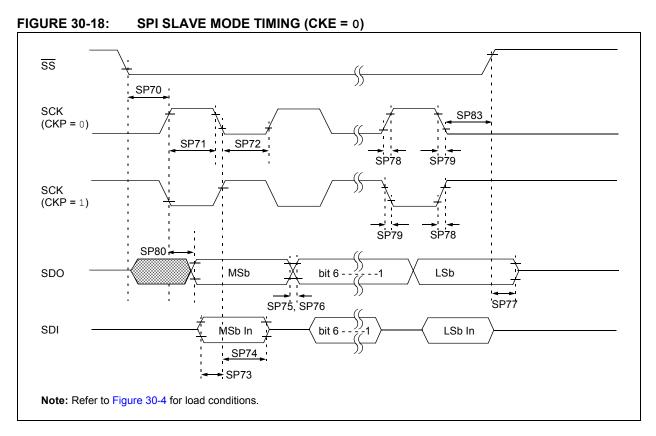

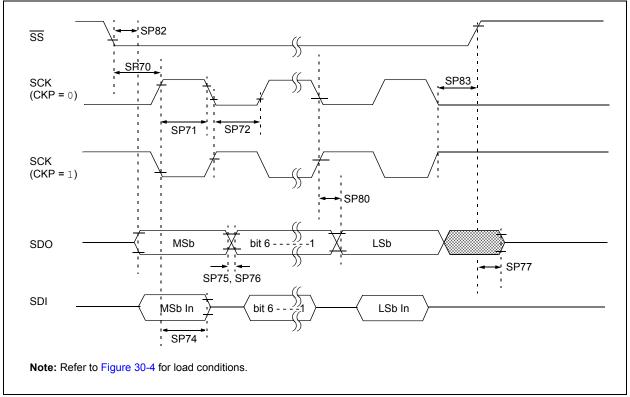

## FIGURE 30-19: SPI SLAVE MODE TIMING (CKE = 1)

# PIC16(L)F1782/3

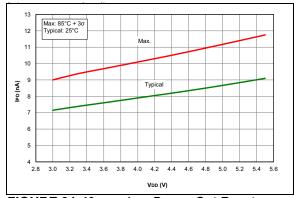

Note: Unless otherwise noted, VIN = 5V, Fosc = 300 kHz, CIN = 0.1  $\mu$ F, TA = 25°C.

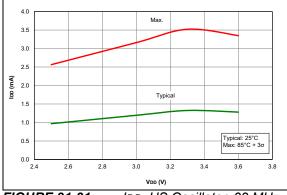

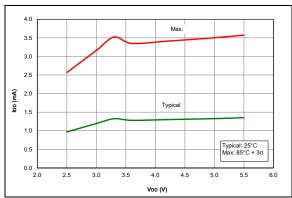

**FIGURE 31-31:** IDD, HS Oscillator, 32 MHz (8 MHz + 4x PLL), PIC16LF1782/3 Only.

**FIGURE 31-32:** IDD, HS Oscillator, 32 MHz (8 MHz + 4x PLL), PIC16F1782/3 Only.

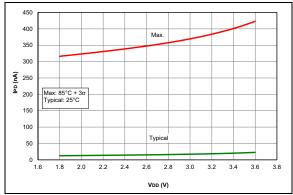

FIGURE 31-33: IPD Base, LP Sleep Mode, PIC16LF1782/3 Only.

FIGURE 31-34: IPD Base, LP Sleep Mode (VREGPM = 1), PIC16F1782/3 Only.

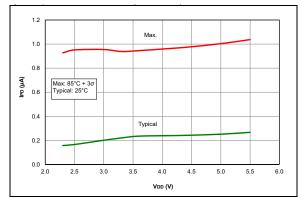

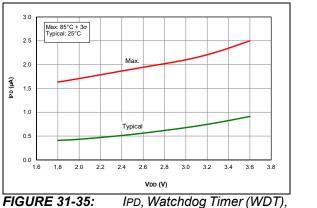

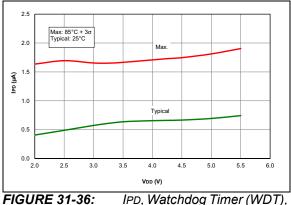

FIGURE 31-35: IPD, Watchdog Timer (WDT), PIC16LF1782/3 Only.

FIGURE 31-36: IPD, Watchdog Timer (WDT), PIC16F1782/3 Only.

# PIC16(L)F1782/3

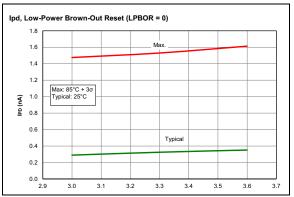

Note: Unless otherwise noted, VIN = 5V, FOSC = 300 kHz, CIN = 0.1  $\mu$ F, TA = 25°C.

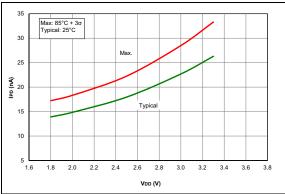

FIGURE 31-37: IPD, Fixed Voltage Reference (FVR), PIC16LF1782/3 Only.

FIGURE 31-38: IPD, Fixed Voltage Reference (FVR), PIC16F1782/3 Only.

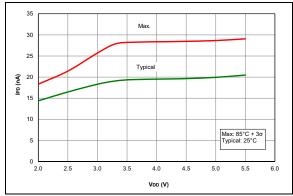

FIGURE 31-39: IPD, Brown-Out Reset (BOR), BORV = 1, PIC16LF1782/3 Only.

FIGURE 31-40: IPD, Brown-Out Reset (BOR), BORV = 1, PIC16F1782/3 Only.

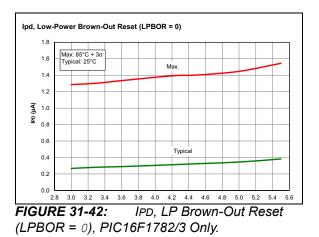

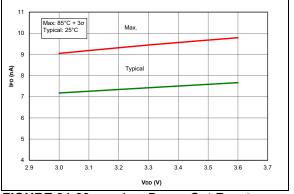

FIGURE 31-41: IPD, LP Brown-Out Reset (LPBOR = 0), PIC16LF1782/3 Only.