#### Microchip Technology - PIC16F684-E/P Datasheet

## E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | PIC                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 20MHz                                                                   |

| Connectivity               | -                                                                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                   |

| Number of I/O              | 12                                                                      |

| Program Memory Size        | 3.5KB (2K x 14)                                                         |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 256 x 8                                                                 |

| RAM Size                   | 128 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                               |

| Data Converters            | A/D 8x10b                                                               |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                      |

| Mounting Type              | Through Hole                                                            |

| Package / Case             | 14-DIP (0.300", 7.62mm)                                                 |

| Supplier Device Package    | 14-PDIP                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f684-e-p |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **PIC16F684**

#### 14-Pin Flash-Based, 8-Bit CMOS Microcontrollers with nanoWatt Technology

#### **High-Performance RISC CPU:**

- Only 35 instructions to learn:

- All single-cycle instructions except branches

- Operating speed:

- DC 20 MHz oscillator/clock input

- DC 200 ns instruction cycle

- · Interrupt capability

- 8-level deep hardware stack

- Direct, Indirect and Relative Addressing modes

#### **Special Microcontroller Features:**

- Precision Internal Oscillator:

- Factory calibrated to ±1%, typical

- Software selectable frequency range of

- 8 MHz to 125 kHz

- Software tunable

- Two-Speed Start-up mode

- Crystal fail detect for critical applications

- Clock mode switching during operation for power savings

- Software Selectable 31 kHz Internal Oscillator

- · Power-Saving Sleep mode

- Wide operating voltage range (2.0V-5.5V)

- Industrial and Extended Temperature range

- Power-on Reset (POR)

- Power-up Timer (PWRT) and Oscillator Start-up Timer (OST)

- Brown-out Reset (BOR) with software control option

- Enhanced low-current Watchdog Timer (WDT) with on-chip oscillator (software selectable nominal 268 seconds with full prescaler) with software enable

- Multiplexed Master Clear with pull-up/input pin

- Programmable code protection

- High Endurance Flash/EEPROM cell:

- 100,000 write Flash endurance

- 1,000,000 write EEPROM endurance

- Flash/Data EEPROM retention: > 40 years

#### Low-Power Features:

- Standby Current:

- 50 nA @ 2.0V, typical

- Operating Current:

- 11 μA @ 32 kHz, 2.0V, typical

- 220 µA @ 4 MHz, 2.0V, typical

- Watchdog Timer Current:

- 1 μA @ 2.0V, typical

#### **Peripheral Features:**

- 12 I/O pins with individual direction control:

- High current source/sink for direct LED drive

- Interrupt-on-change pin

- Individually programmable weak pull-ups

- Ultra Low-Power Wake-Up (ULPWU)

- Analog Comparator module with:

- Two analog comparators

- Programmable on-chip voltage reference (CVREF) module (% of VDD)

- Comparator inputs and outputs externally accessible

- A/D Converter:

- 10-bit resolution and 8 channels

- Timer0: 8-bit timer/counter with 8-bit programmable prescaler

- Enhanced Timer1:

- 16-bit timer/counter with prescaler

- External Timer1 Gate (count enable)

- Option to use OSC1 and OSC2 in LP mode as Timer1 oscillator if INTOSC mode selected

- Timer2: 8-bit timer/counter with 8-bit period register, prescaler and postscaler

- Enhanced Capture, Compare, PWM module:

- 16-bit Capture, max resolution 12.5 ns

- Compare, max resolution 200 ns

- 10-bit PWM with 1, 2 or 4 output channels, programmable "dead time", max frequency 20 kHz

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) via two pins

| Device    | Program<br>Memory | Data N          | lemory            | 1/0 | 10-bit A/D | Comparators | Timers   |

|-----------|-------------------|-----------------|-------------------|-----|------------|-------------|----------|

|           | Flash<br>(words)  | SRAM<br>(bytes) | EEPROM<br>(bytes) | 1/0 | (ch)       |             | 8/16-bit |

| PIC16F684 | 2048              | 128             | 256               | 12  | 8          | 2           | 2/1      |

#### 2.2.2.5 PIR1 Register

The PIR1 register contains the peripheral interrupt flag bits, as shown in Register 2-5.

Note: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE of the INTCON register. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

#### REGISTER 2-5: PIR1: PERIPHERAL INTERRUPT REQUEST REGISTER 1

| R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0  |

|-------|-------|--------|-------|-------|-------|--------|--------|

| EEIF  | ADIF  | CCP1IF | C2IF  | C1IF  | OSFIF | TMR2IF | TMR1IF |

| bit 7 |       |        |       |       |       |        | bit 0  |

| Legend:           |                                                     |                      |                    |  |

|-------------------|-----------------------------------------------------|----------------------|--------------------|--|

| R = Readable bit  | W = Writable bit U = Unimplemented bit, read as '0' |                      |                    |  |

| -n = Value at POR | '1' = Bit is set                                    | '0' = Bit is cleared | x = Bit is unknown |  |

| bit 7 | <b>EEIF:</b> EEPROM Write Operation Interrupt Flag bit<br>1 = The write operation completed (must be cleared in software)<br>0 = The write operation has not completed or has not been started                                                                                                                                                                          |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6 | <ul> <li>ADIF: A/D Interrupt Flag bit</li> <li>1 = A/D conversion complete</li> <li>0 = A/D conversion has not completed or has not been started</li> </ul>                                                                                                                                                                                                             |

| bit 5 | CCP1IF: CCP1 Interrupt Flag bit<br><u>Capture mod</u> e:<br>1 = A TMR1 register capture occurred (must be cleared in software)<br>0 = No TMR1 register capture occurred<br><u>Compare mode</u> :<br>1 = A TMR1 register compare match occurred (must be cleared in software)<br>0 = No TMR1 register compare match occurred<br><u>PWM mode</u> :<br>Unused in this mode |

| bit 4 | <b>C2IF:</b> Comparator 2 Interrupt Flag bit<br>1 = Comparator 2 output has changed (must be cleared in software)<br>0 = Comparator 2 output has not changed                                                                                                                                                                                                            |

| bit 3 | <b>C1IF:</b> Comparator 1 Interrupt Flag bit<br>1 = Comparator 1 output has changed (must be cleared in software)<br>0 = Comparator 1 output has not changed                                                                                                                                                                                                            |

| bit 2 | <b>OSFIF:</b> Oscillator Fail Interrupt Flag bit<br>1 = System oscillator failed, clock input has changed to INTOSC (must be cleared in software)<br>0 = System clock operating                                                                                                                                                                                         |

| bit 1 | <b>TMR2IF:</b> Timer2 to PR2 Match Interrupt Flag bit<br>1 = Timer2 to PR2 match occurred (must be cleared in software)<br>0 = Timer2 to PR2 match has not occurred                                                                                                                                                                                                     |

| bit 0 | <b>TMR1IF:</b> Timer1 Overflow Interrupt Flag bit<br>1 = Timer1 register overflowed (must be cleared in software)<br>0 = Timer1 has not overflowed                                                                                                                                                                                                                      |

#### 2.2.2.6 PCON Register

The Power Control (PCON) register (see Table 12-2) contains flag bits to differentiate between a:

- Power-on Reset (POR)

- Brown-out Reset (BOR)

- Watchdog Timer Reset (WDT)

- External MCLR Reset

The PCON register also controls the Ultra Low-Power Wake-up and software enable of the BOR.

The PCON register bits are shown in Register 2-6.

#### REGISTER 2-6: PCON: POWER CONTROL REGISTER

| U-0   | U-0 | R/W-0  | R/W-1  | U-0 | U-0 | R/W-0 | R/W-x |

|-------|-----|--------|--------|-----|-----|-------|-------|

| —     | —   | ULPWUE | SBOREN | —   | —   | POR   | BOR   |

| bit 7 |     |        |        |     |     |       | bit 0 |

| Legend:    |                   |                                                       |                                  |                                |  |  |  |  |  |

|------------|-------------------|-------------------------------------------------------|----------------------------------|--------------------------------|--|--|--|--|--|

| R = Reada  | ble bit           | W = Writable bit                                      | U = Unimplemented bit,           | read as '0'                    |  |  |  |  |  |

| -n = Value | at POR            | '1' = Bit is set                                      | '0' = Bit is cleared             | x = Bit is unknown             |  |  |  |  |  |

| bit 7-6    | Unimple           | mented: Read as '0'                                   |                                  |                                |  |  |  |  |  |

| bit 5      | •                 | E: Ultra Low-Power Wake-Up                            | Enable bit                       |                                |  |  |  |  |  |

| DIUD       |                   | •                                                     |                                  |                                |  |  |  |  |  |

|            |                   | Low-Power Wake-up enable<br>Low-Power Wake-up disable |                                  |                                |  |  |  |  |  |

| bit 4      | SBOREN            | I: Software BOR Enable bit <sup>(1</sup>              | 1)                               |                                |  |  |  |  |  |

|            | 1 = BOR           | 1 = BOR enabled                                       |                                  |                                |  |  |  |  |  |

|            | 0 = BOR           | disabled                                              |                                  |                                |  |  |  |  |  |

| bit 3-2    | Unimple           | mented: Read as '0'                                   |                                  |                                |  |  |  |  |  |

| bit 1      | POR: Po           | wer-on Reset Status bit                               |                                  |                                |  |  |  |  |  |

|            | 1 = No P          | ower-on Reset occurred                                |                                  |                                |  |  |  |  |  |

|            | 0 = A Po          | wer-on Reset occurred (mus                            | t be set in software after a Po  | wer-on Reset occurs)           |  |  |  |  |  |

| bit 0      | BOR: Br           | own-out Reset Status bit                              |                                  |                                |  |  |  |  |  |

|            | 1 = No B          | rown-out Reset occurred                               |                                  |                                |  |  |  |  |  |

|            | 0 = A Bro<br>occu |                                                       | st be set in software after a Po | wer-on Reset or Brown-out Rese |  |  |  |  |  |

**Note 1:** BOREN<1:0> = 01 in the Configuration Word register for this bit to control the  $\overline{BOR}$ .

#### 3.4.4 EXTERNAL RC MODES

The external Resistor-Capacitor (RC) modes support the use of an external RC circuit. This allows the designer maximum flexibility in frequency choice while keeping costs to a minimum when clock accuracy is not required. There are two modes: RC and RCIO.

In RC mode, the RC circuit connects to OSC1. OSC2/CLKOUT outputs the RC oscillator frequency divided by 4. This signal may be used to provide a clock for external circuitry, synchronization, calibration, test or other application requirements. Figure 3-5 shows the external RC mode connections.

Vdd PIC<sup>®</sup> MCU REXT OSC1/CLKIN Internal Clock CEXT Vss -OSC2/CLKOUT(1) Fosc/4 or < I/O<sup>(2)</sup> Recommended values:  $10 \text{ k}\Omega \leq \text{REXT} \leq 100 \text{ k}\Omega$ . <3V $3 \text{ k}\Omega \leq \text{Rext} \leq 100 \text{ k}\Omega, 3-5 \text{V}$ CEXT > 20 pF, 2-5V Note 1: Alternate pin functions are listed in Section 1.0 "Device Overview". 2: Output depends upon RC or RCIO Clock mode.

FIGURE 3-5: EXTERNAL RC MODES

In RCIO mode, the RC circuit is connected to OSC1. OSC2 becomes an additional general purpose I/O pin.

The RC oscillator frequency is a function of the supply voltage, the resistor (REXT) and capacitor (CEXT) values and the operating temperature. Other factors affecting the oscillator frequency are:

- threshold voltage variation

- component tolerances

- packaging variations in capacitance

The user also needs to take into account variation due to tolerance of external RC components used.

#### 3.5 Internal Clock Modes

The Oscillator module has two independent, internal oscillators that can be configured or selected as the system clock source.

- 1. The **HFINTOSC** (High-Frequency Internal Oscillator) is factory calibrated and operates at 8 MHz. The frequency of the HFINTOSC can be user-adjusted via software using the OSCTUNE register (Register 3-2).

- 2. The **LFINTOSC** (Low-Frequency Internal Oscillator) is uncalibrated and operates at 31 kHz.

The system clock speed can be selected via software using the Internal Oscillator Frequency Select bits IRCF<2:0> of the OSCCON register.

The system clock can be selected between external or internal clock sources via the System Clock Selection (SCS) bit of the OSCCON register. See **Section 3.6 "Clock Switching"** for more information.

#### 3.5.1 INTOSC AND INTOSCIO MODES

The INTOSC and INTOSCIO modes configure the internal oscillators as the system clock source when the device is programmed using the oscillator selection or the FOSC<2:0> bits in the Configuration Word register (CONFIG).

In **INTOSC** mode, OSC1/CLKIN is available for general purpose I/O. OSC2/CLKOUT outputs the selected internal oscillator frequency divided by 4. The CLKOUT signal may be used to provide a clock for external circuitry, synchronization, calibration, test or other application requirements.

In **INTOSCIO** mode, OSC1/CLKIN and OSC2/CLKOUT are available for general purpose I/O.

#### 3.5.2 HFINTOSC

The High-Frequency Internal Oscillator (HFINTOSC) is a factory calibrated 8 MHz internal clock source. The frequency of the HFINTOSC can be altered via software using the OSCTUNE register (Register 3-2).

The output of the HFINTOSC connects to a postscaler and multiplexer (see Figure 3-1). One of seven frequencies can be selected via software using the IRCF<2:0> bits of the OSCCON register. See **Section 3.5.4 "Frequency Select Bits (IRCF)**" for more information.

The HFINTOSC is enabled by selecting any frequency between 8 MHz and 125 kHz by setting the IRCF<2:0> bits of the OSCCON register  $\neq$  000. Then, set the System Clock Source (SCS) bit of the OSCCON register to '1' or enable Two-Speed Start-up by setting the IESO bit in the Configuration Word register (CONFIG) to '1'.

The HF Internal Oscillator (HTS) bit of the OSCCON register indicates whether the HFINTOSC is stable or not.

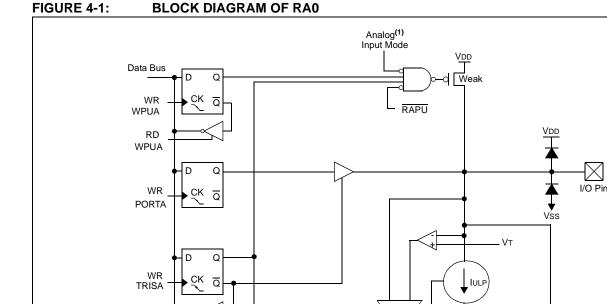

### 4.2.5 PIN DESCRIPTIONS AND DIAGRAMS

Each PORTA pin is multiplexed with other functions. The pins and their combined functions are briefly described here. For specific information about individual functions such as the Comparator or the ADC, refer to the appropriate section in this data sheet.

#### 4.2.5.1 RA0/AN0/C1IN+/ICSPDAT/ULPWU

Figure 4-1 shows the diagram for this pin. The RA0 pin is configurable to function as one of the following:

- a general purpose I/O

- an analog input for the ADC

- an analog non-inverting input to the comparator

RD

RD PORTA

WR

IOCA

RD IOCA

Interrupt-on-Change Q

Q

TRISA

- In-Circuit Serial Programming data

- an analog input for the Ultra Low-Power Wake-Up

Analog(1)

Input Mode

Q

Ω

**RD PORTA**

To Comparator To A/D Converter

Note 1: Comparator mode and ANSEL determines Analog Input mode.

Ч

Q3

D

D

ΕN

ΕN

#### 4.2.5.2 RA1/AN1/C1IN-/VREF/ICSPCLK

Figure 4-2 shows the diagram for this pin. The RA1 pin is configurable to function as one of the following:

- a general purpose I/O

- an analog input for the ADC

- an analog inverting input to the comparator

- a voltage reference input for the ADC

- In-Circuit Serial Programming clock

Vss

ULPWUE

#### REGISTER 6-1: T1CON: TIMER 1 CONTROL REGISTER (CONTINUED)

| bit 2 | T1SYNC: Timer1 External Clock Input Synchronization Control bit                                              |

|-------|--------------------------------------------------------------------------------------------------------------|

|       | <u>TMR1CS = 1:</u>                                                                                           |

|       | 1 = Do not synchronize external clock input                                                                  |

|       | 0 = Synchronize external clock input                                                                         |

|       | <u>TMR1CS = 0:</u>                                                                                           |

|       | This bit is ignored. Timer1 uses the internal clock                                                          |

| bit 1 | TMR1CS: Timer1 Clock Source Select bit                                                                       |

|       | <ul><li>1 = External clock from T1CKI pin (on the rising edge)</li><li>0 = Internal clock (Fosc/4)</li></ul> |

| bit 0 | TMR1ON: Timer1 On bit                                                                                        |

|       | 1 = Enables Timer1                                                                                           |

|       | 0 = Stops Timer1                                                                                             |

**Note 1:** T1GINV bit inverts the Timer1 gate logic, regardless of source.

2: TMR1GE bit must be set to use either T1G pin or C2OUT, as selected by the T1GSS bit of the CMCON1 register, as a Timer1 gate source.

| Name   | Bit 7                                                                         | Bit 6  | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|-------------------------------------------------------------------------------|--------|---------|---------|---------|--------|--------|--------|-----------------------|---------------------------------|

| CMCON1 | _                                                                             | -      | _       | —       | -       | —      | T1GSS  | C2SYNC | 10                    | 10                              |

| INTCON | GIE                                                                           | PEIE   | TOIE    | INTE    | RAIE    | T0IF   | INTF   | RAIF   | 0000 0000             | 0000 0000                       |

| PIE1   | EEIE                                                                          | ADIE   | CCP1IE  | C2IE    | C1IE    | OSFIE  | TMR2IE | TMR1IE | 0000 0000             | 0000 0000                       |

| PIR1   | EEIF                                                                          | ADIF   | CCP1IF  | C2IF    | C1IF    | OSFIF  | TMR2IF | TMR1IF | 0000 0000             | 0000 0000                       |

| TMR1H  | Holding Register for the Most Significant Byte of the 16-bit TMR1 Register    |        |         |         |         |        |        |        |                       | uuuu uuuu                       |

| TMR1L  | L Holding Register for the Least Significant Byte of the 16-bit TMR1 Register |        |         |         |         |        |        |        | xxxx xxxx             | uuuu uuuu                       |

| T1CON  | T1GINV                                                                        | TMR1GE | T1CKPS1 | T1CKPS0 | T1OSCEN | T1SYNC | TMR1CS | TMR1ON | 0000 0000             | uuuu uuuu                       |

TABLE 6-1: SUMMARY OF REGISTERS ASSOCIATED WITH TIMER1

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Timer1 module.

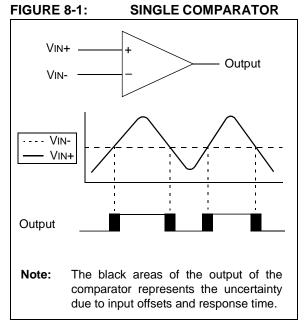

#### 8.0 COMPARATOR MODULE

Comparators are used to interface analog circuits to a digital circuit by comparing two analog voltages and providing a digital indication of their relative magnitudes. The comparators are very useful mixed signal building blocks because they provide analog functionality independent of the device program execution. The analog Comparator module includes the following features:

- Dual comparators

- Multiple comparator configurations

- Comparator outputs are available internally/ externally

- Programmable output polarity

- Interrupt-on-change

- · Wake-up from Sleep

- Timer1 gate (count enable)

- Output synchronization to Timer1 clock input

- Programmable voltage reference

| Note: | Only Comparator C2 can be linked to |

|-------|-------------------------------------|

|       | Timer1.                             |

#### 8.1 Comparator Overview

A comparator is shown in Figure 8-1 along with the relationship between the analog input levels and the digital output. When the analog voltage at VIN+ is less than the analog voltage at VIN-, the output of the comparator is a digital low level. When the analog voltage at VIN+ is greater than the analog voltage at VIN-, the output of the comparator is a digital high level.

This device contains two comparators as shown in Figure 8-2 and Figure 8-3. The comparators are not independently configurable.

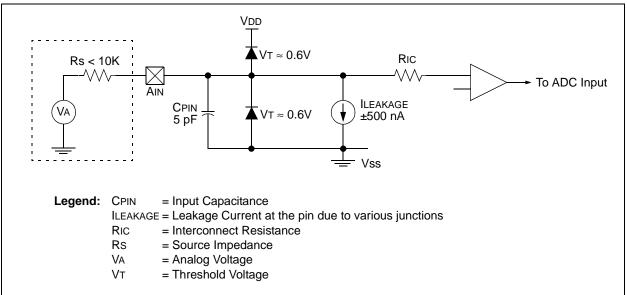

#### 8.1.1 ANALOG INPUT CONNECTION CONSIDERATIONS

A simplified circuit for an analog input is shown in Figure 8-4. Since the analog input pins share their connection with a digital input, they have reverse biased ESD protection diodes to VDD and VSS. The analog input, therefore, must be between VSS and VDD. If the input voltage deviates from this range by more than 0.6V in either direction, one of the diodes is forward biased and a latch-up may occur.

A maximum source impedance of  $10 \text{ k}\Omega$  is recommended for the analog sources. Also, any external component connected to an analog input pin, such as a capacitor or a Zener diode, should have very little leakage current to minimize inaccuracies introduced.

- Note 1: When reading a PORT register, all pins configured as analog inputs will read as a '0'. Pins configured as digital inputs will convert as an analog input, according to the input specification.

- 2: Analog levels on any pin defined as a digital input, may cause the input buffer to consume more current than is specified.

#### FIGURE 8-4: ANALOG INPUT MODEL

#### 9.2.7 ADC REGISTER DEFINITIONS

The following registers are used to control the operation of the ADC.

#### REGISTER 9-1: ADCON0: A/D CONTROL REGISTER 0

| R/W-0           | R/W-0                                                                                                                                                                                                                                                     | U-0              | R/W-0           | R/W-0             | R/W-0             | R/W-0             | R/W-0 |  |  |  |  |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------|-------------------|-------------------|-------------------|-------|--|--|--|--|

| ADFM            | VCFG                                                                                                                                                                                                                                                      | —                | CHS2            | CHS1              | CHS0              | GO/DONE           | ADON  |  |  |  |  |

| bit 7           |                                                                                                                                                                                                                                                           |                  |                 |                   |                   |                   | bit ( |  |  |  |  |

|                 |                                                                                                                                                                                                                                                           |                  |                 |                   |                   |                   |       |  |  |  |  |

| Legend:         |                                                                                                                                                                                                                                                           |                  |                 |                   |                   |                   |       |  |  |  |  |

| R = Readable    | bit                                                                                                                                                                                                                                                       | W = Writable bi  | t               | U = Unimplem      | ented bit, read a | as '0'            |       |  |  |  |  |

| -n = Value at F | POR                                                                                                                                                                                                                                                       | '1' = Bit is set |                 | '0' = Bit is clea | red               | x = Bit is unknow | wn    |  |  |  |  |

| bit 7           | <b>ADFM:</b> A/D Cc<br>1 = Right justifi<br>0 = Left justifie                                                                                                                                                                                             |                  | Format Select b | bit               |                   |                   |       |  |  |  |  |

| bit 6           | VCFG: Voltage<br>1 = VREF pin<br>0 = VDD                                                                                                                                                                                                                  | e Reference bit  |                 |                   |                   |                   |       |  |  |  |  |

| bit 5           | Unimplemente                                                                                                                                                                                                                                              | ed: Read as '0'  |                 |                   |                   |                   |       |  |  |  |  |

| bit 4-2         | CHS<2:0>: Analog Channel Select bits                                                                                                                                                                                                                      |                  |                 |                   |                   |                   |       |  |  |  |  |

|                 | 000 = ANO                                                                                                                                                                                                                                                 |                  |                 |                   |                   |                   |       |  |  |  |  |

|                 | 001 = AN1                                                                                                                                                                                                                                                 |                  |                 |                   |                   |                   |       |  |  |  |  |

|                 | 010 = AN2                                                                                                                                                                                                                                                 |                  |                 |                   |                   |                   |       |  |  |  |  |

|                 | 011 = AN3                                                                                                                                                                                                                                                 |                  |                 |                   |                   |                   |       |  |  |  |  |

|                 | 100 = AN4<br>101 = AN5                                                                                                                                                                                                                                    |                  |                 |                   |                   |                   |       |  |  |  |  |

|                 | 101 = ANS<br>110 = AN6                                                                                                                                                                                                                                    |                  |                 |                   |                   |                   |       |  |  |  |  |

|                 | 110 = ANO<br>111 = AN7                                                                                                                                                                                                                                    |                  |                 |                   |                   |                   |       |  |  |  |  |

| bit 1           |                                                                                                                                                                                                                                                           | Conversion Sta   | tus bit         |                   |                   |                   |       |  |  |  |  |

|                 | <ul> <li>1 = A/D conversion cycle in progress. Setting this bit starts an A/D conversion cycle.<br/>This bit is automatically cleared by hardware when the A/D conversion has completed.</li> <li>0 = A/D conversion completed/not in progress</li> </ul> |                  |                 |                   |                   |                   |       |  |  |  |  |

| bit 0           | ADON: ADC E<br>1 = ADC is ena                                                                                                                                                                                                                             | nable bit        |                 | ng current        |                   |                   |       |  |  |  |  |

#### REGISTER 9-2: ADCON1: A/D CONTROL REGISTER 1

| U-0   | R/W-0 | R/W-0 | R/W-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-------|-------|-------|-----|-----|-----|-------|

| —     | ADCS2 | ADCS1 | ADCS0 | —   | —   | —   | —     |

| bit 7 |       |       |       |     |     |     | bit 0 |

| Legend:      |                  |                                  |                                     |                    |  |  |  |

|--------------|------------------|----------------------------------|-------------------------------------|--------------------|--|--|--|

| R = Readab   | le bit           | W = Writable bit                 | U = Unimplemented bit, read as '0'  |                    |  |  |  |

| -n = Value a | t POR            | '1' = Bit is set                 | '0' = Bit is cleared                | x = Bit is unknown |  |  |  |

| bit 7        | Unimple          | mented: Read as '0'              |                                     |                    |  |  |  |

| bit 6-4      | ADCS<2           | :0>: A/D Conversion Clock Sele   | ct bits                             |                    |  |  |  |

|              | 000 = FC         | osc/2                            |                                     |                    |  |  |  |

|              | 001 = FC         | osc/8                            |                                     |                    |  |  |  |

|              | 010 = FC         | osc/32                           |                                     |                    |  |  |  |

|              | x11 = FR         | c (clock derived from a dedicate | ed internal oscillator = 500 kHz ma | ax)                |  |  |  |

|              | 100 = FC         | osc/4                            |                                     |                    |  |  |  |

|              | 101 <b>= F</b> C | osc/16                           |                                     |                    |  |  |  |

|              | 110 = FC         | osc/64                           |                                     |                    |  |  |  |

| bit 3-0      | Unimple          | mented: Read as '0'              |                                     |                    |  |  |  |

#### 10.5 Protection Against Spurious Write

There are conditions when the user may not want to write to the data EEPROM memory. To protect against spurious EEPROM writes, various mechanisms have been built in. On power-up, WREN is cleared. Also, the Power-up Timer (64 ms duration) prevents EEPROM write.

The write initiate sequence and the WREN bit together help prevent an accidental write during:

- Brown-out

- Power Glitch

- Software Malfunction

#### 10.6 Data EEPROM Operation During Code-Protect

Data memory can be code-protected by programming the  $\overline{CPD}$  bit in the Configuration Word register (Register 12-1) to '0'.

When the data memory is code-protected, the CPU is able to read and write data to the data EEPROM. It is recommended to code-protect the program memory when code-protecting data memory. This prevents anyone from programming zeroes over the existing code (which will execute as NOPS) to reach an added routine, programmed in unused program memory, which outputs the contents of data memory. Programming unused locations in program memory to '0' will also help prevent data memory code protection from becoming breached.

| Name                  | Bit 7  | Bit 6      | Bit 5    | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR, BOR | Value on<br>all other<br>Resets |

|-----------------------|--------|------------|----------|--------|--------|--------|--------|--------|-----------------------|---------------------------------|

| INTCON                | GIE    | PEIE       | T0IE     | INTE   | RAIE   | T0IF   | INTF   | RAIF   | 0000 0000             | 0000 0000                       |

| PIR1                  | EEIF   | ADIF       | CCP1IF   | C2IF   | C1IF   | OSFIF  | TMR2IF | TMR1IF | 0000 0000             | 0000 0000                       |

| PIE1                  | EEIE   | ADIE       | CCP1IE   | C2IE   | C1IE   | OSFIE  | TMR2IE | TMR1IE | 0000 0000             | 0000 0000                       |

| EEDAT                 | EEDAT7 | EEDAT6     | EEDAT5   | EEDAT4 | EEDAT3 | EEDAT2 | EEDAT1 | EEDAT0 | 0000 0000             | 0000 0000                       |

| EEADR                 | EEADR7 | EEADR6     | EEADR5   | EEADR4 | EEADR3 | EEADR2 | EEADR1 | EEADR0 | 0000 0000             | 0000 0000                       |

| EECON1                | _      | _          | _        | _      | WRERR  | WREN   | WR     | RD     | x000                  | q000                            |

| EECON2 <sup>(1)</sup> | EEPROM | Control Re | gister 2 |        |        |        |        |        |                       |                                 |

#### TABLE 10-1: SUMMARY OF ASSOCIATED DATA EEPROM REGISTERS

Legend: x = unknown, u = unchanged, - = unimplemented read as '0', q = value depends upon condition. Shaded cells are not used by the Data EEPROM module.

Note 1: EECON2 is not a physical register.

#### 11.3.1 PWM PERIOD

The PWM period is specified by the PR2 register of Timer2. The PWM period can be calculated using the formula of Equation 11-1.

#### EQUATION 11-1: PWM PERIOD

$PWM Period = [(PR2) + 1] \bullet 4 \bullet Tosc \bullet$ (TMR2 Prescale Value)

When TMR2 is equal to PR2, the following three events occur on the next increment cycle:

- TMR2 is cleared

- The CCP1 pin is set. (Exception: If the PWM duty cycle = 0%, the pin will not be set.)

- The PWM duty cycle is latched from CCPR1L into CCPR1H.

| Note: | The Timer2 postscaler (see Section 7.1 |  |  |  |  |

|-------|----------------------------------------|--|--|--|--|

|       | "Timer2 Operation") is not used in the |  |  |  |  |

|       | determination of the PWM frequency.    |  |  |  |  |

#### 11.3.2 PWM DUTY CYCLE

The PWM duty cycle is specified by writing a 10-bit value to multiple registers: CCPR1L register and CCP1<1:0> bits of the CCP1CON register. The CCPR1L contains the eight MSbs and the CCP1<1:0> bits of the CCP1CON register contain the two LSbs. CCPR1L and CCP1<1:0> bits of the CCP1CON register contain the two LSbs. CCPR1L and CCP1<1:0> bits of the CCP1CON register can be written to at any time. The duty cycle value is not latched into CCPR1H until after the period completes (i.e., a match between PR2 and TMR2 registers occurs). While using the PWM, the CCPR1H register is read-only.

Equation 11-2 is used to calculate the PWM pulse width.

Equation 11-3 is used to calculate the PWM duty cycle ratio.

#### EQUATION 11-2: PULSE WIDTH

$Pulse Width = (CCPR1L:CCP1CON < 5:4>) \bullet$

TOSC • (TMR2 Prescale Value)

#### EQUATION 11-3: DUTY CYCLE RATIO

$$Duty Cycle Ratio = \frac{(CCPR1L:CCP1CON < 5:4>)}{4(PR2 + 1)}$$

The CCPR1H register and a 2-bit internal latch are used to double buffer the PWM duty cycle. This double buffering is essential for glitchless PWM operation.

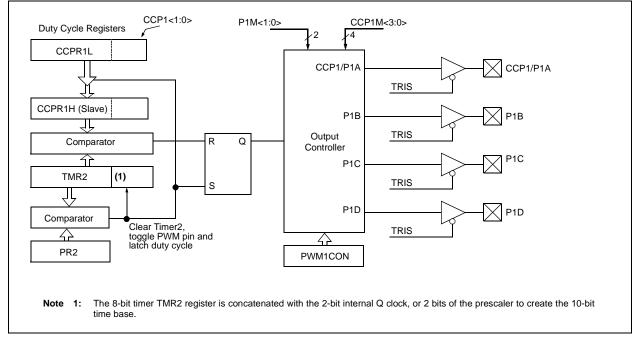

The 8-bit timer TMR2 register is concatenated with either the 2-bit internal system clock (Fosc), or 2 bits of the prescaler, to create the 10-bit time base. The system clock is used if the Timer2 prescaler is set to 1:1.

When the 10-bit time base matches the CCPR1H and 2-bit latch, then the CCP1 pin is cleared (see Figure 11-3).

#### 11.3.3 PWM RESOLUTION

The resolution determines the number of available duty cycles for a given period. For example, a 10-bit resolution will result in 1024 discrete duty cycles, whereas an 8-bit resolution will result in 256 discrete duty cycles.

The maximum PWM resolution is 10 bits when PR2 is 255. The resolution is a function of the PR2 register value as shown by Equation 11-4.

#### EQUATION 11-4: PWM RESOLUTION

Resolution =

$$\frac{\log[4(PR2 + 1)]}{\log(2)}$$

bits

Note: If the pulse width value is greater than the period the assigned PWM pin(s) will remain unchanged.

#### TABLE 11-2: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 20 MHz)

| PWM Frequency             | 1.22 kHz | 4.88 kHz | 19.53 kHz | 78.12 kHz | 156.3 kHz | 208.3 kHz |

|---------------------------|----------|----------|-----------|-----------|-----------|-----------|

| Timer Prescale (1, 4, 16) | 16       | 4        | 1         | 1         | 1         | 1         |

| PR2 Value                 | 0xFF     | 0xFF     | 0xFF      | 0x3F      | 0x1F      | 0x17      |

| Maximum Resolution (bits) | 10       | 10       | 10        | 8         | 7         | 6.6       |

#### TABLE 11-3: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 8 MHz)

| PWM Frequency             | 1.22 kHz | 4.90 kHz | 19.61 kHz | 76.92 kHz | 153.85 kHz | 200.0 kHz |

|---------------------------|----------|----------|-----------|-----------|------------|-----------|

| Timer Prescale (1, 4, 16) | 16       | 4        | 1         | 1         | 1          | 1         |

| PR2 Value                 | 0x65     | 0x65     | 0x65      | 0x19      | 0x0C       | 0x09      |

| Maximum Resolution (bits) | 8        | 8        | 8         | 6         | 5          | 5         |

#### 11.4 PWM (Enhanced Mode)

The Enhanced PWM Mode can generate a PWM signal on up to four different output pins with up to 10-bits of resolution. It can do this through four different PWM output modes:

- Single PWM

- Half-Bridge PWM

- Full-Bridge PWM, Forward mode

- Full-Bridge PWM, Reverse mode

To select an Enhanced PWM mode, the P1M bits of the CCP1CON register must be set appropriately.

The PWM outputs are multiplexed with I/O pins and are designated P1A, P1B, P1C and P1D. The polarity of the PWM pins is configurable and is selected by setting the CCP1M bits in the CCP1CON register appropriately.

Table 11-4 shows the pin assignments for each Enhanced PWM mode.

Figure 11-5 shows an example of a simplified block diagram of the Enhanced PWM module.

Note: To prevent the generation of an incomplete waveform when the PWM is first enabled, the ECCP module waits until the start of a new PWM period before generating a PWM signal.

#### FIGURE 11-5: EXAMPLE SIMPLIFIED BLOCK DIAGRAM OF THE ENHANCED PWM MODE

Note 1: The TRIS register value for each PWM output must be configured appropriately.

- 2: Clearing the CCP1CON register will relinquish ECCP control of all PWM output pins.

- 3: Any pin not used by an Enhanced PWM mode is available for alternate pin functions

#### TABLE 11-4: EXAMPLE PIN ASSIGNMENTS FOR VARIOUS PWM ENHANCED MODES

| ECCP Mode            | P1M | CCP1/P1A | P1B | P1C | P1D |

|----------------------|-----|----------|-----|-----|-----|

| Single               | 00  | Yes      | No  | No  | No  |

| Half-Bridge          | 10  | Yes      | Yes | No  | No  |

| Full-Bridge, Forward | 01  | Yes      | Yes | Yes | Yes |

| Full-Bridge, Reverse | 11  | Yes      | Yes | Yes | Yes |

#### 12.2 Calibration Bits

Brown-out Reset (BOR), Power-on Reset (POR) and 8 MHz internal oscillator (HFINTOSC) are factory calibrated. These calibration values are stored in fuses located in the Calibration Word (2009h). The Calibration Word is not erased when using the specified bulk erase sequence in the "*PIC12F6XX/16F6XX Memory Programming Specification*" (DS41244) and thus, does not require reprogramming.

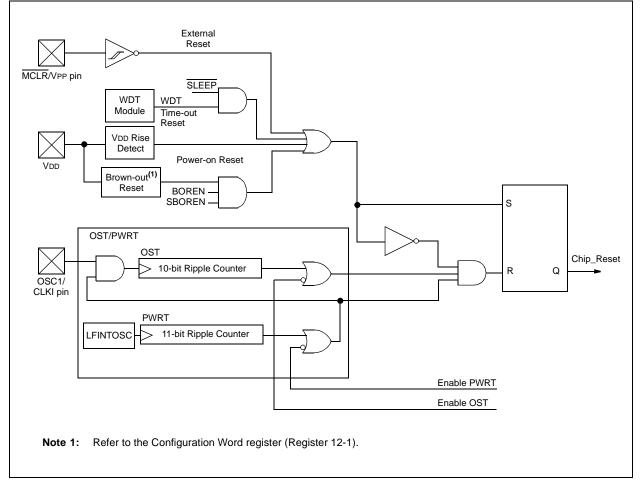

#### 12.3 Reset

The PIC16F684 differentiates between various kinds of Reset:

- a) Power-on Reset (POR)

- b) WDT Reset during normal operation

- c) WDT Reset during Sleep

- d) MCLR Reset during normal operation

- e) MCLR Reset during Sleep

- f) Brown-out Reset (BOR)

Some registers are not affected in any Reset condition; their status is unknown on POR and unchanged in any other Reset. Most other registers are reset to a "Reset state" on:

- Power-on Reset

- MCLR Reset

- MCLR Reset during Sleep

- WDT Reset

- Brown-out Reset (BOR)

WDT wake-up does not cause register resets in the same manner as a WDT Reset since wake-up is viewed as the resumption of normal operation. TO and PD bits are set or cleared differently in different Reset situations, as indicated in Table 12-2. Software can use these bits to determine the nature of the Reset. See Table 12-4 for a full description of Reset states of all registers.

A simplified block diagram of the On-Chip Reset Circuit is shown in Figure 12-1.

The MCLR Reset path has a noise filter to detect and ignore small pulses. See **Section 15.0** "**Electrical Specifications**" for pulse-width specifications.

#### FIGURE 12-1: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

| FIGURE 12-10: | WAKE-UP FROM SLEEP THROUGH INTERRUPT |

|---------------|--------------------------------------|

|               |                                      |

|                             | Q1 Q2 Q3 Q4       | Q1   Q2   Q3   Q4 | Q1                                              | Q1 Q2 Q3 Q4        | Q1 Q2 Q3 Q4    | Q1 Q2 Q3 Q4            | Q1 Q2 Q3 Q4 |

|-----------------------------|-------------------|-------------------|-------------------------------------------------|--------------------|----------------|------------------------|-------------|

| OSC1                        |                   |                   |                                                 |                    | ·~~~·/         |                        |             |

| CLKOUT <sup>(4)</sup>       | \/                |                   | Tost <sup>(2)</sup>                             |                    | ↓/             |                        |             |

| INT pin                     | ı ı               |                   |                                                 | I<br>I             | i i<br>I I     | 1                      | 1<br>1      |

| INTF flag                   |                   |                   | <u>ل ل الم الم الم الم الم الم الم الم الم </u> | I<br>              | (3)            |                        |             |

| (INTCON reg.)               |                   |                   | · · · · · · · · · · · · · · · · · · ·           | Interrupt Laten    | Cy(°)          |                        | 1           |

| GIE bit<br>(INTCON reg.)    |                   |                   | Processor in                                    | <u> </u><br>       | · · ·          | 1                      | <u>'</u>    |

| (                           | ' !               |                   | Sleep                                           |                    | !              | '.                     | !_          |

| Instruction Flow            |                   |                   |                                                 |                    |                |                        |             |

| PC )                        | (PC)              | PC + 1            | PC + 2                                          | X PC + 2           | X PC + 2 X     | <u>    0004h     X</u> | 0005h       |

| Instruction {<br>Fetched    | Inst(PC) = Sleep  | Inst(PC + 1)      | 1<br>1<br>1                                     | Inst(PC + 2)       |                | Inst(0004h)            | Inst(0005h) |

| Instruction {<br>Executed { | Inst(PC – 1)      | Sleep             | 1<br>1<br>1                                     | Inst(PC + 1)       | Dummy Cycle    | Dummy Cycle            | Inst(0004h) |

| Noto 1:                     |                   | llator modo assur | nod                                             |                    |                |                        |             |

|                             | ,                 |                   |                                                 | not apply to EC. I |                | scillator modes        |             |

| Note 1:                     | XT, HS or LP Osci |                   | ned.<br>cale). This delay does                  | not apply to EC, I | NTOSC and RC O | scillator modes.       |             |

- 3: GIE = '1' assumed. In this case after wake-up, the processor jumps to 0004h. If GIE = '0', execution will continue in-line.

- 4: CLKOUT is not available in XT, HS, LP or EC Oscillator modes, but shown here for timing reference.

#### 12.8 Code Protection

If the code protection bit(s) have not been programmed, the on-chip program memory can be read out using  $ICSP^{TM}$  for verification purposes.

| Note: |                                        |

|-------|----------------------------------------|

|       | gram memory will be erased when the    |

|       | code protection is turned off. See the |

|       | "PIC12F6XX/16F6XX Memory               |

|       | Programming Specification" (DS41204)   |

|       | for more information.                  |

#### 12.9 ID Locations

Four memory locations (2000h-2003h) are designated as ID locations where the user can store checksum or other code identification numbers. These locations are not accessible during normal execution but are readable and writable during Program/Verify mode. Only the Least Significant 7 bits of the ID locations are used.

| RETFIE           | Return from Interrupt                                                                                                                                            | RETLW            | Return with literal in W                                                                                                                                                            |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] RETFIE                                                                                                                                                   | Syntax:          | [ <i>label</i> ] RETLW k                                                                                                                                                            |

| Operands:        | None                                                                                                                                                             | Operands:        | $0 \le k \le 255$                                                                                                                                                                   |

| Operation:       | $\begin{array}{l} TOS \to PC, \\ \mathtt{1} \to GIE \end{array}$                                                                                                 | Operation:       | $\begin{array}{l} k \rightarrow (W);\\ TOS \rightarrow PC \end{array}$                                                                                                              |

| Status Affected: | None                                                                                                                                                             | Status Affected: | None                                                                                                                                                                                |

| Description:     | Return from Interrupt. Stack is<br>POPed and Top-of-Stack (TOS) is<br>loaded in the PC. Interrupts are<br>enabled by setting Global<br>Interrupt Enable bit, GIE | Description:     | The W register is loaded with the<br>eight bit literal 'k'. The program<br>counter is loaded from the top of<br>the stack (the return address).<br>This is a two-cycle instruction. |

|                  | (INTCON<7>). This is a two-cycle<br>instruction.                                                                                                                 | Words:           | 1                                                                                                                                                                                   |

| Words:           | 1                                                                                                                                                                | Cycles:          | 2                                                                                                                                                                                   |

| Cycles:          | 2                                                                                                                                                                | Example:         | CALL TABLE;W contains<br>table<br>;offset value                                                                                                                                     |

| <u>Example:</u>  | RETFIE<br>After Interrupt<br>PC = TOS<br>GIE = 1                                                                                                                 | TABLE            | <pre>&gt;;Winset value<br/>;Winow has table value<br/>ADDWF PC ;W = offset<br/>RETLW k1 ;Begin table<br/>RETLW k2 ;</pre>                                                           |

| RETURN           | Return from Subroutine                                                                                                                                     |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] RETURN                                                                                                                                           |

| Operands:        | None                                                                                                                                                       |

| Operation:       | $TOS\toPC$                                                                                                                                                 |

| Status Affected: | None                                                                                                                                                       |

| Description:     | Return from subroutine. The stack<br>is POPed and the top of the stack<br>(TOS) is loaded into the program<br>counter. This is a two-cycle<br>instruction. |

•

RETLW kn ; End of table

W = 0x07

W = value of k8

Before Instruction

After Instruction

#### **15.0 ELECTRICAL SPECIFICATIONS**

#### Absolute Maximum Ratings<sup>(†)</sup>

| Ambient temperature under bias                                                                                   | 40° to +125°C                         |

|------------------------------------------------------------------------------------------------------------------|---------------------------------------|

| Storage temperature                                                                                              | 65°C to +150°C                        |

| Voltage on VDD with respect to Vss                                                                               | 0.3V to +6.5V                         |

| Voltage on MCLR with respect to Vss                                                                              | 0.3V to +13.5V                        |

| Voltage on all other pins with respect to Vss                                                                    | 0.3V to (VDD + 0.3V)                  |

| Total power dissipation <sup>(1)</sup>                                                                           | 800 mW                                |

| Maximum current out of Vss pin                                                                                   | 95 mA                                 |

| Maximum current into VDD pin                                                                                     | 95 mA                                 |

| Input clamp current, Iικ (Vι < 0 or Vι > VDD)                                                                    | ± 20 mA                               |

| Output clamp current, loк (Vo < 0 or Vo >VDD)                                                                    | ± 20 mA                               |

| Maximum output current sunk by any I/O pin                                                                       | 25 mA                                 |

| Maximum output current sourced by any I/O pin                                                                    | 25 mA                                 |

| Maximum current sunk by PORTA and PORTC (combined)                                                               | 90 mA                                 |

| Maximum current sourced PORTA and PORTC (combined)                                                               | 90 mA                                 |

| <b>Note 1:</b> Power dissipation is calculated as follows: PDIS = VDD x {IDD $-\sum$ IOH} + $\sum$ {(VDD $-\sum$ | – VOH) x IOH} + $\Sigma$ (VOI x IOL). |

† NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure above maximum rating conditions for extended periods may affect device reliability.

#### 15.6 Thermal Considerations

| Param<br>No. | Sym       | Characteristic                         | Тур   | Units | Conditions                                               |  |

|--------------|-----------|----------------------------------------|-------|-------|----------------------------------------------------------|--|

| TH01         | θJA       | Thermal Resistance                     | 69.8  | C/W   | 14-pin PDIP package                                      |  |

|              |           | Junction to Ambient                    | 85.0  | C/W   | 14-pin SOIC package                                      |  |

|              |           |                                        | 100.4 | C/W   | 14-pin TSSOP package                                     |  |

|              |           |                                        | 46.3  | C/W   | 16-pin QFN 4x0.9mm package                               |  |

| TH02         | θις       | Thermal Resistance<br>Junction to Case | 32.5  | C/W   | 14-pin PDIP package                                      |  |

|              |           |                                        | 31.0  | C/W   | 14-pin SOIC package                                      |  |

|              |           |                                        | 31.7  | C/W   | 14-pin TSSOP package                                     |  |

|              |           |                                        | 2.6   | C/W   | 16-pin QFN 4x0.9mm package                               |  |

| TH03         | TJ        | Junction Temperature                   | 150   | С     | For derated power calculations                           |  |

| TH04         | PD        | Power Dissipation                      | —     | W     | PD = PINTERNAL + PI/O                                    |  |

| TH05         | PINTERNAL | Internal Power Dissipation             | —     | W     | PINTERNAL = IDD x VDD<br>(NOTE 1)                        |  |

| TH06         | PI/O      | I/O Power Dissipation                  | _     | W     | $PI/O = \Sigma (IOL * VOL) + \Sigma (IOH * (VDD - VOH))$ |  |

| TH07         | Pder      | Derated Power                          | -     | W     | Pder = (Tj - Ta)/θja<br>(NOTE 2, 3)                      |  |

Note 1: IDD is current to run the chip alone without driving any load on the output pins.

**2:** TA = Ambient Temperature.

**3:** Maximum allowable power dissipation is the lower value of either the absolute maximum total power dissipation or derated power (PDER).

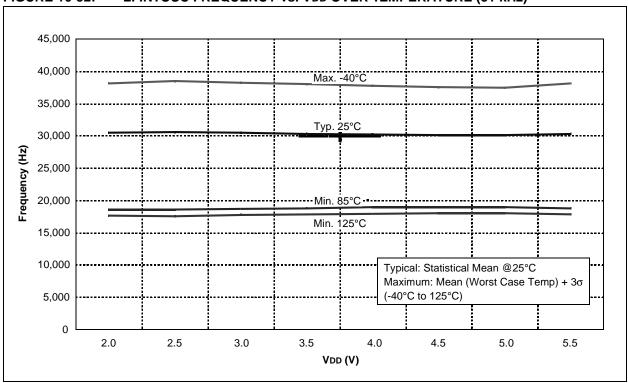

FIGURE 16-32: LFINTOSC FREQUENCY vs. Vdd OVER TEMPERATURE (31 kHz)

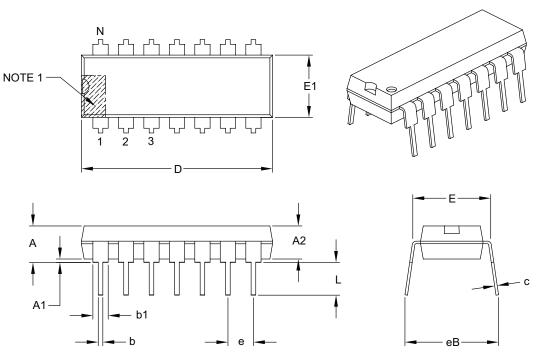

#### 17.2 Package Details

The following sections give the technical details of the packages.

#### 14-Lead Plastic Dual In-Line (P or PD) – 300 mil Body [PDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | INCHES   |          |      |      |  |

|----------------------------|----------|----------|------|------|--|

| Dimensio                   | n Limits | MIN      | NOM  | MAX  |  |

| Number of Pins             | Ν        | 14       |      |      |  |

| Pitch                      | е        | .100 BSC |      |      |  |

| Top to Seating Plane       | Α        | -        | -    | .210 |  |

| Molded Package Thickness   | A2       | .115     | .130 | .195 |  |

| Base to Seating Plane      | A1       | .015     | -    | -    |  |

| Shoulder to Shoulder Width | Е        | .290     | .310 | .325 |  |

| Molded Package Width       | E1       | .240     | .250 | .280 |  |

| Overall Length             | D        | .735     | .750 | .775 |  |

| Tip to Seating Plane       | L        | .115     | .130 | .150 |  |

| Lead Thickness             | С        | .008     | .010 | .015 |  |

| Upper Lead Width           | b1       | .045     | .060 | .070 |  |

| Lower Lead Width           |          | .014     | .018 | .022 |  |

| Overall Row Spacing §      | eB       | -        | -    | .430 |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located with the hatched area.

2. § Significant Characteristic.

3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-005B

#### **READER RESPONSE**

It is our intention to provide you with the best documentation possible to ensure successful use of your Microchip product. If you wish to provide your comments on organization, clarity, subject matter, and ways in which our documentation can better serve you, please FAX your comments to the Technical Publications Manager at (480) 792-4150.

Please list the following information, and use this outline to provide us with your comments about this document.

| To:                     | Technical Publications Manager                                                       | Total Pages Sent                                       |  |  |  |  |  |  |  |

|-------------------------|--------------------------------------------------------------------------------------|--------------------------------------------------------|--|--|--|--|--|--|--|

| RE:                     | Reader Response                                                                      |                                                        |  |  |  |  |  |  |  |

| From                    | n: Name                                                                              |                                                        |  |  |  |  |  |  |  |

|                         | Company                                                                              |                                                        |  |  |  |  |  |  |  |

|                         |                                                                                      |                                                        |  |  |  |  |  |  |  |

|                         | City / State / ZIP / Country                                                         |                                                        |  |  |  |  |  |  |  |

|                         | Telephone: ()                                                                        | FAX: ()                                                |  |  |  |  |  |  |  |

| Application (optional): |                                                                                      |                                                        |  |  |  |  |  |  |  |

| Wou                     | ld you like a reply?YN                                                               |                                                        |  |  |  |  |  |  |  |

| Devi                    | ce: PIC16F684                                                                        | Literature Number: DS41202F                            |  |  |  |  |  |  |  |

| Ques                    | stions:                                                                              |                                                        |  |  |  |  |  |  |  |

| 1. \                    | 1. What are the best features of this document?                                      |                                                        |  |  |  |  |  |  |  |

| _                       |                                                                                      |                                                        |  |  |  |  |  |  |  |

| _                       |                                                                                      |                                                        |  |  |  |  |  |  |  |

| 2. ł                    | 2. How does this document meet your hardware and software development needs?         |                                                        |  |  |  |  |  |  |  |

| -                       |                                                                                      |                                                        |  |  |  |  |  |  |  |

| _                       |                                                                                      |                                                        |  |  |  |  |  |  |  |

| 3. [                    | Do you find the organization of this document easy to follow? If not, why?           |                                                        |  |  |  |  |  |  |  |

| -                       |                                                                                      |                                                        |  |  |  |  |  |  |  |

|                         |                                                                                      |                                                        |  |  |  |  |  |  |  |

| 4. \                    | What additions to the document do you think would enhance the structure and subject? |                                                        |  |  |  |  |  |  |  |

| -                       |                                                                                      |                                                        |  |  |  |  |  |  |  |

| - \<br>-                |                                                                                      |                                                        |  |  |  |  |  |  |  |

| 5. \                    | what deletions from the document c                                                   | ould be made without affecting the overall usefulness? |  |  |  |  |  |  |  |

| -                       |                                                                                      |                                                        |  |  |  |  |  |  |  |

| -<br>6. I               | Is there any incorrect or misleading information (what and where)?                   |                                                        |  |  |  |  |  |  |  |

| 0. 1                    | s there any incorrect of misleading                                                  |                                                        |  |  |  |  |  |  |  |

| -                       |                                                                                      |                                                        |  |  |  |  |  |  |  |

| -<br>7. ł               | How would you improve this docume                                                    | ent?                                                   |  |  |  |  |  |  |  |

|                         |                                                                                      |                                                        |  |  |  |  |  |  |  |

| -                       |                                                                                      |                                                        |  |  |  |  |  |  |  |

| -                       |                                                                                      |                                                        |  |  |  |  |  |  |  |