Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | -                                                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 12                                                                       |

| Program Memory Size        | 3.5KB (2K x 14)                                                          |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 256 x 8                                                                  |

| RAM Size                   | 128 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | A/D 8x10b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 14-SOIC (0.154", 3.90mm Width)                                           |

| Supplier Device Package    | 14-SOIC                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f684-e-sl |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# PIC16F684

|  | TABLE 3-2: | SUMMARY OF REGISTERS ASSOCIATED WITH CLOCK SOURCES |

|--|------------|----------------------------------------------------|

|--|------------|----------------------------------------------------|

| Name                  | Bit 7 | Bit 6 | Bit 5  | Bit 4 | Bit 3 | Bit 2 | Bit 1  | Bit 0  | Value on:<br>POR, BOR | Value on<br>all other<br>Resets <sup>(1)</sup> |

|-----------------------|-------|-------|--------|-------|-------|-------|--------|--------|-----------------------|------------------------------------------------|

| CONFIG <sup>(2)</sup> | CPD   | CP    | MCLRE  | PWRTE | WDTE  | FOSC2 | FOSC1  | FOSC0  | _                     | _                                              |

| OSCCON                | _     | IRCF2 | IRCF1  | IRCF0 | OSTS  | HTS   | LTS    | SCS    | -110 x000             | -110 x000                                      |

| OSCTUNE               | _     | —     | —      | TUN4  | TUN3  | TUN2  | TUN1   | TUN0   | 0 0000                | u uuuu                                         |

| PIE1                  | EEIE  | ADIE  | CCP1IE | C2IE  | C1IE  | OSFIE | TMR2IE | TMR1IE | 0000 0000             | 0000 0000                                      |

| PIR1                  | EEIF  | ADIF  | CCP1IF | C2IF  | C1IF  | OSFIF | TMR2IF | TMR1IF | 0000 0000             | 0000 0000                                      |

$\label{eq:logend: Legend: x = unknown, u = unchanged, - = unimplemented locations read as `0`. Shaded cells are not used by oscillators.$

Note 1: Other (non Power-up) Resets include MCLR Reset and Watchdog Timer Reset during normal operation.

2: See Configuration Word register (Register 12-1) for operation of all register bits.

| U-0                                | U-0                        | R/W-1           | R/W-1        | U-0                                     | R/W-1            | R/W-1    | R/W-1 |

|------------------------------------|----------------------------|-----------------|--------------|-----------------------------------------|------------------|----------|-------|

| _                                  | —                          | WPUA5           | WPUA4        |                                         | WPUA2            | WPUA1    | WPUA0 |

| bit 7                              |                            |                 |              |                                         |                  |          | bit 0 |

|                                    |                            |                 |              |                                         |                  |          |       |

| Legend:                            |                            |                 |              |                                         |                  |          |       |

| R = Reada                          | ble bit                    | W = Writable    | bit          | U = Unimpler                            | mented bit, read | l as '0' |       |

| -n = Value at POR '1' = Bit is set |                            |                 |              | '0' = Bit is cleared x = Bit is unknown |                  |          |       |

|                                    |                            |                 |              |                                         |                  |          |       |

| bit 7-6                            | Unimplemen                 | ted: Read as 'o | )'           |                                         |                  |          |       |

| bit 5-4                            | WPUA<5:4>:                 | Weak Pull-up    | Control bits |                                         |                  |          |       |

|                                    | 1 = Pull-up er             | abled           |              |                                         |                  |          |       |

|                                    | 0 = Pull-up dis            | sabled          |              |                                         |                  |          |       |

| bit 3                              | Unimplemented: Read as '0' |                 |              |                                         |                  |          |       |

| bit 2-0                            | WPUA<2:0>:                 | Weak Pull-up    | Control bits |                                         |                  |          |       |

| 1 = Pull-up enabled                |                            |                 |              |                                         |                  |          |       |

|                                    | 0 = Pull-up dis            | sabled          |              |                                         |                  |          |       |

|                                    |                            |                 |              |                                         |                  |          |       |

#### REGISTER 4-4: WPUA: WEAK PULL-UP PORTA REGISTER

**Note 1:** Global RAPU must be enabled for individual pull-ups to be enabled.

- 2: The weak pull-up device is automatically disabled if the pin is in Output mode (TRISA = 0).

- 3: The RA3 pull-up is enabled when configured as MCLR and disabled as an I/O in the Configuration Word.

- **4:** WPUA<5:4> always reads '1' in XT, HS and LP OSC modes.

#### REGISTER 4-5: IOCA: INTERRUPT-ON-CHANGE PORTA REGISTER

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-------|-------|-------|-------|-------|-------|

| —     | —   | IOCA5 | IOCA4 | IOCA3 | IOCA2 | IOCA1 | IOCA0 |

| bit 7 |     |       |       |       |       |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 7-6 Unimplemented: Read as '0'

bit 5-0 IOCA<5:0>: Interrupt-on-change PORTA Control bit

- 1 = Interrupt-on-change enabled

- 0 = Interrupt-on-change disabled

- Note 1: Global Interrupt Enable (GIE) must be enabled for individual interrupts to be recognized.

- 2: IOCA<5:4> always reads '1' in XT, HS and LP OSC modes.

| R/W-1         | R/W-1                    | R/W-1                    | R/W-1           | R/W-1            | R/W-1           | R/W-1           | R/W-1 |  |  |  |

|---------------|--------------------------|--------------------------|-----------------|------------------|-----------------|-----------------|-------|--|--|--|

| RAPU          | INTEDG                   | TOCS                     | TOSE            | PSA              | PS2             | PS1             | PS0   |  |  |  |

| bit 7         |                          | -                        |                 | -                |                 |                 | bit ( |  |  |  |

|               |                          |                          |                 |                  |                 |                 |       |  |  |  |

| Legend:       |                          |                          |                 |                  |                 |                 |       |  |  |  |

| R = Readable  | e bit                    | W = Writable             | bit             | U = Unimpler     | mented bit, rea | id as '0'       |       |  |  |  |

| -n = Value at | POR                      | '1' = Bit is set         |                 | '0' = Bit is cle | ared            | x = Bit is unkr | nown  |  |  |  |

|               |                          |                          |                 |                  |                 |                 |       |  |  |  |

| bit 7         | RAPU: POR                | TA Pull-up Ena           | ble bit         |                  |                 |                 |       |  |  |  |

|               | 1 = PORTA p              | oull-ups are disa        | abled           |                  |                 |                 |       |  |  |  |

|               | 0 = PORTA p              | oull-ups are ena         | abled by indivi | dual PORT late   | h values        |                 |       |  |  |  |

| bit 6         | INTEDG: Inte             | errupt Edge Se           | lect bit        |                  |                 |                 |       |  |  |  |

|               |                          | on rising edge           | •               |                  |                 |                 |       |  |  |  |

|               | 0 = Interrupt            | on falling edge          | of INT pin      |                  |                 |                 |       |  |  |  |

| bit 5         | TOCS: TMRC               | Clock Source             | Select bit      |                  |                 |                 |       |  |  |  |

|               |                          | n on T0CKI pin           |                 |                  |                 |                 |       |  |  |  |

|               |                          | nstruction cycle         |                 | 4)               |                 |                 |       |  |  |  |

| bit 4         |                          | Source Edge              |                 |                  |                 |                 |       |  |  |  |

|               |                          | nt on high-to-lov        |                 |                  |                 |                 |       |  |  |  |

|               |                          | nt on low-to-hig         |                 | 10CKI pin        |                 |                 |       |  |  |  |

| bit 3         |                          | ller Assignment          |                 |                  |                 |                 |       |  |  |  |

|               |                          | r is assigned to         |                 |                  |                 |                 |       |  |  |  |

|               |                          | r is assigned to         |                 | nodule           |                 |                 |       |  |  |  |

| bit 2-0       | <b>PS&lt;2:0&gt;:</b> Pr | escaler Rate Se          | elect bits      |                  |                 |                 |       |  |  |  |

|               | BIT                      | VALUE TMR0 R             | ATE WDT RA      | TE               |                 |                 |       |  |  |  |

|               |                          | 000 1:2                  | 1:1             |                  |                 |                 |       |  |  |  |

|               |                          | 001 1:4                  | 1:2             |                  |                 |                 |       |  |  |  |

|               |                          | 010 1:8<br>011 1:10      | 1:4             |                  |                 |                 |       |  |  |  |

|               |                          | 011 1 : 10<br>100 1 : 32 |                 |                  |                 |                 |       |  |  |  |

|               |                          | 100 1.32                 |                 |                  |                 |                 |       |  |  |  |

|               |                          | 110 1 : 12               |                 |                  |                 |                 |       |  |  |  |

|               |                          | 111 1:25                 |                 | 3                |                 |                 |       |  |  |  |

#### REGISTER 5-1: OPTION\_REG: OPTION REGISTER

Note 1: A dedicated 16-bit WDT postscaler is available. See Section 12.6 "Watchdog Timer (WDT)" for more information.

#### TABLE 5-1: SUMMARY OF REGISTERS ASSOCIATED WITH TIMER0

| Name       | Bit 7    | Bit 6      | Bit 5  | Bit 4     | Bit 3     | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR, BOR | Value on<br>all other<br>Resets |

|------------|----------|------------|--------|-----------|-----------|--------|--------|--------|-----------------------|---------------------------------|

| TMR0       | Timer0 N | /lodule Re |        | xxxx xxxx | uuuu uuuu |        |        |        |                       |                                 |

| INTCON     | GIE      | PEIE       | TOIE   | INTE      | RAIE      | TOIF   | INTF   | RAIF   | 0000 0000             | 0000 0000                       |

| OPTION_REG | RAPU     | INTEDG     | TOCS   | T0SE      | PSA       | PS2    | PS1    | PS0    | 1111 1111             | 1111 1111                       |

| TRISA      |          | —          | TRISA5 | TRISA4    | TRISA3    | TRISA2 | TRISA1 | TRISA0 | 11 1111               | 11 1111                         |

**Legend:** – = Unimplemented locations, read as '0', u = unchanged, x = unknown. Shaded cells are not used by the Timer0 module.

## 8.3 Comparator Control

The CMCON0 register (Register 8-1) provides access to the following comparator features:

- Mode selection

- Output state

- Output polarity

- Input switch

#### 8.3.1 COMPARATOR OUTPUT STATE

Each comparator state can always be read internally via the associated CxOUT bit of the CMCON0 register. The comparator outputs are directed to the CxOUT pins when CM<2:0> = 110. When this mode is selected, the TRIS bits for the associated CxOUT pins must be cleared to enable the output drivers.

#### 8.3.2 COMPARATOR OUTPUT POLARITY

Inverting the output of a comparator is functionally equivalent to swapping the comparator inputs. The polarity of a comparator output can be inverted by setting the CxINV bits of the CMCON0 register. Clearing CxINV results in a non-inverted output. A complete table showing the output state versus input conditions and the polarity bit is shown in Table 8-1.

# TABLE 8-1: OUTPUT STATE VS. INPUT CONDITIONS

| Input Conditions | CxINV | CxOUT |

|------------------|-------|-------|

| VIN- > VIN+      | 0     | 0     |

| VIN- < VIN+      | 0     | 1     |

| VIN- > VIN+      | 1     | 1     |

| VIN- < VIN+      | 1     | 0     |

Note: CxOUT refers to both the register bit and output pin.

#### 8.3.3 COMPARATOR INPUT SWITCH

The inverting input of the comparators may be switched between two analog pins in the following modes:

- CM<2:0> = 001 (Comparator C1 only)

- CM<2:0> = 010 (Comparators C1 and C2)

In the above modes, both pins remain in Analog mode regardless of which pin is selected as the input. The CIS bit of the CMCON0 register controls the comparator input switch.

# 8.4 Comparator Response Time

The comparator output is indeterminate for a period of time after the change of an input source or the selection of a new reference voltage. This period is referred to as the response time. The response time of the comparator differs from the settling time of the voltage reference. Therefore, both of these times must be considered when determining the total response time to a comparator input change. See Comparator and Voltage Reference specifications of **Section 15.0 "Electrical Specifications"** for more details.

# 8.5 Comparator Interrupt Operation

The comparator interrupt flag is set whenever there is a change in the output value of the comparator. Changes are recognized by means of a mismatch circuit which consists of two latches and an exclusiveor gate (see Figure 8-2 and Figure 8-3). One latch is updated with the comparator output level when the CMCON0 register is read. This latch retains the value until the next read of the CMCON0 register or the occurrence of a reset. The other latch of the mismatch circuit is updated on every Q1 system clock. A mismatch condition will occur when a comparator output change is clocked through the second latch on the Q1 clock cycle. The mismatch condition will persist, holding the CxIF bit of the PIR1 register true, until either the CMCON0 register is read or the comparator output returns to the previous state.

| Note: | A write operation to the CMCON0 register       |  |  |  |  |  |  |  |

|-------|------------------------------------------------|--|--|--|--|--|--|--|

|       | will also clear the mismatch condition         |  |  |  |  |  |  |  |

|       | because all writes include a read              |  |  |  |  |  |  |  |

|       | operation at the beginning of the write cycle. |  |  |  |  |  |  |  |

Software will need to maintain information about the status of the comparator output to determine the actual change that has occurred.

The CxIF bit of the PIR1 register is the comparator interrupt flag. This bit must be reset in software by clearing it to '0'. Since it is also possible to write a '1' to this register, a simulated interrupt may be initiated.

The CxIE bit of the PIE1 register and the PEIE and GIE bits of the INTCON register must all be set to enable comparator interrupts. If any of these bits are cleared, the interrupt is not enabled, although the CxIF bit of the PIR1 register will still be set if an interrupt condition occurs.

The user, in the Interrupt Service Routine, can clear the interrupt in the following manner:

- a) Any read or write of CMCON0. This will end the mismatch condition.

- b) Clear the CxIF interrupt flag.

### 8.10 Comparator Voltage Reference

The comparator voltage reference module provides an internally generated voltage reference for the comparators. The following features are available:

- Independent from Comparator operation

- Two 16-level voltage ranges

- Output clamped to Vss

- Ratiometric with VDD

The VRCON register (Register) controls the voltage reference module shown in Figure 8-8.

#### 8.10.1 INDEPENDENT OPERATION

The comparator voltage reference is independent of the comparator configuration. Setting the VREN bit of the VRCON register will enable the voltage reference.

#### 8.10.2 OUTPUT VOLTAGE SELECTION

The CVREF voltage reference has 2 ranges with 16 voltage levels in each range. Range selection is controlled by the VRR bit of the VRCON register. The 16 levels are set with the VR<3:0> bits of the VRCON register.

The CVREF output voltage is determined by the following equations:

#### EQUATION 8-1: CVREF OUTPUT VOLTAGE

```

VRR = 1 (low range):

CVREF = (VR < 3:0 > /24) \times VDD

VRR = 0 (high range):

CVREF = (VDD/4) + (VR < 3:0 > \times VDD/32)

```

The full range of Vss to VDD cannot be realized due to the construction of the module. See Figure 8-8.

### 8.10.3 OUTPUT CLAMPED TO Vss

The CVREF output voltage can be set to Vss with no power consumption by configuring VRCON as follows:

- VREN = 0

- VRR = 1

- VR<3:0> = 0000

This allows the comparator to detect a zero-crossing while not consuming additional CVREF module current.

#### 8.10.4 OUTPUT RATIOMETRIC TO VDD

The comparator voltage reference is VDD derived and therefore, the CVREF output changes with fluctuations in VDD. The tested absolute accuracy of the Comparator Voltage Reference can be found in **Section 15.0 "Electrical Specifications"**.

#### VRCON: VOLTAGE REFERENCE CONTROL REGISTER

| R/W-0 | U-0 | R/W-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-------|-----|-------|-------|-------|-------|

| VREN  | —   | VRR   | —   | VR3   | VR2   | VR1   | VR0   |

| bit 7 |     |       |     |       |       |       | bit 0 |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

| bit 7   | VREN: CVREF Enable bit                                                                                                                                                                      |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 1 = CVREF circuit powered on                                                                                                                                                                |

|         | 0 = CVREF circuit powered down, no IDD drain and CVREF = VSS.                                                                                                                               |

| bit 6   | Unimplemented: Read as '0'                                                                                                                                                                  |

| bit 5   | VRR: CVREF Range Selection bit                                                                                                                                                              |

|         | 1 = Low range<br>0 = High range                                                                                                                                                             |

| bit 4   | Unimplemented: Read as '0'                                                                                                                                                                  |

| bit 3-0 | <b>VR&lt;3:0&gt;:</b> CVREF Value Selection bits ( $0 \le VR<3:0> \le 15$ )<br><u>When VRR = 1</u> : CVREF = (VR<3:0>/24) * VDD<br><u>When VRR = 0</u> : CVREF = VDD/4 + (VR<3:0>/32) * VDD |

| Name   | Bit 7     | Bit 6        | Bit 5     | Bit 4  | Bit 3  | Bit 2  | Bit 1   | Bit 0  | Value on:<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|-----------|--------------|-----------|--------|--------|--------|---------|--------|-----------------------|---------------------------------|

| ADCON0 | ADFM      | VCFG         | —         | CHS2   | CHS1   | CHS0   | GO/DONE | ADON   | 0000 0000             | 0000 0000                       |

| ADCON1 | _         | ADCS2        | ADCS1     | ADCS0  | —      | _      | _       | _      | -000                  | -000                            |

| ANSEL  | ANS7      | ANS6         | ANS5      | ANS4   | ANS3   | ANS2   | ANS1    | ANS0   | 1111 1111             | 1111 1111                       |

| ADRESH | A/D Resul | t Register H | ligh Byte |        |        |        |         |        | xxxx xxxx             | uuuu uuuu                       |

| ADRESL | A/D Resul | t Register L | ow Byte   |        |        |        |         |        | xxxx xxxx             | uuuu uuuu                       |

| INTCON | GIE       | PEIE         | TOIE      | INTE   | RAIE   | T0IF   | INTF    | RAIF   | 0000 0000             | 0000 0000                       |

| PIE1   | EEIE      | ADIE         | CCPIE     | C2IE   | C1IE   | OSFIE  | TMR2IE  | TMR1IE | 0000 0000             | 0000 0000                       |

| PIR1   | EEIF      | ADIF         | CCPIF     | C2IF   | C1IF   | OSFIF  | TMR2IF  | TMR1IF | 0000 0000             | 0000 0000                       |

| PORTA  | —         | _            | RA5       | RA4    | RA3    | RA2    | RA1     | RA0    | x0 x000               | uu uuuu                         |

| PORTC  | _         | _            | RC5       | RC4    | RC3    | RC2    | RC1     | RC0    | xx 0000               | uu uuuu                         |

| TRISA  |           | _            | TRISA5    | TRISA4 | TRISA3 | TRISA2 | TRISA1  | TRISA0 | 11 1111               | 11 1111                         |

| TRISC  | —         | _            | TRISC5    | TRISC4 | TRISC3 | TRISC2 | TRISC1  | TRISC0 | 11 1111               | 11 1111                         |

### TABLE 9-2:SUMMARY OF ASSOCIATED ADC REGISTERS

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used for ADC module.

#### 10.1 **EECON1 and EECON2 Registers**

EECON1 is the control register with four low-order bits physically implemented. The upper four bits are non-implemented and read as '0's.

Control bits RD and WR initiate read and write, respectively. These bits cannot be cleared, only set in software. They are cleared in hardware at completion of the read or write operation. The inability to clear the WR bit in software prevents the accidental, premature termination of a write operation.

The WREN bit, when set, will allow a write operation. On power-up, the WREN bit is clear. The WRERR bit is set when a write operation is interrupted by a MCLR Reset, or a WDT Time-out Reset during normal operation. In these situations, following Reset, the user can check the WRERR bit, clear it and rewrite the location. The data and address will be cleared. Therefore, the EEDAT and EEADR registers will need to be re-initialized.

Interrupt flag, EEIF bit of the PIR1 register, is set when write is complete. This bit must be cleared in software.

EECON2 is not a physical register. Reading EECON2 will read all '0's. The EECON2 register is used exclusively in the data EEPROM write sequence.

| Note: | The   | EECON1,     | EEDAT      | and      | EEADR    |

|-------|-------|-------------|------------|----------|----------|

|       | regis | ters should | not be mo  | odified  | during a |

|       | data  | EEPROM w    | rite (WR b | oit = 1) |          |

#### REGISTER 10-3: EECON1: EEPROM CONTROL REGISTER

| U-0              | U-0        | U-0              | U-0 | R/W-x            | R/W-0            | R/S-0           | R/S-0 |

|------------------|------------|------------------|-----|------------------|------------------|-----------------|-------|

| —                | —          | —                | —   | WRERR            | WREN             | WR              | RD    |

| bit 7            |            |                  |     |                  |                  |                 | bit 0 |

|                  |            |                  |     |                  |                  |                 |       |

| Legend:          |            |                  |     |                  |                  |                 |       |

| S = Bit can only | y be set   |                  |     |                  |                  |                 |       |

| R = Readable I   | bit        | W = Writable I   | bit | U = Unimpler     | mented bit, read | as '0'          |       |

| -n = Value at P  | OR         | '1' = Bit is set |     | '0' = Bit is cle | ared             | x = Bit is unkr | nown  |

|                  |            |                  |     |                  |                  |                 |       |

| hit 7-4          | Unimplemen | ted: Read as '(  | י'  |                  |                  |                 |       |

| bit 7-4 | Unimplemented: Read as '0'                                                                                                                                                                                             |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 3   | WRERR: EEPROM Error Flag bit                                                                                                                                                                                           |

|         | <ul> <li>1 = A write operation is prematurely terminated (any MCLR Reset, any WDT Reset during normal operation or BOR Reset)</li> <li>0 = The write operation completed</li> </ul>                                    |

| bit 2   | WREN: EEPROM Write Enable bit                                                                                                                                                                                          |

|         | <ul><li>1 = Allows write cycles</li><li>0 = Inhibits write to the data EEPROM</li></ul>                                                                                                                                |

| bit 1   | WR: Write Control bit                                                                                                                                                                                                  |

|         | <ul> <li>1 = Initiates a write cycle (The bit is cleared by hardware once write is complete. The WR bit can only be set, not cleared, in software.)</li> <li>0 = Write cycle to the data EEPROM is complete</li> </ul> |

| bit 0   | RD: Read Control bit                                                                                                                                                                                                   |

|         | <ul> <li>1 = Initiates an EEPROM read (Read takes one cycle. RD is cleared in hardware. The RD bit can only be set, not cleared, in software.)</li> <li>0 = Does not initiate an EEPROM read</li> </ul>                |

|         | bit 3<br>bit 2<br>bit 1                                                                                                                                                                                                |

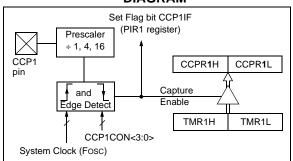

# 11.1 Capture Mode

In Capture mode, CCPR1H:CCPR1L captures the 16-bit value of the TMR1 register when an event occurs on pin CCP1. An event is defined as one of the following and is configured by the CCP1M<3:0> bits of the CCP1CON register:

- · Every falling edge

- Every rising edge

- Every 4th rising edge

- Every 16th rising edge

When a capture is made, the Interrupt Request Flag bit CCP1IF of the PIR1 register is set. The interrupt flag must be cleared in software. If another capture occurs before the value in the CCPR1H, CCPR1L register pair is read, the old captured value is overwritten by the new captured value (see Figure 11-1).

#### 11.1.1 CCP1 PIN CONFIGURATION

In Capture mode, the CCP1 pin should be configured as an input by setting the associated TRIS control bit.

| Note: | If the CCP1 pin is configured as an output, |

|-------|---------------------------------------------|

|       | a write to the port can cause a capture     |

|       | condition.                                  |

#### FIGURE 11-1: CAPTURE MODE OPERATION BLOCK DIAGRAM

#### 11.1.2 TIMER1 MODE SELECTION

Timer1 must be running in Timer mode or Synchronized Counter mode for the CCP module to use the capture feature. In Asynchronous Counter mode, the capture operation may not work.

### 11.1.3 SOFTWARE INTERRUPT

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep the CCP1IE interrupt enable bit of the PIE1 register clear to avoid false interrupts. Additionally, the user should clear the CCP1IF interrupt flag bit of the PIR1 register following any change in operating mode.

#### 11.1.4 CCP PRESCALER

There are four prescaler settings specified by the CCP1M<3:0> bits of the CCP1CON register. Whenever the CCP module is turned off, or the CCP module is not in Capture mode, the prescaler counter is cleared. Any Reset will clear the prescaler counter.

Switching from one capture prescaler to another does not clear the prescaler and may generate a false interrupt. To avoid this unexpected operation, turn the module off by clearing the CCP1CON register before changing the prescaler (see Example 11-1).

#### EXAMPLE 11-1: CHANGING BETWEEN CAPTURE PRESCALERS

| BANKSEL | CCP1CON     | ;Set Bank bits to point |  |  |  |  |  |

|---------|-------------|-------------------------|--|--|--|--|--|

|         | ;to CCP1CON |                         |  |  |  |  |  |

| CLRF    | CCP1CON     | ;Turn CCP module off    |  |  |  |  |  |

| MOVLW   | NEW_CAPT_PS | ;Load the W reg with    |  |  |  |  |  |

|         |             | ; the new prescaler     |  |  |  |  |  |

|         |             | ; move value and CCP ON |  |  |  |  |  |

| MOVWF   | CCP1CON     | ;Load CCP1CON with this |  |  |  |  |  |

|         |             | ; value                 |  |  |  |  |  |

|         |             |                         |  |  |  |  |  |

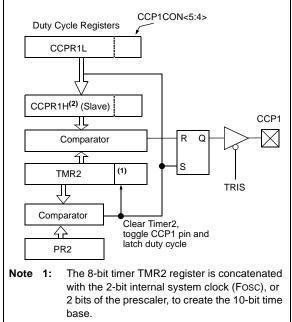

# 11.3 PWM Mode

The PWM mode generates a Pulse-Width Modulated signal on the CCP1 pin. The duty cycle, period and resolution are determined by the following registers:

- PR2

- T2CON

- CCPR1L

- CCP1CON

In Pulse-Width Modulation (PWM) mode, the CCP module produces up to a 10-bit resolution PWM output on the CCP1 pin. Since the CCP1 pin is multiplexed with the PORT data latch, the TRIS for that pin must be cleared to enable the CCP1 pin output driver.

| Note: | Clearing   | the | CCP1CON        | register | will |

|-------|------------|-----|----------------|----------|------|

|       | relinquish | CCP | 1 control of t | ne CCP1  | pin. |

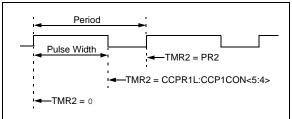

Figure 11-3 shows a simplified block diagram of PWM operation.

Figure 11-4 shows a typical waveform of the PWM signal.

For a step by step procedure on how to set up the CCP module for PWM operation, see **Section 11.3.7** "Setup for PWM Operation".

FIGURE 11-3: SIMPLIFIED PWM BLOCK DIAGRAM

2: In PWM mode, CCPR1H is a read-only register.

The PWM output (Figure 11-4) has a time base (period) and a time that the output stays high (duty cycle).

FIGURE 11-4: CCP PWM OUTPUT

#### 11.3.4 OPERATION IN SLEEP MODE

In Sleep mode, the TMR2 register will not increment and the state of the module will not change. If the CCP1 pin is driving a value, it will continue to drive that value. When the device wakes up, TMR2 will continue from its previous state.

#### 11.3.5 CHANGES IN SYSTEM CLOCK FREQUENCY

The PWM frequency is derived from the system clock frequency. Any changes in the system clock frequency will result in changes to the PWM frequency. See Section 3.0 "Oscillator Module (With Fail-Safe Clock Monitor)" for additional details.

#### 11.3.6 EFFECTS OF RESET

Any Reset will force all ports to Input mode and the CCP registers to their Reset states.

#### 11.3.7 SETUP FOR PWM OPERATION

The following steps should be taken when configuring the CCP module for PWM operation:

- 1. Disable the PWM pin (CCP1) output driver by setting the associated TRIS bit.

- 2. Set the PWM period by loading the PR2 register.

- Configure the CCP module for the PWM mode by loading the CCP1CON register with the appropriate values.

- 4. Set the PWM duty cycle by loading the CCPR1L register and CCP1 bits of the CCP1CON register.

- 5. Configure and start Timer2:

- Clear the TMR2IF interrupt flag bit of the PIR1 register.

- Set the Timer2 prescale value by loading the T2CKPS bits of the T2CON register.

- Enable Timer2 by setting the TMR2ON bit of the T2CON register.

- 6. Enable PWM output after a new PWM cycle has started:

- Wait until Timer2 overflows (TMR2IF bit of the PIR1 register is set).

- Enable the CCP1 pin output driver by clearing the associated TRIS bit.

# 12.5 Context Saving During Interrupts

During an interrupt, only the return PC value is saved on the stack. Typically, users may wish to save key registers during an interrupt (e.g., W and STATUS registers). This must be implemented in software.

Temporary holding registers W\_TEMP and STATUS\_TEMP should be placed in the last 16 bytes of GPR (see Figure 2-2). These 16 locations are common to all banks and do not require banking. This makes context save and restore operations simpler. The code shown in Example 12-1 can be used to:

- Store the W register

- Store the STATUS register

- Execute the ISR code

- Restore the Status (and Bank Select Bit register)

- Restore the W register

| Note: | The PIC16F684 does not require saving  |

|-------|----------------------------------------|

|       | the PCLATH. However, if computed       |

|       | GOTOS are used in both the ISR and the |

|       | main code, the PCLATH must be saved    |

|       | and restored in the ISR.               |

#### EXAMPLE 12-1: SAVING STATUS AND W REGISTERS IN RAM

|                | W_TEMP<br>STATUS,W   | ;Copy W to TEMP register<br>;Swap status to be saved into W                                                  |

|----------------|----------------------|--------------------------------------------------------------------------------------------------------------|

| MOVWF          | STATUS_TEMP          | ;Swaps are used because they do not affect the status bits<br>;Save status to bank zero STATUS_TEMP register |

| :<br>:(ISR)    |                      | ;Insert user code here                                                                                       |

| :<br>SWAPF     | STATUS_TEMP,W        | ;Swap STATUS_TEMP register into W                                                                            |

| MOVWF<br>SWAPF | STATUS               | ;(sets bank to original state)<br>;Move W into STATUS register                                               |

| SWAPF          | W_TEMP,F<br>W_TEMP,W | ;Swap W_TEMP<br>;Swap W_TEMP into W                                                                          |

# 14.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers are supported with a full range of hardware and software development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> IDE Software

- Assemblers/Compilers/Linkers

- MPASM<sup>™</sup> Assembler

- MPLAB C18 and MPLAB C30 C Compilers

- MPLINK<sup>™</sup> Object Linker/

- MPLIB<sup>™</sup> Object Librarian

- MPLAB ASM30 Assembler/Linker/Library

- Simulators

- MPLAB SIM Software Simulator

- Emulators

- MPLAB ICE 2000 In-Circuit Emulator

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debugger

- MPLAB ICD 2

- Device Programmers

- PICSTART<sup>®</sup> Plus Development Programmer

- MPLAB PM3 Device Programmer

- PICkit<sup>™</sup> 2 Development Programmer

- Low-Cost Demonstration and Development Boards and Evaluation Kits

# 14.1 MPLAB Integrated Development Environment Software

The MPLAB IDE software brings an ease of software development previously unseen in the 8/16-bit microcontroller market. The MPLAB IDE is a Windows<sup>®</sup> operating system-based application that contains:

- · A single graphical interface to all debugging tools

- Simulator

- Programmer (sold separately)

- Emulator (sold separately)

- In-Circuit Debugger (sold separately)

- · A full-featured editor with color-coded context

- A multiple project manager

- Customizable data windows with direct edit of contents

- High-level source code debugging

- Visual device initializer for easy register initialization

- Mouse over variable inspection

- Drag and drop variables from source to watch windows

- Extensive on-line help

- Integration of select third party tools, such as HI-TECH Software C Compilers and IAR C Compilers

The MPLAB IDE allows you to:

- Edit your source files (either assembly or C)

- One touch assemble (or compile) and download to PIC MCU emulator and simulator tools (automatically updates all project information)

- Debug using:

- Source files (assembly or C)

- Mixed assembly and C

- Machine code

MPLAB IDE supports multiple debugging tools in a single development paradigm, from the cost-effective simulators, through low-cost in-circuit debuggers, to full-featured emulators. This eliminates the learning curve when upgrading to tools with increased flexibility and power.

| DC CH        | ARACTE | RISTICS                              | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |       |          |       |                                                                    |  |

|--------------|--------|--------------------------------------|------------------------------------------------------|-------|----------|-------|--------------------------------------------------------------------|--|

| Param<br>No. | Sym    | Characteristic                       | Min                                                  | Тур†  | Мах      | Units | Conditions                                                         |  |

|              | VIL    | Input Low Voltage                    |                                                      |       |          |       |                                                                    |  |

|              |        | I/O Port:                            |                                                      |       |          |       |                                                                    |  |

| D030         |        | with TTL buffer                      | Vss                                                  | —     | 0.8      | V     | $4.5V \le VDD \le 5.5V$                                            |  |

| D030A        |        |                                      | Vss                                                  | —     | 0.15 Vdd | V     | $2.0V \le VDD \le 4.5V$                                            |  |

| D031         |        | with Schmitt Trigger buffer          | Vss                                                  | —     | 0.2 Vdd  | V     | $2.0V \le VDD \le 5.5V$                                            |  |

| D032         |        | MCLR, OSC1 (RC mode) <sup>(1)</sup>  | Vss                                                  | —     | 0.2 Vdd  | V     |                                                                    |  |

| D033         |        | OSC1 (XT and LP modes)               | Vss                                                  | —     | 0.3      | V     |                                                                    |  |

| D033A        |        | OSC1 (HS mode)                       | Vss                                                  | —     | 0.3 Vdd  | V     |                                                                    |  |

|              | Vih    | Input High Voltage                   |                                                      |       |          |       |                                                                    |  |

|              |        | I/O ports:                           |                                                      | —     |          |       |                                                                    |  |

| D040         |        | with TTL buffer                      | 2.0                                                  | —     | Vdd      | V     | $4.5V \le VDD \le 5.5V$                                            |  |

| D040A        |        |                                      | 0.25 VDD + 0.8                                       | —     | Vdd      | V     | $2.0V \le VDD \le 4.5V$                                            |  |

| D041         |        | with Schmitt Trigger buffer          | 0.8 Vdd                                              | —     | Vdd      | V     | $2.0V \le VDD \le 5.5V$                                            |  |

| D042         |        | MCLR                                 | 0.8 Vdd                                              | —     | Vdd      | V     |                                                                    |  |

| D043         |        | OSC1 (XT and LP modes)               | 1.6                                                  | —     | Vdd      | V     |                                                                    |  |

| D043A        |        | OSC1 (HS mode)                       | 0.7 Vdd                                              | _     | Vdd      | V     |                                                                    |  |

| D043B        |        | OSC1 (RC mode)                       | 0.9 Vdd                                              | _     | Vdd      | V     | (Note 1)                                                           |  |

|              | lı∟    | Input Leakage Current <sup>(2)</sup> |                                                      |       |          |       |                                                                    |  |

| D060         |        | I/O ports                            | —                                                    | ±0.1  | ± 1      | μA    | Vss ≤ VPIN ≤ VDD,<br>Pin at high-impedance                         |  |

| D061         |        | MCLR <sup>(3)</sup>                  | _                                                    | ± 0.1 | ±5       | μΑ    | $VSS \leq VPIN \leq VDD$                                           |  |

| D063         |        | OSC1                                 | _                                                    | ±0.1  | ± 5      | μA    | Vss $\leq$ VPIN $\leq$ VDD, XT, HS and LP oscillator configuration |  |

| D070*        | IPUR   | PORTA Weak Pull-up Current           | 50                                                   | 250   | 400      | μΑ    | VDD = 5.0V, VPIN = VSS                                             |  |

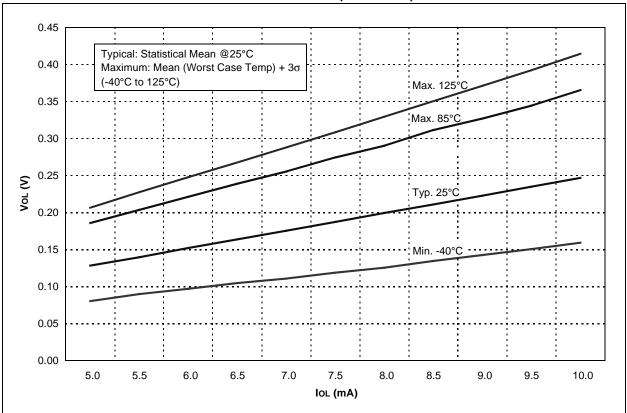

|              | Vol    | Output Low Voltage <sup>(5)</sup>    |                                                      |       |          |       |                                                                    |  |

| D080         |        | I/O ports                            | —                                                    | _     | 0.6      | V     | IOL = 8.5 mA, VDD = 4.5V (Ind.)                                    |  |

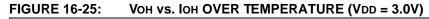

|              | Voн    | Output High Voltage <sup>(5)</sup>   |                                                      |       |          |       |                                                                    |  |

| D090         |        | I/O ports                            | Vdd - 0.7                                            |       | _        | V     | IOH = -3.0 mA, VDD = 4.5V (Ind.)                                   |  |

# 15.5 DC Characteristics: PIC16F684-I (Industrial) PIC16F684-E (Extended)

These parameters are characterized but not tested.

† Data in 'Typ' column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended to use an external clock in RC mode.

2: Negative current is defined as current sourced by the pin.

3: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

4: See Section 10.4.1 "Using the Data EEPROM" for additional information.

**5**: Including OSC2 in CLKOUT mode.

\*

# 15.5 DC Characteristics: PIC16F684-I (Industrial) PIC16F684-E (Extended) (Continued)

| DC CH        | DC CHARACTERISTICS |                                                                     |      | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |     |       |                                                                                                     |  |  |

|--------------|--------------------|---------------------------------------------------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|-----------------------------------------------------------------------------------------------------|--|--|

| Param<br>No. | Sym                | Characteristic                                                      | Min  | Тур†                                                                                                                                                                                    | Max | Units | Conditions                                                                                          |  |  |

| D100         | IULP               | Ultra Low-Power Wake-Up<br>Current                                  | _    | 200                                                                                                                                                                                     | _   | nA    | See Application Note AN879,<br>"Using the Microchip Ultra<br>Low-Power Wake-up Module"<br>(DS00879) |  |  |

|              |                    | Capacitive Loading Specs on<br>Output Pins                          |      |                                                                                                                                                                                         |     |       |                                                                                                     |  |  |

| D101*        | COSC2              | OSC2 pin                                                            | _    | -                                                                                                                                                                                       | 15  | pF    | In XT, HS and LP modes when<br>external clock is used to drive<br>OSC1                              |  |  |

| D101A*       | Сю                 | All I/O pins                                                        | _    | —                                                                                                                                                                                       | 50  | pF    |                                                                                                     |  |  |

|              |                    | Data EEPROM Memory                                                  |      |                                                                                                                                                                                         |     |       |                                                                                                     |  |  |

| D120         | ED                 | Byte Endurance                                                      | 100K | 1M                                                                                                                                                                                      | _   | E/W   | $-40^{\circ}C \le TA \le +85^{\circ}C$                                                              |  |  |

| D120A        | ED                 | Byte Endurance                                                      | 10K  | 100K                                                                                                                                                                                    | _   | E/W   | +85°C ≤ TA ≤ +125°C                                                                                 |  |  |

| D121         | Vdrw               | VDD for Read/Write                                                  | Vmin | -                                                                                                                                                                                       | 5.5 | V     | Using EECON1 to read/write<br>VMIN = Minimum operating<br>voltage                                   |  |  |

| D122         | TDEW               | Erase/Write Cycle Time                                              | _    | 5                                                                                                                                                                                       | 6   | ms    |                                                                                                     |  |  |

| D123         | Tretd              | Characteristic Retention                                            | 40   | —                                                                                                                                                                                       | —   | Year  | Provided no other specifications are violated                                                       |  |  |

| D124         | Tref               | Number of Total Erase/Write<br>Cycles before Refresh <sup>(4)</sup> | 1M   | 10M                                                                                                                                                                                     | —   | E/W   | $-40^{\circ}C \le TA \le +85^{\circ}C$                                                              |  |  |

|              |                    | Program Flash Memory                                                |      |                                                                                                                                                                                         |     |       |                                                                                                     |  |  |

| D130         | Eр                 | Cell Endurance                                                      | 10K  | 100K                                                                                                                                                                                    | —   | E/W   | -40°C ≤ TA ≤ +85°C                                                                                  |  |  |

| D130A        | ED                 | Cell Endurance                                                      | 1K   | 10K                                                                                                                                                                                     | _   | E/W   | +85°C ≤ TA ≤ +125°C                                                                                 |  |  |

| D131         | Vpr                | VDD for Read                                                        | VMIN | -                                                                                                                                                                                       | 5.5 | V     | Vміn = Minimum operating<br>voltage                                                                 |  |  |

| D132         | VPEW               | VDD for Erase/Write                                                 | 4.5  | —                                                                                                                                                                                       | 5.5 | V     |                                                                                                     |  |  |

| D133         | TPEW               | Erase/Write cycle time                                              | —    | 2                                                                                                                                                                                       | 2.5 | ms    |                                                                                                     |  |  |

| D134         | TRETD              | Characteristic Retention                                            | 40   | -                                                                                                                                                                                       | —   | Year  | Provided no other specifications are violated                                                       |  |  |

\* These parameters are characterized but not tested.

† Data in 'Typ' column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended to use an external clock in RC mode.

2: Negative current is defined as current sourced by the pin.

**3:** The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

4: See Section 10.4.1 "Using the Data EEPROM" for additional information.

5: Including OSC2 in CLKOUT mode.

# 15.6 Thermal Considerations

| Param<br>No. | Sym       | Characteristic             | Тур   | Units | Conditions                                               |

|--------------|-----------|----------------------------|-------|-------|----------------------------------------------------------|

| TH01         | θJA       | Thermal Resistance         | 69.8  | C/W   | 14-pin PDIP package                                      |

|              |           | Junction to Ambient        | 85.0  | C/W   | 14-pin SOIC package                                      |

|              |           |                            | 100.4 | C/W   | 14-pin TSSOP package                                     |

|              |           |                            | 46.3  | C/W   | 16-pin QFN 4x0.9mm package                               |

| TH02         | θJC       | Thermal Resistance         | 32.5  | C/W   | 14-pin PDIP package                                      |

|              |           | Junction to Case           | 31.0  | C/W   | 14-pin SOIC package                                      |

|              |           |                            | 31.7  | C/W   | 14-pin TSSOP package                                     |

|              |           |                            | 2.6   | C/W   | 16-pin QFN 4x0.9mm package                               |

| TH03         | TJ        | Junction Temperature       | 150   | С     | For derated power calculations                           |

| TH04         | PD        | Power Dissipation          | —     | W     | PD = PINTERNAL + PI/O                                    |

| TH05         | PINTERNAL | Internal Power Dissipation | —     | W     | PINTERNAL = IDD x VDD<br>(NOTE 1)                        |

| TH06         | PI/O      | I/O Power Dissipation      | _     | W     | $PI/O = \Sigma (IOL * VOL) + \Sigma (IOH * (VDD - VOH))$ |

| TH07         | Pder      | Derated Power              | -     | W     | Pder = (Tj - Ta)/θja<br>(NOTE 2, 3)                      |

Note 1: IDD is current to run the chip alone without driving any load on the output pins.

**2:** TA = Ambient Temperature.

**3:** Maximum allowable power dissipation is the lower value of either the absolute maximum total power dissipation or derated power (PDER).

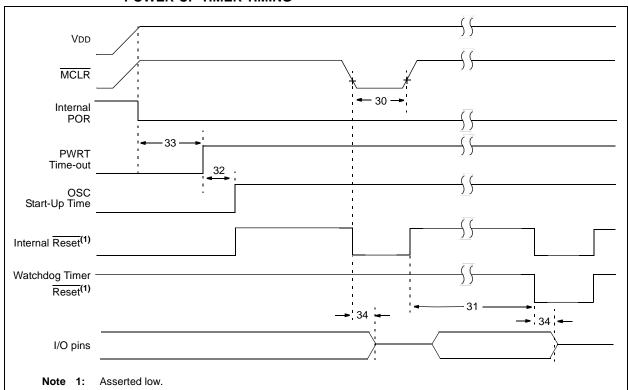

# FIGURE 15-6: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER TIMING

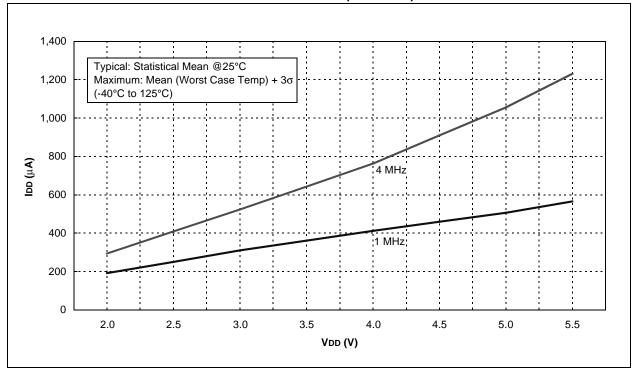

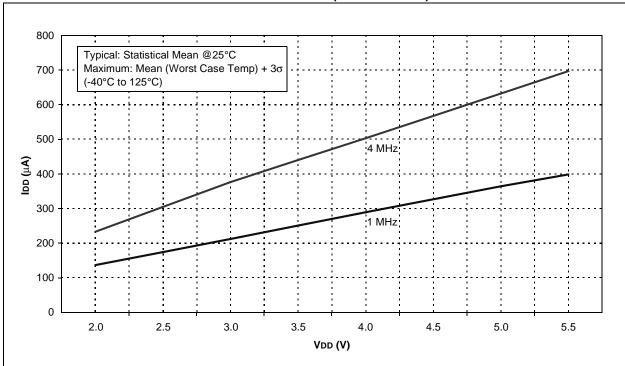

FIGURE 16-7: TYPICAL IDD vs. VDD OVER Fosc (EXTRC MODE)

© 2007 Microchip Technology Inc.

# APPENDIX A: DATA SHEET REVISION HISTORY

#### **Revision A**

This is a new data sheet.

# **Revision B**

Rewrites of the Oscillator and Special Features of the CPU Sections. General corrections to Figures and formatting.

# **Revision C**

# **Revision D**

Added Characterization Data. Updated Electrical Specifications. Incorporated Golden Chapter Sections for the following:

- Section 3.0 "Oscillator Module (With Fail-Safe Clock Monitor)"

- Section 5.0 "Timer0 Module"

- Section 6.0 "Timer1 Module with Gate Control"

- Section 7.0 "Timer2 Module"

- Section 8.0 "Comparator Module"

- Section 9.0 "Analog-to-Digital Converter (ADC) Module"

- Section 11.0 "Enhanced Capture/Compare/PWM (With Auto-Shutdown and Dead Band) Module"

# **Revision E**

Updated Package Drawings; Replace PICmicro with PIC.

# Revision F (03/2007)

Replaced Package Drawings (Rev. AM); Replaced Development Support Section.

# APPENDIX B: MIGRATING FROM OTHER PIC® DEVICES

This discusses some of the issues in migrating from other PIC devices to the PIC16F6XX Family of devices.

# B.1 PIC16F676 to PIC16F684

#### TABLE B-1: FEATURE COMPARISON

| Feature                               | PIC16F676     | PIC16F684            |

|---------------------------------------|---------------|----------------------|

| Max Operating<br>Speed                | 20 MHz        | 20 MHz               |

| Max Program<br>Memory (Words)         | 1024          | 2048                 |

| SRAM (bytes)                          | 64            | 128                  |

| A/D Resolution                        | 10-bit        | 10-bit               |

| Data EEPROM<br>(Bytes)                | 128           | 256                  |

| Timers (8/16-bit)                     | 1/1           | 2/1                  |

| Oscillator Modes                      | 8             | 8                    |

| Brown-out Reset                       | Y             | Y                    |

| Internal Pull-ups                     | RA0/1/2/4/5   | RA0/1/2/4/5,<br>MCLR |

| Interrupt-on-change                   | RA0/1/2/3/4/5 | RA0/1/2/3/4/5        |

| Comparator                            | 1             | 2                    |

| ECCP                                  | N             | Y                    |

| Ultra Low-Power<br>Wake-Up            | N             | Y                    |

| Extended WDT                          | N             | Y                    |

| Software Control<br>Option of WDT/BOR | N             | Y                    |

| INTOSC<br>Frequencies                 | 4 MHz         | 32 kHz-<br>8 MHz     |

| Clock Switching                       | N             | Y                    |

Note: This device has been designed to perform to the parameters of its data sheet. It has been tested to an electrical specification designed to determine its conformance with these parameters. Due to process differences in the manufacture of this device, this device may have different performance characteristics than its earlier version. These differences may cause this device to perform differently in your application than the earlier version of this device.