# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | PIC                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 20MHz                                                                   |

| Connectivity               | -                                                                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                   |

| Number of I/O              | 12                                                                      |

| Program Memory Size        | 3.5KB (2K x 14)                                                         |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 256 x 8                                                                 |

| RAM Size                   | 128 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                               |

| Data Converters            | A/D 8x10b                                                               |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Through Hole                                                            |

| Package / Case             | 14-DIP (0.300", 7.62mm)                                                 |

| Supplier Device Package    | 14-PDIP                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f684-i-p |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

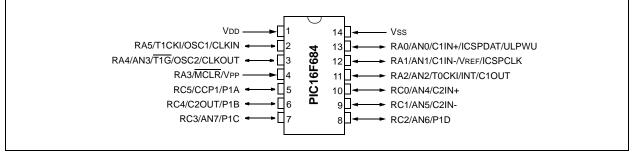

## 14-Pin Diagram (PDIP, SOIC, TSSOP)

TABLE 1: DUAL IN-LINE PIN SUMMARY

| I/O                | Pin | Analog   | Comparators | Timer | ССР      | Interrupts | Pull-ups | Basic         |

|--------------------|-----|----------|-------------|-------|----------|------------|----------|---------------|

| RA0                | 13  | AN0      | C1IN+       | —     | —        | IOC        | Y        | ICSPDAT/ULPWU |

| RA1                | 12  | AN1/VREF | C1IN-       | —     | —        | IOC        | Y        | ICSPCLK       |

| RA2                | 11  | AN2      | C1OUT       | T0CKI | —        | INT/IOC    | Y        | —             |

| RA3 <sup>(1)</sup> | 4   | _        | _           | _     | _        | IOC        | Y(2)     | MCLR/Vpp      |

| RA4                | 3   | AN3      | —           | T1G   | —        | IOC        | Y        | OSC2/CLKOUT   |

| RA5                | 2   |          | —           | T1CKI | —        | IOC        | Y        | OSC1/CLKIN    |

| RC0                | 10  | AN4      | C2IN+       | _     | —        | —          | —        | —             |

| RC1                | 9   | AN5      | C2IN-       | _     | —        | —          | —        | —             |

| RC2                | 8   | AN6      | —           | _     | P1D      | —          | —        | —             |

| RC3                | 7   | AN7      | —           | _     | P1C      | —          | —        | —             |

| RC4                | 6   | —        | C2OUT       | —     | P1B      | —          | —        | —             |

| RC5                | 5   | _        | —           | _     | CCP1/P1A |            | —        |               |

| —                  | 1   | _        | _           | _     | _        |            | —        | Vdd           |

|                    | 14  | _        | —           | _     | —        | _          | _        | Vss           |

Note 1: Input only.

**2:** Only when pin is configured for external  $\overline{MCLR}$ .

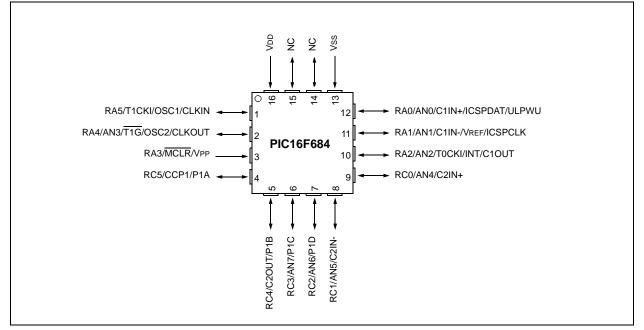

### 16-Pin Diagram (QFN)

#### TABLE 2: QFN PIN SUMMARY

| I/O                | Pin | Analog   | Comparators | Timers | ССР      | Interrupts | Pull-ups | Basic         |

|--------------------|-----|----------|-------------|--------|----------|------------|----------|---------------|

| RA0                | 12  | AN0      | C1IN+       |        | _        | IOC        | Y        | ICSPDAT/ULPWU |

| RA1                | 11  | AN1/VREF | C1IN-       | —      |          | IOC        | Y        | ICSPCLK       |

| RA2                | 10  | AN2      | C1OUT       | T0CKI  | —        | INT/IOC    | Y        | —             |

| RA3 <sup>(1)</sup> | 3   | _        | —           | _      |          | IOC        | Y(2)     | MCLR/Vpp      |

| RA4                | 2   | AN3      | —           | T1G    | —        | IOC        | Y        | OSC2/CLKOUT   |

| RA5                | 1   |          | —           | T1CKI  | _        | IOC        | Y        | OSC1/CLKIN    |

| RC0                | 9   | AN4      | C2IN+       | _      | —        | _          | —        | —             |

| RC1                | 8   | AN5      | C2IN-       |        | _        | _          | —        | —             |

| RC2                | 7   | AN6      | —           | _      | P1D      | _          | —        | —             |

| RC3                | 6   | AN7      | —           | _      | P1C      |            | —        | —             |

| RC4                | 5   | —        | C2OUT       |        | P1B      | —          | —        | —             |

| RC5                | 4   | _        | —           | _      | CCP1/P1A | _          | —        | —             |

|                    | 16  | _        | —           |        | _        | _          | —        | Vdd           |

|                    | 13  | _        |             |        | _        | _          | _        | Vss           |

Note 1: Input only.

2: Only when pin is configured for external MCLR.

#### 2.2.1 GENERAL PURPOSE REGISTER FILE

The register file is organized as 128 x 8 in the PIC16F684. Each register is accessed, either directly or indirectly, through the File Select Register (FSR) (see Section 2.4 "Indirect Addressing, INDF and FSR Registers").

#### 2.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers are registers used by the CPU and peripheral functions for controlling the desired operation of the device (see Table 2-1). These registers are static RAM.

The special registers can be classified into two sets: core and peripheral. The Special Function Registers associated with the "core" are described in this section. Those related to the operation of the peripheral features are described in the section of that peripheral feature.

#### FIGURE 2-2: DATA MEMORY MAP OF THE PIC16F684

| Indirect Addr. <sup>(1)</sup> 00h           TMR0         01h           PCL         02h           STATUS         03h           FSR         04h           PORTA         05h           OPRTC         07h           OPNTC         07h           OPNTC         08h           PORTC         08h           PORTC         08h           PORTC         08h           INTCON         0Bh           PIR1         0Ch           TMR1L         0Eh           TMR1H         0Fh           T1CON         10h           TMR2         11h           T2CON         12h           CCPR1L         13h           CCPR1H         14h           CCPAS         17h           WDTCON         18h           CMCON1         1Ah           CMCON1         1Ah           MDRON1         1Ch           ADRESH         1Eh           ADCON0         1Fh           Qub         20h | Indirect Addr. <sup>(1)</sup><br>OPTION_REG<br>PCL<br>STATUS<br>FSR<br>TRISA<br>TRISA<br>PCLATH<br>INTCON<br>PIE1<br>PCON<br>OSCCON<br>OSCCON<br>OSCTUNE<br>ANSEL<br>PR2<br>WPUA<br>IOCA<br>VRCON<br>EEDAT<br>EEADR<br>EECON1 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| STATUS         03h           FSR         04h           PORTA         05h           06h         06h           PORTC         07h           08h         09h           PCLATH         0Ah           INTCON         0Bh           PIR1         0Ch           TMR1L         0Eh           TMR1H         0Fh           T1CON         10h           TMR2         11h           T2CON         12h           CCPR1L         13h           CCPR1H         14h           CCPR1H         16h           ECCPAS         17h           WDTCON         18h           CMCON0         19h           CMCON1         1Ah           1Bh         1Ch           ADRESH         1Eh           ADCON0         1Fh                                                                                                                                                            | STATUS<br>FSR<br>TRISA<br>TRISA<br>PCLATH<br>INTCON<br>PIE1<br>PCON<br>OSCCON<br>OSCTUNE<br>ANSEL<br>PR2<br>WPUA<br>IOCA<br>VRCON<br>EEDAT<br>EEADR                                                                           |

| FSR         04h           PORTA         05h           06h         06h           PORTC         07h           08h         09h           PCLATH         0Ah           INTCON         0Bh           PIR1         0Ch           TMR1L         0Eh           TMR1H         0Fh           T1CON         10h           TMR2         11h           T2CON         12h           CCPR1L         13h           CCPR1H         14h           CCPR1CON         15h           PWM1CON         16h           ECCPAS         17h           WDTCON         18h           CMCON0         19h           CMCON1         1Ah           Dh         1Ch           ADRESH         1Eh           ADCON0         1Fh                                                                                                                                                          | FSR<br>TRISA<br>TRISA<br>PCLATH<br>INTCON<br>PIE1<br>PCON<br>OSCCON<br>OSCCON<br>OSCTUNE<br>ANSEL<br>PR2<br>WPUA<br>IOCA<br>IOCA                                                                                              |

| FSR         04h           PORTA         05h           06h         06h           PORTC         07h           08h         09h           PCLATH         0Ah           INTCON         0Bh           PIR1         0Ch           TMR1L         0Eh           TMR1H         0Fh           T1CON         10h           TMR2         11h           T2CON         12h           CCPR1L         13h           CCPR1H         14h           CCPR1H         16h           ECCPAS         17h           WDTCON         18h           CMCON0         19h           CMCON1         1Ah           Dh         1Ch           ADRESH         1Eh           ADCON0         1Fh                                                                                                                                                                                          | TRISA<br>TRISC<br>PCLATH<br>INTCON<br>PIE1<br>PCON<br>OSCCON<br>OSCTUNE<br>ANSEL<br>PR2<br>WPUA<br>IOCA<br>IOCA                                                                                                               |

| PORTA         05h           06h         06h           PORTC         07h           08h         09h           PCLATH         0Ah           INTCON         0Bh           PIR1         0Ch           TMR1L         0Eh           TMR1H         0Fh           T1CON         10h           TMR2         11h           T2CON         12h           CCPR1L         13h           CCPR1H         14h           CCPR1H         16h           ECCPAS         17h           WDTCON         18h           CMCON0         19h           CMCON1         1Ah           Dh         1Ch           ADRESH         1Eh           ADCON0         1Fh                                                                                                                                                                                                                    | TRISC  PCLATH INTCON PIE1  PCON OSCCON OSCCUNE ANSEL PR2  WPUA IOCA  VRCON EEDAT EEADR                                                                                                                                        |

| 06h           PORTC         07h           08h         09h           PCLATH         0Ah           INTCON         0Bh           PIR1         0Ch           0Dh         0Dh           TMR1L         0Eh           TMR1H         0Fh           T1CON         10h           TMR2         11h           T2CON         12h           CCPR1L         13h           CCPR1H         14h           CCPR1H         16h           ECCPAS         17h           WDTCON         18h           CMCON0         19h           CMCON1         1Ah           1Dh         ADRESH           ADCON0         1Fh           20h         1                                                                                                                                                                                                                                   | PCLATH<br>INTCON<br>PIE1<br>PCON<br>OSCCON<br>OSCTUNE<br>ANSEL<br>PR2<br>WPUA<br>IOCA<br>VRCON<br>EEDAT<br>EEADR                                                                                                              |

| PORTC         07h           08h         09h           PCLATH         0Ah           INTCON         0Bh           PIR1         0Ch           0Dh         0Dh           TMR1L         0Eh           TMR1L         0Fh           T1CON         10h           TMR2         11h           T2CON         12h           CCPR1L         13h           CCPR1H         14h           CCPR1H         16h           ECCPAS         17h           WDTCON         18h           CMCON1         1Ah           Bh         1Ch           ADRESH         1Eh           ADCON0         1Fh                                                                                                                                                                                                                                                                             | PCLATH<br>INTCON<br>PIE1<br>PCON<br>OSCCON<br>OSCTUNE<br>ANSEL<br>PR2<br>WPUA<br>IOCA<br>VRCON<br>EEDAT<br>EEADR                                                                                                              |

| 08h           09h           PCLATH         0Ah           INTCON         0Bh           PIR1         0Ch           0Dh         0Dh           TMR1L         0Eh           TMR1H         0Fh           T1CON         10h           TMR2         11h           T2CON         12h           CCPR1L         13h           CCPR1H         14h           CCPR1H         16h           ECCPAS         17h           WDTCON         18h           CMCON1         1Ah           Bh         1Ch           Dh         1Dh           ADRESH         1Eh           ADCON0         1Fh                                                                                                                                                                                                                                                                              | INTCON<br>PIE1<br>PCON<br>OSCCON<br>OSCTUNE<br>ANSEL<br>PR2<br>WPUA<br>IOCA<br>VRCON<br>EEDAT<br>EEADR                                                                                                                        |

| 09h           PCLATH         0Ah           INTCON         0Bh           PIR1         0Ch           0Dh         0Dh           TMR1L         0Eh           TMR1H         0Fh           T1CON         10h           TMR2         11h           T2CON         12h           CCPR1L         13h           CCPR1H         14h           CCPR1H         16h           ECCPAS         17h           WDTCON         18h           CMCON1         1Ah           1Bh         1Ch           1Dh         ADRESH           ADCON0         1Fh                                                                                                                                                                                                                                                                                                                    | INTCON<br>PIE1<br>PCON<br>OSCCON<br>OSCTUNE<br>ANSEL<br>PR2<br>WPUA<br>IOCA<br>VRCON<br>EEDAT<br>EEADR                                                                                                                        |

| PCLATH         OAh           INTCON         0Bh           PIR1         0Ch           0Dh         0Dh           TMR1L         0Eh           TMR1H         0Fh           T1CON         10h           TMR2         11h           T2CON         12h           CCPR1L         13h           CCPR1H         14h           CCP1CON         15h           PWM1CON         16h           ECCPAS         17h           WDTCON         18h           CMCON1         1Ah           1Bh         1Ch           ADRESH         1Eh           ADCON0         1Fh                                                                                                                                                                                                                                                                                                   | INTCON<br>PIE1<br>PCON<br>OSCCON<br>OSCTUNE<br>ANSEL<br>PR2<br>WPUA<br>IOCA<br>VRCON<br>EEDAT<br>EEADR                                                                                                                        |

| INTCON         0Bh           PIR1         0Ch           0Dh         0Dh           TMR1L         0Eh           TMR1H         0Fh           T1CON         10h           TMR2         11h           T2CON         12h           CCPR1L         13h           CCPR1H         14h           CCP1CON         15h           PWM1CON         16h           ECCPAS         17h           WDTCON         18h           CMCON1         1Ah           1Bh         1Ch           ADRESH         1Eh           ADCON0         1Fh                                                                                                                                                                                                                                                                                                                                | INTCON<br>PIE1<br>PCON<br>OSCCON<br>OSCTUNE<br>ANSEL<br>PR2<br>WPUA<br>IOCA<br>VRCON<br>EEDAT<br>EEADR                                                                                                                        |

| PIR1         OCh           0Dh         0Dh           TMR1L         0Eh           TMR1H         0Fh           T1CON         10h           TMR2         11h           T2CON         12h           CCPR1L         13h           CCPR1H         14h           CCP1CON         15h           PWM1CON         16h           ECCPAS         17h           WDTCON         18h           CMCON1         1Ah           1Bh         1Ch           ADRESH         1Eh           ADCON0         1Fh                                                                                                                                                                                                                                                                                                                                                             | PIE1<br>PCON<br>OSCCON<br>OSCTUNE<br>ANSEL<br>PR2<br>WPUA<br>IOCA<br>IOCA<br>VRCON<br>EEDAT<br>EEADR                                                                                                                          |

| ODh           TMR1L         0Eh           TMR1H         0Fh           T1CON         10h           TMR2         11h           T2CON         12h           CCPR1L         13h           CCPR1H         14h           CCPR1H         15h           PWM1CON         16h           ECCPAS         17h           WDTCON         18h           CMCON1         1Ah           1Bh         1Ch           ADRESH         1Eh           ADCON0         1Fh                                                                                                                                                                                                                                                                                                                                                                                                     | PCON<br>OSCCON<br>OSCTUNE<br>ANSEL<br>PR2<br>WPUA<br>IOCA<br>IOCA<br>VRCON<br>EEDAT<br>EEADR                                                                                                                                  |

| TMR1L         0Eh           TMR1H         0Fh           T1CON         10h           TMR2         11h           T2CON         12h           CCPR1L         13h           CCPR1H         14h           CCP1CON         15h           PWM1CON         16h           ECCPAS         17h           WDTCON         18h           CMCON0         19h           CMCON1         1Ah           Bh         1Ch           ADRESH         1Eh           ADCON0         1Fh                                                                                                                                                                                                                                                                                                                                                                                      | OSCCON<br>OSCTUNE<br>ANSEL<br>PR2<br>WPUA<br>IOCA<br>VRCON<br>EEDAT<br>EEADR                                                                                                                                                  |

| TMR1H         OFh           T1CON         10h           TMR2         11h           T2CON         12h           CCPR1L         13h           CCPR1H         14h           CCP1CON         15h           PWM1CON         16h           ECCPAS         17h           WDTCON         18h           CMCON0         19h           CMCON1         1Ah           Bh         1Ch           ADRESH         1Eh           ADCON0         1Fh           20h         15h                                                                                                                                                                                                                                                                                                                                                                                        | OSCCON<br>OSCTUNE<br>ANSEL<br>PR2<br>WPUA<br>IOCA<br>VRCON<br>EEDAT<br>EEADR                                                                                                                                                  |

| T1CON         10h           TMR2         11h           T2CON         12h           CCPR1L         13h           CCPR1H         14h           CCP1CON         15h           PWM1CON         16h           ECCPAS         17h           WDTCON         18h           CMCON0         19h           CMCON1         1Ah           Bh         1Ch           DDh         ADRESH           ADCON0         1Fh           20h         15h                                                                                                                                                                                                                                                                                                                                                                                                                    | OSCTUNE<br>ANSEL<br>PR2<br>WPUA<br>IOCA<br>VRCON<br>EEDAT<br>EEADR                                                                                                                                                            |

| TMR2         11h           T2CON         12h           CCPR1L         13h           CCPR1H         14h           CCP1CON         15h           PWM1CON         16h           ECCPAS         17h           WDTCON         18h           CMCON0         19h           CMCON1         1Ah           1Bh         1Ch           1Dh         ADRESH           ADCON0         1Fh           20h         1                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ANSEL<br>PR2<br>WPUA<br>IOCA<br>VRCON<br>EEDAT<br>EEADR                                                                                                                                                                       |

| T2CON         12h           CCPR1L         13h           CCPR1H         14h           CCP1CON         15h           PWM1CON         16h           ECCPAS         17h           WDTCON         18h           CMCON0         19h           CMCON1         1Ah           1Bh         1Ch           1Dh         ADRESH           ADCON0         1Fh           20h         1                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | PR2<br>WPUA<br>IOCA<br>VRCON<br>EEDAT<br>EEADR                                                                                                                                                                                |

| CCPR1L         13h           CCPR1H         14h           CCP1CON         15h           PWM1CON         16h           ECCPAS         17h           WDTCON         18h           CMCON0         19h           CMCON1         1Ah           1Bh         1Ch           1Dh         ADRESH           ADCON0         1Fh           20h         1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | WPUA<br>IOCA<br>VRCON<br>EEDAT<br>EEADR                                                                                                                                                                                       |

| CCPR1H         14h           CCP1CON         15h           PWM1CON         16h           ECCPAS         17h           WDTCON         18h           CMCON0         19h           CMCON1         1Ah           1Bh         1Ch           1Dh         1Dh           ADRESH         1Eh           ADCON0         1Fh                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | IOCA<br>VRCON<br>EEDAT<br>EEADR                                                                                                                                                                                               |

| CCP1CON         15h           PWM1CON         16h           ECCPAS         17h           WDTCON         18h           CMCON0         19h           CMCON1         1Ah           1Bh         1Ch           ADRESH         1Eh           ADCON0         1Fh           20h         1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | IOCA<br>VRCON<br>EEDAT<br>EEADR                                                                                                                                                                                               |

| PWM1CON         16h           ECCPAS         17h           WDTCON         18h           CMCON0         19h           CMCON1         1Ah           Bh         1Ch           JDh         1Dh           ADRESH         1Fh           20h         20h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | IOCA<br>VRCON<br>EEDAT<br>EEADR                                                                                                                                                                                               |

| ECCPAS17hWDTCON18hCMCON019hCMCON11Ah1Bh1Ch1Dh1DhADRESH1EhADCON01Fh20h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | VRCON<br>EEDAT<br>EEADR                                                                                                                                                                                                       |

| WDTCON18hCMCON019hCMCON11Ah1Bh1Ch1Dh1DhADRESH1EhADCON01Fh20h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | EEDAT<br>EEADR                                                                                                                                                                                                                |

| CMCON019hCMCON11Ah1Bh1Ch1DhADRESH1EhADCON01Fh20h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | EEDAT<br>EEADR                                                                                                                                                                                                                |

| CMCON11Ah1Bh1Ch1DhADRESHADCON01Fh20h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | EEDAT<br>EEADR                                                                                                                                                                                                                |

| ADRESH 15h<br>ADCON0 15h<br>20h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | EEADR                                                                                                                                                                                                                         |

| 1Ch1DhADRESH1EhADCON01Fh20h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                               |

| ADRESH 1Dh<br>ADCON0 1Fh<br>20h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | EECONT                                                                                                                                                                                                                        |

| ADRESH 1Eh<br>ADCON0 1Fh<br>20h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                               |

| ADCON0 1Fh<br>20h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | EECON2 <sup>(1)</sup>                                                                                                                                                                                                         |

| 20h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ADRESL                                                                                                                                                                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ADCON1<br>General                                                                                                                                                                                                             |

| General                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Purpose                                                                                                                                                                                                                       |

| General                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Registers                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 32 Bytes                                                                                                                                                                                                                      |

| Purpose                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                               |

| Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                               |

| 96 Bytes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                               |

| 00 29100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                               |

| 6Fh                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                               |

| 70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Accesses 70h-7Fh                                                                                                                                                                                                              |

| Bank 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Bank 1                                                                                                                                                                                                                        |

#### 2.2.2.1 STATUS Register

The STATUS register, shown in Register 2-1, contains:

- the arithmetic status of the ALU

- · the Reset status

- the bank select bits for data memory (SRAM)

The STATUS register can be the destination for any instruction, like any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

For example, CLRF STATUS, will clear the upper three bits and set the Z bit. This leaves the STATUS register as `000u uluu' (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS register, because these instructions do not affect any Status bits. For other instructions not affecting any Status bits, see Section 13.0 "Instruction Set Summary".

- Note 1: Bits IRP and RP1 of the STATUS register are not used by the PIC16F684 and should be maintained as clear. Use of these bits is not recommended, since this may affect upward compatibility with future products.

- 2: The <u>C</u> and <u>DC</u> bits operate as a Borrow and <u>Digit</u> Borrow out bit, respectively, in subtraction. See the SUBLW and SUBWF instructions for examples.

#### REGISTER 2-1: STATUS: STATUS REGISTER

| Reserved | Reserved | R/W-0 | R-1 | R-1 | R/W-x | R/W-x | R/W-x |

|----------|----------|-------|-----|-----|-------|-------|-------|

| IRP      | RP1      | RP0   | TO  | PD  | Z     | DC    | С     |

| bit 7    |          |       |     |     |       |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7   | IRP: This bit is reserved and should be maintained as '0'                                                          |

|---------|--------------------------------------------------------------------------------------------------------------------|

| bit 6   | RP1: This bit is reserved and should be maintained as '0'                                                          |

| bit 5   | RP0: Register Bank Select bit (used for direct addressing)                                                         |

|         | 1 = Bank 1 (80h – FFh)                                                                                             |

|         | 0 = Bank 0 (00h - 7Fh)                                                                                             |

| bit 4   | TO: Time-out bit                                                                                                   |

|         | 1 = After power-up, CLRWDT instruction or SLEEP instruction                                                        |

|         | 0 = A WDT time-out occurred                                                                                        |

| bit 3   | PD: Power-down bit                                                                                                 |

|         | 1 = After power-up or by the CLRWDT instruction                                                                    |

|         | 0 = By execution of the SLEEP instruction                                                                          |

| bit 2   | Z: Zero bit                                                                                                        |

|         | 1 = The result of an arithmetic or logic operation is zero                                                         |

|         | 0 = The result of an arithmetic or logic operation is not zero                                                     |

| bit 1   | <b>DC:</b> Digit Carry/Borrow bit (ADDWF, ADDLW, SUBLW, SUBWF instructions), For Borrow, the polarity is reversed. |

|         | 1 = A carry-out from the 4th low-order bit of the result occurred                                                  |

|         | 0 = No carry-out from the 4th low-order bit of the result                                                          |

| bit 0   | C: Carry/Borrow bit <sup>(1)</sup> (ADDWF, ADDLW, SUBLW, SUBWF instructions)                                       |

|         | 1 = A carry-out from the Most Significant bit of the result occurred                                               |

|         | 0 = No carry-out from the Most Significant bit of the result occurred                                              |

| Note 1: | For Borrow, the polarity is reversed. A subtraction is executed by adding the two's complement of the sec-         |

**Note 1:** For Borrow, the polarity is reversed. A subtraction is executed by adding the two's complement of the second operand. For rotate (RRF, RLF) instructions, this bit is loaded with either the high-order or low-order bit of the source register.

## 4.2.5 PIN DESCRIPTIONS AND DIAGRAMS

Each PORTA pin is multiplexed with other functions. The pins and their combined functions are briefly described here. For specific information about individual functions such as the Comparator or the ADC, refer to the appropriate section in this data sheet.

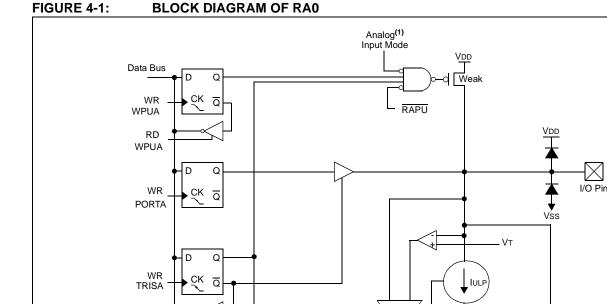

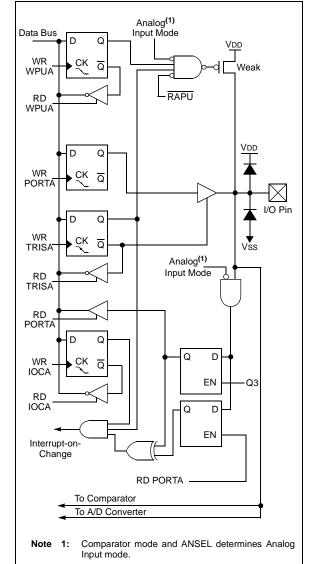

#### 4.2.5.1 RA0/AN0/C1IN+/ICSPDAT/ULPWU

Figure 4-1 shows the diagram for this pin. The RA0 pin is configurable to function as one of the following:

- a general purpose I/O

- an analog input for the ADC

- an analog non-inverting input to the comparator

RD

RD PORTA

WR

IOCA

RD IOCA

Interrupt-on-Change Q

Q

TRISA

- In-Circuit Serial Programming data

- an analog input for the Ultra Low-Power Wake-Up

Analog(1)

Input Mode

Q

Ω

**RD PORTA**

To Comparator To A/D Converter

Note 1: Comparator mode and ANSEL determines Analog Input mode.

Ч

Q3

D

D

ΕN

ΕN

#### 4.2.5.2 RA1/AN1/C1IN-/VREF/ICSPCLK

Figure 4-2 shows the diagram for this pin. The RA1 pin is configurable to function as one of the following:

- a general purpose I/O

- an analog input for the ADC

- an analog inverting input to the comparator

- a voltage reference input for the ADC

- In-Circuit Serial Programming clock

Vss

ULPWUE

## PIC16F684

#### FIGURE 4-2:

#### BLOCK DIAGRAM OF RA1

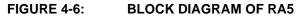

#### 4.2.5.3 RA2/AN2/T0CKI/INT/C1OUT

Figure 4-3 shows the diagram for this pin. The RA2 pin is configurable to function as one of the following:

- a general purpose I/O

- an analog input for the ADC

- the clock input for TMR0

- an external edge triggered interrupt

- a digital output from Comparator 1

#### BLOCK DIAGRAM OF RA2

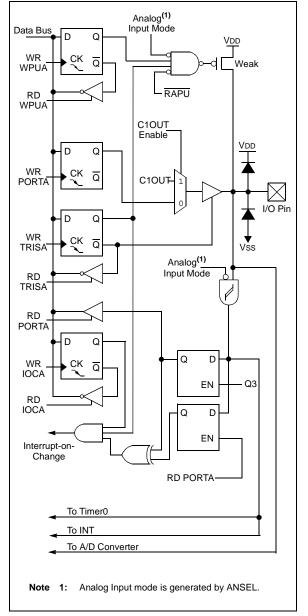

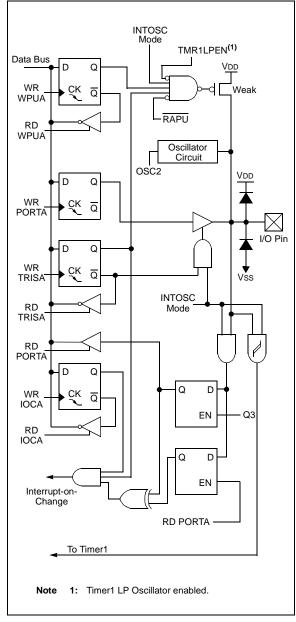

#### 4.2.5.6 RA5/T1CKI/OSC1/CLKIN

Figure 4-6 shows the diagram for this pin. The RA5 pin is configurable to function as one of the following:

- a general purpose I/O

- a Timer1 clock input

- a crystal/resonator connection

- · a clock input

#### 8.8 **Comparator C2 Gating Timer1**

This feature can be used to time the duration or interval of analog events. Clearing the T1GSS bit of the CMCON1 register will enable Timer1 to increment based on the output of Comparator C2. This requires that Timer1 is on and gating is enabled. See Section 6.0 "Timer1 Module with Gate Control" for details.

It is recommended to synchronize Comparator C2 with Timer1 by setting the C2SYNC bit when the comparator is used as the Timer1 gate source. This ensures Timer1 does not miss an increment if the comparator changes during an increment.

#### 8.9 Synchronizing Comparator C2 **Output to Timer1**

The output of Comparator C2 can be synchronized with Timer1 by setting the C2SYNC bit of the CMCON1 register. When enabled, the comparator output is latched on the falling edge of the Timer1 clock source. If a prescaler is used with Timer1, the comparator output is latched after the prescaling function. To prevent a race condition, the comparator output is latched on the falling edge of the Timer1 clock source and Timer1 increments on the rising edge of its clock source. Reference the comparator block diagrams (Figure 8-2 and Figure 8-3) and the Timer1 Block Diagram (Figure 6-1) for more information.

#### **REGISTER 8-2: CMCON1: COMPARATOR CONFIGURATION REGISTER**

| U-0                                                     | U-0 | U-0                                                   | U-0 | U-0             | U-0  | R/W-1 | R/W-0  |

|---------------------------------------------------------|-----|-------------------------------------------------------|-----|-----------------|------|-------|--------|

| —                                                       | _   | —                                                     | —   | —               | —    | T1GSS | C2SYNC |

| bit 7                                                   |     |                                                       |     |                 | •    |       | bit 0  |

|                                                         |     |                                                       |     |                 |      |       |        |

| Legend:                                                 |     |                                                       |     |                 |      |       |        |

| R = Readable b                                          | oit | t W = Writable bit U = Unimplemented bit, read as '0' |     |                 |      |       |        |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared |     |                                                       |     | x = Bit is unki | nown |       |        |

| bit 7-2 | Unimplemented: Read as '0' |  |

|---------|----------------------------|--|

|         |                            |  |

```

bit 1

T1GSS: Timer1 Gate Source Select bit<sup>(1)</sup>

```

1 = Timer1 gate source is  $\overline{T1G}$  pin (pin should be configured as digital input)

0 = Timer1 gate source is Comparator C2 output

bit 0 C2SYNC: Comparator C2 Output Synchronization bit<sup>(2)</sup>

- 1 = Output is synchronized with falling edge of Timer1 clock

- 0 = Output is asynchronous

- Note 1: Refer to Section 6.6 "Timer1 Gate".

- 2: Refer to Figure 8-3.

### 10.5 Protection Against Spurious Write

There are conditions when the user may not want to write to the data EEPROM memory. To protect against spurious EEPROM writes, various mechanisms have been built in. On power-up, WREN is cleared. Also, the Power-up Timer (64 ms duration) prevents EEPROM write.

The write initiate sequence and the WREN bit together help prevent an accidental write during:

- Brown-out

- Power Glitch

- Software Malfunction

#### 10.6 Data EEPROM Operation During Code-Protect

Data memory can be code-protected by programming the  $\overline{CPD}$  bit in the Configuration Word register (Register 12-1) to '0'.

When the data memory is code-protected, the CPU is able to read and write data to the data EEPROM. It is recommended to code-protect the program memory when code-protecting data memory. This prevents anyone from programming zeroes over the existing code (which will execute as NOPS) to reach an added routine, programmed in unused program memory, which outputs the contents of data memory. Programming unused locations in program memory to '0' will also help prevent data memory code protection from becoming breached.

| Name                  | Bit 7                                           | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR, BOR | Value on<br>all other<br>Resets |

|-----------------------|-------------------------------------------------|--------|--------|--------|--------|--------|--------|--------|-----------------------|---------------------------------|

| INTCON                | GIE                                             | PEIE   | T0IE   | INTE   | RAIE   | T0IF   | INTF   | RAIF   | 0000 0000             | 0000 0000                       |

| PIR1                  | EEIF                                            | ADIF   | CCP1IF | C2IF   | C1IF   | OSFIF  | TMR2IF | TMR1IF | 0000 0000             | 0000 0000                       |

| PIE1                  | EEIE                                            | ADIE   | CCP1IE | C2IE   | C1IE   | OSFIE  | TMR2IE | TMR1IE | 0000 0000             | 0000 0000                       |

| EEDAT                 | EEDAT7                                          | EEDAT6 | EEDAT5 | EEDAT4 | EEDAT3 | EEDAT2 | EEDAT1 | EEDAT0 | 0000 0000             | 0000 0000                       |

| EEADR                 | EEADR7                                          | EEADR6 | EEADR5 | EEADR4 | EEADR3 | EEADR2 | EEADR1 | EEADR0 | 0000 0000             | 0000 0000                       |

| EECON1                | _                                               | _      | _      | _      | WRERR  | WREN   | WR     | RD     | x000                  | q000                            |

| EECON2 <sup>(1)</sup> | EECON2 <sup>(1)</sup> EEPROM Control Register 2 |        |        |        |        |        |        |        |                       |                                 |

#### TABLE 10-1: SUMMARY OF ASSOCIATED DATA EEPROM REGISTERS

Legend: x = unknown, u = unchanged, - = unimplemented read as '0', q = value depends upon condition. Shaded cells are not used by the Data EEPROM module.

Note 1: EECON2 is not a physical register.

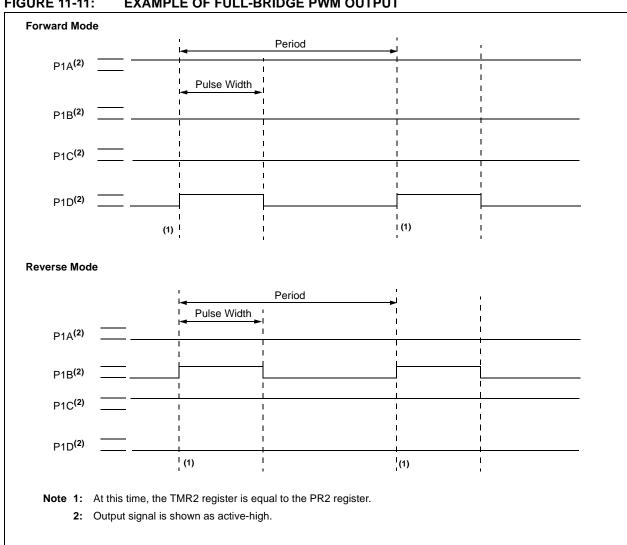

#### 11.3.1 PWM PERIOD

The PWM period is specified by the PR2 register of Timer2. The PWM period can be calculated using the formula of Equation 11-1.

### EQUATION 11-1: PWM PERIOD

$PWM Period = [(PR2) + 1] \bullet 4 \bullet Tosc \bullet$ (TMR2 Prescale Value)

When TMR2 is equal to PR2, the following three events occur on the next increment cycle:

- TMR2 is cleared

- The CCP1 pin is set. (Exception: If the PWM duty cycle = 0%, the pin will not be set.)

- The PWM duty cycle is latched from CCPR1L into CCPR1H.

| Note: | The Timer2 postscaler (see Section 7.1 |

|-------|----------------------------------------|

|       | "Timer2 Operation") is not used in the |

|       | determination of the PWM frequency.    |

#### 11.3.2 PWM DUTY CYCLE

The PWM duty cycle is specified by writing a 10-bit value to multiple registers: CCPR1L register and CCP1<1:0> bits of the CCP1CON register. The CCPR1L contains the eight MSbs and the CCP1<1:0> bits of the CCP1CON register contain the two LSbs. CCPR1L and CCP1<1:0> bits of the CCP1CON register contain the two LSbs. CCPR1L and CCP1<1:0> bits of the CCP1CON register can be written to at any time. The duty cycle value is not latched into CCPR1H until after the period completes (i.e., a match between PR2 and TMR2 registers occurs). While using the PWM, the CCPR1H register is read-only.

Equation 11-2 is used to calculate the PWM pulse width.

Equation 11-3 is used to calculate the PWM duty cycle ratio.

#### EQUATION 11-2: PULSE WIDTH

$Pulse Width = (CCPR1L:CCP1CON < 5:4>) \bullet$

TOSC • (TMR2 Prescale Value)

## EQUATION 11-3: DUTY CYCLE RATIO

$$Duty Cycle Ratio = \frac{(CCPR1L:CCP1CON < 5:4>)}{4(PR2 + 1)}$$

The CCPR1H register and a 2-bit internal latch are used to double buffer the PWM duty cycle. This double buffering is essential for glitchless PWM operation.

The 8-bit timer TMR2 register is concatenated with either the 2-bit internal system clock (Fosc), or 2 bits of the prescaler, to create the 10-bit time base. The system clock is used if the Timer2 prescaler is set to 1:1.

When the 10-bit time base matches the CCPR1H and 2-bit latch, then the CCP1 pin is cleared (see Figure 11-3).

#### 11.3.3 PWM RESOLUTION

The resolution determines the number of available duty cycles for a given period. For example, a 10-bit resolution will result in 1024 discrete duty cycles, whereas an 8-bit resolution will result in 256 discrete duty cycles.

The maximum PWM resolution is 10 bits when PR2 is 255. The resolution is a function of the PR2 register value as shown by Equation 11-4.

#### EQUATION 11-4: PWM RESOLUTION

Resolution =

$$\frac{\log[4(PR2 + 1)]}{\log(2)}$$

bits

Note: If the pulse width value is greater than the period the assigned PWM pin(s) will remain unchanged.

#### TABLE 11-2: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 20 MHz)

| PWM Frequency             | 1.22 kHz | 4.88 kHz | 19.53 kHz | 78.12 kHz | 156.3 kHz | 208.3 kHz |

|---------------------------|----------|----------|-----------|-----------|-----------|-----------|

| Timer Prescale (1, 4, 16) | 16       | 4        | 1         | 1         | 1         | 1         |

| PR2 Value                 | 0xFF     | 0xFF     | 0xFF      | 0x3F      | 0x1F      | 0x17      |

| Maximum Resolution (bits) | 10       | 10       | 10        | 8         | 7         | 6.6       |

#### TABLE 11-3: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 8 MHz)

| PWM Frequency             | 1.22 kHz | 4.90 kHz | 19.61 kHz | 76.92 kHz | 153.85 kHz | 200.0 kHz |

|---------------------------|----------|----------|-----------|-----------|------------|-----------|

| Timer Prescale (1, 4, 16) | 16       | 4        | 1         | 1         | 1          | 1         |

| PR2 Value                 | 0x65     | 0x65     | 0x65      | 0x19      | 0x0C       | 0x09      |

| Maximum Resolution (bits) | 8        | 8        | 8         | 6         | 5          | 5         |

#### **EXAMPLE OF FULL-BRIDGE PWM OUTPUT** FIGURE 11-11:

#### 12.3.1 POWER-ON RESET (POR)

The on-chip POR circuit holds the chip in Reset until VDD has reached a high enough level for proper operation. To take advantage of the POR, simply connect the MCLR pin through a resistor to VDD. This will eliminate external RC components usually needed to create Power-on Reset. A maximum rise time for VDD is required. See **Section 15.0** "**Electrical Specifications**" for details. If the BOR is enabled, the maximum rise time specification does not apply. The BOR circuitry will keep the device in Reset until VDD reaches VBOR (see **Section 12.3.4** "**Brown-Out Reset (BOR)**").

Note: The POR circuit does not produce an internal Reset when VDD declines. To re-enable the POR, VDD must reach Vss for a minimum of 100 μs.

When the device starts normal operation (exits the Reset condition), device operating parameters (i.e., voltage, frequency, temperature, etc.) must be met to ensure proper operation. If these conditions are not met, the device must be held in Reset until the operating conditions are met.

For additional information, refer to Application Note AN607, *"Power-up Trouble Shooting"* (DS00607).

#### 12.3.2 MCLR

PIC16F684 has a noise filter in the  $\overline{\text{MCLR}}$  Reset path. The filter will detect and ignore small pulses.

$\underline{\text{It should}}$  be noted that a WDT Reset does not drive  $\overline{\text{MCLR}}$  pin low.

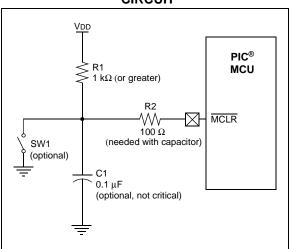

Voltages applied to the MCLR pin that exceed its specification can result in both MCLR Resets and excessive current beyond the device specification during the ESD event. For this reason, Microchip recommends that the MCLR pin no longer be tied directly to VDD. The use of an RC network, as shown in Figure 12-2, is suggested.

An internal  $\overline{\text{MCLR}}$  option is enabled by clearing the  $\overline{\text{MCLRE}}$  bit in the Configuration Word register. When  $\overline{\text{MCLRE}} = 0$ , the Reset signal to the chip is generated internally. When the  $\overline{\text{MCLRE}} = 1$ , the RA3/ $\overline{\text{MCLR}}$  pin becomes an external Reset input. In this mode, the RA3/ $\overline{\text{MCLR}}$  pin has a weak pull-up to VDD.

#### FIGURE 12-2: RECOMMENDED MCLR CIRCUIT

#### 12.3.3 POWER-UP TIMER (PWRT)

The Power-up Timer provides a fixed 64 ms (nominal) time-out on power-up only, from POR or Brown-out Reset. The Power-up Timer operates from the 31 kHz LFINTOSC oscillator. For more information, see **Section 3.5 "Internal Clock Modes"**. The chip is kept in Reset as long as PWRT is active. The PWRT delay allows the VDD to rise to an acceptable level. A Configuration bit, PWRTE, can disable (if set) or enable (if cleared or programmed) the Power-up Timer. The Power-up Timer should be enabled when Brown-out Reset is enabled, although it is not required.

The Power-up Timer delay will varies from chip-to-chip due to:

- VDD variation

- Temperature variation

- · Process variation

See DC parameters for details (Section 15.0 "Electrical Specifications").

**Note:** Voltage spikes below Vss at the  $\overline{\text{MCLR}}$  pin, inducing currents greater than 80 mA, may cause latch-up. Thus, a series resistor of 50-100  $\Omega$  should be used when applying a "low" level to the  $\overline{\text{MCLR}}$  pin, rather than pulling this pin directly to Vss.

| FIGURE 12-10: | WAKE-UP FROM SLEEP THROUGH INTERRUPT |

|---------------|--------------------------------------|

|               |                                      |

|                             | Q1 Q2 Q3 Q4       | Q1   Q2   Q3   Q4 | Q1                                    | Q1 Q2 Q3 Q4        | Q1 Q2 Q3 Q4    | Q1 Q2 Q3 Q4            | Q1 Q2 Q3 Q4 |

|-----------------------------|-------------------|-------------------|---------------------------------------|--------------------|----------------|------------------------|-------------|

| OSC1                        |                   |                   |                                       |                    | ·~~~·/         |                        |             |

| CLKOUT <sup>(4)</sup>       | \/                |                   | Tost <sup>(2)</sup>                   |                    | ↓/             |                        |             |

| INT pin                     | ı ı               |                   |                                       | I<br>I             | i i<br>I I     | 1                      | 1<br>1      |

| INTF flag                   |                   |                   | <u>ل ل الم</u>                        | I<br>              | (3)            |                        |             |

| (INTCON reg.)               |                   |                   | · · · · · · · · · · · · · · · · · · · | Interrupt Laten    | Cy(°)          |                        | 1           |

| GIE bit<br>(INTCON reg.)    |                   |                   | Processor in                          | <u> </u><br>       | · · ·          | 1                      | <u>'</u>    |

| (                           | ' !               |                   | Sleep                                 |                    | !              | '.                     | !_          |

| Instruction Flow            |                   |                   |                                       |                    |                |                        |             |

| PC )                        | (PC)              | PC + 1            | PC + 2                                | X PC + 2           | X PC + 2 X     | <u>    0004h     X</u> | 0005h       |

| Instruction {<br>Fetched    | Inst(PC) = Sleep  | Inst(PC + 1)      | 1<br>1<br>1                           | Inst(PC + 2)       | <br>     <br>  | Inst(0004h)            | Inst(0005h) |

| Instruction {<br>Executed { | Inst(PC – 1)      | Sleep             | 1<br>1                                | Inst(PC + 1)       | Dummy Cycle    | Dummy Cycle            | Inst(0004h) |

| Noto 1:                     |                   | llator modo assur | nod                                   |                    |                |                        |             |

|                             | ,                 |                   |                                       | not apply to EC. I |                | scillator modes        |             |

| Note 1:                     | XT, HS or LP Osci |                   | ned.<br>cale). This delay does        | not apply to EC, I | NTOSC and RC O | scillator modes.       |             |

- 3: GIE = '1' assumed. In this case after wake-up, the processor jumps to 0004h. If GIE = '0', execution will continue in-line.

- 4: CLKOUT is not available in XT, HS, LP or EC Oscillator modes, but shown here for timing reference.

#### 12.8 Code Protection