Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | -                                                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 12                                                                       |

| Program Memory Size        | 3.5KB (2K x 14)                                                          |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 256 x 8                                                                  |

| RAM Size                   | 128 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | A/D 8x10b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 14-SOIC (0.154", 3.90mm Width)                                           |

| Supplier Device Package    | 14-SOIC                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f684-i-sl |

## 2.2.1 GENERAL PURPOSE REGISTER FILE

The register file is organized as 128 x 8 in the PIC16F684. Each register is accessed, either directly or indirectly, through the File Select Register (FSR) (see Section 2.4 "Indirect Addressing, INDF and FSR Registers").

#### 2.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers are registers used by the CPU and peripheral functions for controlling the desired operation of the device (see Table 2-1). These registers are static RAM.

The special registers can be classified into two sets: core and peripheral. The Special Function Registers associated with the "core" are described in this section. Those related to the operation of the peripheral features are described in the section of that peripheral feature.

FIGURE 2-2: DATA MEMORY MAP OF THE PIC16F684

|                   | File<br>Address | ,                        | File<br>Address |  |  |  |  |  |  |

|-------------------|-----------------|--------------------------|-----------------|--|--|--|--|--|--|

| Indirect Addr.(1) | 00h             | Indirect Addr. (1)       | _               |  |  |  |  |  |  |

| TMR0              | 00h             | OPTION_REG               | 80h<br>81h      |  |  |  |  |  |  |

|                   | 1               |                          | -               |  |  |  |  |  |  |

| PCL<br>STATUS     | 02h             | PCL<br>STATUS            | 82h             |  |  |  |  |  |  |

| FSR               | 03h<br>04h      | FSR                      | 83h<br>84h      |  |  |  |  |  |  |

| PORTA             | 1               | TRISA                    |                 |  |  |  |  |  |  |

| FORTA             | 05h<br>06h      | IRIOA                    | 85h<br>86h      |  |  |  |  |  |  |

| PORTC             | 07h             | TRISC                    | 87h             |  |  |  |  |  |  |

| FORTC             | 1               | TRISC                    | 88h             |  |  |  |  |  |  |

|                   | 08h<br>09h      |                          | 89h             |  |  |  |  |  |  |

| PCLATH            | 0Ah             | PCLATH                   | 8Ah             |  |  |  |  |  |  |

| INTCON            | 1               | INTCON                   |                 |  |  |  |  |  |  |

| PIR1              | 0Bh             | PIE1                     | 8Bh             |  |  |  |  |  |  |

| FIKI              | 0Ch             | PIEI                     | 8Ch             |  |  |  |  |  |  |

| TMR1L             | 0Dh             | PCON                     | 8Dh             |  |  |  |  |  |  |

| TMR1H             | 0Eh             | OSCCON                   | 8Eh             |  |  |  |  |  |  |

|                   | 0Fh             |                          | 8Fh             |  |  |  |  |  |  |

| T1CON<br>TMR2     | 10h             | OSCTUNE<br>ANSEL         | 90h             |  |  |  |  |  |  |

| T2CON             | 11h             | PR2                      | 91h             |  |  |  |  |  |  |

| CCPR1L            | 12h             | PR2                      | 92h             |  |  |  |  |  |  |

| CCPR1H            | 13h             |                          | 93h             |  |  |  |  |  |  |

|                   | 14h             | 14/5/14                  | 94h             |  |  |  |  |  |  |

| CCP1CON           | 15h             | WPUA                     | 95h             |  |  |  |  |  |  |

| PWM1CON           | 16h             | IOCA                     | 96h             |  |  |  |  |  |  |

| ECCPAS            | 17h             |                          | 97h             |  |  |  |  |  |  |

| WDTCON            | 18h             | 1/2001/                  | 98h             |  |  |  |  |  |  |

| CMCON0            | 19h             | VRCON                    | 99h             |  |  |  |  |  |  |

| CMCON1            | 1Ah             | EEDAT                    | 9Ah             |  |  |  |  |  |  |

|                   | 1Bh             | EEADR                    | 9Bh             |  |  |  |  |  |  |

|                   | 1Ch             | EECON1                   | 9Ch             |  |  |  |  |  |  |

|                   | 1Dh             | EECON2 <sup>(1)</sup>    | 9Dh             |  |  |  |  |  |  |

| ADRESH            | 1Eh             | ADRESL                   | 9Eh             |  |  |  |  |  |  |

| ADCON0            | 1Fh             | ADCON1                   | 9Fh             |  |  |  |  |  |  |

|                   | 20h             | General<br>Purpose       | A0h             |  |  |  |  |  |  |

|                   |                 | Registers                |                 |  |  |  |  |  |  |

| General           |                 | 32 Bytes                 | BFh             |  |  |  |  |  |  |

| Purpose           |                 |                          |                 |  |  |  |  |  |  |

| Registers         |                 |                          |                 |  |  |  |  |  |  |

| 96 Bytes          |                 |                          |                 |  |  |  |  |  |  |

|                   |                 |                          |                 |  |  |  |  |  |  |

|                   |                 |                          |                 |  |  |  |  |  |  |

|                   |                 |                          |                 |  |  |  |  |  |  |

|                   |                 |                          |                 |  |  |  |  |  |  |

|                   | 6Fh             |                          |                 |  |  |  |  |  |  |

|                   | 70              | A 0000000 701- 751       | F0h             |  |  |  |  |  |  |

|                   | 7Fh             | Accesses 70h-7Fh         | FFh             |  |  |  |  |  |  |

| Bank 0            |                 | Bank 1                   |                 |  |  |  |  |  |  |

| Unimplemented da  | ata memor       | y locations, read as '0' |                 |  |  |  |  |  |  |

| <del></del>       |                 |                          |                 |  |  |  |  |  |  |

| •                 |                 |                          |                 |  |  |  |  |  |  |

TABLE 2-2: PIC16F684 SPECIAL FUNCTION REGISTERS SUMMARY BANK 1

| Addr   | Name                | Bit 7              | Bit 6                                | Bit 5            | Bit 4         | Bit 3               | Bit 2           | Bit 1         | Bit 0     | Value on POR, BOR | Page    |

|--------|---------------------|--------------------|--------------------------------------|------------------|---------------|---------------------|-----------------|---------------|-----------|-------------------|---------|

| Bank 1 |                     |                    |                                      |                  |               |                     |                 |               |           |                   |         |

| 80h    | INDF                | Addressing         | this location                        | uses conten      | ts of FSR to  | address data        | a memory (no    | ot a physical | register) | xxxx xxxx         | 19, 104 |

| 81h    | OPTION_REG          | RAPU               | INTEDG                               | T0CS             | T0SE          | PSA                 | PS2             | PS1           | PS0       | 1111 1111         | 14, 104 |

| 82h    | PCL                 | Program Co         | ounter's (PC)                        | Least Signif     | icant Byte    |                     |                 |               |           | 0000 0000         | 19, 104 |

| 83h    | STATUS              | IRP <sup>(1)</sup> | RP1 <sup>(1)</sup>                   | RP0              | TO            | PD                  | Z               | DC            | С         | 0001 1xxx         | 13, 104 |

| 84h    | FSR                 | Indirect Dat       | Indirect Data Memory Address Pointer |                  |               |                     |                 |               |           | xxxx xxxx         | 19, 104 |

| 85h    | TRISA               | _                  | 1                                    | TRISA5           | TRISA4        | TRISA3              | TRISA2          | TRISA1        | TRISA0    | 11 1111           | 31, 104 |

| 86h    | _                   | Unimplemented      |                                      |                  |               |                     |                 |               |           | _                 | _       |

| 87h    | TRISC               | _                  | _                                    | TRISC5           | TRISC4        | TRISC3              | TRISC2          | TRISC1        | TRISC0    | 11 1111           | 40, 104 |

| 88h    | _                   | Unimpleme          | Jnimplemented                        |                  |               |                     |                 |               |           |                   | _       |

| 89h    | _                   | Unimpleme          | Inimplemented                        |                  |               |                     |                 |               |           | _                 | _       |

| 8Ah    | PCLATH              | _                  | 1                                    | _                | Write         | e Buffer for u      | pper 5 bits of  | Program Co    | ounter    | 0 0000            | 19, 104 |

| 8Bh    | INTCON              | GIE                | PEIE                                 | T0IE             | INTE          | RAIE                | TOIF            | INTF          | RAIF      | 0000 0000         | 15, 104 |

| 8Ch    | PIE1                | EEIE               | ADIE                                 | CCP1IE           | C2IE          | C1IE                | OSFIE           | TMR2IE        | TMR1IE    | 0000 0000         | 16, 104 |

| 8Dh    | _                   | Unimpleme          | nted                                 |                  |               |                     |                 |               |           | _                 | _       |

| 8Eh    | PCON                | _                  | 1                                    | ULPWUE           | SBOREN        | _                   | _               | POR           | BOR       | 01qq              | 18, 104 |

| 8Fh    | OSCCON              | _                  | IRCF2                                | IRCF1            | IRCF0         | OSTS <sup>(2)</sup> | HTS             | LTS           | SCS       | -110 x000         | 20, 104 |

| 90h    | OSCTUNE             | _                  | _                                    | _                | TUN4          | TUN3                | TUN2            | TUN1          | TUN0      | 0 0000            | 24, 105 |

| 91h    | ANSEL               | ANS7               | ANS6                                 | ANS5             | ANS4          | ANS3                | ANS2            | ANS1          | ANS0      | 1111 1111         | 32, 105 |

| 92h    | PR2                 | Timer2 Mod         | lule Period R                        | egister          |               |                     |                 |               |           | 1111 1111         | 53, 105 |

| 93h    | _                   | Unimpleme          | nted                                 |                  |               |                     |                 |               |           | _                 | _       |

| 94h    | _                   | Unimpleme          | nted                                 |                  |               |                     |                 |               |           | _                 | _       |

| 95h    | WPUA <sup>(3)</sup> | _                  | 1                                    | WPUA5            | WPUA4         | _                   | WPUA2           | WPUA1         | WPUA0     | 11 -111           | 33, 105 |

| 96h    | IOCA                | _                  | _                                    | IOCA5            | IOCA4         | IOCA3               | IOCA2           | IOCA1         | IOCA0     | 00 0000           | 33, 105 |

| 97h    | _                   | Unimpleme          | nted                                 |                  |               |                     |                 |               |           | _                 | _       |

| 98h    | _                   | Unimpleme          | nted                                 |                  |               |                     |                 |               |           | _                 | _       |

| 99h    | VRCON               | VREN               | _                                    | VRR              | _             | VR3                 | VR2             | VR1           | VR0       | 0-0- 0000         | 63, 105 |

| 9Ah    | EEDAT               | EEDAT7             | EEDAT6                               | EEDAT5           | EEDAT4        | EEDAT3              | EEDAT2          | EEDAT1        | EEDAT0    | 0000 0000         | 75, 105 |

| 9Bh    | EEADR               | EEADR7             | EEADR6                               | EEADR5           | EEADR4        | EEADR3              | EEADR2          | EEADR1        | EEADR0    | 0000 0000         | 75, 105 |

| 9Ch    | EECON1              | _                  | _                                    | _                | _             | WRERR               | WREN            | WR            | RD        | x000              | 76, 105 |

| 9Dh    | EECON2              | EEPROM C           | ontrol Regis                         | ter 2 (not a p   | hysical regis | ster)               |                 |               |           |                   | 76, 105 |

| 9Eh    | ADRESL              | Least Signif       | icant 2 bits o                       | f the left shift | ted result or | 8 bits of the       | right shifted i | esult         |           | xxxx xxxx         | 71, 105 |

| 9Fh    | ADCON1              | _                  | ADCS2                                | ADCS1            | ADCS0         | _                   | _               | _             | _         | -000              | 70, 105 |

|        |                     |                    |                                      |                  |               |                     |                 |               |           |                   |         |

$\textbf{Legend:} \qquad - = \text{Unimplemented locations read as '0'}, \ u = \text{unchanged, } x = \text{unknown, } q = \text{value depends on condition, shaded} = \text{unimplemented locations} \\ \text{unimplemented locations read as '0'}, \ u = \text{unchanged, } x = \text{unknown, } q = \text{value depends on condition, shaded} \\ \text{unimplemented locations} \\ \text{unimplemente$

Note 1: IRP and RP1 bits are reserved, always maintain these bits clear.

<sup>2:</sup> OSTS bit of the OSCCON register reset to '0' with Dual Speed Start-up and LP, HS or XT selected as the oscillator.

<sup>3:</sup> RA3 pull-up is enabled when MCLRE is '1' in the Configuration Word register.

#### 2.2.2.5 PIR1 Register

The PIR1 register contains the peripheral interrupt flag bits, as shown in Register 2-5.

Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE of the INTCON register. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

#### REGISTER 2-5: PIR1: PERIPHERAL INTERRUPT REQUEST REGISTER 1

| R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0  |

|-------|-------|--------|-------|-------|-------|--------|--------|

| EEIF  | ADIF  | CCP1IF | C2IF  | C1IF  | OSFIF | TMR2IF | TMR1IF |

| bit 7 |       |        |       |       |       |        | bit 0  |

Note:

| Legend:           |                  |                       |                                    |  |  |  |  |

|-------------------|------------------|-----------------------|------------------------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | U = Unimplemented bit, read as '0' |  |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown                 |  |  |  |  |

bit 7 **EEIF:** EEPROM Write Operation Interrupt Flag bit

1 = The write operation completed (must be cleared in software)0 = The write operation has not completed or has not been started

bit 6 ADIF: A/D Interrupt Flag bit

1 = A/D conversion complete

0 = A/D conversion has not completed or has not been started

bit 5 CCP1IF: CCP1 Interrupt Flag bit

Capture mode:

1 = A TMR1 register capture occurred (must be cleared in software)

0 = No TMR1 register capture occurred

Compare mode:

1 = A TMR1 register compare match occurred (must be cleared in software)

0 = No TMR1 register compare match occurred

PWM mode:

Unused in this mode

bit 4 **C2IF:** Comparator 2 Interrupt Flag bit

1 = Comparator 2 output has changed (must be cleared in software)

0 = Comparator 2 output has not changed

bit 3 C1IF: Comparator 1 Interrupt Flag bit

1 = Comparator 1 output has changed (must be cleared in software)

0 = Comparator 1 output has not changed

bit 2 OSFIF: Oscillator Fail Interrupt Flag bit

1 = System oscillator failed, clock input has changed to INTOSC (must be cleared in software)

0 = System clock operating

bit 1 TMR2IF: Timer2 to PR2 Match Interrupt Flag bit

1 = Timer2 to PR2 match occurred (must be cleared in software)

0 = Timer2 to PR2 match has not occurred

bit 0 TMR1IF: Timer1 Overflow Interrupt Flag bit

1 = Timer1 register overflowed (must be cleared in software)

0 = Timer1 has not overflowed

#### 2.3 PCL and PCLATH

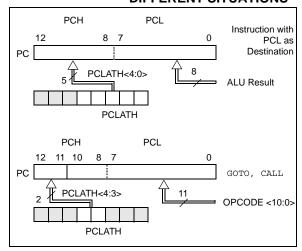

The Program Counter (PC) is 13 bits wide. The low byte comes from the PCL register, which is a readable and writable register. The high byte (PC<12:8>) is not directly readable or writable and comes from PCLATH. On any Reset, the PC is cleared. Figure 2-3 shows the two situations for the loading of the PC. The upper example in Figure 2-3 shows how the PC is loaded on a write to PCL (PCLATH<4:0>  $\rightarrow$  PCH). The lower example in Figure 2-3 shows how the PC is loaded during a CALL or GOTO instruction (PCLATH<4:3>  $\rightarrow$  PCH).

FIGURE 2-3: LOADING OF PC IN DIFFERENT SITUATIONS

#### 2.3.1 MODIFYING PCL

Executing any instruction with the PCL register as the destination simultaneously causes the Program Counter PC<12:8> bits (PCH) to be replaced by the contents of the PCLATH register. This allows the entire contents of the program counter to be changed by first writing the desired upper 5 bits to the PCLATH register. Then, when the lower 8 bits are written to the PCL register, all 13 bits of the program counter will change to the values contained in the PCLATH register and those being written to the PCL register.

A computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL). Care should be exercised when jumping into a look-up table or program branch table (computed GOTO) by modifying the PCL register. Assuming that PCLATH is set to the table start address, if the table length is greater than 255 instructions or if the lower 8 bits of the memory address rolls over from 0xFF to 0x00 in the middle of the table, then PCLATH must be incremented for each address rollover that occurs between the table beginning and the target location within the table.

For more information refer to Application Note AN556, "Implementing a Table Read" (DS00556).

#### 2.3.2 STACK

The PIC16F684 Family has an 8-level x 13-bit wide hardware stack (see Figure 2-1). The stack space is not part of either program or data space and the Stack Pointer is not readable or writable. The PC is PUSHed onto the stack when a CALL instruction is executed or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not affected by a PUSH or POP operation.

The stack operates as a circular buffer. This means that after the stack has been PUSHed eight times, the ninth push overwrites the value that was stored from the first push. The tenth push overwrites the second push (and so on).

- Note 1: There are no Status bits to indicate stack overflow or stack underflow conditions.

- 2: There are no instructions/mnemonics called PUSH or POP. These are actions that occur from the execution of the CALL, RETURN, RETLW and RETFIE instructions or the vectoring to an interrupt address.

# 2.4 Indirect Addressing, INDF and FSR Registers

The INDF register is not a physical register. Addressing the INDF register will cause indirect addressing.

Indirect addressing is possible by using the INDF register. Any instruction using the INDF register actually accesses data pointed to by the File Select Register (FSR). Reading INDF itself indirectly will produce 00h. Writing to the INDF register indirectly results in a no operation (although Status bits may be affected). An effective 9-bit address is obtained by concatenating the 8-bit FSR and the IRP bit of the STATUS register, as shown in Figure 2-4.

A simple program to clear RAM location 20h-2Fh using indirect addressing is shown in Example 2-1.

EXAMPLE 2-1: INDIRECT ADDRESSING

|          | MOVLW | 0x20   | ;initialize pointer  |  |  |

|----------|-------|--------|----------------------|--|--|

|          | MOVWF | FSR    | ;to RAM              |  |  |

| NEXT     | CLRF  | INDF   | clear INDF register; |  |  |

|          | INCF  | FSR, f | ;inc pointer         |  |  |

|          | BTFSS | FSR,4  | ;all done?           |  |  |

|          | GOTO  | NEXT   | ;no clear next       |  |  |

| CONTINUE |       |        | ;yes continue        |  |  |

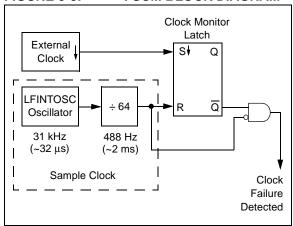

#### 3.8 Fail-Safe Clock Monitor

The Fail-Safe Clock Monitor (FSCM) allows the device to continue operating should the external oscillator fail. The FSCM can detect oscillator failure any time after the Oscillator Start-up Timer (OST) has expired. The FSCM is enabled by setting the FCMEN bit in the Configuration Word register (CONFIG). The FSCM is applicable to all external oscillator modes (LP, XT, HS, EC, RC and RCIO).

FIGURE 3-8: FSCM BLOCK DIAGRAM

#### 3.8.1 FAIL-SAFE DETECTION

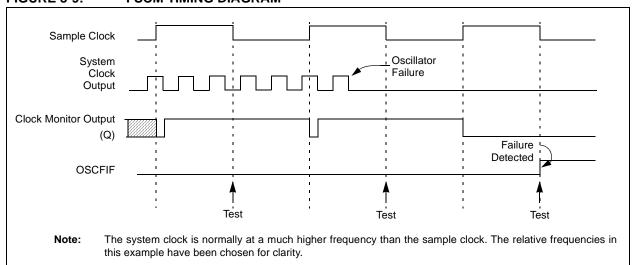

The FSCM module detects a failed oscillator by comparing the external oscillator to the FSCM sample clock. The sample clock is generated by dividing the LFINTOSC by 64. See Figure 3-8. Inside the fail detector block is a latch. The external clock sets the latch on each falling edge of the external clock. The sample clock clears the latch on each rising edge of the sample clock. A failure is detected when an entire half-cycle of the sample clock elapses before the primary clock goes low.

#### 3.8.2 FAIL-SAFE OPERATION

When the external clock fails, the FSCM switches the device clock to an internal clock source and sets the bit flag OSFIF of the PIR1 register. Setting this flag will generate an interrupt if the OSFIE bit of the PIE1 register is also set. The device firmware can then take steps to mitigate the problems that may arise from a failed clock. The system clock will continue to be sourced from the internal clock source until the device firmware successfully restarts the external oscillator and switches back to external operation.

The internal clock source chosen by the FSCM is determined by the IRCF<2:0> bits of the OSCCON register. This allows the internal oscillator to be configured before a failure occurs.

#### 3.8.3 FAIL-SAFE CONDITION CLEARING

The Fail-Safe condition is cleared after a Reset, executing a SLEEP instruction or toggling the SCS bit of the OSCCON register. When the SCS bit is toggled, the OST is restarted. While the OST is running, the device continues to operate from the INTOSC selected in OSCCON. When the OST times out, the Fail-Safe condition is cleared and the device will be operating from the external clock source. The Fail-Safe condition must be cleared before the OSFIF flag can be cleared.

#### 3.8.4 RESET OR WAKE-UP FROM SLEEP

The FSCM is designed to detect an oscillator failure after the Oscillator Start-up Timer (OST) has expired. The OST is used after waking up from Sleep and after any type of Reset. The OST is not used with the EC or RC Clock modes so that the FSCM will be active as soon as the Reset or wake-up has completed. When the FSCM is enabled, the Two-Speed Start-up is also enabled. Therefore, the device will always be executing code while the OST is operating.

Note: Due to the wide range of oscillator start-up times, the Fail-Safe circuit is not active during oscillator start-up (i.e., after exiting Reset or Sleep). After an appropriate amount of time, the user should check the OSTS bit of the OSCCON register to verify the oscillator start-up and that the system clock switchover has successfully completed.

FIGURE 3-9: FSCM TIMING DIAGRAM

TABLE 3-2: SUMMARY OF REGISTERS ASSOCIATED WITH CLOCK SOURCES

| Name                  | Bit 7 | Bit 6 | Bit 5  | Bit 4 | Bit 3 | Bit 2 | Bit 1  | Bit 0  | Value on:<br>POR, BOR | Value on<br>all other<br>Resets <sup>(1)</sup> |

|-----------------------|-------|-------|--------|-------|-------|-------|--------|--------|-----------------------|------------------------------------------------|

| CONFIG <sup>(2)</sup> | CPD   | CP    | MCLRE  | PWRTE | WDTE  | FOSC2 | FOSC1  | FOSC0  | _                     | _                                              |

| OSCCON                | _     | IRCF2 | IRCF1  | IRCF0 | OSTS  | HTS   | LTS    | SCS    | -110 x000             | -110 x000                                      |

| OSCTUNE               | _     | _     | _      | TUN4  | TUN3  | TUN2  | TUN1   | TUN0   | 0 0000                | u uuuu                                         |

| PIE1                  | EEIE  | ADIE  | CCP1IE | C2IE  | C1IE  | OSFIE | TMR2IE | TMR1IE | 0000 0000             | 0000 0000                                      |

| PIR1                  | EEIF  | ADIF  | CCP1IF | C2IF  | C1IF  | OSFIF | TMR2IF | TMR1IF | 0000 0000             | 0000 0000                                      |

**Legend:** x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by oscillators.

Note 1: Other (non Power-up) Resets include MCLR Reset and Watchdog Timer Reset during normal operation.

2: See Configuration Word register (Register 12-1) for operation of all register bits.

#### 4.0 I/O PORTS

There are as many as twelve general purpose I/O pins available. Depending on which peripherals are enabled, some or all of the pins may not be available as general purpose I/O. In general, when a peripheral is enabled, the associated pin may not be used as a general purpose I/O pin.

#### 4.1 PORTA and the TRISA Registers

PORTA is a 6-bit wide, bidirectional port. The corresponding data direction register is TRISA (Register 4-2). Setting a TRISA bit (= 1) will make the corresponding PORTA pin an input (i.e., disable the output driver). Clearing a TRISA bit (= 0) will make the corresponding PORTA pin an output (i.e., enables output driver and puts the contents of the output latch on the selected pin). The exception is RA3, which is input only and its TRIS bit will always read as '1'. Example 4-1 shows how to initialize PORTA.

Reading the PORTA register (Register 4-1) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the

port pins are read, this value is modified and then written to the PORT data latch. RA3 reads '0' when MCLRE = 1.

The TRISA register controls the direction of the PORTA pins, even when they are being used as analog inputs. The user must ensure the bits in the TRISA register are maintained set when using them as analog inputs. I/O pins configured as analog input always read '0'.

Note: The ANSEL and CMCON0 registers must be initialized to configure an analog channel as a digital input. Pins configured as analog inputs will read '0'.

#### **EXAMPLE 4-1: INITIALIZING PORTA**

| BCF   | STATUS, RPO | ;Bank 0                |

|-------|-------------|------------------------|

| CLRF  | PORTA       | ;Init PORTA            |

| MOVLW | 07h         | ;Set RA<2:0> to        |

| MOVWF | CMCON0      | ;digital I/O           |

| BSF   | STATUS, RPO | ;Bank 1                |

| CLRF  | ANSEL       | ;digital I/O           |

| MOVLW | 0Ch         | ;Set RA<3:2> as inputs |

| MOVWF | TRISA       | ;and set RA<5:4,1:0>   |

|       |             | ;as outputs            |

| BCF   | STATUS, RPO | ;Bank 0                |

|       |             |                        |

#### REGISTER 4-1: PORTA: PORTA REGISTER

| U-0   | U-0 | R/W-x | R/W-0 | R-x | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-------|-------|-----|-------|-------|-------|

| _     | _   | RA5   | RA4   | RA3 | RA2   | RA1   | RA0   |

| bit 7 |     |       |       |     |       |       | bit 0 |

Legend:

$R = Readable \ bit$   $W = Writable \ bit$   $U = Unimplemented \ bit$ , read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7-6 Unimplemented: Read as '0'

bit 5-0 RA<5:0>: PORTA I/O Pin bit

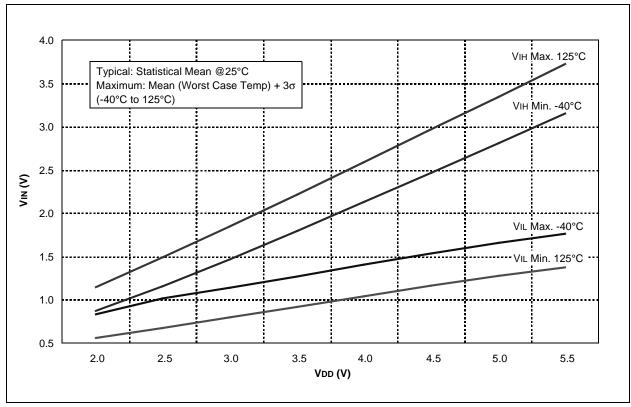

1 = PORTA pin is > VIH

0 = PORTA pin is < VIL

#### REGISTER 4-2: TRISA: PORTA TRI-STATE REGISTER

| U-0   | U-0 | R/W-1  | R/W-1  | R-1    | R/W-1  | R/W-1  | R/W-1  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| _     | _   | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7-6 Unimplemented: Read as '0'

bit 5-0 TRISA<5:0>: PORTA Tri-State Control bit

1 = PORTA pin configured as an input (tri-stated)

0 = PORTA pin configured as an output

Note 1: TRISA<3> always reads '1'.

2: TRISA<5:4> always reads '1' in XT, HS and LP OSC modes.

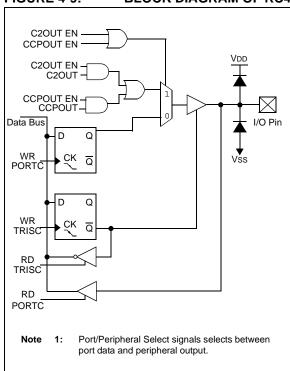

#### 4.3.5 RC4/C2OUT/P1B

The RC4 is configurable to function as one of the following:

- a general purpose I/O

- · a digital output from the comparator

- · a digital output from the Enhanced CCP

Note: Enabling both C2OUT and P1B will cause a conflict on RC4 and create unpredictable results. Therefore, if C2OUT is enabled, the ECCP can not be used in Half-Bridge or Full-Bridge mode and vice-versa.

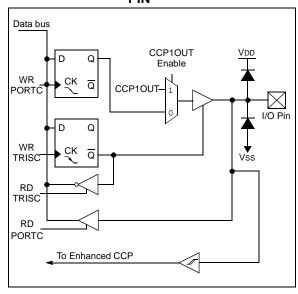

#### FIGURE 4-9: BLOCK DIAGRAM OF RC4

#### 4.3.6 RC5/CCP1/P1A

The RC5 is configurable to function as one of the following:

- a general purpose I/O

- a digital input/output for the Enhanced CCP

FIGURE 4-10: BLOCK DIAGRAM OF RC5

PIN

TABLE 4-2: SUMMARY OF REGISTERS ASSOCIATED WITH PORTC

| Name   | Bit 7 | Bit 6 | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|-------|-------|--------|--------|--------|--------|--------|--------|-----------------------|---------------------------------|

| ANSEL  | ANS7  | ANS6  | ANS5   | ANS4   | ANS3   | ANS2   | ANS1   | ANS0   | 1111 1111             | 1111 1111                       |

| CMCON0 | C2OUT | C1OUT | C2INV  | C1INV  | CIS    | CM2    | CM1    | CM0    | 0000 0000             | 0000 0000                       |

| PORTC  | _     | _     | RC5    | RC4    | RC3    | RC2    | RC1    | RC0    | xx 0000               | uu uu00                         |

| TRISC  | _     | _     | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 11 1111               | 11 1111                         |

**Legend:** x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTC.

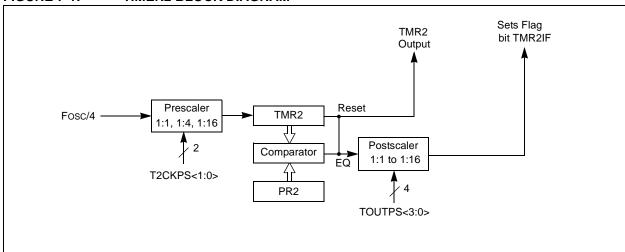

#### 7.0 TIMER2 MODULE

The Timer2 module is an eight-bit timer with the following features:

- 8-bit timer register (TMR2)

- 8-bit period register (PR2)

- · Interrupt on TMR2 match with PR2

- Software programmable prescaler (1:1, 1:4, 1:16)

- Software programmable postscaler (1:1 to 1:16)

See Figure 7-1 for a block diagram of Timer2.

#### 7.1 Timer2 Operation

The clock input to the Timer2 module is the system instruction clock (Fosc/4). The clock is fed into the Timer2 prescaler, which has prescale options of 1:1, 1:4 or 1:16. The output of the prescaler is then used to increment the TMR2 register.

The values of TMR2 and PR2 are constantly compared to determine when they match. TMR2 will increment from 00h until it matches the value in PR2. When a match occurs, two things happen:

- TMR2 is reset to 00h on the next increment cycle.

- The Timer2 postscaler is incremented

The match output of the Timer2/PR2 comparator is fed into the Timer2 postscaler. The postscaler has postscale options of 1:1 to 1:16 inclusive. The output of the Timer2 postscaler is used to set the TMR2IF interrupt flag bit in the PIR1 register.

The TMR2 and PR2 registers are both fully readable and writable. On any Reset, the TMR2 register is set to 00h and the PR2 register is set to FFh.

Timer2 is turned on by setting the TMR2ON bit in the T2CON register to a '1'. Timer2 is turned off by clearing the TMR2ON bit to a '0'.

The Timer2 prescaler is controlled by the T2CKPS bits in the T2CON register. The Timer2 postscaler is controlled by the TOUTPS bits in the T2CON register. The prescaler and postscaler counters are cleared when:

- · A write to TMR2 occurs.

- A write to T2CON occurs.

- Any device Reset occurs (Power-on Reset, MCLR Reset, Watchdog Timer Reset, or Brown-out Reset).

**Note:** TMR2 is not cleared when T2CON is written.

FIGURE 7-1: TIMER2 BLOCK DIAGRAM

#### 11.3.4 OPERATION IN SLEEP MODE

In Sleep mode, the TMR2 register will not increment and the state of the module will not change. If the CCP1 pin is driving a value, it will continue to drive that value. When the device wakes up, TMR2 will continue from its previous state.

## 11.3.5 CHANGES IN SYSTEM CLOCK FREQUENCY

The PWM frequency is derived from the system clock frequency. Any changes in the system clock frequency will result in changes to the PWM frequency. See Section 3.0 "Oscillator Module (With Fail-Safe Clock Monitor)" for additional details.

#### 11.3.6 EFFECTS OF RESET

Any Reset will force all ports to Input mode and the CCP registers to their Reset states.

#### 11.3.7 SETUP FOR PWM OPERATION

The following steps should be taken when configuring the CCP module for PWM operation:

- Disable the PWM pin (CCP1) output driver by setting the associated TRIS bit.

- 2. Set the PWM period by loading the PR2 register.

- Configure the CCP module for the PWM mode by loading the CCP1CON register with the appropriate values.

- Set the PWM duty cycle by loading the CCPR1L register and CCP1 bits of the CCP1CON register.

- 5. Configure and start Timer2:

- Clear the TMR2IF interrupt flag bit of the PIR1 register.

- Set the Timer2 prescale value by loading the T2CKPS bits of the T2CON register.

- Enable Timer2 by setting the TMR2ON bit of the T2CON register.

- Enable PWM output after a new PWM cycle has started:

- Wait until Timer2 overflows (TMR2IF bit of the PIR1 register is set).

- Enable the CCP1 pin output driver by clearing the associated TRIS bit.

## 11.4.2.1 Direction Change in Full-Bridge Mode

In the Full-Bridge mode, the P1M1 bit in the CCP1CON register allows users to control the forward/reverse direction. When the application firmware changes this direction control bit, the module will change to the new direction on the next PWM cycle.

A direction change is initiated in software by changing the P1M1 bit of the CCP1CON register. The following sequence occurs four Timer2 cycles prior to the end of the current PWM period:

- The modulated outputs (P1B and P1D) are placed in their inactive state.

- The associated unmodulated outputs (P1A and P1C) are switched to drive in the opposite direction.

- PWM modulation resumes at the beginning of the next period.

See Figure 11-12 for an illustration of this sequence.

The Full-Bridge mode does not provide dead-band delay. As one output is modulated at a time, dead-band delay is generally not required. There is a situation where dead-band delay is required. This situation occurs when both of the following conditions are true:

- The direction of the PWM output changes when the duty cycle of the output is at or near 100%.

- The turn off time of the power switch, including the power device and driver circuit, is greater than the turn on time.

Figure 11-13 shows an example of the PWM direction changing from forward to reverse, at a near 100% duty cycle. In this example, at time t1, the output P1A and P1D become inactive, while output P1C becomes active. Since the turn off time of the power devices is longer than the turn on time, a shoot-through current will flow through power devices QC and QD (see Figure 11-10) for the duration of 't'. The same phenomenon will occur to power devices QA and QB for PWM direction change from reverse to forward.

If changing PWM direction at high duty cycle is required for an application, two possible solutions for eliminating the shoot-through current are:

- 1. Reduce PWM duty cycle for one PWM period before changing directions.

- 2. Use switch drivers that can drive the switches off faster than they can drive them on.

Other options to prevent shoot-through current may exist.

- Note 1: The direction bit P1M1 of the CCP1CON register is written any time during the PWM cycle.

- 2: When changing directions, the P1A and P1C signals switch before the end of the current PWM cycle. The modulated P1B and P1D signals are inactive at this time. The length of this time is four Timer2 counts.

#### REGISTER 11-3: PWM1CON: ENHANCED PWM CONTROL REGISTER

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| PRSEN | PDC6  | PDC5  | PDC4  | PDC3  | PDC2  | PDC1  | PDC0  |

| bit 7 |       |       |       |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7 PRSEN: PWM Restart Enable bit

1 = Upon auto-shutdown, the ECCPASE bit clears automatically once the shutdown event goes away; the PWM restarts automatically

0 = Upon auto-shutdown, ECCPASE must be cleared in software to restart the PWM

bit 6-0 PDC<6:0>: PWM Delay Count bits

PDCn = Number of Fosc/4 (4 \* Tosc) cycles between the scheduled time when a PWM signal **should** transition active and the **actual** time it transitions active

Note 1: Bit resets to '0' with Two-Speed Start-up and LP, XT or HS selected as the Oscillator mode or Fail-Safe mode is enabled.

TABLE 11-5: SUMMARY OF REGISTERS ASSOCIATED WITH CAPTURE, COMPARE AND PWM

| Name    | Bit 7                                                                       | Bit 6       | Bit 5         | Bit 4       | Bit 3   | Bit 2  | Bit 1   | Bit 0   |      | e on:<br>BOR | all o | e on<br>other<br>sets |

|---------|-----------------------------------------------------------------------------|-------------|---------------|-------------|---------|--------|---------|---------|------|--------------|-------|-----------------------|

| CCPR1L  | Capture/Compare/PWM Register 1 Low Byte                                     |             |               |             |         |        |         |         |      | xxxx         | uuuu  | uuuu                  |

| CCPR1H  | Capture/Co                                                                  | mpare/PWI   | √l Register ′ | 1 High Byte |         |        |         |         | xxxx | xxxx         | uuuu  | uuuu                  |

| CCP1CON | P1M1                                                                        | P1M0        | DC1B1         | DC1B0       | CCP1M3  | CCP1M2 | CCP1M1  | CCP1M0  | 0000 | 0000         | 0000  | 0000                  |

| CMCON0  | C2OUT                                                                       | C1OUT       | C2INV         | C1INV       | CIS     | CM2    | CM1     | CM0     | 0000 | 0000         | 0000  | 0000                  |

| CMCON1  | 1                                                                           |             |               | I           | _       | 1      | T1GSS   | C2SYNC  |      | 10           |       | 10                    |

| ECCPAS  | ECCPASE                                                                     | ECCPAS2     | ECCPAS1       | ECCPAS0     | PSSAC1  | PSSAC0 | PSSBD1  | PSSBD0  | 0000 | 0000         | 0000  | 0000                  |

| INTCON  | GIE                                                                         | PEIE        | TOIE          | INTE        | RAIE    | TOIF   | INTF    | RAIF    | 0000 | 0000         | 0000  | 0000                  |

| PIE1    | EEIE                                                                        | ADIE        | CCP1IE        | C2IE        | C1IE    | OSFIE  | TMR2IE  | TMR1IE  | 0000 | 0000         | 0000  | 0000                  |

| PIR1    | EEIF                                                                        | ADIF        | CCP1IF        | C2IF        | C1IF    | OSFIF  | TMR2IF  | TMR1IF  | 0000 | 0000         | 0000  | 0000                  |

| PR2     | Timer2 Mod                                                                  | dule Period | Register      |             |         |        |         |         | 1111 | 1111         | 1111  | 1111                  |

| PWM1CON | PRSEN                                                                       | PDC6        | PDC5          | PDC4        | PDC3    | PDC2   | PDC1    | PDC0    | 0000 | 0000         | 0000  | 0000                  |

| T1CON   | T1GINV                                                                      | TMR1GE      | T1CKPS1       | T1CKPS0     | T10SCEN | T1SYNC | TMR1CS  | TMR10N  | 0000 | 0000         | uuuu  | uuuu                  |

| T2CON   | _                                                                           | TOUTPS3     | TOUTPS2       | TOUTPS1     | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000 | 0000         | -000  | 0000                  |

| TMR1L   | Holding Register for the Least Significant Byte of the 16-bit TMR1 Register |             |               |             |         |        |         |         | xxxx | xxxx         | uuuu  | uuuu                  |

| TMR1H   | Holding Register for the Most Significant Byte of the 16-bit TMR1 Register  |             |               |             |         |        |         |         | xxxx | xxxx         | uuuu  | uuuu                  |

| TMR2    | Timer2 Module Register                                                      |             |               |             |         |        |         |         | 0000 | 0000         | 0000  | 0000                  |

| TRISA   | _                                                                           | _           | TRISA5        | TRISA4      | TRISA3  | TRISA2 | TRISA1  | TRISA0  | 11   | 1111         | 11    | 1111                  |

| TRISC   | _                                                                           | _           | TRISC5        | TRISC4      | TRISC3  | TRISC2 | TRISC1  | TRISC0  | 11   | 1111         | 11    | 1111                  |

**Legend:** - = Unimplemented locations, read as '0', u = unchanged, x = unknown. Shaded cells are not used by the Capture, Compare and PWM.

#### REGISTER 12-1: CONFIG: CONFIGURATION WORD REGISTER

| _            | _ | _ | _ | FCMEN | IESO | BOREN1 | BOREN0 |

|--------------|---|---|---|-------|------|--------|--------|

| bit 15 bit 8 |   |   |   |       |      |        |        |

| CPD   | CP | MCLRE | PWRTE | WDTE | FOSC2 | FOSC1 | FOSC0 |

|-------|----|-------|-------|------|-------|-------|-------|

| bit 7 |    |       |       |      |       |       | bit 0 |

| Legend:           |                  |                      |                                    |

|-------------------|------------------|----------------------|------------------------------------|

| R = Readable bit  | W = Writable bit | P = Programmable'    | U = Unimplemented bit, read as '0' |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown                 |

| -II = Value at FO | JN I = DILIS SEL U                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | = bit is cleared                                                                                                                                                          | X = DIL IS UTKNOWN                                                                   |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                           |                                                                                      |

| bit 15-12         | Unimplemented: Read as '1'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                           |                                                                                      |

| bit 11            | FCMEN: Fail-Safe Clock Monitor Enabled bit<br>1 = Fail-Safe Clock Monitor is enabled<br>0 = Fail-Safe Clock Monitor is disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                           |                                                                                      |

| bit 10            | IESO: Internal External Switchover bit  1 = Internal External Switchover mode is enabled  0 = Internal External Switchover mode is disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                           |                                                                                      |

| bit 9-8           | BOREN<1:0>: Brown-out Reset Selection bits <sup>(1)</sup> 11 = BOR enabled 10 = BOR enabled during operation and disabled i 01 = BOR controlled by SBOREN bit of the PCON 00 = BOR disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | •                                                                                                                                                                         |                                                                                      |

| bit 7             | <b>CPD:</b> Data Code Protection bit <sup>(2)</sup> 1 = Data memory code protection is disabled 0 = Data memory code protection is enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                           |                                                                                      |

| bit 6             | CP: Code Protection bit <sup>(3)</sup> 1 = Program memory code protection is disabled 0 = Program memory code protection is enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                           |                                                                                      |

| bit 5             | MCLRE: RA3/MCLR pin function select bit <sup>(4)</sup> 1 = RA3/MCLR pin function is MCLR  0 = RA3/MCLR pin function is digital input, MCLR in the select bit (4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | nternally tied to VDD                                                                                                                                                     |                                                                                      |

| bit 4             | <b>PWRTE</b> : Power-up Timer Enable bit<br>1 = PWRT disabled<br>0 = PWRT enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                           |                                                                                      |

| bit 3             | WDTE: Watchdog Timer Enable bit  1 = WDT enabled  0 = WDT disabled and can be enabled by SWDTE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | N bit of the WDTCON registe                                                                                                                                               | r                                                                                    |

| bit 2-0           | FOSC<2:0>: Oscillator Selection bits  111 = RC oscillator: CLKOUT function on RA4/O: 110 = RCIO oscillator: I/O function on RA4/OSC2 101 = INTOSC oscillator: CLKOUT function on RA4/O 100 = INTOSCIO oscillator: I/O function on RA4/O 111 = EC: I/O function on RA4/OSC2/CLKOUT p 100 = HS oscillator: High-speed crystal/resonator 100 = XT oscillator: Crystal/resonator on RA4/OSC00 = LP oscillator: Low-power crystal on RA4/OSC000 = | CCLKOUT pin, RC on RA5/O:<br>4/OSC2/CLKOUT pin, I/O funct<br>OSC2/CLKOUT pin, I/O functi<br>in, CLKIN on RA5/OSC1/CLK<br>on RA4/OSC2/CLKOUT and<br>C2/CLKOUT and RA5/OSC1 | SC1/CLKIN ction on RA5/OSC1/CLKIN tion on RA5/OSC1/CLKIN KIN I RA5/OSC1/CLKIN /CLKIN |