Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | -                                                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 12                                                                        |

| Program Memory Size        | 3.5KB (2K x 14)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 128 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                 |

| Data Converters            | A/D 8x10b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 16-VQFN Exposed Pad                                                       |

| Supplier Device Package    | 16-QFN (4x4)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f684t-i-ml |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

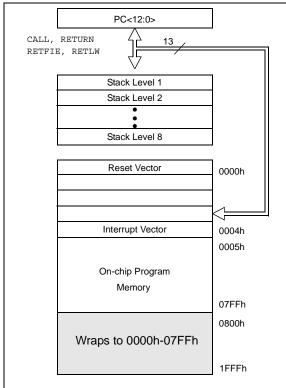

### 2.0 MEMORY ORGANIZATION

### 2.1 Program Memory Organization

The PIC16F684 has a 13-bit program counter capable of addressing an  $8k \times 14$  program memory space. Only the first  $2k \times 14$  (0000h-07FFh) for the PIC16F684 is physically implemented. Accessing a location above these boundaries will cause a wrap around within the first  $2k \times 14$  space. The Reset vector is at 0000h and the interrupt vector is at 0004h (see Figure 2-1).

#### FIGURE 2-1: PROGRAM MEMORY MAP AND STACK FOR THE PIC16F684

### 2.2 Data Memory Organization

The data memory (see Figure 2-2) is partitioned into two banks, which contain the General Purpose Registers (GPR) and the Special Function Registers (SFR). The Special Function Registers are located in the first 32 locations of each bank. Register locations 20h-7Fh in Bank 0 and A0h-BFh in Bank 1 are General Purpose Registers, implemented as static RAM. Register locations F0h-FFh in Bank 1 point to addresses 70h-7Fh in Bank 0. All other RAM is unimplemented and returns '0' when read. The RP0 bit of the STATUS register is the bank select bit.

### <u>RP0</u>

- $0 \rightarrow \text{Bank 0 is selected}$

- $1 \rightarrow \text{Bank 1 is selected}$

Note: The IRP and RP1 bits of the STATUS register are reserved and should always be maintained as '0's.

| R-0           | R-0                                | R/W-0                             | R/W-0           | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|---------------|------------------------------------|-----------------------------------|-----------------|-------------------|-----------------|-----------------|-------|

| C2OUT         | C1OUT                              | C2INV                             | C1INV           | CIS               | CM2             | CM1             | CM0   |

| bit 7         |                                    |                                   |                 |                   |                 |                 | bit 0 |

|               |                                    |                                   |                 |                   |                 |                 |       |

| Legend:       |                                    |                                   |                 |                   |                 |                 |       |

| R = Readable  |                                    | W = Writable                      |                 | -                 | mented bit, rea |                 |       |

| -n = Value at | POR                                | '1' = Bit is set                  |                 | '0' = Bit is cle  | eared           | x = Bit is unkr | nown  |

| bit 7         |                                    | norotor 2 Outo                    | ut hit          |                   |                 |                 |       |

| DIL 7         | When C2INV                         | parator 2 Outp                    |                 |                   |                 |                 |       |

|               | 1 = C2 VIN+ >                      |                                   |                 |                   |                 |                 |       |

|               | 0 = C2 VIN+ <                      | < C2 VIN-                         |                 |                   |                 |                 |       |

|               | When C2INV                         |                                   |                 |                   |                 |                 |       |

|               | 1 = C2 VIN+ <                      | -                                 |                 |                   |                 |                 |       |

|               | 0 = C2 VIN+ >                      |                                   |                 |                   |                 |                 |       |

| bit 6         |                                    | parator 1 Outp                    | ut dit          |                   |                 |                 |       |

|               | <u>When C1INV</u><br>1 = C1 VIN+ > |                                   |                 |                   |                 |                 |       |

|               | 0 = C1 VIN+ <                      | • • • • • •                       |                 |                   |                 |                 |       |

|               | When C1INV                         | <u>= 1:</u>                       |                 |                   |                 |                 |       |

|               | 1 = C1 VIN+ <                      |                                   |                 |                   |                 |                 |       |

|               | 0 = C1 VIN+ >                      | -                                 |                 |                   |                 |                 |       |

| bit 5         | -                                  | parator 2 Outpu                   | it Inversion bi | t                 |                 |                 |       |

|               | 1 = C2 output<br>0 = C2 output     |                                   |                 |                   |                 |                 |       |

| bit 4         | -                                  | parator 1 Outpu                   | It Inversion bi | t                 |                 |                 |       |

|               | 1 = C1 Outpu                       | =                                 |                 |                   |                 |                 |       |

|               | 0 = C1 Outpu                       | t not inverted                    |                 |                   |                 |                 |       |

| bit 3         | -                                  | ator Input Swite                  | ch bit          |                   |                 |                 |       |

|               | When CM<2:                         |                                   |                 |                   |                 |                 |       |

|               |                                    | nnects to C1 V<br>onnects to C2 V |                 |                   |                 |                 |       |

|               |                                    | nnects to C1 Vi                   |                 |                   |                 |                 |       |

|               |                                    | nnects to C2 V                    | IN-             |                   |                 |                 |       |

|               | When CM<2:                         |                                   |                 |                   |                 |                 |       |

|               |                                    | nnects to C1 V<br>nnects to C1 VI |                 |                   |                 |                 |       |

| bit 2-0       |                                    | mparator Mode                     |                 | oure 8-5)         |                 |                 |       |

|               |                                    |                                   |                 | figured as anal   | log             |                 |       |

|               | 001 = Three                        | inputs multiple>                  | ked to two cor  | mparators         | 0               |                 |       |

|               |                                    | puts multiplexe                   |                 |                   |                 |                 |       |

|               |                                    | ommon referend<br>dependent com   | -               | rs                |                 |                 |       |

|               |                                    | dependent con                     |                 |                   |                 |                 |       |

|               | 110 <b>= Two co</b>                | ommon referen                     | ce comparato    | rs with outputs   |                 |                 |       |

|               | 111 <b>= Compa</b>                 | arators off. CxIN                 | l pins are cor  | nfigured as digit | al I/O          |                 |       |

|               |                                    |                                   |                 |                   |                 |                 |       |

### REGISTER 8-1: CMCON0: COMPARATOR CONFIGURATION REGISTER

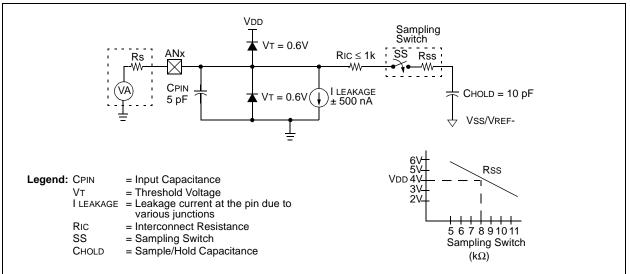

### 9.1 ADC Configuration

When configuring and using the ADC the following functions must be considered:

- Port configuration

- Channel selection

- ADC voltage reference selection

- ADC conversion clock source

- Interrupt control

- Results formatting

#### 9.1.1 PORT CONFIGURATION

The ADC can be used to convert both analog and digital signals. When converting analog signals, the I/O pin should be configured for analog by setting the associated TRIS and ANSEL bits. See the corresponding port section for more information.

| Note: | Analog voltages on any pin that is defined |  |  |  |  |

|-------|--------------------------------------------|--|--|--|--|

|       | as a digital input may cause the input     |  |  |  |  |

|       | buffer to conduct excess current.          |  |  |  |  |

#### 9.1.2 CHANNEL SELECTION

The CHS bits of the ADCON0 register determine which channel is connected to the sample and hold circuit.

When changing channels, a delay is required before starting the next conversion. Refer to **Section 9.2** "**ADC Operation**" for more information.

### 9.1.3 ADC VOLTAGE REFERENCE

The VCFG bit of the ADCON0 register provides control of the positive voltage reference. The positive voltage reference can be either VDD or an external voltage source. The negative voltage reference is always connected to the ground reference.

### 9.1.4 CONVERSION CLOCK

The source of the conversion clock is software selectable via the ADCS bits of the ADCON1 register. There are seven possible clock options:

- Fosc/2

- Fosc/4

- Fosc/8

- Fosc/16

- Fosc/32

- Fosc/64

- FRC (dedicated internal oscillator)

The time to complete one bit conversion is defined as TAD. One full 10-bit conversion requires 11 TAD periods as shown in Figure 9-3.

For correct conversion, the appropriate TAD specification must be met. See A/D conversion requirements in **Section 15.0** "**Electrical Specifications**" for more information. Table 9-1 gives examples of appropriate ADC clock selections.

**Note:** Unless using the FRC, any changes in the system clock frequency will change the ADC clock frequency, which may adversely affect the ADC result.

| ADC Clock F      | Period (TAD) |                         | Device Frequ            | uency (Fosc)                  |                               |

|------------------|--------------|-------------------------|-------------------------|-------------------------------|-------------------------------|

| ADC Clock Source | ADCS<2:0>    | 20 MHz                  | 8 MHz                   | 4 MHz                         | 1 MHz                         |

| Fosc/2           | 000          | 100 ns <sup>(2)</sup>   | 250 ns <sup>(2)</sup>   | 500 ns <sup>(2)</sup>         | 2.0 μs                        |

| Fosc/4           | 100          | 200 ns <sup>(2)</sup>   | 500 ns <sup>(2)</sup>   | 1.0 μs <b>(2)</b>             | 4.0 μs                        |

| Fosc/8           | 001          | 400 ns <sup>(2)</sup>   | 1.0 μs <sup>(2)</sup>   | 2.0 μs                        | 8.0 μs <b><sup>(3)</sup></b>  |

| Fosc/16          | 101          | 800 ns <sup>(2)</sup>   | 2.0 μs                  | 4.0 μs                        | 16.0 μs <b><sup>(3)</sup></b> |

| Fosc/32          | 010          | 1.6 μs                  | 4.0 μs                  | 8.0 μs <sup>(3)</sup>         | 32.0 μs <b><sup>(3)</sup></b> |

| Fosc/64          | 110          | 3.2 μs                  | 8.0 μs <sup>(3)</sup>   | 16.0 μs <b><sup>(3)</sup></b> | 64.0 μs <sup>(3)</sup>        |

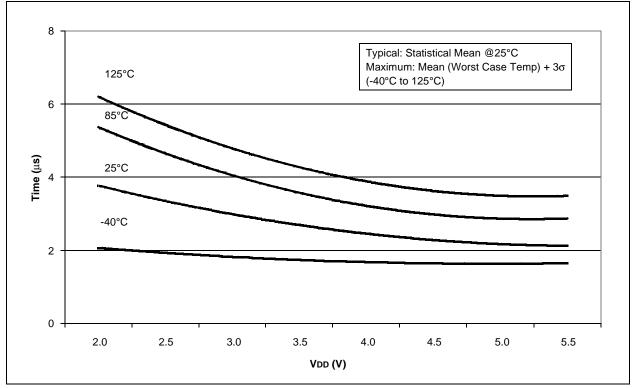

| Frc              | x11          | 2-6 μs <sup>(1,4)</sup> | 2-6 μs <sup>(1,4)</sup> | 2-6 μs <sup>(1,4)</sup>       | 2-6 μs <sup>(1,4)</sup>       |

### TABLE 9-1: ADC CLOCK PERIOD (TAD) Vs. DEVICE OPERATING FREQUENCIES (VDD > 3.0V)

Legend: Shaded cells are outside of recommended range.

Note 1: The FRC source has a typical TAD time of 4  $\mu$ s for VDD > 3.0V.

2: These values violate the minimum required TAD time.

**3:** For faster conversion times, the selection of another clock source is recommended.

4: When the device frequency is greater than 1 MHz, the FRC clock source is only recommended if the conversion will be performed during Sleep.

### EXAMPLE 9-1: A/D CONVERSION

| BANKSELADCON1;MOVLWB'01110000';ADC Frc clockMOVWFADCON1;BANKSELTRISA;BSFTRISA,0;Set RA0 to inputBANKSELANSEL;BSFANSEL,0;Set RA0 to analogBANKSELADCON0;MOVLWB'1000001';Right justify,MOVWFADCON0; Vdd Vref, AN0, OnCALLSampleTime;Acquisiton delayBSFADCON0,GO;Start conversionBTFSCADCON0,GO;Is conversion done?GOTO\$-1;No, test againBANKSELADRESH;MOVFADRESH,W;Read upper 2 bitsMOVFRESULTHI;store in GPR spaceBANKSELADRESL;MOVFRESULTLO;Store in GPR space | ;for poll<br>;and AN0<br>;<br>;Conversi | <pre>;This code block configures the ADC<br/>;for polling, Vdd reference, Frc clock<br/>;and AN0 input.<br/>;<br/>;Conversion start &amp; polling for completion<br/>; are included.</pre> |                      |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--|--|--|--|

| MOVLWB'01110000';ADC Frc clockMOVWFADCON1;BANKSELTRISA;BSFTRISA,0;Set RA0 to inputBANKSELANSEL;BSFANSEL,0;Set RA0 to analogBANKSELADCON0;MOVLWB'10000001';Right justify,MOVWFADCON0; Vdd Vref, AN0, OnCALLSampleTime;Acquisiton delayBSFADCON0,GO;Is conversionBTFSCADCON0,GO;Is conversion done?GOTO\$-1;No, test againBANKSELADRESH;MOVFADRESH,W;Read upper 2 bitsMOVFRESULTHI;store in GPR spaceBANKSELADRESL;MOVFADRESL,W;Read lower 8 bits                  | -                                       | ADCON1                                                                                                                                                                                     | :                    |  |  |  |  |

| MOVWFADCON1BANKSELTRISABSFTRISA,0BSFTRISA,0BANKSELANSELBSFANSEL,0BANKSELADCON0MOVLWB'1000001'BYADCON0CALLSampleTimeBSFADCON0,GOBTFSCADCON0,GOGOTO\$-1BANKSELADRESHMOVFADRESH,WKMOVFRESULTHIBANKSELADRESLMOVFADRESLMOVFADRESL,WKMOVFADRESL,W                                                                                                                                                                                                                      |                                         |                                                                                                                                                                                            | ,<br>;ADC Frc clock  |  |  |  |  |

| BANKSELTRISA;BSFTRISA,0;Set RA0 to inputBANKSELANSEL;BSFANSEL,0;Set RA0 to analogBANKSELADCON0;MOVLWB'1000001';Right justify,MOVWFADCON0; Vdd Vref, AN0, OnCALLSampleTime;Acquisiton delayBSFADCON0,GO; Start conversionBTFSCADCON0,GO; Is conversion done?GOTO\$-1;No, test againBANKSELADRESH;MOVFRESULTHI;store in GPR spaceBANKSELADRESL;MOVFADRESL,W;Read lower 8 bits                                                                                      | MOVWF                                   |                                                                                                                                                                                            |                      |  |  |  |  |

| BANKSEL ANSEL ;<br>BSF ANSEL,0 ;Set RA0 to analog<br>BANKSEL ADCON0 ;<br>MOVLW B'10000001' ;Right justify,<br>MOVWF ADCON0 ; Vdd Vref, AN0, On<br>CALL SampleTime ;Acquisiton delay<br>BSF ADCON0,GO ;Start conversion<br>BTFSC ADCON0,GO ;Is conversion done?<br>GOTO \$-1 ;No, test again<br>BANKSEL ADRESH ;<br>MOVF ADRESH,W ;Read upper 2 bits<br>MOVWF RESULTHI ;store in GPR space<br>BANKSEL ADRESL ;<br>MOVF ADRESL,W ;Read lower 8 bits                | BANKSEL                                 | TRISA                                                                                                                                                                                      | ;                    |  |  |  |  |

| BSFANSEL,0;Set RA0 to analogBANKSELADCON0;MOVLWB'1000001';Right justify,MOVWFADCON0; Vdd Vref, AN0, OnCALLSampleTime;Acquisiton delayBSFADCON0,GO;Start conversionBTFSCADCON0,GO;Is conversion done?GOTO\$-1;No, test againBANKSELADRESH;MOVFADRESH,W;Read upper 2 bitsMOVFFRESULTHI;store in GPR spaceBANKSELADRESL;MOVFADRESL,W;Read lower 8 bits                                                                                                              | BSF                                     | TRISA,0                                                                                                                                                                                    | ;Set RA0 to input    |  |  |  |  |

| BANKSELADCON0;MOVLWB'10000001';Right justify,MOVWFADCON0; Vdd Vref, AN0, OnCALLSampleTime;Acquisiton delayBSFADCON0,GO;Start conversionBTFSCADCON0,GO;Is conversion done?GOTO\$-1;No, test againBANKSELADRESH;MOVFADRESH,W;Read upper 2 bitsMOVFRESULTHI;store in GPR spaceBANKSELADRESL;MOVFADRESL,W;Read lower 8 bits                                                                                                                                          | BANKSEL                                 | ANSEL                                                                                                                                                                                      | ;                    |  |  |  |  |

| MOVLWB'10000001';Right justify,MOVWFADCON0; Vdd Vref, AN0, OnCALLSampleTime;Acquisiton delayBSFADCON0,GO;Start conversionBTFSCADCON0,GO;Is conversion done?GOTO\$-1;No, test againBANKSELADRESH;MOVFADRESH,W;Read upper 2 bitsMOVWFRESULTHI;store in GPR spaceBANKSELADRESL;MOVFADRESL,W;Read lower 8 bits                                                                                                                                                       | BSF                                     | ANSEL,0                                                                                                                                                                                    | ;Set RA0 to analog   |  |  |  |  |

| MOVWFADCON0; Vdd Vref, AN0, OnCALLSampleTime;Acquisiton delayBSFADCON0,GO;Start conversionBTFSCADCON0,GO;Is conversion done?GOTO\$-1;No, test againBANKSELADRESH;MOVFADRESH,W;Read upper 2 bitsMOVWFRESULTHI;store in GPR spaceBANKSELADRESL;MOVFADRESL,W;Read lower 8 bits                                                                                                                                                                                      | BANKSEL                                 | ADCON0                                                                                                                                                                                     | ;                    |  |  |  |  |

| CALL SampleTime ;Acquisiton delay<br>BSF ADCON0,GO ;Start conversion<br>BTFSC ADCON0,GO ;Is conversion done?<br>GOTO \$-1 ;No, test again<br>BANKSEL ADRESH ;<br>MOVF ADRESH,W ;Read upper 2 bits<br>MOVWF RESULTHI ;store in GPR space<br>BANKSEL ADRESL ;<br>MOVF ADRESL,W ;Read lower 8 bits                                                                                                                                                                  | MOVLW                                   | B'10000001'                                                                                                                                                                                | ;Right justify,      |  |  |  |  |

| BSFADCON0,GO;Start conversionBTFSCADCON0,GO;Is conversion done?GOTO\$-1;No, test againBANKSELADRESH;MOVFADRESH,W;Read upper 2 bitsMOVWFRESULTHI;store in GPR spaceBANKSELADRESL;MOVFADRESL,W;Read lower 8 bits                                                                                                                                                                                                                                                   | MOVWF                                   | ADCON0                                                                                                                                                                                     | ; Vdd Vref, ANO, On  |  |  |  |  |

| BTFSCADCON0,GO; Is conversion done?GOTO\$-1;No, test againBANKSELADRESH;MOVFADRESH,W;Read upper 2 bitsMOVWFRESULTHI;store in GPR spaceBANKSELADRESL;MOVFADRESL,W;Read lower 8 bits                                                                                                                                                                                                                                                                               | CALL                                    | SampleTime                                                                                                                                                                                 | ;Acquisiton delay    |  |  |  |  |

| GOTO\$-1;No, test againBANKSELADRESH;MOVFADRESH,W;Read upper 2 bitsMOVWFRESULTHI;store in GPR spaceBANKSELADRESL;MOVFADRESL,W;Read lower 8 bits                                                                                                                                                                                                                                                                                                                  | BSF                                     | ADCON0,GO                                                                                                                                                                                  | ;Start conversion    |  |  |  |  |

| BANKSELADRESH;MOVFADRESH,W;Read upper 2 bitsMOVWFRESULTHI;store in GPR spaceBANKSELADRESL;MOVFADRESL,W;Read lower 8 bits                                                                                                                                                                                                                                                                                                                                         | BTFSC                                   | ADCON0,GO                                                                                                                                                                                  | ;Is conversion done? |  |  |  |  |

| MOVFADRESH,W;Read upper 2 bitsMOVWFRESULTHI;store in GPR spaceBANKSELADRESL;MOVFADRESL,W;Read lower 8 bits                                                                                                                                                                                                                                                                                                                                                       | GOTO                                    | \$-1                                                                                                                                                                                       | ;No, test again      |  |  |  |  |

| MOVWFRESULTHI; store in GPR spaceBANKSELADRESL;MOVFADRESL,W; Read lower 8 bits                                                                                                                                                                                                                                                                                                                                                                                   | BANKSEL                                 | ADRESH                                                                                                                                                                                     | ;                    |  |  |  |  |

| BANKSEL ADRESL ;<br>MOVF ADRESL,W ;Read lower 8 bits                                                                                                                                                                                                                                                                                                                                                                                                             | MOVF                                    | ADRESH,W                                                                                                                                                                                   | ;Read upper 2 bits   |  |  |  |  |

| MOVF ADRESL,W ;Read lower 8 bits                                                                                                                                                                                                                                                                                                                                                                                                                                 | MOVWF                                   | RESULTHI                                                                                                                                                                                   | ;store in GPR space  |  |  |  |  |

| - , ,                                                                                                                                                                                                                                                                                                                                                                                                                                                            | BANKSEL                                 | ADRESL                                                                                                                                                                                     | ;                    |  |  |  |  |

| MOVWF RESULTLO ;Store in GPR space                                                                                                                                                                                                                                                                                                                                                                                                                               | MOVF                                    | ADRESL,W                                                                                                                                                                                   | ;Read lower 8 bits   |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | MOVWF                                   | RESULTLO                                                                                                                                                                                   | ;Store in GPR space  |  |  |  |  |

### 10.0 DATA EEPROM MEMORY

The EEPROM data memory is readable and writable during normal operation (full VDD range). This memory is not directly mapped in the register file space. Instead, it is indirectly addressed through the Special Function Registers. There are four SFRs used to read and write this memory:

- EECON1

- EECON2 (not a physically implemented register)

- EEDAT

- EEADR

EEDAT holds the 8-bit data for read/write, and EEADR holds the address of the EEPROM location being accessed. PIC16F684 has 256 bytes of data EEPROM with an address range from 0h to FFh.

The EEPROM data memory allows byte read and write. A byte write automatically erases the location and writes the new data (erase before write). The EEPROM data memory is rated for high erase/write cycles. The write time is controlled by an on-chip timer. The write time will vary with voltage and temperature as well as from chip-to-chip. Please refer to AC Specifications in Section 15.0 "Electrical Specifications" for exact limits.

When the data memory is code-protected, the CPU may continue to read and write the data EEPROM memory. The device programmer can no longer access the data EEPROM data and will read zeroes.

| R/W-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| EEDAT7 | EEDAT6 | EEDAT5 | EEDAT4 | EEDAT3 | EEDAT2 | EEDAT1 | EEDAT0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

|        |        |        |        |        |        |        |        |

REGISTER 10-1: EEDAT: EEPROM DATA REGISTER

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 7-0 EEDATn: Byte Value to Write To or Read From Data EEPROM bits

#### REGISTER 10-2: EEADR: EEPROM ADDRESS REGISTER

| R/W-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| EEADR7 | EEADR6 | EEADR5 | EEADR4 | EEADR3 | EEADR2 | EEADR1 | EEADR0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | 1 as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 7-0 EEADR: Specifies One of 256 Locations for EEPROM Read/Write Operation bits

### 10.2 Reading the EEPROM Data Memory

To read a data memory location, the user must write the address to the EEADR register and then set control bit RD of the EECON1 register, as shown in Example 10-1. The data is available, at the very next cycle, in the EEDAT register. Therefore, it can be read in the next instruction. EEDAT holds this value until another read, or until it is written to by the user (during a write operation).

| EXAMPLE 10-1: | DATA EEPROM READ |

|---------------|------------------|

|               |                  |

| BANKSEL | EEADR       | ;                |

|---------|-------------|------------------|

| MOVLW   | CONFIG_ADDR | i                |

| MOVWF   | EEADR       | ;Address to read |

| BSF     | EECON1,RD   | ;EE Read         |

| MOVF    | EEDAT,W     | ;Move data to W  |

|         |             |                  |

### 10.3 Writing to the EEPROM Data Memory

To write an EEPROM data location, the user must first write the address to the EEADR register and the data to the EEDAT register. Then the user must follow a specific sequence to initiate the write for each byte, as shown in Example 10-2.

EXAMPLE 10-2: DATA EEPROM WRITE

| -   |         |             |                  |

|-----|---------|-------------|------------------|

|     | BANKSEL | EECON1      | i                |

|     | BSF     | EECON1,WREN | ;Enable write    |

|     | BCF     | INTCON,GIE  | ;Disable INTs    |

|     | BTFSC   | INTCON,GIE  | ;See AN576       |

|     | GOTO    | \$-2        | ;                |

|     | MOVLW   | 55h         | ;Unlock write    |

| red | MOVWF   | EECON2      | ;                |

| qui | MOVLW   | AAh         | ;                |

| Re  | MOVWF   | EECON2      | ;                |

|     | BSF     | EECON1,WR   | ;Start the write |

|     | BSF     | INTCON,GIE  | ;Enable INTS     |

|     |         |             |                  |

The write will not initiate if the above sequence is not exactly followed (write 55h to EECON2, write AAh to EECON2, then set WR bit) for each byte. We strongly recommend that interrupts be disabled during this code segment. A cycle count is executed during the required sequence. Any number that is not equal to the required cycles to execute the required sequence will prevent the data from being written into the EEPROM.

Additionally, the WREN bit in EECON1 must be set to enable write. This mechanism prevents accidental writes to data EEPROM due to errant (unexpected) code execution (i.e., lost programs). The user should keep the WREN bit clear at all times, except when updating EEPROM. The WREN bit is not cleared by hardware. After a write sequence has been initiated, clearing the WREN bit will not affect this write cycle. The WR bit will be inhibited from being set unless the WREN bit is set.

At the completion of the write cycle, the WR bit is cleared in hardware and the EE Write Complete Interrupt Flag bit (EEIF) is set. The user can either enable this interrupt or poll this bit. The EEIF bit of the PIR1 register must be cleared by software.

### 10.4 Write Verify

Depending on the application, good programming practice may dictate that the value written to the data EEPROM should be verified (see Example 10-3) to the desired value to be written.

| <b>EXAMPLE 10-3</b> | : WRITE | VERIFY |

|---------------------|---------|--------|

|                     |         |        |

| BANKSE | ELEEDAT   | ;                    |

|--------|-----------|----------------------|

| MOVF   | EEDAT,W   | ;EEDAT not changed   |

|        |           | ;from previous write |

| BSF    | EECON1,RD | ;YES, Read the       |

|        |           | ;value written       |

| XORWF  | EEDAT,W   |                      |

| BTFSS  | STATUS,Z  | ;Is data the same    |

| GOTO   | WRITE_ERR | ;No, handle error    |

| :      |           | ;Yes, continue       |

|        |           |                      |

### 10.4.1 USING THE DATA EEPROM

The data EEPROM is a high-endurance, byte addressable array that has been optimized for the storage of frequently changing information (e.g., program variables or other data that are updated often). When variables in one section change frequently, while variables in another section do not change, it is possible to exceed the total number of write cycles to the EEPROM (specification D124) without exceeding the total number of write cycles to a single byte (specifications D120 and D120A). If this is the case, then a refresh of the array must be performed. For this reason, variables that change infrequently (such as constants, IDs, calibration, etc.) should be stored in Flash program memory.

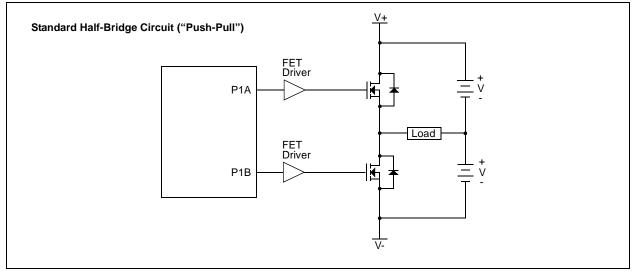

### 11.4 PWM (Enhanced Mode)

The Enhanced PWM Mode can generate a PWM signal on up to four different output pins with up to 10-bits of resolution. It can do this through four different PWM output modes:

- Single PWM

- Half-Bridge PWM

- Full-Bridge PWM, Forward mode

- Full-Bridge PWM, Reverse mode

To select an Enhanced PWM mode, the P1M bits of the CCP1CON register must be set appropriately.

The PWM outputs are multiplexed with I/O pins and are designated P1A, P1B, P1C and P1D. The polarity of the PWM pins is configurable and is selected by setting the CCP1M bits in the CCP1CON register appropriately.

Table 11-4 shows the pin assignments for each Enhanced PWM mode.

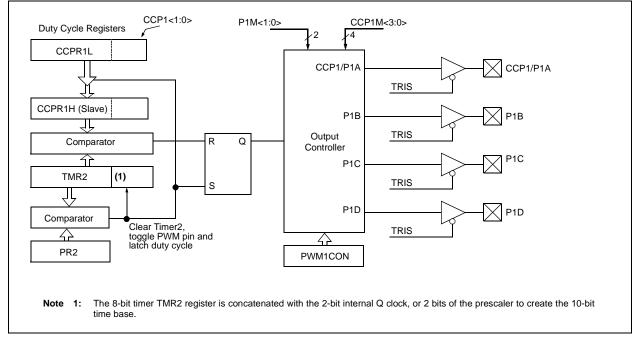

Figure 11-5 shows an example of a simplified block diagram of the Enhanced PWM module.

Note: To prevent the generation of an incomplete waveform when the PWM is first enabled, the ECCP module waits until the start of a new PWM period before generating a PWM signal.

#### FIGURE 11-5: EXAMPLE SIMPLIFIED BLOCK DIAGRAM OF THE ENHANCED PWM MODE

Note 1: The TRIS register value for each PWM output must be configured appropriately.

- 2: Clearing the CCP1CON register will relinquish ECCP control of all PWM output pins.

- 3: Any pin not used by an Enhanced PWM mode is available for alternate pin functions

#### TABLE 11-4: EXAMPLE PIN ASSIGNMENTS FOR VARIOUS PWM ENHANCED MODES

| ECCP Mode            | P1M | CCP1/P1A | P1B | P1C | P1D |

|----------------------|-----|----------|-----|-----|-----|

| Single               | 00  | Yes      | No  | No  | No  |

| Half-Bridge          | 10  | Yes      | Yes | No  | No  |

| Full-Bridge, Forward | 01  | Yes      | Yes | Yes | Yes |

| Full-Bridge, Reverse | 11  | Yes      | Yes | Yes | Yes |

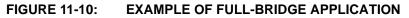

#### 11.4.2 FULL-BRIDGE MODE

In Full-Bridge mode, all four pins are used as outputs. An example of full-bridge application is shown in Figure 11-10.

In the Forward mode, pin CCP1/P1A is driven to its active state, pin P1D is modulated, while P1B and P1C will be driven to their inactive state as shown in Figure 11-11.

In the Reverse mode, P1C is driven to its active state, pin P1B is modulated, while P1A and P1D will be driven to their inactive state as shown Figure 11-11.

P1A, P1B, P1C and P1D outputs are multiplexed with the PORT data latches. The associated TRIS bits must be cleared to configure the P1A, P1B, P1C and P1D pins as outputs.

### 11.4.4 ENHANCED PWM AUTO-SHUTDOWN MODE

The PWM mode supports an Auto-Shutdown mode that will disable the PWM outputs when an external shutdown event occurs. Auto-Shutdown mode places the PWM output pins into a predetermined state. This mode is used to help prevent the PWM from damaging the application.

The auto-shutdown sources are selected using the ECCPASx bits of the ECCPAS register. A shutdown event may be generated by:

- A logic '0' on the INT pin

- · Comparator 1

- Comparator 2

- Setting the ECCPASE bit in firmware

A shutdown condition is indicated by the ECCPASE (Auto-Shutdown Event Status) bit of the ECCPAS register. If the bit is a '0', the PWM pins are operating normally. If the bit is a '1', the PWM outputs are in the shutdown state.

When a shutdown event occurs, two things happen:

The ECCPASE bit is set to '1'. The ECCPASE will remain set until cleared in firmware or an auto-restart occurs (see **Section 11.4.5 "Auto-Restart Mode"**).

The enabled PWM pins are asynchronously placed in their shutdown states. The PWM output pins are grouped into pairs [P1A/P1C] and [P1B/P1D]. The state of each pin pair is determined by the PSSAC and PSSBD bits of the ECCPAS register. Each pin pair may be placed into one of three states:

- Drive logic '1'

- Drive logic '0'

- Tri-state (high-impedance)

#### REGISTER 11-2: ECCPAS: ENHANCED CAPTURE/COMPARE/PWM AUTO-SHUTDOWN CONTROL REGISTER

| U-0     | U-0     | R/W-0   | R/W-0   | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|---------|---------|---------|---------|--------|--------|--------|--------|

| ECCPASE | ECCPAS2 | ECCPAS1 | ECCPAS0 | PSSAC1 | PSSAC0 | PSSBD1 | PSSBD0 |

| bit 7   |         |         |         |        |        |        | bit 0  |

|         |         |         |         |        |        |        |        |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

| bit 7   | ECCPASE: ECCP Auto-Shutdown Event Status bit                                                                                   |

|---------|--------------------------------------------------------------------------------------------------------------------------------|

|         | <ul><li>1 = A shutdown event has occurred; ECCP outputs are in shutdown state</li><li>0 = ECCP outputs are operating</li></ul> |

| bit 6-4 | ECCPAS<2:0>: ECCP Auto-shutdown Source Select bits                                                                             |

|         | 000 = Auto-Shutdown is disabled                                                                                                |

|         | 001 = Comparator 1 output change                                                                                               |

|         | 010 = Comparator 2 output change                                                                                               |

|         | 011 = Either Comparator 1 or 2 change                                                                                          |

|         | 100 = VIL on INT pin                                                                                                           |

|         | 101 = VIL on INT pin or Comparator 1 change                                                                                    |

|         | 110 = VIL on INT pin or Comparator 2 change                                                                                    |

|         | 111 = VIL on INT pin or Comparator 1 or 2 change                                                                               |

| bit 3-2 | PSSACn: Pins P1A and P1C Shutdown State Control bits                                                                           |

|         | 00 = Drive pins P1A and P1C to '0'                                                                                             |

|         | 01 = Drive pins P1A and P1C to '1'                                                                                             |

|         | 1x = Pins P1A and P1C tri-state                                                                                                |

| bit 1-0 | PSSBDn: Pins P1B and P1D Shutdown State Control bits                                                                           |

|         | 00 = Drive pins P1B and P1D to '0'                                                                                             |

|         | 01 = Drive pins P1B and P1D to '1'                                                                                             |

|         | 1x = Pins P1B and P1D tri-state                                                                                                |

|         |                                                                                                                                |

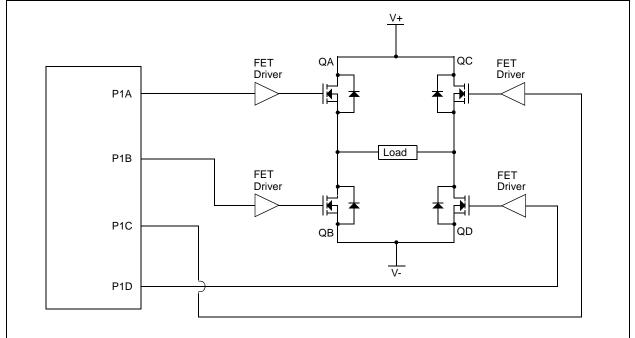

#### 11.4.6 PROGRAMMABLE DEAD-BAND DELAY MODE

In half-bridge applications where all power switches are modulated at the PWM frequency, the power switches normally require more time to turn off than to turn on. If both the upper and lower power switches are switched at the same time (one turned on, and the other turned off), both switches may be on for a short period of time until one switch completely turns off. During this brief interval, a very high current (*shoot-through current*) will flow through both power switches, shorting the bridge supply. To avoid this potentially destructive shoot-through current from flowing during switching, turning on either of the power switches is normally delayed to allow the other switch to completely turn off.

In Half-Bridge mode, a digitally programmable dead-band delay is available to avoid shoot-through current from destroying the bridge power switches. The delay occurs at the signal transition from the non-active state to the active state. See Section FIGURE 11-17: "Example of Half-Bridge Applications" for illustration. The lower seven bits of the associated PWM1CON register (Register 11-3) sets the delay period in terms of microcontroller instruction cycles (TcY or 4 Tosc).

### FIGURE 11-16: EXAMPLE OF HALF-BRIDGE PWM OUTPUT

### FIGURE 11-17: EXAMPLE OF HALF-BRIDGE APPLICATIONS

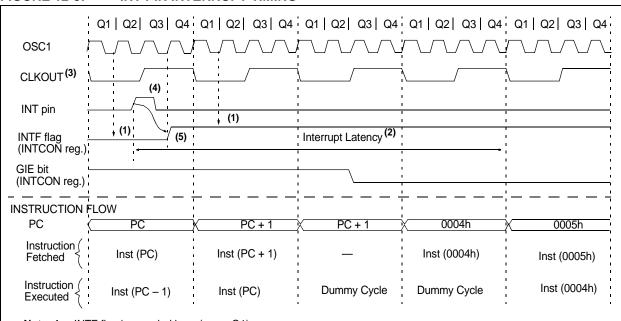

#### FIGURE 12-8: INT PIN INTERRUPT TIMING

Note 1: INTF flag is sampled here (every Q1).

- 2: Asynchronous interrupt latency = 3-4 TCY. Synchronous latency = 3 TCY, where TCY = instruction cycle time. Latency is the same whether Inst (PC) is a single cycle or a 2-cycle instruction.

- 3: CLKOUT is available only in INTOSC and RC Oscillator modes.

- 4: For minimum width of INT pulse, refer to AC specifications in Section 15.0 "Electrical Specifications".

- 5: INTF is enabled to be set any time during the Q4-Q1 cycles.

#### TABLE 12-6: SUMMARY OF REGISTERS ASSOCIATED WITH INTERRUPTS

| Name   | Bit 7 | Bit 6 | Bit 5  | Bit 4 | Bit 3 | Bit 2 | Bit 1  | Bit 0  | Value on:<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|-------|-------|--------|-------|-------|-------|--------|--------|-----------------------|---------------------------------|

| INTCON | GIE   | PEIE  | T0IE   | INTE  | RAIE  | T0IF  | INTF   | RAIF   | 0000 0000             | 0000 0000                       |

| IOCA   | —     |       | IOCA5  | IOCA4 | IOCA3 | IOCA2 | IOCA1  | IOCA0  | 00 0000               | 00 0000                         |

| PIR1   | EEIF  | ADIF  | CCP1IF | C2IF  | C1IF  | OSFIF | TMR2IF | TMR1IF | 0000 0000             | 0000 0000                       |

| PIE1   | EEIE  | ADIE  | CCP1IE | C2IE  | C1IE  | OSFIE | TMR2IE | TMR1IE | 0000 0000             | 0000 0000                       |

**Legend:** x = unknown, u = unchanged, - = unimplemented read as '0', q = value depends upon condition. Shaded cells are not used by the interrupt module.

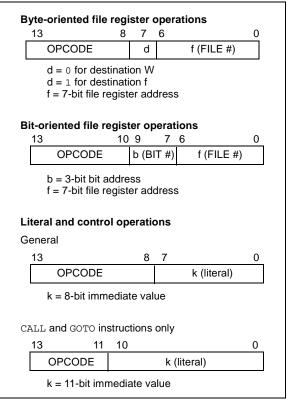

### 13.0 INSTRUCTION SET SUMMARY

The PIC16F684 instruction set is highly orthogonal and is comprised of three basic categories:

- Byte-oriented operations

- Bit-oriented operations

- Literal and control operations

Each PIC16 instruction is a 14-bit word divided into an **opcode**, which specifies the instruction type and one or more **operands**, which further specify the operation of the instruction. The formats for each of the categories is presented in Figure 13-1, while the various opcode fields are summarized in Table 13-1.

Table 13-2 lists the instructions recognized by the MPASM<sup>TM</sup> assembler.

For **byte-oriented** instructions, 'f' represents a file register designator and 'd' represents a destination designator. The file register designator specifies which file register is to be used by the instruction.

The destination designator specifies where the result of the operation is to be placed. If 'd' is zero, the result is placed in the W register. If 'd' is one, the result is placed in the file register specified in the instruction.

For **bit-oriented** instructions, 'b' represents a bit field designator, which selects the bit affected by the operation, while 'f' represents the address of the file in which the bit is located.

For **literal and control** operations, 'k' represents an 8-bit or 11-bit constant, or literal value.

One instruction cycle consists of four oscillator periods; for an oscillator frequency of 4 MHz, this gives a nominal instruction execution time of 1  $\mu$ s. All instructions are executed within a single instruction cycle, unless a conditional test is true, or the program counter is changed as a result of an instruction. When this occurs, the execution takes two instruction cycles, with the second cycle executed as a NOP.

All instruction examples use the format '0xhh' to represent a hexadecimal number, where 'h' signifies a hexadecimal digit.

### 13.1 Read-Modify-Write Operations

Any instruction that specifies a file register as part of the instruction performs a Read-Modify-Write (R-M-W) operation. The register is read, the data is modified, and the result is stored according to either the instruction, or the destination designator 'd'. A read operation is performed on a register even if the instruction writes to that register.

For example, a CLRF PORTA instruction will read PORTA, clear all the data bits, then write the result back to PORTA. This example would have the unintended consequence of clearing the condition that set the RAIF flag.

#### TABLE 13-1: OPCODE FIELD DESCRIPTIONS

| Field | Description                                                                                                                                                                       |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f     | Register file address (0x00 to 0x7F)                                                                                                                                              |

| W     | Working register (accumulator)                                                                                                                                                    |

| b     | Bit address within an 8-bit file register                                                                                                                                         |

| k     | Literal field, constant data or label                                                                                                                                             |

| x     | Don't care location (= $0$ or 1).<br>The assembler will generate code with x = $0$ .<br>It is the recommended form of use for<br>compatibility with all Microchip software tools. |

| d     | Destination select; $d = 0$ : store result in W,<br>d = 1: store result in file register f.<br>Default is $d = 1$ .                                                               |

| PC    | Program Counter                                                                                                                                                                   |

| TO    | Time-out bit                                                                                                                                                                      |

| С     | Carry bit                                                                                                                                                                         |

| DC    | Digit carry bit                                                                                                                                                                   |

| Z     | Zero bit                                                                                                                                                                          |

| PD    | Power-down bit                                                                                                                                                                    |

# FIGURE 13-1: GENERAL FORMAT FOR INSTRUCTIONS

| Mnem                                   | nonic,   | Description                                      |              |        | 14-Bit | Opcode | Status   |          |         |

|----------------------------------------|----------|--------------------------------------------------|--------------|--------|--------|--------|----------|----------|---------|

| Oper                                   | Operands |                                                  | Cycles       | MSb    |        |        | LSb      | Affected | Notes   |

| BYTE-ORIENTED FILE REGISTER OPERATIONS |          |                                                  |              |        |        |        |          |          |         |

| ADDWF                                  | f, d     | Add W and f                                      | 1            | 00     | 0111   | dfff   | ffff     | C, DC, Z | 1, 2    |

| ANDWF                                  | f, d     | AND W with f                                     | 1            | 00     | 0101   | dfff   | ffff     | Z        | 1, 2    |

| CLRF                                   | f        | Clear f                                          | 1            | 00     | 0001   | lfff   | ffff     | Z        | 2       |

| CLRW                                   | -        | Clear W                                          | 1            | 00     | 0001   | 0xxx   | xxxx     | Z        |         |

| COMF                                   | f, d     | Complement f                                     | 1            | 00     | 1001   | dfff   | ffff     | Z        | 1, 2    |

| DECF                                   | f, d     | Decrement f                                      | 1            | 00     | 0011   | dfff   | ffff     | Z        | 1, 2    |

| DECFSZ                                 | f, d     | Decrement f, Skip if 0                           | 1 <b>(2)</b> | 00     | 1011   | dfff   | ffff     |          | 1, 2, 3 |

| INCF                                   | f, d     | Increment f                                      | 1            | 00     | 1010   | dfff   | ffff     | Z        | 1, 2    |

| INCFSZ                                 | f, d     | Increment f, Skip if 0                           | 1 <b>(2)</b> | 00     | 1111   | dfff   | ffff     |          | 1, 2, 3 |

| IORWF                                  | f, d     | Inclusive OR W with f                            | 1            | 00     | 0100   | dfff   | ffff     | Z        | 1, 2    |

| MOVF                                   | f, d     | Move f                                           | 1            | 00     | 1000   | dfff   | ffff     | Z        | 1, 2    |

| MOVWF                                  | f        | Move W to f                                      | 1            | 0.0    | 0000   | lfff   |          |          | ,       |

| NOP                                    | _        | No Operation                                     | 1            | 0.0    | 0000   | 0xx0   | 0000     |          |         |

| RLF                                    | f, d     | Rotate Left f through Carry                      | 1            | 00     | 1101   | dfff   | ffff     | С        | 1, 2    |

| RRF                                    | f, d     | Rotate Right f through Carry                     | 1            | 0.0    | 1100   | dfff   |          | Ċ        | 1, 2    |

| SUBWF                                  | f. d     | Subtract W from f                                | 1            | 0.0    | 0010   |        | ffff     | C, DC, Z | 1, 2    |

| SWAPF                                  | f, d     | Swap nibbles in f                                | 1            | 00     | 1110   |        | ffff     | 0,20,2   | 1, 2    |

| XORWF                                  | f, d     | Exclusive OR W with f                            | 1            | 00     | 0110   |        | ffff     | Z        | 1, 2    |

| -                                      | , -      | BIT-ORIENTED FILE REGIST                         |              | RATION |        | -      |          |          | ,       |

| BCF                                    | f, b     | Bit Clear f                                      | 1            | 01     | -      | bfff   | ffff     |          | 1, 2    |

| BSF                                    | f, b     | Bit Set f                                        | 1            | 01     |        | bfff   |          |          | 1, 2    |

| BTFSC                                  | f, b     | Bit Test f, Skip if Clear                        | 1 <b>(2)</b> | 01     |        |        | ffff     |          | 3       |

| BTFSS                                  | f, b     | Bit Test f, Skip if Set                          | 1 (2)        | 01     | 11bb   | bfff   | ffff     |          | 3       |

| DI100                                  | Ι, Ο     |                                                  |              | -      | datt   | DIII   | LLLL     |          | J       |

| ADDLW                                  | k        | Add literal and W                                | 1            | 11     | 111.   | kkkk   | lelelele | C, DC, Z |         |

| ANDLW                                  | k        | AND literal with W                               | 1            | 11     | 1001   |        | kkkk     | C, DC, Z |         |

| CALL                                   | k k      | Call Subroutine                                  | 2            | 10     |        | kkkk   |          | 2        |         |

|                                        | к<br>—   | Clear Watchdog Timer                             | 1            | 00     | 0000   | 0110   | 0100     | TO, PD   |         |

| GOTO                                   | –<br>k   | Go to address                                    | 2            | 10     |        | kkkk   |          | 10, PD   |         |

|                                        |          |                                                  | 1            | -      |        |        |          | Z        |         |

|                                        | k        | Inclusive OR literal with W<br>Move literal to W | 1            | 11     |        | kkkk   |          | ۷        |         |

| MOVLW<br>RETFIE                        | k<br>—   |                                                  | 1            | 11     |        | kkkk   |          |          |         |

|                                        |          | Return from interrupt                            |              | 00     | 0000   | 0000   | 1001     |          |         |

| RETLW                                  | k        | Return with literal in W                         | 2            | 11     |        | kkkk   |          |          |         |

| RETURN                                 | -        | Return from Subroutine                           | 2            | 00     | 0000   | 0000   | 1000     | TO 55    |         |

| SLEEP                                  | -        | Go into Standby mode                             | 1            | 00     | 0000   | 0110   | 0011     | TO, PD   |         |

| SUBLW                                  | k        | Subtract W from literal                          | 1            | 11     | 110x   |        | kkkk     | C, DC, Z |         |

| XORLW                                  | k        | Exclusive OR literal with W                      | 1            | 11     | 1010   | kkkk   | kkkk     | Z        |         |

### TABLE 13-2: PIC16F684 INSTRUCTION SET

**Note 1:** When an I/O register is modified as a function of itself (e.g., MOVF GPIO, 1), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and where applicable, d = 1), the prescaler will be cleared if assigned to the Timer0 module.

**3:** If the Program Counter (PC) is modified, or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

### 15.4 DC Characteristics: PIC16F684-E (Extended)

| DC CHA |                              | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |       |      |       |     |                                               |  |  |

|--------|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-------|------|-------|-----|-----------------------------------------------|--|--|

| Param  | Device Characteristics       | Min                                                                                                                               | Trunt | Max  | Unite |     | Conditions                                    |  |  |

| No.    | Device Characteristics       | Min                                                                                                                               | Тур†  | Мах  | Units | Vdd | Note                                          |  |  |

| D020E  | Power-down Base              | _                                                                                                                                 | 0.05  | 9    | μA    | 2.0 | WDT, BOR, Comparators, VREF and               |  |  |

|        | Current (IPD) <sup>(2)</sup> |                                                                                                                                   | 0.15  | 11   | μA    | 3.0 | T1OSC disabled                                |  |  |

|        |                              | —                                                                                                                                 | 0.35  | 15   | μA    | 5.0 |                                               |  |  |

| D021E  |                              | _                                                                                                                                 | 1     | 17.5 | μΑ    | 2.0 | WDT Current <sup>(1)</sup>                    |  |  |

|        |                              |                                                                                                                                   | 2     | 19   | μA    | 3.0 |                                               |  |  |

|        |                              | _                                                                                                                                 | 3     | 22   | μΑ    | 5.0 |                                               |  |  |

| D022E  |                              | _                                                                                                                                 | 42    | 65   | μΑ    | 3.0 | BOR Current <sup>(1)</sup>                    |  |  |

|        |                              | _                                                                                                                                 | 85    | 127  | μΑ    | 5.0 |                                               |  |  |

| D023E  |                              | _                                                                                                                                 | 32    | 45   | μΑ    | 2.0 | Comparator Current <sup>(1)</sup> , both      |  |  |

|        |                              | _                                                                                                                                 | 60    | 78   | μΑ    | 3.0 | comparators enabled                           |  |  |

|        |                              | _                                                                                                                                 | 120   | 160  | μΑ    | 5.0 |                                               |  |  |

| D024E  |                              | _                                                                                                                                 | 30    | 70   | μΑ    | 2.0 | CVREF Current <sup>(1)</sup> (high range)     |  |  |

|        |                              | _                                                                                                                                 | 45    | 90   | μΑ    | 3.0 |                                               |  |  |

|        |                              | _                                                                                                                                 | 75    | 120  | μΑ    | 5.0 |                                               |  |  |

| D025E* |                              |                                                                                                                                   | 39    | 91   | μA    | 2.0 | CVREF Current <sup>(1)</sup> (low range)      |  |  |

|        |                              | _                                                                                                                                 | 59    | 117  | μA    | 3.0 |                                               |  |  |

|        |                              | _                                                                                                                                 | 98    | 156  | μΑ    | 5.0 |                                               |  |  |

| D026E  |                              |                                                                                                                                   | 4.5   | 25   | μA    | 2.0 | T1OSC Current <sup>(1)</sup> , 32.768 kHz     |  |  |

|        |                              | _                                                                                                                                 | 5     | 30   | μA    | 3.0 | ]                                             |  |  |

|        |                              | —                                                                                                                                 | 6     | 40   | μΑ    | 5.0 | 7                                             |  |  |

| D027E  |                              |                                                                                                                                   | 0.30  | 12   | μΑ    | 3.0 | A/D Current <sup>(1)</sup> , no conversion in |  |  |

|        |                              | _                                                                                                                                 | 0.36  | 16   | μA    | 5.0 | progress                                      |  |  |

\* These parameters are characterized but not tested.

† Data in 'Typ' column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** The peripheral current is the sum of the base IDD or IPD and the additional current consumed when this peripheral is enabled. The peripheral  $\Delta$  current can be determined by subtracting the base IDD or IPD current from this limit. Max values should be used when calculating total current consumption.

2: The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD.

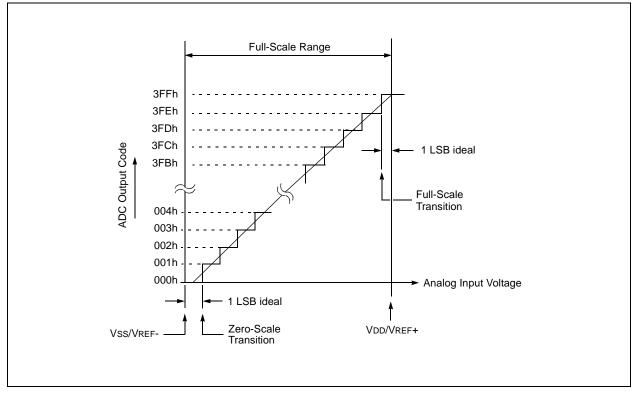

#### TABLE 15-9: PIC16F684 A/D CONVERTER (ADC) CHARACTERISTICS

|               | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |                                                      |            |      |          |       |                                                                     |  |  |  |  |

|---------------|----------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|------------|------|----------|-------|---------------------------------------------------------------------|--|--|--|--|

| Param<br>No.  | Sym                                                                                                                  | Characteristic                                       | Min        | Тур† | Мах      | Units | Conditions                                                          |  |  |  |  |

| AD01          | NR                                                                                                                   | Resolution                                           | —          | _    | 10 bits  | bit   |                                                                     |  |  |  |  |

| AD02          | EIL                                                                                                                  | Integral Error                                       | —          | —    | ±1       | LSb   | VREF = 5.12V                                                        |  |  |  |  |

| AD03          | Edl                                                                                                                  | Differential Error                                   | -          |      | ±1       | LSb   | No missing codes to 10 bits<br>VREF = 5.12V                         |  |  |  |  |

| AD04          | EOFF                                                                                                                 | Offset Error                                         | _          | _    | ±1       | LSb   | VREF = 5.12V                                                        |  |  |  |  |

| AD07          | Egn                                                                                                                  | Gain Error                                           | _          | _    | ±1       | LSb   | VREF = 5.12V                                                        |  |  |  |  |

| AD06<br>AD06A | Vref                                                                                                                 | Reference Voltage <sup>(3)</sup>                     | 2.2<br>2.7 | _    | —<br>Vdd | V     | Absolute minimum to ensure 1 LSb accuracy                           |  |  |  |  |

| AD07          | VAIN                                                                                                                 | Full-Scale Range                                     | Vss        | _    | Vref     | V     |                                                                     |  |  |  |  |

| AD08          | ZAIN                                                                                                                 | Recommended<br>Impedance of Analog<br>Voltage Source | —          | _    | 10       | kΩ    |                                                                     |  |  |  |  |

| AD09*         | IREF                                                                                                                 | VREF Input Current <sup>(3)</sup>                    | 10         | —    | 1000     | μA    | During VAIN acquisition.<br>Based on differential of VHOLD to VAIN. |  |  |  |  |

|               |                                                                                                                      |                                                      | —          | _    | 50       | μA    | During A/D conversion cycle.                                        |  |  |  |  |

\* These parameters are characterized but not tested.

† Data in 'Typ' column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** Total Absolute Error includes integral, differential, offset and gain errors.

2: The A/D conversion result never decreases with an increase in the input voltage and has no missing codes.

3: ADC VREF is from external VREF or VDD pin, whichever is selected as reference input.

4: When ADC is off, it will not consume any current other than leakage current. The power-down current specification includes any such leakage from the ADC module.

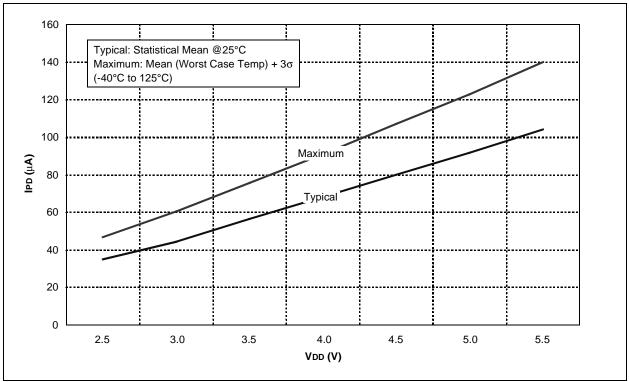

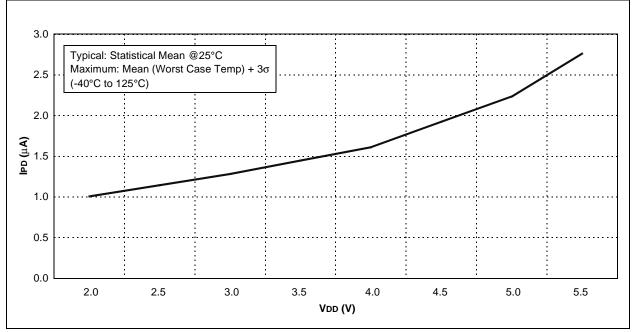

FIGURE 16-32: LFINTOSC FREQUENCY vs. Vdd OVER TEMPERATURE (31 kHz)

### U

| Ultra Low-Power Wake-Up                              | 6, 32, 34 |

|------------------------------------------------------|-----------|

| v                                                    |           |

| Voltage Reference. See Comparator Voltage<br>(CVREF) | Reference |

| Voltage References                                   |           |

| Associated Registers                                 | 64        |

| VREF. SEE ADC Reference Voltage                      |           |

### W

| Wake-up Using Interrupts |     |

|--------------------------|-----|

| Watchdog Timer (WDT)     |     |

| Associated Registers     | 111 |

| Clock Source             | 110 |

| Modes                    | 110 |

| Period                   | 110 |

| Specifications           |     |

| WDTCON Register          | 111 |

| WPUA Register            |     |

| WWW Address              |     |

| WWW, On-Line Support     |     |

## THE MICROCHIP WEB SITE

Microchip provides online support via our WWW site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- **Product Support** Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

### CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.