Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | AVR                                                                         |

| Core Size                  | 32-Bit Single-Core                                                          |

| Speed                      | 66MHz                                                                       |

| Connectivity               | EBI/EMI, Ethernet, I <sup>2</sup> C, SPI, SSC, UART/USART, USB OTG          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 109                                                                         |

| Program Memory Size        | 128KB (128K x 8)                                                            |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 32K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 3.6V                                                                |

| Data Converters            | A/D 8x10b                                                                   |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 144-LQFP                                                                    |

| Supplier Device Package    | 144-LQFP (20x20)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at32uc3a0128-alur |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Table 6-1.TQFP100 Package Pinout

| 23 | PA02 |

|----|------|

| 24 | PA03 |

| 25 | PA04 |

| 48 | DM  |  |  |  |  |

|----|-----|--|--|--|--|

| 49 | DP  |  |  |  |  |

| 50 | GND |  |  |  |  |

| 73 | PB05 |

|----|------|

| 74 | PB06 |

| 75 | PB07 |

|    |      |

| 98  | PB17 |

|-----|------|

| 99  | PB18 |

| 100 | PB19 |

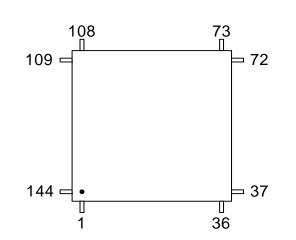

## Figure 6-2. LQFP144 Pinout

#### Table 6-2.VQFP144 Package Pinout

| 1  | PX00   |

|----|--------|

| 2  | PX01   |

| 3  | PB20   |

| 4  | PX02   |

| 5  | PB21   |

| 6  | PB22   |

| 7  | VDDIO  |

| 8  | GND    |

| 9  | PB23   |

| 10 | PX03   |

| 11 | PB24   |

| 12 | PX04   |

| 13 | PB25   |

| 14 | PB26   |

| 15 | PB27   |

| 16 | VDDOUT |

| 17 | VDDIN  |

| 18 | GND    |

| 19 | PB28   |

| 20 | PB29   |

| 21 | PB30   |

| erinoul |         |  |  |  |  |  |  |

|---------|---------|--|--|--|--|--|--|

| 37      | GND     |  |  |  |  |  |  |

| 38      | PX10    |  |  |  |  |  |  |

| 39      | PA05    |  |  |  |  |  |  |

| 40      | PX11    |  |  |  |  |  |  |

| 41      | PA06    |  |  |  |  |  |  |

| 42      | PX12    |  |  |  |  |  |  |

| 43      | PA07    |  |  |  |  |  |  |

| 44      | PX13    |  |  |  |  |  |  |

| 45      | PA08    |  |  |  |  |  |  |

| 46      | PX14    |  |  |  |  |  |  |

| 47      | PA09    |  |  |  |  |  |  |

| 48      | PA10    |  |  |  |  |  |  |

| 49      | N/C     |  |  |  |  |  |  |

| 50      | PA11    |  |  |  |  |  |  |

| 51      | VDDCORE |  |  |  |  |  |  |

| 52      | GND     |  |  |  |  |  |  |

| 53      | PA12    |  |  |  |  |  |  |

| 54      | PA13    |  |  |  |  |  |  |

| 55      | VDDCORE |  |  |  |  |  |  |

| 56      | PA14    |  |  |  |  |  |  |

| 57      | PA15    |  |  |  |  |  |  |

|         |         |  |  |  |  |  |  |

| 73 | PA21   |  |  |  |  |  |

|----|--------|--|--|--|--|--|

| 74 | PA22   |  |  |  |  |  |

| 75 | PA23   |  |  |  |  |  |

| 76 | PA24   |  |  |  |  |  |

| 77 | PA25   |  |  |  |  |  |

| 78 | PA26   |  |  |  |  |  |

| 79 | PA27   |  |  |  |  |  |

| 80 | PA28   |  |  |  |  |  |

| 81 | VDDANA |  |  |  |  |  |

| 82 | ADVREF |  |  |  |  |  |

| 83 | GNDANA |  |  |  |  |  |

| 84 | VDDPLL |  |  |  |  |  |

| 85 | PC00   |  |  |  |  |  |

| 86 | PC01   |  |  |  |  |  |

| 87 | PX20   |  |  |  |  |  |

| 88 | PB00   |  |  |  |  |  |

| 89 | PX21   |  |  |  |  |  |

| 90 | PB01   |  |  |  |  |  |

| 91 | PX22   |  |  |  |  |  |

| 92 | VDDIO  |  |  |  |  |  |

| 93 | VDDIO  |  |  |  |  |  |

| 109 | GND   |

|-----|-------|

| 110 | PX30  |

| 111 | PB08  |

| 112 | PX31  |

| 113 | PB09  |

| 114 | PX32  |

| 115 | PB10  |

| 116 | VDDIO |

| 117 | GND   |

| 118 | PX33  |

| 119 | PB11  |

| 120 | PX34  |

| 121 | PB12  |

| 122 | PA29  |

| 123 | PA30  |

| 124 | PC02  |

| 125 | PC03  |

| 126 | PB13  |

| 127 | PB14  |

| 128 | TMS   |

| 129 | TCK   |

|   | 1     | 2       | 3    | 4    | 5      | 6    | 7    | 8       |

|---|-------|---------|------|------|--------|------|------|---------|

| Α | VDDIO | PB07    | PB05 | PB02 | PB03   | PB01 | PC00 | PA28    |

| в | PB08  | GND     | PB06 | PB04 | VDDIO  | PB00 | PC01 | VDDPLL  |

| С | PB09  | PX33    | PA29 | PC02 | PX28   | PX26 | PX22 | PX21    |

| D | PB11  | PB13    | PB12 | PX30 | PX29   | PX25 | PX24 | PX20    |

| Е | PB10  | VDDIO   | PX32 | PX31 | VDDIO  | PX27 | PX23 | VDDANA  |

| F | PA30  | PB14    | PX34 | PB16 | тск    | GND  | GND  | PX16    |

| G | TMS   | PC03    | PX36 | PX35 | PX37   | GND  | GND  | PA16    |

| н | TDO   | VDDCORE | PX38 | PX39 | VDDIO  | PA01 | PA10 | VDDCORE |

| J | TDI   | PB17    | PB15 | PX00 | PX01   | PA00 | PA03 | PA04    |

| κ | PC05  | PC04    | PB19 | PB20 | PX02   | PB29 | PB30 | PA02    |

| L | PB21  | GND     | PB18 | PB24 | VDDOUT | PX04 | PB31 | VDDIN   |

| М | PB22  | PB23    | PB25 | PB26 | PX03   | PB27 | PB28 | RESET_N |

## Table 6-4.BGA144 Package Pinout A9..M12

|   | 9      | 10     | 11        | 12      |  |

|---|--------|--------|-----------|---------|--|

| Α | PA26   | PA25   | PA24      | PA23    |  |

| В | PA27   | PA21   | GND       | PA22    |  |

| С | ADVREF | GNDANA | PX19      | PA19    |  |

| D | PA18   | PA20   | DP        | DM      |  |

| Е | PX18   | PX17   | VDDIO     | VBUS    |  |

| F | PA17   | PX15   | PA15      | PA14    |  |

| G | PA13   | PA12   | PA11      | NC      |  |

| н | PX11   | PA08   | VDDCORE   | VDDCORE |  |

| J | PX14   | PA07   | PX13      | PA09    |  |

| к | PX08   | GND    | PA05 PX12 |         |  |

| L | PX06   | PX10   | GND       | PA06    |  |

| М | PX05   | PX07   | PX09      | VDDIO   |  |

Note: NC is not connected.

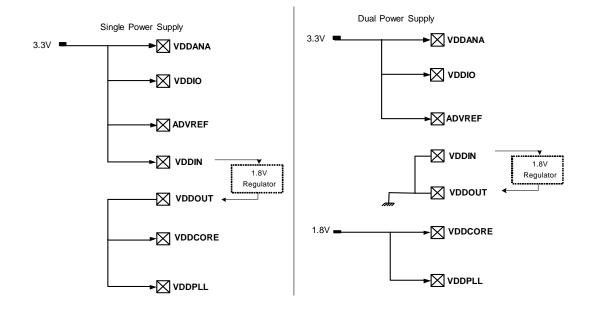

## 7. Power Considerations

## 7.1 Power Supplies

The AT32UC3A has several types of power supply pins:

- VDDIO: Powers I/O lines. Voltage is 3.3V nominal.

- VDDANA: Powers the ADC Voltage is 3.3V nominal.

- VDDIN: Input voltage for the voltage regulator. Voltage is 3.3V nominal.

- VDDCORE: Powers the core, memories, and peripherals. Voltage is 1.8V nominal.

- VDDPLL: Powers the PLL. Voltage is 1.8V nominal.

The ground pins GND are common to VDDCORE, VDDIO, VDDPLL. The ground pin for VDDANA is GNDANA.

Refer to "Power Consumption" on page 44 for power consumption on the various supply pins.

## 7.2 Voltage Regulator

#### 7.2.1 Single Power Supply

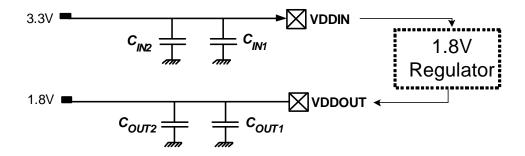

The AT32UC3A embeds a voltage regulator that converts from 3.3V to 1.8V. The regulator takes its input voltage from VDDIN, and supplies the output voltage on VDDOUT. VDDOUT should be externally connected to the 1.8V domains.

Adequate input supply decoupling is mandatory for VDDIN in order to improve startup stability and reduce source voltage drop. Two input decoupling capacitors must be placed close to the chip.

Adequate output supply decoupling is mandatory for VDDOUT to reduce ripple and avoid oscillations. The best way to achieve this is to use two capacitors in parallel between VDDOUT and GND as close to the chip as possible

Refer to Section 12.3 on page 42 for decoupling capacitors values and regulator characteristics

#### 7.2.2 Dual Power Supply

In case of dual power supply, VDDIN and VDDOUT should be connected to ground to prevent from leakage current.

| Part Number  | Flash Size<br>( <i>FLASH_PW</i> ) | Number of pages<br>(FLASH_P) | Page size<br>( <i>FLASH_W</i> ) | General Purpose<br>Fuse bits<br>(FLASH_F) |

|--------------|-----------------------------------|------------------------------|---------------------------------|-------------------------------------------|

| AT32UC3A0512 | 512 Kbytes                        | 1024                         | 128 words                       | 32 fuses                                  |

| AT32UC3A1512 | 512 Kbytes                        | 1024                         | 128 words                       | 32 fuses                                  |

| AT32UC3A0256 | 256 Kbytes                        | 512                          | 128 words                       | 32 fuses                                  |

| AT32UC3A1256 | 256 Kbytes                        | 512                          | 128 words                       | 32 fuses                                  |

| AT32UC3A1128 | 128 Kbytes                        | 256                          | 128 words                       | 32 fuses                                  |

| AT32UC3A0128 | 128 Kbytes                        | 256                          | 128 words                       | 32 fuses                                  |

**Table 9-2.**Flash Memory Parameters

### 9.3 Bus Matrix Connections

Accesses to unused areas returns an error result to the master requesting such an access.

The bus matrix has the several masters and slaves. Each master has its own bus and its own decoder, thus allowing a different memory mapping per master. The master number in the table below can be used to index the HMATRIX control registers. For example, MCFG0 is associated with the CPU Data master interface.

| Table 9-3. | High Speed bus masters |

|------------|------------------------|

| Master 0   | CPU Data               |

| Master 1   | CPU Instruction        |

| Master 2   | CPU SAB                |

| Master 3   | PDCA                   |

| Master 4   | MACB DMA               |

| Master 5   | USBB DMA               |

Table 9-3.High Speed Bus masters

Each slave has its own arbiter, thus allowing a different arbitration per slave. The slave number in the table below can be used to index the HMATRIX control registers. For example, SCFG3 is associated with the Internal SRAM Slave Interface.

| Table 9-4. | High Speed Bus slaves |

|------------|-----------------------|

|------------|-----------------------|

|         | •               |

|---------|-----------------|

| Slave 0 | Internal Flash  |

| Slave 1 | HSB-PB Bridge 0 |

| Slave 2 | HSB-PB Bridge 1 |

| Slave 3 | Internal SRAM   |

| Slave 4 | USBB DPRAM      |

| Slave 5 | EBI             |

|    | interrupt Request | l Signal Map                      |        |

|----|-------------------|-----------------------------------|--------|

| 9  | 0                 | Serial Peripheral Interface       | SPI0   |

| 10 | 0                 | Serial Peripheral Interface       | SPI1   |

| 11 | 0                 | Two-wire Interface                | TWI    |

| 12 | 0                 | Pulse Width Modulation Controller | PWM    |

| 13 | 0                 | Synchronous Serial Controller     | SSC    |

|    | 0                 | Timer/Counter                     | TC0    |

| 14 | 1                 | Timer/Counter                     | TC1    |

|    | 2                 | Timer/Counter                     | TC2    |

| 15 | 0                 | Analog to Digital Converter       | ADC    |

| 16 | 0                 | Ethernet MAC                      | MACB   |

| 17 | 0                 | USB 2.0 OTG Interface             | USBB   |

| 18 | 0                 | SDRAM Controller                  | SDRAMC |

| 19 | 0                 | Audio Bitstream DAC               | DAC    |

Table 10-3.

Interrupt Request Signal Map

## **10.4 Clock Connections**

#### 10.4.1 Timer/Counters

Each Timer/Counter channel can independently select an internal or external clock source for its counter:

| Source   | Name         | Connection        |

|----------|--------------|-------------------|

| Internal | TIMER_CLOCK1 | 32 KHz Oscillator |

|          | TIMER_CLOCK2 | PBA clock / 2     |

|          | TIMER_CLOCK3 | PBA clock / 8     |

|          | TIMER_CLOCK4 | PBA clock / 32    |

|          | TIMER_CLOCK5 | PBA clock / 128   |

| External | XC0          | See Section 10.7  |

|          | XC1          |                   |

|          | XC2          |                   |

Table 10-4.

Timer/Counter clock connections

#### 10.4.2 USARTs

Each USART can be connected to an internally divided clock:

| USART | Source   | Name    | Connection    |  |  |  |  |  |

|-------|----------|---------|---------------|--|--|--|--|--|

| 0     | Internal | CLK_DIV | PBA clock / 8 |  |  |  |  |  |

| 1     |          |         |               |  |  |  |  |  |

| 2     |          |         |               |  |  |  |  |  |

| 3     |          |         |               |  |  |  |  |  |

Table 10-5. USART clock connections

Table 10-9.

GPIO Controller Function Multiplexing

| Table 10-9. |     | roller Functio |          | 1              |               |              |

|-------------|-----|----------------|----------|----------------|---------------|--------------|

| 7           | 11  | PB24           | GPIO 56  | TC - B0        | USART1 - DSR  |              |

| 8           | 13  | PB25           | GPIO 57  | TC - A1        | USART1 - DTR  |              |

| 9           | 14  | PB26           | GPIO 58  | TC - B1        | USART1 - RI   |              |

| 10          | 15  | PB27           | GPIO 59  | TC - A2        | PWM - PWM[4]  |              |

| 14          | 19  | PB28           | GPIO 60  | TC - B2        | PWM - PWM[5]  |              |

| 15          | 20  | PB29           | GPIO 61  | USART2 - RXD   | PM - GCLK[1]  | EBI - NCS[2] |

| 16          | 21  | PB30           | GPIO 62  | USART2 - TXD   | PM - GCLK[2]  | EBI - SDCS   |

| 17          | 22  | PB31           | GPIO 63  | USART2 - CLK   | PM - GCLK[3]  | EBI - NWAIT  |

| 63          | 85  | PC00           | GPIO 64  |                |               |              |

| 64          | 86  | PC01           | GPIO 65  |                |               |              |

| 85          | 124 | PC02           | GPIO 66  |                |               |              |

| 86          | 125 | PC03           | GPIO 67  |                |               |              |

| 93          | 132 | PC04           | GPIO 68  |                |               |              |

| 94          | 133 | PC05           | GPIO 69  |                |               |              |

|             | 1   | PX00           | GPIO 100 | EBI - DATA[10] | USART0 - RXD  |              |

|             | 2   | PX01           | GPIO 99  | EBI - DATA[9]  | USART0 - TXD  |              |

|             | 4   | PX02           | GPIO 98  | EBI - DATA[8]  | USART0 - CTS  |              |

|             | 10  | PX03           | GPIO 97  | EBI - DATA[7]  | USART0 - RTS  |              |

|             | 12  | PX04           | GPIO 96  | EBI - DATA[6]  | USART1 - RXD  |              |

|             | 24  | PX05           | GPIO 95  | EBI - DATA[5]  | USART1 - TXD  |              |

|             | 26  | PX06           | GPIO 94  | EBI - DATA[4]  | USART1 - CTS  |              |

|             | 31  | PX07           | GPIO 93  | EBI - DATA[3]  | USART1 - RTS  |              |

|             | 33  | PX08           | GPIO 92  | EBI - DATA[2]  | USART3 - RXD  |              |

|             | 35  | PX09           | GPIO 91  | EBI - DATA[1]  | USART3 - TXD  |              |

|             | 38  | PX10           | GPIO 90  | EBI - DATA[0]  | USART2 - RXD  |              |

|             | 40  | PX11           | GPIO 109 | EBI - NWE1     | USART2 - TXD  |              |

|             | 42  | PX12           | GPIO 108 | EBI - NWE0     | USART2 - CTS  |              |

|             | 44  | PX13           | GPIO 107 | EBI - NRD      | USART2 - RTS  |              |

|             | 46  | PX14           | GPIO 106 | EBI - NCS[1]   |               | TC - A0      |

|             | 59  | PX15           | GPIO 89  | EBI - ADDR[19] | USART3 - RTS  | TC - B0      |

|             | 61  | PX16           | GPIO 88  | EBI - ADDR[18] | USART3 - CTS  | TC - A1      |

|             | 63  | PX17           | GPIO 87  | EBI - ADDR[17] |               | TC - B1      |

|             | 65  | PX18           | GPIO 86  | EBI - ADDR[16] |               | TC - A2      |

|             | 67  | PX19           | GPIO 85  | EBI - ADDR[15] | EIM - SCAN[0] | TC - B2      |

|             | 87  | PX20           | GPIO 84  | EBI - ADDR[14] | EIM - SCAN[1] | TC - CLK0    |

|             | 89  | PX21           | GPIO 83  | EBI - ADDR[13] | EIM - SCAN[2] | TC - CLK1    |

|             | 91  | PX22           | GPIO 82  | EBI - ADDR[12] | EIM - SCAN[3] | TC - CLK2    |

|             | 95  | PX23           | GPIO 81  | EBI - ADDR[11] | EIM - SCAN[4] |              |

|             | 97  | PX24           | GPIO 80  | EBI - ADDR[10] | EIM - SCAN[5] |              |

|             |     |                |          | L - 1          | L-1           |              |

AT32UC3A

## 12.2 DC Characteristics

The following characteristics are applicable to the operating temperature range:  $T_A = -40^{\circ}$ C to 85°C, unless otherwise specified and are certified for a junction temperature up to  $T_J = 100^{\circ}$ C.

| Table 12-1. DO | C Characteristics |

|----------------|-------------------|

|----------------|-------------------|

| Symbol                                   | Parameter                                                                                | Condition                                                                                         | Min.                        | Тур. | Мах  | Units |

|------------------------------------------|------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|-----------------------------|------|------|-------|

| V <sub>VDDCOR</sub><br>e                 | DC Supply Core                                                                           |                                                                                                   | 1.65                        |      | 1.95 | V     |

| V <sub>VDDPLL</sub>                      | DC Supply PLL                                                                            |                                                                                                   | 1.65                        |      | 1.95 | V     |

| V <sub>VDDIO</sub>                       | DC Supply Peripheral I/Os                                                                |                                                                                                   | 3.0                         |      | 3.6  | V     |

| V <sub>REF</sub>                         | Analog reference voltage                                                                 |                                                                                                   | 2.6                         |      | 3.6  | V     |

| V <sub>IL</sub>                          | Input Low-level Voltage                                                                  |                                                                                                   | -0.3                        |      | +0.8 | V     |

| V <sub>IH</sub>                          | Input High-level Voltage                                                                 | All GPIOS except for PC00, PC01, PC02, PC03, PC04, PC05.                                          | 2.0                         |      | 5.5V | V     |

|                                          |                                                                                          | PC00, PC01, PC02, PC03, PC04, PC05.                                                               | 2.0                         |      | 3.6V | V     |

|                                          |                                                                                          | I <sub>OL</sub> =-4mA for PA0-PA20, PB0, PB4-PB9,<br>PB11-PB18, PB24-PB26, PB29-PB31,<br>PX0-PX39 |                             |      | 0.4  | V     |

| V <sub>OL</sub> Output Low-level Voltage | I <sub>OL</sub> =-8mA for PA21-PA30, PB1-PB3,<br>PB10, PB19-PB23, PB27-PB28, PC0-<br>PC5 |                                                                                                   |                             | 0.4  | V    |       |

| V <sub>OH</sub>                          | Output High-level Voltage                                                                | I <sub>OH</sub> =4mA for PA0-PA20, PB0, PB4-PB9,<br>PB11-PB18, PB24-PB26, PB29-PB31,<br>PX0-PX39  | V <sub>VDDIO</sub> -<br>0.4 |      |      | V     |

| Ön                                       |                                                                                          | I <sub>OH</sub> =8mA for PA21-PA30, PB1-PB3,<br>PB10, PB19-PB23, PB27-PB28, PC0-<br>PC5           | V <sub>VDDIO</sub> -<br>0.4 |      |      | V     |

| I <sub>OL</sub>                          |                                                                                          | PA0-PA20, PB0, PB4-PB9, PB11-PB18,<br>PB24-PB26, PB29-PB31, PX0-PX39                              |                             |      | -4   | mA    |

|                                          | Output Low-level Current                                                                 | PA21-PA30, PB1-PB3, PB10, PB19-<br>PB23, PB27-PB28, PC0-PC5                                       |                             |      | -8   | mA    |

| I <sub>ОН</sub>                          |                                                                                          | PA0-PA20, PB0, PB4-PB9, PB11-PB18,<br>PB24-PB26, PB29-PB31, PX0-PX39                              |                             |      | 4    | mA    |

|                                          | Output High-level Current                                                                | PA21-PA30, PB1-PB3, PB10, PB19-<br>PB23, PB27-PB28, PC0-PC5                                       |                             |      | 8    | mA    |

| I <sub>LEAK</sub>                        | Input Leakage Current                                                                    | Pullup resistors disabled                                                                         |                             |      | 1    | μA    |

| C <sub>IN</sub>                          |                                                                                          | TQFP100 Package                                                                                   |                             | 7    |      | pF    |

| Input Cap                                | acitance                                                                                 | LQFP144 Package                                                                                   |                             | 7    |      | pF    |

| R <sub>PULLUP</sub>                      | Pull-up Resistance                                                                       | All GPIO and RESET_N pin.                                                                         | 10K                         | 15K  |      | Ohm   |

## 12.3 Regulator characteristics

Table 12-2.

Electrical characteristics

| Symbol              | Parameter                                         | Condition                                                         | Min. | Тур. | Max. | Units |

|---------------------|---------------------------------------------------|-------------------------------------------------------------------|------|------|------|-------|

| $V_{\text{VDDIN}}$  | Supply voltage (input)                            |                                                                   | 3    | 3.3  | 3.6  | V     |

| V <sub>VDDOUT</sub> | Supply voltage (output)                           |                                                                   | 1.81 | 1.85 | 1.89 | V     |

|                     | Maximum DC output current with $V_{VDDIN = 3.3V}$ |                                                                   |      |      | 100  | mA    |

| OUT                 | Maximum DC output current with $V_{VDDIN = 2.7V}$ |                                                                   |      |      | 90   | mA    |

| I <sub>SCR</sub>    | Static Current of internal regulator              | Low Power mode (stop, deep stop or static) at $T_A = 25^{\circ}C$ |      | 10   |      | μA    |

#### Table 12-3.Decoupling requirements

| Symbol            | Parameter                    | Condition | Тур. | Techno. | Units |

|-------------------|------------------------------|-----------|------|---------|-------|

| C <sub>IN1</sub>  | Input Regulator Capacitor 1  |           | 1    | NPO     | nF    |

| C <sub>IN2</sub>  | Input Regulator Capacitor 2  |           | 4.7  | X7R     | uF    |

| C <sub>OUT1</sub> | Output Regulator Capacitor 1 |           | 470  | NPO     | pF    |

| C <sub>OUT2</sub> | Output Regulator Capacitor 2 |           | 2.2  | X7R     | uF    |

## 12.4 Analog characteristics

Table 12-4. Electrical characteristics

| Symbol  | Parameter                        | Condition | Min. | Тур. | Max. | Units |

|---------|----------------------------------|-----------|------|------|------|-------|

| VADVREF | Analog voltage reference (input) |           | 2.6  |      | 3.6  | V     |

#### **Table 12-5.**Decoupling requirements

| Symbol             | Parameter                     | Condition | Тур. | Techno | Units |

|--------------------|-------------------------------|-----------|------|--------|-------|

| C <sub>VREF1</sub> | Voltage reference Capacitor 1 |           | 10   | -      | nF    |

| C <sub>VREF2</sub> | Voltage reference Capacitor 2 |           | 1    | -      | uF    |

12.4.1 BOD

Table 12-6.BODLEVEL Values

| BODLEVEL Value | Тур. | Тур. | Тур. | Units. |

|----------------|------|------|------|--------|

| 00 0000b       | 1.40 | 1.47 | 1.55 | V      |

| 01 0111b       | 1.45 | 1.52 | 1.6  | V      |

| 01 1111b       | 1.55 | 1.6  | 1.65 | V      |

| 10 0111b       | 1.65 | 1.69 | 1.75 | V      |

The values in Table 12-6 describes the values of the BODLEVEL in the flash FGPFR register.

## Table 12-7. BOD Timing

| Symbol           | Parameter                                                      | Test Conditions                      | Тур. | Max. | Units. |

|------------------|----------------------------------------------------------------|--------------------------------------|------|------|--------|

| T <sub>BOD</sub> | Minimum time with<br>VDDCORE < VBOD to<br>detect power failure | Falling VDDCORE<br>from 1.8V to 1.1V | 300  | 800  | ns     |

#### 12.4.2 POR

#### Table 12-8. Electrical Characteristic

| Symbol               | Parameter                                                                                                                            | Test Conditions                                              | Min. | Тур. | Max. | Units. |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|------|------|------|--------|

| V <sub>DDRR</sub>    | VDDCORE rise rate to ensure power-on-reset                                                                                           |                                                              | 0.01 |      |      | V/ms   |

| V <sub>SSFR</sub>    | VDDCORE fall rate to ensure power-on-reset                                                                                           |                                                              | 0.01 |      | 400  | V/ms   |

| V <sub>POR+</sub>    | Rising threshold voltage: voltage up to which device is kept under reset by POR on rising VDDCORE                                    | Rising VDDCORE:<br>V <sub>RESTART</sub> -> V <sub>POR+</sub> | 1.35 | 1.5  | 1.6  | v      |

| V <sub>POR-</sub>    | Falling threshold voltage: voltage when POR resets device on falling VDDCORE                                                         | Falling VDDCORE:<br>1.8V -> V <sub>POR+</sub>                | 1.25 | 1.3  | 1.4  | V      |

| V <sub>RESTART</sub> | On falling VDDCORE, voltage must go down to this value before supply can rise again to ensure reset signal is released at $V_{POR+}$ | Falling VDDCORE:<br>1.8V -> V <sub>RESTART</sub>             | -0.1 |      | 0.5  | v      |

| T <sub>POR</sub>     | Minimum time with VDDCORE < V <sub>POR</sub> .                                                                                       | Falling VDDCORE:<br>1.8V -> 1.1V                             |      | 15   |      | us     |

| T <sub>RST</sub>     | Time for reset signal to be propagated to system                                                                                     |                                                              |      | 200  | 400  | us     |

## 12.9 EBI Timings

These timings are given for worst case process, T = 85·C, VDDCORE = 1.65V, VDDIO = 3V and 40 pF load capacitance.

| Symbol                  | Parameter                      | Max <sup>(1)</sup>      | Units |

|-------------------------|--------------------------------|-------------------------|-------|

| 1/(t <sub>CPSMC</sub> ) | SMC Controller Clock Frequency | 1/(t <sub>cpcpu</sub> ) | MHz   |

Note: 1. The maximum frequency of the SMC interface is the same as the max frequency for the HSB.

#### Table 12-23. SMC Read Signals with Hold Settings

| Symbol            | Parameter                                  | Min                                                             | Units |

|-------------------|--------------------------------------------|-----------------------------------------------------------------|-------|

|                   | NRD C                                      | ontrolled (READ_MODE = 1)                                       |       |

| SMC <sub>1</sub>  | Data Setup before NRD High                 | 12                                                              |       |

| SMC <sub>2</sub>  | Data Hold after NRD High                   | 0                                                               |       |

| SMC <sub>3</sub>  | NRD High to NBS0/A0 Change <sup>(1)</sup>  | nrd hold length * t <sub>CPSMC</sub> - 1.3                      |       |

| SMC <sub>4</sub>  | NRD High to NBS1 Change <sup>(1)</sup>     | nrd hold length * t <sub>CPSMC</sub> - 1.3                      |       |

| SMC <sub>5</sub>  | NRD High to NBS2/A1 Change <sup>(1)</sup>  | nrd hold length * t <sub>CPSMC</sub> - 1.3                      | ns    |

| SMC <sub>6</sub>  | NRD High to NBS3 Change <sup>(1)</sup>     | nrd hold length * t <sub>CPSMC</sub> - 1.3                      |       |

| SMC <sub>7</sub>  | NRD High to A2 - A25 Change <sup>(1)</sup> | nrd hold length * t <sub>CPSMC</sub> - 1.3                      |       |

| SMC <sub>8</sub>  | NRD High to NCS Inactive <sup>(1)</sup>    | (nrd hold length - ncs rd hold length) * $t_{CPSMC}$ - 2.3      |       |

| SMC <sub>9</sub>  | NRD Pulse Width                            | nrd pulse length * t <sub>CPSMC</sub> - 1.4                     |       |

|                   | NRD C                                      | ontrolled (READ_MODE = 0)                                       | I     |

| SMC <sub>10</sub> | Data Setup before NCS High                 | 11.5                                                            |       |

| SMC <sub>11</sub> | Data Hold after NCS High                   | 0                                                               |       |

| SMC <sub>12</sub> | NCS High to NBS0/A0 Change <sup>(1)</sup>  | ncs rd hold length * t <sub>CPSMC</sub> - 2.3                   |       |

| SMC <sub>13</sub> | NCS High to NBS0/A0 Change <sup>(1)</sup>  | ncs rd hold length * t <sub>CPSMC</sub> - 2.3                   |       |

| SMC <sub>14</sub> | NCS High to NBS2/A1 Change <sup>(1)</sup>  | ncs rd hold length * t <sub>CPSMC</sub> - 2.3                   | ns    |

| SMC <sub>15</sub> | NCS High to NBS3 Change <sup>(1)</sup>     | ncs rd hold length * t <sub>CPSMC</sub> - 2.3                   |       |

| SMC <sub>16</sub> | NCS High to A2 - A25 Change <sup>(1)</sup> | ncs rd hold length * t <sub>CPSMC</sub> - 4                     |       |

| SMC <sub>17</sub> | NCS High to NRD Inactive <sup>(1)</sup>    | ncs rd hold length - nrd hold length)* t <sub>CPSMC</sub> - 1.3 |       |

| SMC <sub>18</sub> | NCS Pulse Width                            | ncs rd pulse length * t <sub>CPSMC</sub> - 3.6                  |       |

Note: 1. hold length = total cycle duration - setup duration - pulse duration. "hold length" is for "ncs rd hold length" or "nrd hold length".

## Table 12-30. SPI Timings

| Symbol            | Parameter                                  | Conditions                 | Min                        | Max  | Units |

|-------------------|--------------------------------------------|----------------------------|----------------------------|------|-------|

| SPI0              | MISO Setup time before SPCK rises (master) | 3.3V domain <sup>(1)</sup> | $22 + (t_{CPMCK})/2^{(2)}$ |      | ns    |

| SPI <sub>1</sub>  | MISO Hold time after SPCK rises (master)   | 3.3V domain <sup>(1)</sup> | 0                          |      | ns    |

| SPI <sub>2</sub>  | SPCK rising to MOSI Delay (master)         | 3.3V domain <sup>(1)</sup> |                            | 7    | ns    |

| SPI <sub>3</sub>  | MISO Setup time before SPCK falls (master) | 3.3V domain <sup>(1)</sup> | $22 + (t_{CPMCK})/2^{(2)}$ |      | ns    |

| SPI <sub>4</sub>  | MISO Hold time after SPCK falls (master)   | 3.3V domain <sup>(1)</sup> | 0                          |      | ns    |

| SPI <sub>5</sub>  | SPCK falling to MOSI Delay (master)        | 3.3V domain <sup>(1)</sup> |                            | 7    | ns    |

| SPI <sub>6</sub>  | SPCK falling to MISO Delay (slave)         | 3.3V domain <sup>(1)</sup> |                            | 26.5 | ns    |

| SPI7              | MOSI Setup time before SPCK rises (slave)  | 3.3V domain <sup>(1)</sup> | 0                          |      | ns    |

| SPI <sub>8</sub>  | MOSI Hold time after SPCK rises (slave)    | 3.3V domain <sup>(1)</sup> | 1.5                        |      | ns    |

| SPI <sub>9</sub>  | SPCK rising to MISO Delay (slave)          | 3.3V domain <sup>(1)</sup> |                            | 27   | ns    |

| SPI <sub>10</sub> | MOSI Setup time before SPCK falls (slave)  | 3.3V domain <sup>(1)</sup> | 0                          |      | ns    |

| SPI <sub>11</sub> | MOSI Hold time after SPCK falls (slave)    | 3.3V domain <sup>(1)</sup> | 1                          |      | ns    |

Notes: 1. 3.3V domain:  $V_{VDDIO}$  from 3.0V to 3.6V, maximum external capacitor = 40 pF.

2.  $t_{CPMCK}$ : Master Clock period in ns.

## **12.12 MACB Characteristics**

## Table 12-31. Ethernet MAC Signals

| Symbol            | Parameter                        | Conditions                | Min (ns) | Max (ns) |

|-------------------|----------------------------------|---------------------------|----------|----------|

| EMAC <sub>1</sub> | Setup for EMDIO from EMDC rising | Load: 20pF <sup>(2)</sup> |          |          |

| EMAC <sub>2</sub> | Hold for EMDIO from EMDC rising  | Load: 20pF <sup>(2)</sup> |          |          |

| EMAC <sub>3</sub> | EMDIO toggling from EMDC falling | Load: 20pF <sup>(2)</sup> |          |          |

Notes: 1. f: MCK frequency (MHz)

2.  $V_{VDDIO}$  from 3.0V to 3.6V, maximum external capacitor = 20 pF

## Table 12-32. Ethernet MAC MII Specific Signals

| Symbol             | Parameter                        | Conditions                | Min (ns) | Max (ns) |

|--------------------|----------------------------------|---------------------------|----------|----------|

| EMAC <sub>4</sub>  | Setup for ECOL from ETXCK rising | Load: 20pF <sup>(1)</sup> | 3        |          |

| EMAC <sub>5</sub>  | Hold for ECOL from ETXCK rising  | Load: 20pF <sup>(1)</sup> | 0        |          |

| EMAC <sub>6</sub>  | Setup for ECRS from ETXCK rising | Load: 20pF <sup>(1)</sup> | 3        |          |

| EMAC <sub>7</sub>  | Hold for ECRS from ETXCK rising  | Load: 20pF <sup>(1)</sup> | 0        |          |

| EMAC <sub>8</sub>  | ETXER toggling from ETXCK rising | Load: 20pF <sup>(1)</sup> |          | 15       |

| EMAC <sub>9</sub>  | ETXEN toggling from ETXCK rising | Load: 20pF <sup>(1)</sup> |          | 15       |

| EMAC <sub>10</sub> | ETX toggling from ETXCK rising   | Load: 20pF <sup>(1)</sup> |          | 15       |

| EMAC <sub>11</sub> | Setup for ERX from ERXCK         | Load: 20pF <sup>(1)</sup> | 1        |          |

# **13. Mechanical Characteristics**

## 13.1 Thermal Considerations

### 13.1.1 Thermal Data

Table 13-1 summarizes the thermal resistance data depending on the package.

| Symbol               | Parameter                              | Condition | Package | Тур  | Unit |

|----------------------|----------------------------------------|-----------|---------|------|------|

| $\theta_{JA}$        | Junction-to-ambient thermal resistance | Still Air | TQFP100 | 43.4 | CAN  |

| θ <sub>JC</sub>      | Junction-to-case thermal resistance    |           | TQFP100 | 5.5  | ·C/W |

| $\theta_{JA}$        | Junction-to-ambient thermal resistance | Still Air | LQFP144 | 39.8 | 0.00 |

| $\theta_{\text{JC}}$ | Junction-to-case thermal resistance    |           | LQFP144 | 8.9  | ·C/W |

Table 13-1.

Thermal Resistance Data

#### 13.1.2 Junction Temperature

The average chip-junction temperature, T<sub>J</sub>, in °C can be obtained from the following:

1.

$$T_J = T_A + (P_D \times \theta_{JA})$$

2.  $T_J = T_A + (P_D \times (\theta_{HEATSINK} + \theta_{JC}))$

where:

- θ<sub>JA</sub> = package thermal resistance, Junction-to-ambient (°C/W), provided in Table 13-1 on page 64.

- $\theta_{JC}$  = package thermal resistance, Junction-to-case thermal resistance (°C/W), provided in Table 13-1 on page 64.

- $\theta_{HEAT SINK}$  = cooling device thermal resistance (°C/W), provided in the device datasheet.

- P<sub>D</sub> = device power consumption (W) estimated from data provided in the section "Power Consumption" on page 44.

- T<sub>A</sub> = ambient temperature (°C).

From the first equation, the user can derive the estimated lifetime of the chip and decide if a cooling device is necessary or not. If a cooling device is to be fitted on the chip, the second equation should be used to compute the resulting average chip-junction temperature  $T_J$  in °C.

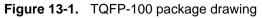

## 13.2 Package Drawings

#### Table 13-2. Device and Package Maximum Weight

| 500 mg |

|--------|

|--------|

### Table 13-3. Package Characteristics

| Moisture Sensitivity Level | Jdec J-STD0-20D - MSL 3 |

|----------------------------|-------------------------|

|----------------------------|-------------------------|

#### Table 13-4.Package Reference

| JEDEC Drawing Reference | MS-026 |

|-------------------------|--------|

| JESD97 Classification   | E3     |

## 13.3 Soldering Profile

Table 13-11 gives the recommended soldering profile from J-STD-20.

| Profile Feature                            | Green Package            |

|--------------------------------------------|--------------------------|

| Average Ramp-up Rate (217°C to Peak)       | 3°C/sec                  |

| Preheat Temperature 175°C ±25°C            | Min. 150 °C, Max. 200 °C |

| Time Maintained Above 217°C                | 60-150 sec               |

| Time within 5.C of Actual Peak Temperature | 30 sec                   |

| Peak Temperature Range                     | 260 °C                   |

| Ramp-down Rate                             | 6 °C/sec                 |

| Time 25 C to Peak Temperature              | Max. 8 minutes           |

Note: It is recommended to apply a soldering temperature higher than 250°C. A maximum of three reflow passes is allowed per component.

None.

#### 15.2.9 USART

ISO7816 info register US\_NER cannot be read The NER register always returns zero.

Fix/Workaround None

#### 15.2.10 Processor and Architecture

1. LDM instruction with PC in the register list and without ++ increments Rp For LDM with PC in the register list: the instruction behaves as if the ++ field is always set, ie the pointer is always updated. This happens even if the ++ field is cleared. Specifically, the increment of the pointer is done in parallel with the testing of R12.

Fix/Workaround

None.

#### 2. RETE instruction does not clear SREG[L] from interrupts.

The RETE instruction clears  $\mbox{SREG}[L]$  as expected from exceptions.  $\mbox{Fix/Workaround}$

When using the STCOND instruction, clear SREG[L] in the stacked value of SR before returning from interrupts with RETE.

#### 3. Exceptions when system stack is protected by MPU

RETS behaves incorrectly when MPU is enabled and MPU is configured so that system stack is not readable in unprivileged mode.

#### **Fix/Woraround**

Workaround 1: Make system stack readable in unprivileged mode, or

Workaround 2: Return from supervisor mode using rete instead of rets. This requires :

1. Changing the mode bits from 001b to 110b before issuing the instruction. Updating the mode bits to the desired value must be done using a single mtsr instruction so it is done atomically. Even if this step is described in general as not safe in the UC technical reference guide, it is safe in this very specific case.

2. Execute the RETE instruction.

When multiple CS are in use, if one of the baudrate equals 1, the other must also equal 1 if CPOL=1 and CPHA=0.

# 4. SPI Glitch on RXREADY flag in slave mode when enabling the SPI or during the first transfer

In slave mode, the SPI can generate a false RXREADY signal during enabling of the SPI or during the first transfer.

#### **Fix/Workaround**

- 1. Set slave mode, set required CPOL/CPHA.

- 2. Enable SPI.

- 3. Set the polarity CPOL of the line in the opposite value of the required one.

- 4. Set the polarity CPOL to the required one.

- 5. Read the RXHOLDING register.

Transfers can now befin and RXREADY will now behave as expected.

#### 5. SPI Disable does not work in Slave mode Fix/workaround

Read the last received data then perform a Software reset.

#### 15.3.4 Power Manager

1. If the BOD level is higher than VDDCORE, the part is constantly under reset

If the BOD level is set to a value higher than VDDCORE and enabled by fuses, the part will be in constant reset.

#### **Fix/Workaround**

Apply an external voltage on VDDCORE that is higher than the BOD level and is lower than VDDCORE max and disable the BOD.

#### 15.3.5 Flashc

# 1. On AT32UC3A0512 and AT32UC3A1512, corrupted read in flash after FLASHC WP, EP, EA, WUP, EUP commands may happen

- After a FLASHC Write Page (WP) or Erase Page (EP) command applied to a page in a given half of the flash (first or last 256 kB of flash), reading (data read or code fetch) the other half of the flash may fail. This may lead to an exception or to other errors derived from this corrupted read access.

After a FLASHC Erase All (EA) command, reading (data read or code fetch) the flash may fail. This may lead to an exception or to other errors derived from this corrupted read access.

After a FLASHC Write User Page (WUP) or Erase User Page (EUP) command, reading (data read or code fetch) the second half (last 256 kB) of the flash may fail. This may lead to an exception or to other errors derived from this corrupted read access.

#### Fix/Workaround

Flashc WP, EP, EA, WUP, EUP commands: these commands must be issued from RAM or through the EBI. After these commands, read twice one flash page initialized to 00h in each half part of the flash.

15.3.6 PDCA

1. Wrong PDCA behavior when using two PDCA channels with the same PID.

# AT32UC3A

specific case. 2. Execute the RETE instruction.

AT32UC3A

#### Fix/Workaround

In PLL0/1 Control register, the bit 7 should be set in order to prevent unexpected behaviour.

4. Peripheral Bus A maximum frequency is 33MHz instead of 66MHz. Fix/Workaround

Do not set PBA frequency higher than 33 MHz.

#### 5. PCx pins go low in stop mode

In sleep mode stop all PCx pins will be controlled by GPIO module instead of oscillators. This can cause drive contention on the XINx in worst case.

#### Fix/Workaround

Before entering stop mode set all PCx pins to input and GPIO controlled.

6. On some rare parts, the maximum HSB and CPU speed is 50MHz instead of 66MHz. Fix/Workaround

Do not set the HSB/CPU speed higher than 50MHz when the firmware generate exceptions.

7. If the BOD level is higher than VDDCORE, the part is constantly under reset

If the BOD level is set to a value higher than VDDCORE and enabled by fuses, the part will be in constant reset.

#### Fix/Workaround

Apply an external voltage on VDDCORE that is higher than the BOD level and is lower than VDDCORE max and disable the BOD.

8. System Timer mask (Bit 16) of the PM CPUMASK register is not available. Fix/Workaround

Do not use this bit.

#### 15.5.9 HMatrix

1. HMatrix fixed priority arbitration does not work Fixed priority arbitration does not work.

#### Fix/Workaround

Use Round-Robin arbitration instead.

#### 15.5.10 ADC

1. ADC possible miss on DRDY when disabling a channel The ADC does not work properly when more than one channel is enabled.

#### Fix/Workaround

Do not use the ADC with more than one channel enabled at a time.

2. ADC OVRE flag sometimes not reset on Status Register read The OVRE flag does not clear properly if read simultaneously to an end of conversion.

Fix/Workaround None.

3. Sleep Mode activation needs additional A to D conversion

## 16.6 Rev. C - 10/07

- 1. Updated "Signal Description List" on page 8. Removed RXDN and TXDN from USART section.

- 2. Updated "Errata" on page 70. Rev G replaced by rev H.

## 16.7 Rev. B - 10/07

- 1. Updated "Features" on page 1.

- 2. Update "Blockdiagram" on page 4 with local bus.

- 3. Updated "Peripherals" on page 34 with local bus.

- 4. Add SPI feature in "Universial Synchronous/Asynchronous Receiver/Transmitter (USART)" on page 315.

- 5. Updated "USB On-The-Go Interface (USBB)" on page 517.

- 6. Updated "JTAG and Boundary Scan" on page 750 with programming procedure .

- 7. Add description for silicon Rev G.

## 16.8 Rev. A - 03/07

1. Initial revision.