Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | AVR                                                                         |

| Core Size                  | 32-Bit Single-Core                                                          |

| Speed                      | 66MHz                                                                       |

| Connectivity               | EBI/EMI, Ethernet, I <sup>2</sup> C, SPI, SSC, UART/USART, USB OTG          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 109                                                                         |

| Program Memory Size        | 128KB (128K x 8)                                                            |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 32K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 3.6V                                                                |

| Data Converters            | A/D 8x10b                                                                   |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 144-LQFP                                                                    |

| Supplier Device Package    | 144-LQFP (20x20)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at32uc3a0128-alut |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

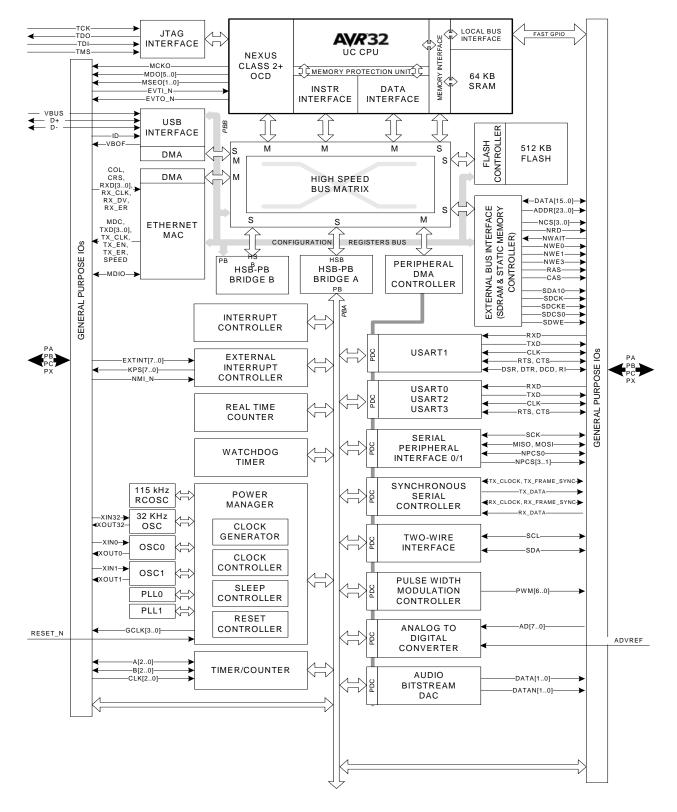

## 4. Blockdiagram

## Figure 4-1. Blockdiagram

## 4.1 Processor and architecture

## 4.1.1 AVR32 UC CPU

## • 32-bit load/store AVR32A RISC architecture.

- 15 general-purpose 32-bit registers.

- 32-bit Stack Pointer, Program Counter and Link Register reside in register file.

- Fully orthogonal instruction set.

- Privileged and unprivileged modes enabling efficient and secure Operating Systems.

- Innovative instruction set together with variable instruction length ensuring industry leading code density.

- DSP extention with saturating arithmetic, and a wide variety of multiply instructions.

- 3 stage pipeline allows one instruction per clock cycle for most instructions.

- Byte, half-word, word and double word memory access.

- Multiple interrupt priority levels.

- MPU allows for operating systems with memory protection.

## 4.1.2 Debug and Test system

- IEEE1149.1 compliant JTAG and boundary scan

- Direct memory access and programming capabilities through JTAG interface

- Extensive On-Chip Debug features in compliance with IEEE-ISTO 5001-2003 (Nexus 2.0) Class 2+ - Low-cost NanoTrace supported.

- Auxiliary port for high-speed trace information

- Hardware support for 6 Program and 2 data breakpoints

- Unlimited number of software breakpoints supported

- Advanced Program, Data, Ownership, and Watchpoint trace supported

#### 4.1.3 Peripheral DMA Controller

- Transfers from/to peripheral to/from any memory space without intervention of the processor.

- Next Pointer Support, forbids strong real-time constraints on buffer management.

- Fifteen channels

- Two for each USART

- Two for each Serial Synchronous Controller

- Two for each Serial Peripheral Interface

- One for each ADC

- Two for each TWI Interface

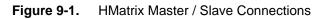

#### 4.1.4 Bus system

- High Speed Bus (HSB) matrix with 6 Masters and 6 Slaves handled

- Handles Requests from the CPU Data Fetch, CPU Instruction Fetch, PDCA, USBB, Ethernet Controller, CPU SAB, and to internal Flash, internal SRAM, Peripheral Bus A, Peripheral Bus B, EBI.

- Round-Robin Arbitration (three modes supported: no default master, last accessed default master, fixed default master)

- Burst Breaking with Slot Cycle Limit

- One Address Decoder Provided per Master

Peripheral Bus A able to run on at divided bus speeds compared to the High Speed Bus

Figure 4-1 gives an overview of the bus system. All modules connected to the same bus use the same clock, but the clock to each module can be individually shut off by the Power Manager. The figure identifies the number of master and slave interfaces of each module connected to the High Speed Bus, and which DMA controller is connected to which peripheral.

## Table 5-1.Signal Description List

| Signal Name   | Function                                   | Туре         | Active<br>Level | Comments           |

|---------------|--------------------------------------------|--------------|-----------------|--------------------|

| RX_DATA       | SSC Receive Data                           | Input        |                 |                    |

| RX_FRAME_SYNC | SSC Receive Frame Sync                     | I/O          |                 |                    |

| TX_CLOCK      | SSC Transmit Clock                         | I/O          |                 |                    |

| TX_DATA       | SSC Transmit Data                          | Output       |                 |                    |

| TX_FRAME_SYNC | SSC Transmit Frame Sync                    | I/O          |                 |                    |

|               | Timer/Counter -                            | TIMER        |                 |                    |

| A0            | Channel 0 Line A                           | I/O          |                 |                    |

| A1            | Channel 1 Line A                           | I/O          |                 |                    |

| A2            | Channel 2 Line A                           | I/O          |                 |                    |

| В0            | Channel 0 Line B                           | I/O          |                 |                    |

| B1            | Channel 1 Line B                           | I/O          |                 |                    |

| B2            | Channel 2 Line B                           | I/O          |                 |                    |

| CLK0          | Channel 0 External Clock Input             | Input        |                 |                    |

| CLK1          | Channel 1 External Clock Input             | Input        |                 |                    |

| CLK2          | Channel 2 External Clock Input             | Input        |                 |                    |

|               | Two-wire Interfac                          | e - TWI      |                 |                    |

| SCL           | Serial Clock                               | I/O          |                 |                    |

| SDA           | Serial Data                                | I/O          |                 |                    |

| Universa      | I Synchronous Asynchronous Receiver Transı | nitter - USA | RT0, USAR       | T1, USART2, USART3 |

| CLK           | Clock                                      | I/O          |                 |                    |

| CTS           | Clear To Send                              | Input        |                 |                    |

| DCD           | Data Carrier Detect                        |              |                 | Only USART1        |

| DSR           | Data Set Ready                             |              |                 | Only USART1        |

| DTR           | Data Terminal Ready                        |              |                 | Only USART1        |

| RI            | Ring Indicator                             |              |                 | Only USART1        |

| RTS           | Request To Send                            | Output       |                 |                    |

| RXD           | Receive Data                               | Input        |                 |                    |

| TXD           | Transmit Data                              | Output       |                 |                    |

## 9. Memories

## 9.1 Embedded Memories

- Internal High-Speed Flash

- 512 KBytes (AT32UC3A0512, AT32UC3A1512)

- 256 KBytes (AT32UC3A0256, AT32UC3A1256)

- 128 KBytes (AT32UC3A1128, AT32UC3A2128)

- 0 Wait State Access at up to 33 MHz in Worst Case Conditions

- 1 Wait State Access at up to 66 MHz in Worst Case Conditions

- Pipelined Flash Architecture, allowing burst reads from sequential Flash locations, hiding penalty of 1 wait state access

- Pipelined Flash Architecture typically reduces the cycle penalty of 1 wait state operation to only 15% compared to 0 wait state operation

- 100 000 Write Cycles, 15-year Data Retention Capability

- 4 ms Page Programming Time, 8 ms Chip Erase Time

- Sector Lock Capabilities, Bootloader Protection, Security Bit

- 32 Fuses, Erased During Chip Erase

- User Page For Data To Be Preserved During Chip Erase

- Internal High-Speed SRAM, Single-cycle access at full speed

- 64 KBytes (AT32UC3A0512, AT32UC3A0256, AT32UC3A1512, AT32UC3A1256)

- 32KBytes (AT32UC3A1128)

## 9.2 Physical Memory Map

The system bus is implemented as a bus matrix. All system bus addresses are fixed, and they are never remapped in any way, not even in boot. Note that AVR32 UC CPU uses unsegmented translation, as described in the AVR32 Architecture Manual. The 32-bit physical address space is mapped as follows:

| Device                     | Start Address | Size         |              |              |              |              |              |

|----------------------------|---------------|--------------|--------------|--------------|--------------|--------------|--------------|

| Start Addres               |               | AT32UC3A0512 | AT32UC3A1512 | AT32UC3A0256 | AT32UC3A1256 | AT32UC3A0128 | AT32UC3A1128 |

| Embedded SRAM              | 0x0000_0000   | 64 Kbyte     | 64 Kbyte     | 64 Kbyte     | 64 Kbyte     | 32 Kbyte     | 32 Kbyte     |

| Embedded Flash             | 0x8000_0000   | 512 Kbyte    | 512 Kbyte    | 256 Kbyte    | 256 Kbyte    | 128 Kbyte    | 128 Kbyte    |

| EBI SRAM CS0               | 0xC000_0000   | 16 Mbyte     | -            | 16 Mbyte     | -            | 16 Mbyte     | -            |

| EBI SRAM CS2               | 0xC800_0000   | 16 Mbyte     | -            | 16 Mbyte     | -            | 16 Mbyte     | -            |

| EBI SRAM CS3               | 0xCC00_0000   | 16 Mbyte     | -            | 16 Mbyte     | -            | 16 Mbyte     | -            |

| EBI SRAM CS1<br>/SDRAM CS0 | 0xD000_0000   | 128 Mbyte    | -            | 128 Mbyte    | -            | 128 Mbyte    | -            |

| USB<br>Configuration       | 0xE000_0000   | 64 Kbyte     |

| HSB-PB Bridge A            | 0xFFFE_0000   | 64 Kbyte     |

| HSB-PB Bridge B            | 0xFFFF_0000   | 64 Kbyte     |

Table 9-1.

AT32UC3A Physical Memory Map

AT32UC3A

## Table 10-1. Peripheral Address Mapping (Continued)

| Address    |        | Peripheral Name                                                     | Bus |

|------------|--------|---------------------------------------------------------------------|-----|

| 0xFFFF1C00 | USART2 | Universal Synchronous Asynchronous Receiver<br>Transmitter - USART2 | PBA |

| 0xFFFF2000 | USART3 | Universal Synchronous Asynchronous Receiver<br>Transmitter - USART3 | PBA |

| 0xFFFF2400 | SPI0   | Serial Peripheral Interface - SPI0                                  | PBA |

| 0xFFFF2800 | SPI1   | Serial Peripheral Interface - SPI1                                  | PBA |

| 0xFFFF2C00 | TWI    | Two Wire Interface - TWI                                            | PBA |

| 0xFFFF3000 | PWM    | Pulse Width Modulation Controller - PWM                             | PBA |

| 0xFFFF3400 | SSC    | Synchronous Serial Controller - SSC                                 | PBA |

| 0xFFFF3800 | тс     | Timer/Counter - TC                                                  | PBA |

| 0xFFFF3C00 | ADC    | Analog To Digital Converter - ADC                                   | PBA |

## 10.2 CPU Local Bus Mapping

Some of the registers in the GPIO module are mapped onto the CPU local bus, in addition to being mapped on the Peripheral Bus. These registers can therefore be reached both by accesses on the Peripheral Bus, and by accesses on the local bus.

Mapping these registers on the local bus allows cycle-deterministic toggling of GPIO pins since the CPU and GPIO are the only modules connected to this bus. Also, since the local bus runs at CPU speed, one write or read operation can be performed per clock cycle to the local busmapped GPIO registers.

## 10.4.3 SPIs

Each SPI can be connected to an internally divided clock:

| Table 10-6. | SPI | clock conn | ections |

|-------------|-----|------------|---------|

|             | 011 |            | 000000  |

| SPI | Source   | Name    | Connection     |

|-----|----------|---------|----------------|

| 0   | Internal | CLK_DIV | PBA clock or   |

| 1   |          |         | PBA clock / 32 |

## 10.5 Nexus OCD AUX port connections

If the OCD trace system is enabled, the trace system will take control over a number of pins, irrespectively of the PIO configuration. Two different OCD trace pin mappings are possible, depending on the configuration of the OCD AXS register. For details, see the AVR32 UC Technical Reference Manual.

| Table 10-7. Nexus OCD ADA poir connections |       |       |

|--------------------------------------------|-------|-------|

| Pin                                        | AXS=0 | AXS=1 |

| EVTI_N                                     | PB19  | PA08  |

| MDO[5]                                     | PB16  | PA27  |

| MDO[4]                                     | PB14  | PA26  |

| MDO[3]                                     | PB13  | PA25  |

| MDO[2]                                     | PB12  | PA24  |

| MDO[1]                                     | PB11  | PA23  |

| MDO[0]                                     | PB10  | PA22  |

| EVTO_N                                     | PB20  | PB20  |

| MCKO                                       | PB21  | PA21  |

| MSEO[1]                                    | PB04  | PA07  |

| MSEO[0]                                    | PB17  | PA28  |

Table 10-7.

Nexus OCD AUX port connections

## 10.6 PDC handshake signals

The PDC and the peripheral modules communicate through a set of handshake signals. The following table defines the valid settings for the Peripheral Identifier (PID) in the PDC Peripheral Select Register (PSR).

|           | PDC Hanushake Signals         |

|-----------|-------------------------------|

| PID Value | Peripheral module & direction |

| 0         | ADC                           |

| 1         | SSC - RX                      |

| 2         | USART0 - RX                   |

| 3         | USART1 - RX                   |

Table 10-8. PDC Handshake Signals

Table 10-9.

GPIO Controller Function Multiplexing

| Table 10-9. |     | roller Functio |          | 1              |               |              |

|-------------|-----|----------------|----------|----------------|---------------|--------------|

| 7           | 11  | PB24           | GPIO 56  | TC - B0        | USART1 - DSR  |              |

| 8           | 13  | PB25           | GPIO 57  | TC - A1        | USART1 - DTR  |              |

| 9           | 14  | PB26           | GPIO 58  | TC - B1        | USART1 - RI   |              |

| 10          | 15  | PB27           | GPIO 59  | TC - A2        | PWM - PWM[4]  |              |

| 14          | 19  | PB28           | GPIO 60  | TC - B2        | PWM - PWM[5]  |              |

| 15          | 20  | PB29           | GPIO 61  | USART2 - RXD   | PM - GCLK[1]  | EBI - NCS[2] |

| 16          | 21  | PB30           | GPIO 62  | USART2 - TXD   | PM - GCLK[2]  | EBI - SDCS   |

| 17          | 22  | PB31           | GPIO 63  | USART2 - CLK   | PM - GCLK[3]  | EBI - NWAIT  |

| 63          | 85  | PC00           | GPIO 64  |                |               |              |

| 64          | 86  | PC01           | GPIO 65  |                |               |              |

| 85          | 124 | PC02           | GPIO 66  |                |               |              |

| 86          | 125 | PC03           | GPIO 67  |                |               |              |

| 93          | 132 | PC04           | GPIO 68  |                |               |              |

| 94          | 133 | PC05           | GPIO 69  |                |               |              |

|             | 1   | PX00           | GPIO 100 | EBI - DATA[10] | USART0 - RXD  |              |

|             | 2   | PX01           | GPIO 99  | EBI - DATA[9]  | USART0 - TXD  |              |

|             | 4   | PX02           | GPIO 98  | EBI - DATA[8]  | USART0 - CTS  |              |

|             | 10  | PX03           | GPIO 97  | EBI - DATA[7]  | USART0 - RTS  |              |

|             | 12  | PX04           | GPIO 96  | EBI - DATA[6]  | USART1 - RXD  |              |

|             | 24  | PX05           | GPIO 95  | EBI - DATA[5]  | USART1 - TXD  |              |

|             | 26  | PX06           | GPIO 94  | EBI - DATA[4]  | USART1 - CTS  |              |

|             | 31  | PX07           | GPIO 93  | EBI - DATA[3]  | USART1 - RTS  |              |

|             | 33  | PX08           | GPIO 92  | EBI - DATA[2]  | USART3 - RXD  |              |

|             | 35  | PX09           | GPIO 91  | EBI - DATA[1]  | USART3 - TXD  |              |

|             | 38  | PX10           | GPIO 90  | EBI - DATA[0]  | USART2 - RXD  |              |

|             | 40  | PX11           | GPIO 109 | EBI - NWE1     | USART2 - TXD  |              |

|             | 42  | PX12           | GPIO 108 | EBI - NWE0     | USART2 - CTS  |              |

|             | 44  | PX13           | GPIO 107 | EBI - NRD      | USART2 - RTS  |              |

|             | 46  | PX14           | GPIO 106 | EBI - NCS[1]   |               | TC - A0      |

|             | 59  | PX15           | GPIO 89  | EBI - ADDR[19] | USART3 - RTS  | TC - B0      |

|             | 61  | PX16           | GPIO 88  | EBI - ADDR[18] | USART3 - CTS  | TC - A1      |

|             | 63  | PX17           | GPIO 87  | EBI - ADDR[17] |               | TC - B1      |

|             | 65  | PX18           | GPIO 86  | EBI - ADDR[16] |               | TC - A2      |

|             | 67  | PX19           | GPIO 85  | EBI - ADDR[15] | EIM - SCAN[0] | TC - B2      |

|             | 87  | PX20           | GPIO 84  | EBI - ADDR[14] | EIM - SCAN[1] | TC - CLK0    |

|             | 89  | PX21           | GPIO 83  | EBI - ADDR[13] | EIM - SCAN[2] | TC - CLK1    |

|             | 91  | PX22           | GPIO 82  | EBI - ADDR[12] | EIM - SCAN[3] | TC - CLK2    |

|             | 95  | PX23           | GPIO 81  | EBI - ADDR[11] | EIM - SCAN[4] |              |

|             | 97  | PX24           | GPIO 80  | EBI - ADDR[10] | EIM - SCAN[5] |              |

|             |     |                |          | L - 1          | L-1           |              |

- Supports Mobile SDRAM Devices

- Error Detection

- Refresh Error Interrupt

- SDRAM Power-up Initialization by Software

- CAS Latency of 1, 2, 3 Supported

- Auto Precharge Command Not Used

## 10.11.4 USB Controller

- USB 2.0 Compliant, Full-/Low-Speed (FS/LS) and On-The-Go (OTG), 12 Mbit/s

- 7 Pipes/Endpoints

- 960 bytes of Embedded Dual-Port RAM (DPRAM) for Pipes/Endpoints

- Up to 2 Memory Banks per Pipe/Endpoint (Not for Control Pipe/Endpoint)

- Flexible Pipe/Endpoint Configuration and Management with Dedicated DMA Channels

- On-Chip Transceivers Including Pull-Ups

## 10.11.5 Serial Peripheral Interface

- Supports communication with serial external devices

- Four chip selects with external decoder support allow communication with up to 15 peripherals

- Serial memories, such as DataFlash and 3-wire EEPROMs

- Serial peripherals, such as ADCs, DACs, LCD Controllers, CAN Controllers and Sensors

- External co-processors

- Master or slave serial peripheral bus interface

- 8- to 16-bit programmable data length per chip select

- Programmable phase and polarity per chip select

- Programmable transfer delays between consecutive transfers and between clock and data per chip select

- Programmable delay between consecutive transfers

- Selectable mode fault detection

- Very fast transfers supported

- Transfers with baud rates up to Peripheral Bus A (PBA) max frequency

- The chip select line may be left active to speed up transfers on the same device

## 10.11.6 Two-wire Interface

- High speed up to 400kbit/s

- · Compatibility with standard two-wire serial memory

- One, two or three bytes for slave address

- Sequential read/write operations

## 10.11.7 USART

- Programmable Baud Rate Generator

- 5- to 9-bit full-duplex synchronous or asynchronous serial communications

- 1, 1.5 or 2 stop bits in Asynchronous Mode or 1 or 2 stop bits in Synchronous Mode

- Parity generation and error detection

- Framing error detection, overrun error detection

- MSB- or LSB-first

- Optional break generation and detection

- By 8 or by-16 over-sampling receiver frequency

- Hardware handshaking RTS-CTS

- Receiver time-out and transmitter timeguard

- Optional Multi-drop Mode with address generation and detection

## 11. Boot Sequence

This chapter summarizes the boot sequence of the AT32UC3A. The behaviour after power-up is controlled by the Power Manager. For specific details, refer to Section 13. "Power Manager (PM)" on page 53.

## 11.1 Starting of clocks

After power-up, the device will be held in a reset state by the Power-On Reset circuitry, until the power has stabilized throughout the device. Once the power has stabilized, the device will use the internal RC Oscillator as clock source.

On system start-up, the PLLs are disabled. All clocks to all modules are running. No clocks have a divided frequency, all parts of the system recieves a clock with the same frequency as the internal RC Oscillator.

## **11.2** Fetching of initial instructions

After reset has been released, the AVR32 UC CPU starts fetching instructions from the reset address, which is 0x8000\_0000. This address points to the first address in the internal Flash.

The code read from the internal Flash is free to configure the system to use for example the PLLs, to divide the frequency of the clock routed to some of the peripherals, and to gate the clocks to unused peripherals.

## Table 12-7. BOD Timing

| Symbol           | Parameter                                                      | Test Conditions                      | Тур. | Max. | Units. |

|------------------|----------------------------------------------------------------|--------------------------------------|------|------|--------|

| T <sub>BOD</sub> | Minimum time with<br>VDDCORE < VBOD to<br>detect power failure | Falling VDDCORE<br>from 1.8V to 1.1V | 300  | 800  | ns     |

## 12.4.2 POR

## Table 12-8. Electrical Characteristic

| Symbol               | Parameter                                                                                                                            | Test Conditions                                              | Min. | Тур. | Max. | Units. |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|------|------|------|--------|

| V <sub>DDRR</sub>    | VDDCORE rise rate to ensure power-on-reset                                                                                           |                                                              | 0.01 |      |      | V/ms   |

| V <sub>SSFR</sub>    | VDDCORE fall rate to ensure power-on-reset                                                                                           |                                                              | 0.01 |      | 400  | V/ms   |

| V <sub>POR+</sub>    | Rising threshold voltage: voltage up to which device is kept under reset by POR on rising VDDCORE                                    | Rising VDDCORE:<br>V <sub>RESTART</sub> -> V <sub>POR+</sub> | 1.35 | 1.5  | 1.6  | v      |

| V <sub>POR-</sub>    | Falling threshold voltage: voltage when POR resets device on falling VDDCORE                                                         | Falling VDDCORE:<br>1.8V -> V <sub>POR+</sub>                | 1.25 | 1.3  | 1.4  | V      |

| V <sub>RESTART</sub> | On falling VDDCORE, voltage must go down to this value before supply can rise again to ensure reset signal is released at $V_{POR+}$ | Falling VDDCORE:<br>1.8V -> V <sub>RESTART</sub>             | -0.1 |      | 0.5  | v      |

| T <sub>POR</sub>     | Minimum time with VDDCORE < V <sub>POR</sub> .                                                                                       | Falling VDDCORE:<br>1.8V -> 1.1V                             |      | 15   |      | us     |

| T <sub>RST</sub>     | Time for reset signal to be propagated to system                                                                                     |                                                              |      | 200  | 400  | us     |

These figures represent the power consumption measured on the power supplies.

Table 12-9.

Power Consumption for Different Modes

| Mode                                                                                                                                                                                                              | Conditions                                                                                                                                          |            | Тур. | Unit |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|------------|------|------|

|                                                                                                                                                                                                                   | Тур : Та =25 °С                                                                                                                                     | f = 12 MHz | 9    | mA   |

|                                                                                                                                                                                                                   | CPU running from flash <sup>(1)</sup> .                                                                                                             | f = 24 MHz | 15   | mA   |

|                                                                                                                                                                                                                   | VDDIN=3.3 V. VDDCORE =1.8V.<br>CPU clocked from PLL0 at f MHz                                                                                       | f = 36MHz  | 20   | mA   |

| Active                                                                                                                                                                                                            | Voltage regulator is on.<br>XIN0 : external clock. <sup>(1)</sup><br>XIN1 stopped. XIN32 stopped                                                    | f = 50 MHz | 28   | mA   |

|                                                                                                                                                                                                                   | PLL0 running<br>All peripheral clocks activated.<br>GPIOs on internal pull-up.<br>JTAG unconnected with ext pull-up.                                | f = 66 MHz | 36.3 | mA   |

|                                                                                                                                                                                                                   | Typ : Ta = 25 °C                                                                                                                                    | f = 12 MHz | 5    | mA   |

|                                                                                                                                                                                                                   | CPU running from flash <sup>(1)</sup> .                                                                                                             | f = 24 MHz | 10   | mA   |

|                                                                                                                                                                                                                   | VDDIN=3.3 V. VDDCORE =1.8V.<br>CPU clocked from PLL0 at f MHz                                                                                       | f = 36MHz  | 14   | mA   |

|                                                                                                                                                                                                                   | Voltage regulator is on.                                                                                                                            | f = 50 MHz | 19   | mA   |

| Idle       XIN0 : external clock.         XIN1 stopped. XIN32 stopped         PLL0 running         All peripheral clocks activated.         GPIOs on internal pull-up.         JTAG unconnected with ext pull-up. | f = 66 MHz                                                                                                                                          | 25.5       | mA   |      |

|                                                                                                                                                                                                                   | Typ : Ta = 25 °C                                                                                                                                    | f = 12 MHz | 3    | mA   |

|                                                                                                                                                                                                                   | CPU running from flash <sup>(1)</sup> .                                                                                                             | f = 24 MHz | 6    | mA   |

|                                                                                                                                                                                                                   | CPU clocked from PLL0 at f MHz<br>Voltage regulator is on.                                                                                          | f = 36MHz  | 9    | mA   |

| Freese                                                                                                                                                                                                            | XIN0 : external clock.                                                                                                                              | f = 50 MHz | 13   | mA   |

| Frozen                                                                                                                                                                                                            | XIN1 stopped. XIN32 stopped<br>PLL0 running<br>All peripheral clocks activated.<br>GPIOs on internal pull-up.<br>JTAG unconnected with ext pull-up. | f = 66 MHz | 16.8 | mA   |

|                                                                                                                                                                                                                   | Typ : Ta = 25 °C                                                                                                                                    | f = 12 MHz | 1    | mA   |

|                                                                                                                                                                                                                   | CPU running from flash <sup>(1)</sup> .                                                                                                             | f = 24 MHz | 2    | mA   |

|                                                                                                                                                                                                                   | CPU clocked from PLL0 at f MHz<br>Voltage regulator is on.                                                                                          | f = 36MHz  | 3    | mA   |

| Standby                                                                                                                                                                                                           | XIN0 : external clock.                                                                                                                              | f = 50 MHz | 4    | mA   |

| Standby                                                                                                                                                                                                           | XIN1 stopped. XIN32 stopped<br>PLL0 running<br>All peripheral clocks activated.<br>GPIOs on internal pull-up.<br>JTAG unconnected with ext pull-up. | f = 66 MHz | 4.8  | mA   |

## 12.7.2 Main Oscillators Characteristics

Table 12-15.

Main Oscillator Characteristics

| Symbol                   | Parameter                                     | Conditions     | Min                         | Тур | Max                         | Unit |

|--------------------------|-----------------------------------------------|----------------|-----------------------------|-----|-----------------------------|------|

| 1/(t <sub>CPMAIN</sub> ) | Crystal Oscillator Frequency                  |                | 0.45                        |     | 16                          | MHz  |

| $C_{L1}, C_{L2}$         | Internal Load Capacitance $(C_{L1} = C_{L2})$ |                |                             | 12  |                             | pF   |

|                          | Duty Cycle                                    |                | 40                          | 50  | 60                          | %    |

| t <sub>ST</sub>          | Startup Time                                  |                |                             |     | TBD                         | ms   |

| A // L )                 | XIN Clock Frequency                           | External clock |                             |     | 50                          | MHz  |

| 1/(t <sub>CPXIN</sub> )  |                                               | Crystal        | 0.45                        |     | 16                          | MHz  |

| t <sub>CHXIN</sub>       | XIN Clock High Half-period                    |                | 0.4 x<br>t <sub>CPXIN</sub> |     | 0.6 x<br>t <sub>CPXIN</sub> |      |

| t <sub>CLXIN</sub>       | XIN Clock Low Half-period                     |                | 0.4 x<br>t <sub>CPXIN</sub> |     | 0.6 x<br>t <sub>CPXIN</sub> |      |

| C <sub>IN</sub>          | XIN Input Capacitance                         |                |                             | 7   |                             | pF   |

## 12.7.3 PLL Characteristics

Table 12-16. Phase Lock Loop Characteristics

| Symbol           | Parameter           | Conditions                | Min | Тур | Max | Unit |

|------------------|---------------------|---------------------------|-----|-----|-----|------|

| F <sub>OUT</sub> | Output Frequency    |                           | 80  |     | 240 | MHz  |

| F <sub>IN</sub>  | Input Frequency     |                           | 4   |     | 16  | MHz  |

|                  | Current Consumption | active mode (Fout=80Mhz)  |     | 250 |     | μA   |

| PLL              | Current Consumption | active mode (Fout=240Mhz) |     | 600 |     | μA   |

# AT32UC3A

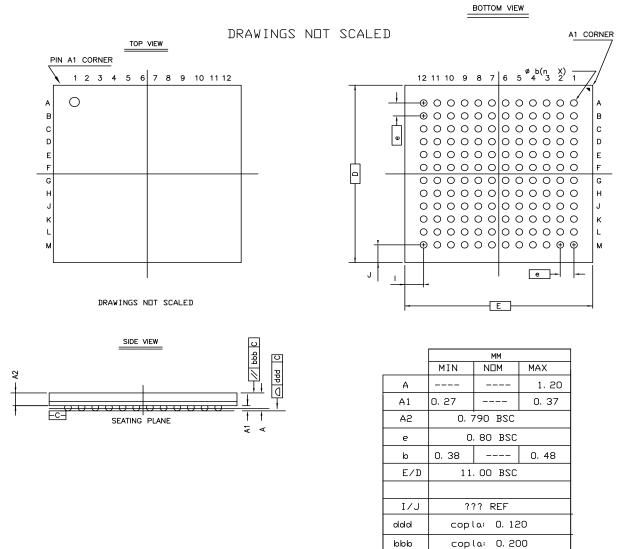

Figure 13-3. FFBGA-144 package drawing

| Table 13-8. | Device and Package Maximum Weight |

|-------------|-----------------------------------|

|-------------|-----------------------------------|

|   | 1300 | mg |

|---|------|----|

| _ |      |    |

## Table 13-9. Package Characteristics

| Moisture Sensitivity Level MSL3 |

|---------------------------------|

|---------------------------------|

## Table 13-10. Package Reference

| JEDEC Drawing Reference | MS-026 |

|-------------------------|--------|

| JESD97 Classification   | E3     |

3. SPI Bad Serial Clock Generation on 2nd chip\_select when SCBR = 1, CPOL=1 and NCPHA=0

When multiple CS are in use, if one of the baudrate equals to 1 and one of the others doesn't equal to 1, and CPOL=1 and CPHA=0, then an aditional pulse will be generated on SCK. **Fix/workaround**

When multiple CS are in use, if one of the baudrate equals 1, the other must also equal 1 if CPOL=1 and CPHA=0.

4. SPI Glitch on RXREADY flag in slave mode when enabling the SPI or during the first transfer

In slave mode, the SPI can generate a false RXREADY signal during enabling of the SPI or during the first transfer.

## Fix/Workaround

1. Set slave mode, set required CPOL/CPHA.

- 2. Enable SPI.

- 3. Set the polarity CPOL of the line in the opposite value of the required one.

- 4. Set the polarity CPOL to the required one.

- 5. Read the RXHOLDING register.

Transfers can now befin and RXREADY will now behave as expected.

SPI Disable does not work in Slave mode Fix/workaround Read the last received data then perform a Software reset.

## 15.1.4 Power Manager

If the BOD level is higher than VDDCORE, the part is constantly under reset

If the BOD level is set to a value higher than VDDCORE and enabled by fuses, the part will

be in constant reset.

## Fix/Workaround

Apply an external voltage on VDDCORE that is higher than the BOD level and is lower than VDDCORE max and disable the BOD.

- 15.1.5 PDCA

- 1. Wrong PDCA behavior when using two PDCA channels with the same PID. Fix/Workaround

The same PID should not be assigned to more than one channel.

## 15.1.6 TWI

1. The TWI RXRDY flag in SR register is not reset when a software reset is performed. Fix/Workaround

After a Software Reset, the register TWI RHR must be read.

- 15.1.7 USART

- ISO7816 info register US\_NER cannot be read The NER register always returns zero.

Fix/Workaround None

## 15.1.8 Processor and Architecture

1. LDM instruction with PC in the register list and without ++ increments Rp

## 15.4 Rev. H

15.4.1 PWM

## 1. PWM channel interrupt enabling triggers an interrupt

When enabling a PWM channel that is configured with center aligned period (CALG=1), an interrupt is signalled.

## Fix/Workaround

When using center aligned mode, enable the channel and read the status before channel interrupt is enabled.

## 2. PWM counter restarts at 0x0001

The PWM counter restarts at 0x0001 and not 0x0000 as specified. Because of this the first PWM period has one more clock cycle.

Fix/Workaround

- The first period is 0x0000, 0x0001, ..., period

- Consecutive periods are 0x0001, 0x0002, ..., period

## 3. PWM update period to a 0 value does not work

It is impossible to update a period equal to 0 by the using the PWM update register (PWM\_CUPD).

## **Fix/Workaround**

Do not update the PWM\_CUPD register with a value equal to 0.

15.4.2 ADC

## 1. Sleep Mode activation needs additional A to D conversion

If the ADC sleep mode is activated when the ADC is idle the ADC will not enter sleep mode before after the next AD conversion.

## Fix/Workaround

Activate the sleep mode in the mode register and then perform an AD conversion.

15.4.3 SPI

## 1. SPI Slave / PDCA transfer: no TX UNDERRUN flag

There is no TX UNDERRUN flag available, therefore in SPI slave mode, there is no way to be informed of a character lost in transmission.

## Fix/Workaround

For PDCA transfer: none.

## 2. SPI FDIV option does not work

Selecting clock signal using FDIV = 1 does not work as specified.

## **Fix/Workaround**

Do not set FDIV = 1

## 3. SPI disable does not work in SLAVE mode. Fix/Workaround

Read the last received data, then perform a Software Reset.

RETS behaves incorrectly when MPU is enabled and MPU is configured so that system stack is not readable in unprivileged mode.

## Fix/Woraround

Workaround 1: Make system stack readable in unprivileged mode, or

Workaround 2: Return from supervisor mode using rete instead of rets. This requires :

1. Changing the mode bits from 001b to 110b before issuing the instruction. Updating the mode bits to the desired value must be done using a single mtsr instruction so it is done atomically. Even if this step is described in general as not safe in the UC technical reference guide, it is safe in this very specific case.

2. Execute the RETE instruction.

## 15.5.4 USB

## 1. USB No end of host reset signaled upon disconnection

In host mode, in case of an unexpected device disconnection whereas a usb reset is being sent by the usb controller, the UHCON.RESET bit may not been cleared by the hardware at the end of the reset.

## **Fix/Workaround**

A software workaround consists in testing (by polling or interrupt) the disconnection (UHINT.DDISCI == 1) while waiting for the end of reset (UHCON.RESET == 0) to avoid being stuck.

## 2. USBFSM and UHADDR1/2/3 registers are not available.

Do not use USBFSM register.

## Fix/Workaround

Do not use USBFSM register and use HCON[6:0] field instead for all the pipes.

#### 15.5.5 Processor and Architecture

#### 1. Incorrect Processor ID

The processor ID reads 0x01 and not 0x02 as it should.

## **Fix/Workaround**

None.

#### 2. Bus error should be masked in Debug mode

If a bus error occurs during debug mode, the processor will not respond to debug commands through the DINST register.

#### Fix/Workaround

A reset of the device will make the CPU respond to debug commands again.

# 3. Read Modify Write (RMW) instructions on data outside the internal RAM does not work.

Read Modify Write (RMW) instructions on data outside the internal RAM does not work.

## Fix/Workaround

Do not perform RMW instructions on data outside the internal RAM.

# 4. CRC calculation of a locked device will calculate CRC for 512 kB of flash memory, even though the part has less flash. Fix/Workaround

The flash address space is wrapping, so it is possible to use the CRC value by calculating CRC of the flash content concatenated with itself N times. Where N is 512 kB/flash size.

## 5. Need two NOPs instruction after instructions masking interrupts

The instructions following in the pipeline the instruction masking the interrupt through SR may behave abnormally.

## **Fix/Workaround**

Place two NOPs instructions after each SSRF or MTSR instruction setting IxM or GM in SR.

# AT32UC3A