Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Detuils                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | AVR                                                                         |

| Core Size                  | 32-Bit Single-Core                                                          |

| Speed                      | 66MHz                                                                       |

| Connectivity               | EBI/EMI, Ethernet, I <sup>2</sup> C, SPI, SSC, UART/USART, USB OTG          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 109                                                                         |

| Program Memory Size        | 128KB (128K x 8)                                                            |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 32K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 3.6V                                                                |

| Data Converters            | A/D 8x10b                                                                   |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 144-TFBGA                                                                   |

| Supplier Device Package    | 144-FFBGA (11x11)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at32uc3a0128-ctur |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2. Configuration Summary

| Device       | Flash      | SRAM      | Ext. Bus Interface | Ethernet<br>MAC | Package                     |

|--------------|------------|-----------|--------------------|-----------------|-----------------------------|

| AT32UC3A0512 | 512 Kbytes | 64 Kbytes | yes                | yes             | 144 pin LQFP<br>144 pin BGA |

| AT32UC3A0256 | 256 Kbytes | 64 Kbytes | yes                | yes             | 144 pin LQFP<br>144 pin BGA |

| AT32UC3A0128 | 128 Kbytes | 32 Kbytes | yes                | yes             | 144 pin LQFP<br>144 pin BGA |

| AT32UC3A1512 | 512 Kbytes | 64 Kbytes | no                 | yes             | 100 pin TQFP                |

| AT32UC3A1256 | 256 Kbytes | 64 Kbytes | no                 | yes             | 100 pin TQFP                |

| AT32UC3A1128 | 128 Kbytes | 32 Kbytes | no                 | yes             | 100 pin TQFP                |

The table below lists all AT32UC3A memory and package configurations:

## 3. Abbreviations

- GCLK: Power Manager Generic Clock

- GPIO: General Purpose Input/Output

- HSB: High Speed Bus

- MPU: Memory Protection Unit

- OCD: On Chip Debug

- PB: Peripheral Bus

- PDCA: Peripheral Direct Memory Access Controller (PDC) version A

- USBB: USB On-The-GO Controller version B

| Part Number  | Flash Size<br>( <i>FLASH_PW</i> ) | Number of pages<br>(FLASH_P) | Page size<br>( <i>FLASH_W</i> ) | General Purpose<br>Fuse bits<br>(FLASH_F) |

|--------------|-----------------------------------|------------------------------|---------------------------------|-------------------------------------------|

| AT32UC3A0512 | 512 Kbytes                        | 1024                         | 128 words                       | 32 fuses                                  |

| AT32UC3A1512 | 512 Kbytes                        | 1024                         | 128 words                       | 32 fuses                                  |

| AT32UC3A0256 | 256 Kbytes                        | 512                          | 128 words                       | 32 fuses                                  |

| AT32UC3A1256 | 256 Kbytes                        | 512                          | 128 words                       | 32 fuses                                  |

| AT32UC3A1128 | 128 Kbytes                        | 256                          | 128 words                       | 32 fuses                                  |

| AT32UC3A0128 | 128 Kbytes                        | 256                          | 128 words                       | 32 fuses                                  |

**Table 9-2.**Flash Memory Parameters

## 9.3 Bus Matrix Connections

Accesses to unused areas returns an error result to the master requesting such an access.

The bus matrix has the several masters and slaves. Each master has its own bus and its own decoder, thus allowing a different memory mapping per master. The master number in the table below can be used to index the HMATRIX control registers. For example, MCFG0 is associated with the CPU Data master interface.

| Table 9-3. | High Speed bus masters |

|------------|------------------------|

| Master 0   | CPU Data               |

| Master 1   | CPU Instruction        |

| Master 2   | CPU SAB                |

| Master 3   | PDCA                   |

| Master 4   | MACB DMA               |

| Master 5   | USBB DMA               |

Table 9-3.High Speed Bus masters

Each slave has its own arbiter, thus allowing a different arbitration per slave. The slave number in the table below can be used to index the HMATRIX control registers. For example, SCFG3 is associated with the Internal SRAM Slave Interface.

| Table 9-4. | High Speed Bus slaves |

|------------|-----------------------|

|------------|-----------------------|

|         | •               |

|---------|-----------------|

| Slave 0 | Internal Flash  |

| Slave 1 | HSB-PB Bridge 0 |

| Slave 2 | HSB-PB Bridge 1 |

| Slave 3 | Internal SRAM   |

| Slave 4 | USBB DPRAM      |

| Slave 5 | EBI             |

# 10. Peripherals

# 10.1 Peripheral address map

Table 10-1.

Peripheral Address Mapping

| Address    |         | Peripheral Name                                                     | Bus |

|------------|---------|---------------------------------------------------------------------|-----|

|            |         | 1                                                                   |     |

| 0xE0000000 | USBB    | USBB Slave Interface - USBB                                         | HSB |

| 0xFFFE0000 | USBB    | USBB Configuration Interface - USBB                                 | PBB |

| 0xFFFE1000 | HMATRIX | HMATRIX Configuration Interface - HMATRIX                           | PBB |

| 0xFFFE1400 | FLASHC  | Flash Controller - FLASHC                                           | PBB |

| 0xFFFE1800 | MACB    | MACB Configuration Interface - MACB                                 | PBB |

| 0xFFFE1C00 | SMC     | Static Memory Controller Configuration Interface -                  | PBB |

| 0xFFFE2000 | SDRAMC  | SDRAM Controller Configuration Interface -<br>SDRAMC                | PBB |

| 0xFFFF0000 | PDCA    | Peripheral DMA Interface - PDCA                                     | PBA |

| 0xFFFF0800 | INTC    | Interrupt Controller Interface - INTC                               | PBA |

| 0xFFFF0C00 | РМ      | Power Manager - PM                                                  | PBA |

| 0xFFFF0D00 | RTC     | Real Time Clock - RTC                                               | PBA |

| 0xFFFF0D30 | WDT     | WatchDog Timer - WDT                                                | PBA |

| 0xFFFF0D80 | EIC     | External Interrupt Controller - EIC                                 | PBA |

| 0xFFFF1000 | GPIO    | General Purpose IO Controller - GPIO                                | PBA |

| 0xFFFF1400 | USART0  | Universal Synchronous Asynchronous Receiver<br>Transmitter - USART0 | PBA |

| 0xFFFF1800 | USART1  | Universal Synchronous Asynchronous Receiver<br>Transmitter - USART1 | PBA |

| l          |         | 1                                                                   |     |

#### 10.4.3 SPIs

Each SPI can be connected to an internally divided clock:

| Table 10-6. | SPI | clock conn | ections |

|-------------|-----|------------|---------|

|             | 011 |            | 000000  |

| SPI | Source   | Name    | Connection     |

|-----|----------|---------|----------------|

| 0   | Internal | CLK_DIV | PBA clock or   |

| 1   |          |         | PBA clock / 32 |

### 10.5 Nexus OCD AUX port connections

If the OCD trace system is enabled, the trace system will take control over a number of pins, irrespectively of the PIO configuration. Two different OCD trace pin mappings are possible, depending on the configuration of the OCD AXS register. For details, see the AVR32 UC Technical Reference Manual.

|         | Nexus OCD ADA | port connections |

|---------|---------------|------------------|

| Pin     | AXS=0         | AXS=1            |

| EVTI_N  | PB19          | PA08             |

| MDO[5]  | PB16          | PA27             |

| MDO[4]  | PB14          | PA26             |

| MDO[3]  | PB13          | PA25             |

| MDO[2]  | PB12          | PA24             |

| MDO[1]  | PB11          | PA23             |

| MDO[0]  | PB10          | PA22             |

| EVTO_N  | PB20          | PB20             |

| MCKO    | PB21          | PA21             |

| MSEO[1] | PB04          | PA07             |

| MSEO[0] | PB17          | PA28             |

Table 10-7.

Nexus OCD AUX port connections

## 10.6 PDC handshake signals

The PDC and the peripheral modules communicate through a set of handshake signals. The following table defines the valid settings for the Peripheral Identifier (PID) in the PDC Peripheral Select Register (PSR).

|                                         | Table 10-0. FDC Hallushake Signals |  |  |

|-----------------------------------------|------------------------------------|--|--|

| PID Value Peripheral module & direction |                                    |  |  |

| 0                                       | ADC                                |  |  |

| 1                                       | SSC - RX                           |  |  |

| 2                                       | USART0 - RX                        |  |  |

| 3                                       | USART1 - RX                        |  |  |

Table 10-8. PDC Handshake Signals

- Optional Manchester Encoding

- RS485 with driver control signal

- ISO7816, T = 0 or T = 1 Protocols for interfacing with smart cards

- NACK handling, error counter with repetition and iteration limit

- IrDA modulation and demodulation

- Communication at up to 115.2 Kbps

- Test Modes

- Remote Loopback, Local Loopback, Automatic Echo

- SPI Mode

- Master or Slave

- Serial Clock Programmable Phase and Polarity

- SPI Serial Clock (SCK) Frequency up to Internal Clock Frequency PBA/4

- Supports Connection of Two Peripheral DMA Controller Channels (PDC)

- Offers Buffer Transfer without Processor Intervention

#### 10.11.8 Serial Synchronous Controller

- Provides serial synchronous communication links used in audio and telecom applications (with CODECs in Master or Slave Modes, I2S, TDM Buses, Magnetic Card Reader, etc.)

- · Contains an independent receiver and transmitter and a common clock divider

- Offers a configurable frame sync and data length

- Receiver and transmitter can be programmed to start automatically or on detection of different event on the frame sync signal

- Receiver and transmitter include a data signal, a clock signal and a frame synchronization signal

- 10.11.9 Timer Counter

- Three 16-bit Timer Counter Channels

- Wide range of functions including:

- Frequency Measurement

- Event Counting

- Interval Measurement

- Pulse Generation

- Delay Timing

- Pulse Width Modulation

- Up/down Capabilities

- Each channel is user-configurable and contains:

- Three external clock inputs

- Five internal clock inputs

- Two multi-purpose input/output signals

- Two global registers that act on all three TC Channels

#### 10.11.10 Pulse Width Modulation Controller

- 7 channels, one 20-bit counter per channel

- Common clock generator, providing Thirteen Different Clocks

- A Modulo n counter providing eleven clocks

- Two independent Linear Dividers working on modulo n counter outputs

- Independent channel programming

- Independent Enable Disable Commands

- Independent Clock

- Independent Period and Duty Cycle, with Double Bufferization

- Programmable selection of the output waveform polarity

- Programmable center or left aligned output waveform

## 11. Boot Sequence

This chapter summarizes the boot sequence of the AT32UC3A. The behaviour after power-up is controlled by the Power Manager. For specific details, refer to Section 13. "Power Manager (PM)" on page 53.

## 11.1 Starting of clocks

After power-up, the device will be held in a reset state by the Power-On Reset circuitry, until the power has stabilized throughout the device. Once the power has stabilized, the device will use the internal RC Oscillator as clock source.

On system start-up, the PLLs are disabled. All clocks to all modules are running. No clocks have a divided frequency, all parts of the system recieves a clock with the same frequency as the internal RC Oscillator.

## **11.2** Fetching of initial instructions

After reset has been released, the AVR32 UC CPU starts fetching instructions from the reset address, which is 0x8000\_0000. This address points to the first address in the internal Flash.

The code read from the internal Flash is free to configure the system to use for example the PLLs, to divide the frequency of the clock routed to some of the peripherals, and to gate the clocks to unused peripherals.

## 12.3 Regulator characteristics

Table 12-2.

Electrical characteristics

| Symbol              | Parameter                                         | Condition                                                   | Min. | Тур. | Max. | Units |

|---------------------|---------------------------------------------------|-------------------------------------------------------------|------|------|------|-------|

| $V_{\text{VDDIN}}$  | Supply voltage (input)                            |                                                             | 3    | 3.3  | 3.6  | V     |

| V <sub>VDDOUT</sub> | Supply voltage (output)                           |                                                             | 1.81 | 1.85 | 1.89 | V     |

|                     | Maximum DC output current with $V_{VDDIN = 3.3V}$ |                                                             |      |      | 100  | mA    |

| OUT                 | Maximum DC output current with $V_{VDDIN = 2.7V}$ |                                                             |      |      | 90   | mA    |

|                     | Static Current of internal regulator              | Low Power mode (stop, deep stop or static) at $T_A = 25$ °C |      | 10   |      | μA    |

## Table 12-3.Decoupling requirements

| Symbol            | Parameter                    | Condition | Тур. | Techno. | Units |

|-------------------|------------------------------|-----------|------|---------|-------|

| C <sub>IN1</sub>  | Input Regulator Capacitor 1  |           | 1    | NPO     | nF    |

| C <sub>IN2</sub>  | Input Regulator Capacitor 2  |           | 4.7  | X7R     | uF    |

| C <sub>OUT1</sub> | Output Regulator Capacitor 1 |           | 470  | NPO     | pF    |

| C <sub>OUT2</sub> | Output Regulator Capacitor 2 |           | 2.2  | X7R     | uF    |

## 12.4 Analog characteristics

Table 12-4. Electrical characteristics

| Symbol  | Parameter                        | Condition | Min. | Тур. | Max. | Units |

|---------|----------------------------------|-----------|------|------|------|-------|

| VADVREF | Analog voltage reference (input) |           | 2.6  |      | 3.6  | V     |

### **Table 12-5.**Decoupling requirements

| Symbol             | Parameter                     | Condition | Тур. | Techno | Units |

|--------------------|-------------------------------|-----------|------|--------|-------|

| C <sub>VREF1</sub> | Voltage reference Capacitor 1 |           | 10   | -      | nF    |

| C <sub>VREF2</sub> | Voltage reference Capacitor 2 |           | 1    | -      | uF    |

12.4.1 BOD

Table 12-6.BODLEVEL Values

| BODLEVEL Value | Тур. | Тур. | Тур. | Units. |

|----------------|------|------|------|--------|

| 00 0000b       | 1.40 | 1.47 | 1.55 | V      |

| 01 0111b       | 1.45 | 1.52 | 1.6  | V      |

| 01 1111b       | 1.55 | 1.6  | 1.65 | V      |

| 10 0111b       | 1.65 | 1.69 | 1.75 | V      |

The values in Table 12-6 describes the values of the BODLEVEL in the flash FGPFR register.

## 12.5 Power Consumption

The values in Table 12-9 and Table 12-10 on page 46 are measured values of power consumption with operating conditions as follows:

- $\bullet V_{DDIO} = 3.3V$

- • $V_{DDCORE} = V_{DDPLL} = 1.8V$

- •TA =  $25^{\circ}$ C, TA =  $85^{\circ}$ C

- •I/Os are configured in input, pull-up enabled.

Figure 12-1. Measurement setup

### 12.7.2 Main Oscillators Characteristics

Table 12-15.

Main Oscillator Characteristics

| Symbol                   | Parameter                                     | Conditions     | Min                         | Тур | Max                         | Unit |

|--------------------------|-----------------------------------------------|----------------|-----------------------------|-----|-----------------------------|------|

| 1/(t <sub>CPMAIN</sub> ) | Crystal Oscillator Frequency                  |                | 0.45                        |     | 16                          | MHz  |

| $C_{L1}, C_{L2}$         | Internal Load Capacitance $(C_{L1} = C_{L2})$ |                |                             | 12  |                             | pF   |

|                          | Duty Cycle                                    |                | 40                          | 50  | 60                          | %    |

| t <sub>ST</sub>          | Startup Time                                  |                |                             |     | TBD                         | ms   |

| A // L )                 |                                               | External clock |                             |     | 50                          | MHz  |

| 1/(t <sub>CPXIN</sub> )  | XIN Clock Frequency                           | Crystal        | 0.45                        |     | 16                          | MHz  |

| t <sub>CHXIN</sub>       | XIN Clock High Half-period                    |                | 0.4 x<br>t <sub>CPXIN</sub> |     | 0.6 x<br>t <sub>CPXIN</sub> |      |

| t <sub>CLXIN</sub>       | XIN Clock Low Half-period                     |                | 0.4 x<br>t <sub>CPXIN</sub> |     | 0.6 x<br>t <sub>CPXIN</sub> |      |

| C <sub>IN</sub>          | XIN Input Capacitance                         |                |                             | 7   |                             | pF   |

## 12.7.3 PLL Characteristics

Table 12-16. Phase Lock Loop Characteristics

| Symbol           | Parameter           | Conditions                | Min | Тур | Max | Unit |

|------------------|---------------------|---------------------------|-----|-----|-----|------|

| F <sub>OUT</sub> | Output Frequency    |                           | 80  |     | 240 | MHz  |

| F <sub>IN</sub>  | Input Frequency     |                           | 4   |     | 16  | MHz  |

|                  | Current Consumption | active mode (Fout=80Mhz)  |     | 250 |     | μA   |

| PLL              | Current Consumption | active mode (Fout=240Mhz) |     | 600 |     | μA   |

## 12.9 EBI Timings

These timings are given for worst case process, T = 85·C, VDDCORE = 1.65V, VDDIO = 3V and 40 pF load capacitance.

| Symbol                  | Parameter                      | Max <sup>(1)</sup>      | Units |

|-------------------------|--------------------------------|-------------------------|-------|

| 1/(t <sub>CPSMC</sub> ) | SMC Controller Clock Frequency | 1/(t <sub>cpcpu</sub> ) | MHz   |

Note: 1. The maximum frequency of the SMC interface is the same as the max frequency for the HSB.

## Table 12-23. SMC Read Signals with Hold Settings

| Symbol            | Parameter                                  | Min                                                             | Units |

|-------------------|--------------------------------------------|-----------------------------------------------------------------|-------|

|                   | NRD C                                      | ontrolled (READ_MODE = 1)                                       |       |

| SMC <sub>1</sub>  | Data Setup before NRD High                 | 12                                                              |       |

| SMC <sub>2</sub>  | Data Hold after NRD High                   | 0                                                               |       |

| SMC <sub>3</sub>  | NRD High to NBS0/A0 Change <sup>(1)</sup>  | nrd hold length * t <sub>CPSMC</sub> - 1.3                      |       |

| SMC <sub>4</sub>  | NRD High to NBS1 Change <sup>(1)</sup>     | nrd hold length * t <sub>CPSMC</sub> - 1.3                      |       |

| SMC <sub>5</sub>  | NRD High to NBS2/A1 Change <sup>(1)</sup>  | nrd hold length * t <sub>CPSMC</sub> - 1.3                      | ns    |

| SMC <sub>6</sub>  | NRD High to NBS3 Change <sup>(1)</sup>     | nrd hold length * t <sub>CPSMC</sub> - 1.3                      |       |

| SMC <sub>7</sub>  | NRD High to A2 - A25 Change <sup>(1)</sup> | nrd hold length * t <sub>CPSMC</sub> - 1.3                      |       |

| SMC <sub>8</sub>  | NRD High to NCS Inactive <sup>(1)</sup>    | (nrd hold length - ncs rd hold length) * $t_{CPSMC}$ - 2.3      |       |

| SMC <sub>9</sub>  | NRD Pulse Width                            | nrd pulse length * t <sub>CPSMC</sub> - 1.4                     |       |

|                   | NRD C                                      | ontrolled (READ_MODE = 0)                                       | I     |

| SMC <sub>10</sub> | Data Setup before NCS High                 | 11.5                                                            |       |

| SMC <sub>11</sub> | Data Hold after NCS High                   | 0                                                               |       |

| SMC <sub>12</sub> | NCS High to NBS0/A0 Change <sup>(1)</sup>  | ncs rd hold length * t <sub>CPSMC</sub> - 2.3                   |       |

| SMC <sub>13</sub> | NCS High to NBS0/A0 Change <sup>(1)</sup>  | ncs rd hold length * t <sub>CPSMC</sub> - 2.3                   |       |

| SMC <sub>14</sub> | NCS High to NBS2/A1 Change <sup>(1)</sup>  | ncs rd hold length * t <sub>CPSMC</sub> - 2.3                   | ns    |

| SMC <sub>15</sub> | NCS High to NBS3 Change <sup>(1)</sup>     | ncs rd hold length * t <sub>CPSMC</sub> - 2.3                   |       |

| SMC <sub>16</sub> | NCS High to A2 - A25 Change <sup>(1)</sup> | ncs rd hold length * t <sub>CPSMC</sub> - 4                     |       |

| SMC <sub>17</sub> | NCS High to NRD Inactive <sup>(1)</sup>    | ncs rd hold length - nrd hold length)* t <sub>CPSMC</sub> - 1.3 |       |

| SMC <sub>18</sub> | NCS Pulse Width                            | ncs rd pulse length * t <sub>CPSMC</sub> - 3.6                  |       |

Note: 1. hold length = total cycle duration - setup duration - pulse duration. "hold length" is for "ncs rd hold length" or "nrd hold length".

| Symbol            | Parameter                  | Min                        | Units |

|-------------------|----------------------------|----------------------------|-------|

|                   | NRD C                      | Controlled (READ_MODE = 1) |       |

| SMC <sub>19</sub> | Data Setup before NRD High | 13.7                       |       |

| SMC <sub>20</sub> | Data Hold after NRD High   | 1                          | ns    |

|                   | NRD C                      | Controlled (READ_MODE = 0) |       |

| SMC <sub>21</sub> | Data Setup before NCS High | 13.3                       |       |

| SMC <sub>22</sub> | Data Hold after NCS High   | 0                          | ns    |

## Table 12-24. SMC Read Signals with no Hold Settings

Table 12-25. SMC Write Signals with Hold Settings

| Symbol            | Parameter                                    | Min                                                              | Units |

|-------------------|----------------------------------------------|------------------------------------------------------------------|-------|

|                   | NRD C                                        | controlled (READ_MODE = 1)                                       |       |

| SMC <sub>23</sub> | Data Out Valid before NWE High               | (nwe pulse length - 1) * t <sub>CPSMC</sub> - 0.9                |       |

| SMC <sub>24</sub> | Data Out Valid after NWE High <sup>(1)</sup> | nwe hold length * t <sub>CPSMC</sub> - 6                         |       |

| SMC <sub>25</sub> | NWE High to NBS0/A0 Change <sup>(1)</sup>    | nwe hold length * t <sub>CPSMC</sub> - 1.9                       |       |

| SMC <sub>26</sub> | NWE High to NBS1 Change <sup>(1)</sup>       | nwe hold length * t <sub>CPSMC</sub> - 1.9                       |       |

| SMC <sub>29</sub> | NWE High to NBS2/A1 Change <sup>(1)</sup>    | nwe hold length * t <sub>CPSMC</sub> - 1.9                       | ns    |

| SMC <sub>30</sub> | NWE High to NBS3 Change <sup>(1)</sup>       | nwe hold length * t <sub>CPSMC</sub> - 1.9                       |       |

| SMC <sub>31</sub> | NWE High to A2 - A25 Change <sup>(1)</sup>   | nwe hold length * t <sub>CPSMC</sub> - 1.7                       |       |

| SMC <sub>32</sub> | NWE High to NCS Inactive <sup>(1)</sup>      | (nwe hold length - ncs wr hold length)* t <sub>CPSMC</sub> - 2.9 |       |

| SMC <sub>33</sub> | NWE Pulse Width                              | nwe pulse length * t <sub>CPSMC</sub> - 0.9                      |       |

|                   | NRD C                                        | controlled (READ_MODE = 0)                                       | U     |

| SMC <sub>34</sub> | Data Out Valid before NCS High               | (ncs wr pulse length - 1)* t <sub>CPSMC</sub> - 4.6              |       |

| SMC <sub>35</sub> | Data Out Valid after NCS High <sup>(1)</sup> | ncs wr hold length * t <sub>CPSMC</sub> - 5.8                    | ns    |

| SMC <sub>36</sub> | NCS High to NWE Inactive <sup>(1)</sup>      | (ncs wr hold length - nwe hold length)* t <sub>CPSMC</sub> - 0.6 |       |

Note: 1. hold length = total cycle duration - setup duration - pulse duration. "hold length" is for "ncs wr hold length" or "nwe hold length"

## 12.10 JTAG Timings

## 12.10.1 JTAG Interface Signals

## Table 12-29. JTAG Interface Timing specification

| Symbol             | Parameter                      | Conditions | Min | Max | Units |

|--------------------|--------------------------------|------------|-----|-----|-------|

| JTAG <sub>0</sub>  | TCK Low Half-period            | (1)        | 6   |     | ns    |

| JTAG <sub>1</sub>  | TCK High Half-period           | (1)        | 3   |     | ns    |

| JTAG <sub>2</sub>  | TCK Period                     | (1)        | 9   |     | ns    |

| JTAG <sub>3</sub>  | TDI, TMS Setup before TCK High | (1)        | 1   |     | ns    |

| JTAG <sub>4</sub>  | TDI, TMS Hold after TCK High   | (1)        | 0   |     | ns    |

| JTAG <sub>5</sub>  | TDO Hold Time                  | (1)        | 4   |     | ns    |

| JTAG <sub>6</sub>  | TCK Low to TDO Valid           | (1)        |     | 6   | ns    |

| JTAG <sub>7</sub>  | Device Inputs Setup Time       | (1)        |     |     | ns    |

| JTAG <sub>8</sub>  | Device Inputs Hold Time        | (1)        |     |     | ns    |

| JTAG <sub>9</sub>  | Device Outputs Hold Time       | (1)        |     |     | ns    |

| JTAG <sub>10</sub> | TCK to Device Outputs Valid    | (1)        |     |     | ns    |

Note: 1.  $V_{VDDIO}$  from 3.0V to 3.6V, maximum external capacitor = 40pF

## Table 12-30. SPI Timings

| Symbol            | Parameter                                  | Conditions                 | Min                        | Max  | Units |

|-------------------|--------------------------------------------|----------------------------|----------------------------|------|-------|

| SPI0              | MISO Setup time before SPCK rises (master) | 3.3V domain <sup>(1)</sup> | $22 + (t_{CPMCK})/2^{(2)}$ |      | ns    |

| SPI <sub>1</sub>  | MISO Hold time after SPCK rises (master)   | 3.3V domain <sup>(1)</sup> | 0                          |      | ns    |

| SPI <sub>2</sub>  | SPCK rising to MOSI Delay (master)         | 3.3V domain <sup>(1)</sup> |                            | 7    | ns    |

| SPI <sub>3</sub>  | MISO Setup time before SPCK falls (master) | 3.3V domain <sup>(1)</sup> | $22 + (t_{CPMCK})/2^{(2)}$ |      | ns    |

| SPI <sub>4</sub>  | MISO Hold time after SPCK falls (master)   | 3.3V domain <sup>(1)</sup> | 0                          |      | ns    |

| SPI <sub>5</sub>  | SPCK falling to MOSI Delay (master)        | 3.3V domain <sup>(1)</sup> |                            | 7    | ns    |

| SPI <sub>6</sub>  | SPCK falling to MISO Delay (slave)         | 3.3V domain <sup>(1)</sup> |                            | 26.5 | ns    |

| SPI7              | MOSI Setup time before SPCK rises (slave)  | 3.3V domain <sup>(1)</sup> | 0                          |      | ns    |

| SPI <sub>8</sub>  | MOSI Hold time after SPCK rises (slave)    | 3.3V domain <sup>(1)</sup> | 1.5                        |      | ns    |

| SPI <sub>9</sub>  | SPCK rising to MISO Delay (slave)          | 3.3V domain <sup>(1)</sup> |                            | 27   | ns    |

| SPI <sub>10</sub> | MOSI Setup time before SPCK falls (slave)  | 3.3V domain <sup>(1)</sup> | 0                          |      | ns    |

| SPI <sub>11</sub> | MOSI Hold time after SPCK falls (slave)    | 3.3V domain <sup>(1)</sup> | 1                          |      | ns    |

Notes: 1. 3.3V domain:  $V_{VDDIO}$  from 3.0V to 3.6V, maximum external capacitor = 40 pF.

2.  $t_{CPMCK}$ : Master Clock period in ns.

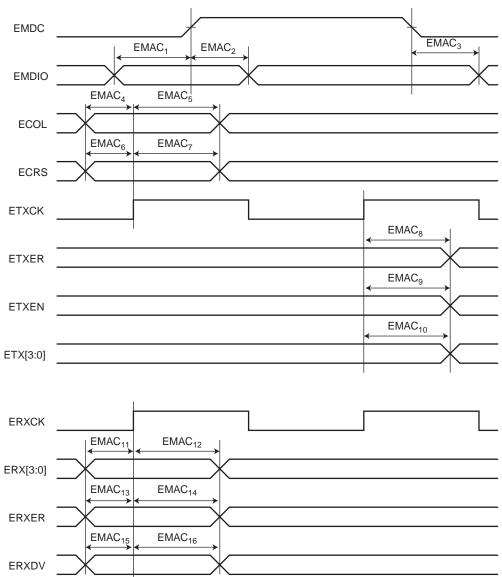

# **12.12 MACB Characteristics**

## Table 12-31. Ethernet MAC Signals

| Symbol            | Parameter                        | Conditions                | Min (ns) | Max (ns) |

|-------------------|----------------------------------|---------------------------|----------|----------|

| EMAC <sub>1</sub> | Setup for EMDIO from EMDC rising | Load: 20pF <sup>(2)</sup> |          |          |

| EMAC <sub>2</sub> | Hold for EMDIO from EMDC rising  | Load: 20pF <sup>(2)</sup> |          |          |

| EMAC <sub>3</sub> | EMDIO toggling from EMDC falling | Load: 20pF <sup>(2)</sup> |          |          |

Notes: 1. f: MCK frequency (MHz)

2.  $V_{VDDIO}$  from 3.0V to 3.6V, maximum external capacitor = 20 pF

## Table 12-32. Ethernet MAC MII Specific Signals

| Symbol             | Parameter                        | Conditions                | Min (ns) | Max (ns) |

|--------------------|----------------------------------|---------------------------|----------|----------|

| EMAC <sub>4</sub>  | Setup for ECOL from ETXCK rising | Load: 20pF <sup>(1)</sup> | 3        |          |

| EMAC <sub>5</sub>  | Hold for ECOL from ETXCK rising  | Load: 20pF (1)            | 0        |          |

| EMAC <sub>6</sub>  | Setup for ECRS from ETXCK rising | Load: 20pF <sup>(1)</sup> | 3        |          |

| EMAC <sub>7</sub>  | Hold for ECRS from ETXCK rising  | Load: 20pF <sup>(1)</sup> | 0        |          |

| EMAC <sub>8</sub>  | ETXER toggling from ETXCK rising | Load: 20pF <sup>(1)</sup> |          | 15       |

| EMAC <sub>9</sub>  | ETXEN toggling from ETXCK rising | Load: 20pF <sup>(1)</sup> |          | 15       |

| EMAC <sub>10</sub> | ETX toggling from ETXCK rising   | Load: 20pF <sup>(1)</sup> |          | 15       |

| EMAC <sub>11</sub> | Setup for ERX from ERXCK         | Load: 20pF <sup>(1)</sup> | 1        |          |

## Table 12-32. Ethernet MAC MII Specific Signals

| Symbol             | Parameter                  | Conditions                | Min (ns) | Max (ns) |

|--------------------|----------------------------|---------------------------|----------|----------|

| EMAC <sub>12</sub> | Hold for ERX from ERXCK    | Load: 20pF <sup>(1)</sup> | 1.5      |          |

| EMAC <sub>13</sub> | Setup for ERXER from ERXCK | Load: 20pF <sup>(1)</sup> | 1        |          |

| EMAC <sub>14</sub> | Hold for ERXER from ERXCK  | Load: 20pF <sup>(1)</sup> | 0.5      |          |

| EMAC <sub>15</sub> | Setup for ERXDV from ERXCK | Load: 20pF <sup>(1)</sup> | 1.5      |          |

| EMAC <sub>16</sub> | Hold for ERXDV from ERXCK  | Load: 20pF <sup>(1)</sup> | 1        |          |

Note: 1.  $V_{VDDIO}$  from 3.0V to 3.6V, maximum external capacitor = 20 pF

## Figure 12-10. Ethernet MAC MII Mode

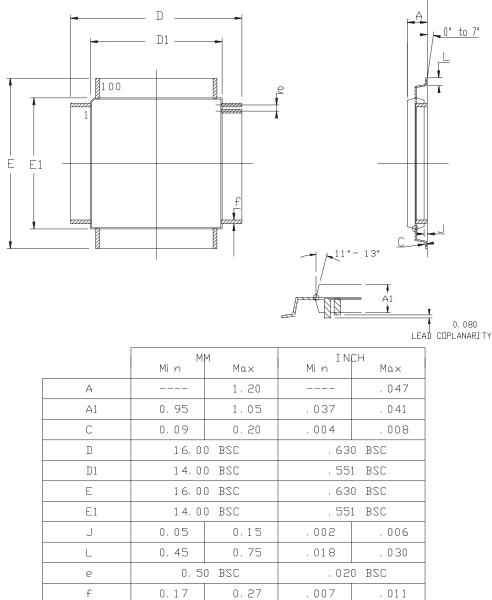

## 13.2 Package Drawings

### Table 13-2. Device and Package Maximum Weight

| 500 mg |

|--------|

|--------|

## Table 13-3. Package Characteristics

| Moisture Sensitivity Level | Jdec J-STD0-20D - MSL 3 |

|----------------------------|-------------------------|

|----------------------------|-------------------------|

### Table 13-4.Package Reference

| JEDEC Drawing Reference | MS-026 |

|-------------------------|--------|

| JESD97 Classification   | E3     |

None.

#### 15.2.9 USART

ISO7816 info register US\_NER cannot be read The NER register always returns zero.

Fix/Workaround None

### 15.2.10 Processor and Architecture

1. LDM instruction with PC in the register list and without ++ increments Rp For LDM with PC in the register list: the instruction behaves as if the ++ field is always set, ie the pointer is always updated. This happens even if the ++ field is cleared. Specifically, the increment of the pointer is done in parallel with the testing of R12.

Fix/Workaround

None.

#### 2. RETE instruction does not clear SREG[L] from interrupts.

The RETE instruction clears  $\mbox{SREG}[L]$  as expected from exceptions.  $\mbox{Fix/Workaround}$

When using the STCOND instruction, clear SREG[L] in the stacked value of SR before returning from interrupts with RETE.

#### 3. Exceptions when system stack is protected by MPU

RETS behaves incorrectly when MPU is enabled and MPU is configured so that system stack is not readable in unprivileged mode.

#### **Fix/Woraround**

Workaround 1: Make system stack readable in unprivileged mode, or

Workaround 2: Return from supervisor mode using rete instead of rets. This requires :

1. Changing the mode bits from 001b to 110b before issuing the instruction. Updating the mode bits to the desired value must be done using a single mtsr instruction so it is done atomically. Even if this step is described in general as not safe in the UC technical reference guide, it is safe in this very specific case.

2. Execute the RETE instruction.

## 15.4 Rev. H

15.4.1 PWM

## 1. PWM channel interrupt enabling triggers an interrupt

When enabling a PWM channel that is configured with center aligned period (CALG=1), an interrupt is signalled.

#### Fix/Workaround

When using center aligned mode, enable the channel and read the status before channel interrupt is enabled.

### 2. PWM counter restarts at 0x0001

The PWM counter restarts at 0x0001 and not 0x0000 as specified. Because of this the first PWM period has one more clock cycle.

Fix/Workaround

- The first period is 0x0000, 0x0001, ..., period

- Consecutive periods are 0x0001, 0x0002, ..., period

### 3. PWM update period to a 0 value does not work

It is impossible to update a period equal to 0 by the using the PWM update register (PWM\_CUPD).

#### **Fix/Workaround**

Do not update the PWM\_CUPD register with a value equal to 0.

15.4.2 ADC

### 1. Sleep Mode activation needs additional A to D conversion

If the ADC sleep mode is activated when the ADC is idle the ADC will not enter sleep mode before after the next AD conversion.

### Fix/Workaround

Activate the sleep mode in the mode register and then perform an AD conversion.

15.4.3 SPI

### 1. SPI Slave / PDCA transfer: no TX UNDERRUN flag

There is no TX UNDERRUN flag available, therefore in SPI slave mode, there is no way to be informed of a character lost in transmission.

### Fix/Workaround

For PDCA transfer: none.

## 2. SPI FDIV option does not work

Selecting clock signal using FDIV = 1 does not work as specified.

#### **Fix/Workaround**

Do not set FDIV = 1

# 3. SPI disable does not work in SLAVE mode. Fix/Workaround

Read the last received data, then perform a Software Reset.

RETS behaves incorrectly when MPU is enabled and MPU is configured so that system stack is not readable in unprivileged mode.

### Fix/Woraround

Workaround 1: Make system stack readable in unprivileged mode, or

Workaround 2: Return from supervisor mode using rete instead of rets. This requires :

1. Changing the mode bits from 001b to 110b before issuing the instruction. Updating the mode bits to the desired value must be done using a single mtsr instruction so it is done atomically. Even if this step is described in general as not safe in the UC technical reference guide, it is safe in this very specific case.

2. Execute the RETE instruction.

#### 12. CPU cannot operate on a divided slow clock (internal RC oscillator) Fix/Workaround

Do not run the CPU on a divided slow clock.

### 13. LDM instruction with PC in the register list and without ++ increments Rp

For LDM with PC in the register list: the instruction behaves as if the ++ field is always set, ie the pointer is always updated. This happens even if the ++ field is cleared. Specifically, the increment of the pointer is done in parallel with the testing of R12. **Fix/Workaround**

None.

#### 14. RETE instruction does not clear SREG[L] from interrupts.

The RETE instruction clears SREG[L] as expected from exceptions. **Fix/Workaround**

When using the STCOND instruction, clear SREG[L] in the stacked value of SR before returning from interrupts with RETE.

#### 15. Exceptions when system stack is protected by MPU

RETS behaves incorrectly when MPU is enabled and MPU is configured so that system stack is not readable in unprivileged mode.

#### **Fix/Woraround**

Workaround 1: Make system stack readable in unprivileged mode, or

Workaround 2: Return from supervisor mode using rete instead of rets. This requires :

1. Changing the mode bits from 001b to 110b before issuing the instruction. Updating the mode bits to the desired value must be done using a single mtsr instruction so it is done atomically. Even if this step is described in general as not safe in the UC technical reference guide, it is safe in this very specific case.

2. Execute the RETE instruction.

#### 15.5.6 SDRAMC

### 1. Code execution from external SDRAM does not work

Code execution from SDRAM does not work.

#### Fix/Workaround

Do not run code from SDRAM.

## 2. SDRAM SDCKE rise at the same time as SDCK while exiting self-refresh mode SDCKE rise at the same time as SDCK while exiting self-refresh mode.

#### Fix/Workaround

None.

#### 15.5.7 USART

1. USART Manchester Encoder Not Working Manchester encoding/decoding is not working.

#### Fix/Workaround

Do not use manchester encoding.

#### Atmel Corporation

2325 Orchard Parkway San Jose, CA 95131 USA Tel: (+1)(408) 441-0311 Fax: (+1)(408) 487-2600 www.atmel.com

#### Atmel Asia Limited

Unit 1-5 & 16, 19/F BEA Tower, Millennium City 5 418 Kwun Tong Road Kwun Tong, Kowloon HONG KONG Tel: (+852) 2245-6100 Fax: (+852) 2722-1369

#### Atmel Munich GmbH

Business Campus Parkring 4 D-85748 Garching b. Munich GERMANY Tel: (+49) 89-31970-0 Fax: (+49) 89-3194621

#### Atmel Japan

16F, Shin Osaki Kangyo Bldg. 1-6-4 Osaka Shinagawa-ku Tokyo 104-0032 JAPAN Tel: (+81) 3-6417-0300 Fax: (+81) 3-6417-0370

#### © 2012 Atmel Corporation. All rights reserved.

Atmel<sup>®</sup>, Atmel logo and combinations thereof, AVR<sup>®</sup> and others are registered trademarks or trademarks of Atmel Corporation or its subsidiaries. Other terms and product names may be trademarks of others.

Disclaimer: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN THE ATMEL TERMS AND CONDITIONS OF SALES LOCATED ON THE ATMEL WEBSITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDENTAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS AND PROF-ITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and product descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically provided otherwise, Atmel products are not suit-able for, and shall not be used in, automotive applications. Atmel products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life.