# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                    |

|----------------------------|--------------------------------------------------------------------|

| Product Status             | Active                                                             |

| Core Processor             | AVR                                                                |

| Core Size                  | 32-Bit Single-Core                                                 |

| Speed                      | 66MHz                                                              |

| Connectivity               | EBI/EMI, Ethernet, I <sup>2</sup> C, SPI, SSC, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                              |

| Number of I/O              | 109                                                                |

| Program Memory Size        | 128KB (128K x 8)                                                   |

| Program Memory Type        | FLASH                                                              |

| EEPROM Size                | -                                                                  |

| RAM Size                   | 32K x 8                                                            |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 3.6V                                                       |

| Data Converters            | A/D 8x10b                                                          |

| Oscillator Type            | Internal                                                           |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                  |

| Mounting Type              | Surface Mount                                                      |

| Package / Case             | 144-LQFP                                                           |

| Supplier Device Package    | 144-LQFP (20x20)                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/atmel/at32uc3a0128au-alut     |

|                            |                                                                    |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 2. Configuration Summary

| Device       | Flash      | SRAM      | Ext. Bus Interface | Ethernet<br>MAC | Package                     |

|--------------|------------|-----------|--------------------|-----------------|-----------------------------|

| AT32UC3A0512 | 512 Kbytes | 64 Kbytes | yes                | yes             | 144 pin LQFP<br>144 pin BGA |

| AT32UC3A0256 | 256 Kbytes | 64 Kbytes | yes                | yes             | 144 pin LQFP<br>144 pin BGA |

| AT32UC3A0128 | 128 Kbytes | 32 Kbytes | yes                | yes             | 144 pin LQFP<br>144 pin BGA |

| AT32UC3A1512 | 512 Kbytes | 64 Kbytes | no                 | yes             | 100 pin TQFP                |

| AT32UC3A1256 | 256 Kbytes | 64 Kbytes | no                 | yes             | 100 pin TQFP                |

| AT32UC3A1128 | 128 Kbytes | 32 Kbytes | no                 | yes             | 100 pin TQFP                |

The table below lists all AT32UC3A memory and package configurations:

## 3. Abbreviations

- GCLK: Power Manager Generic Clock

- GPIO: General Purpose Input/Output

- HSB: High Speed Bus

- MPU: Memory Protection Unit

- OCD: On Chip Debug

- PB: Peripheral Bus

- PDCA: Peripheral Direct Memory Access Controller (PDC) version A

- USBB: USB On-The-GO Controller version B

## Table 5-1.Signal Description List

| Signal Name   | Function                                | Туре            | Active<br>Level | Comments    |

|---------------|-----------------------------------------|-----------------|-----------------|-------------|

|               | Analog to Digital Co                    | nverter - ADC   |                 |             |

| AD0 - AD7     | Analog input pins                       | Analog<br>input |                 |             |

| ADVREF        | Analog positive reference voltage input | Analog<br>input |                 | 2.6 to 3.6V |

|               | Pulse Width Modu                        | lator - PWM     | •               |             |

| PWM0 - PWM6   | PWM Output Pins                         | Output          |                 |             |

|               | Universal Serial Bus                    | Device - USB    |                 |             |

| DDM           | USB Device Port Data -                  | Analog          |                 |             |

| DDP           | USB Device Port Data +                  | Analog          |                 |             |

| VBUS          | USB VBUS Monitor and OTG Negociation    | Analog<br>Input |                 |             |

| USBID         | ID Pin of the USB Bus                   | Input           |                 |             |

| USB_VBOF      | USB VBUS On/off: bus power control port | output          |                 |             |

|               | Audio Bitstream D                       | AC (ABDAC)      |                 | 1           |

| DATA0-DATA1   | D/A Data out                            | Outpu           |                 |             |

| DATAN0-DATAN1 | D/A Data inverted out                   | Outpu           |                 |             |

## Table 6-2.VQFP144 Package Pinout

| 22 | PB31    |

|----|---------|

| 23 | RESET_N |

| 24 | PX05    |

| 25 | PA00    |

| 26 | PX06    |

| 27 | PA01    |

| 28 | GND     |

| 29 | VDDCORE |

| 30 | PA02    |

| 31 | PX07    |

| 32 | PA03    |

| 33 | PX08    |

| 34 | PA04    |

| 35 | PX09    |

| 36 | VDDIO   |

|    |         |

| 58 | PA16  |  |  |  |

|----|-------|--|--|--|

| 59 | PX15  |  |  |  |

| 60 | PA17  |  |  |  |

| 61 | PX16  |  |  |  |

| 62 | PA18  |  |  |  |

| 63 | PX17  |  |  |  |

| 64 | PA19  |  |  |  |

| 65 | PX18  |  |  |  |

| 66 | PA20  |  |  |  |

| 67 | PX19  |  |  |  |

| 68 | VBUS  |  |  |  |

| 69 | VDDIO |  |  |  |

| 70 | DM    |  |  |  |

| 71 | DP    |  |  |  |

| 72 | GND   |  |  |  |

| 94  | GND   |

|-----|-------|

| 95  | PX23  |

| 96  | PB02  |

| 97  | PX24  |

| 98  | PB03  |

| 99  | PX25  |

| 100 | PB04  |

| 101 | PX26  |

| 102 | PB05  |

| 103 | PX27  |

| 104 | PB06  |

| 105 | PX28  |

| 106 | PB07  |

| 107 | PX29  |

| 108 | VDDIO |

|     |       |

| 130 | TDO     |

|-----|---------|

| 131 | TDI     |

| 132 | PC04    |

| 133 | PC05    |

| 134 | PB15    |

| 135 | PX35    |

| 136 | PB16    |

| 137 | PX36    |

| 138 | VDDCORE |

| 139 | PB17    |

| 140 | PX37    |

| 141 | PB18    |

| 142 | PX38    |

| 143 | PB19    |

| 144 | PX39    |

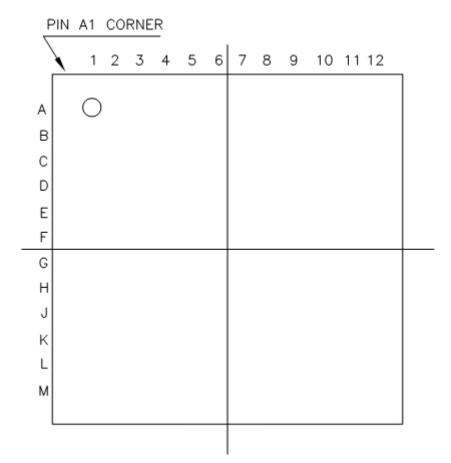

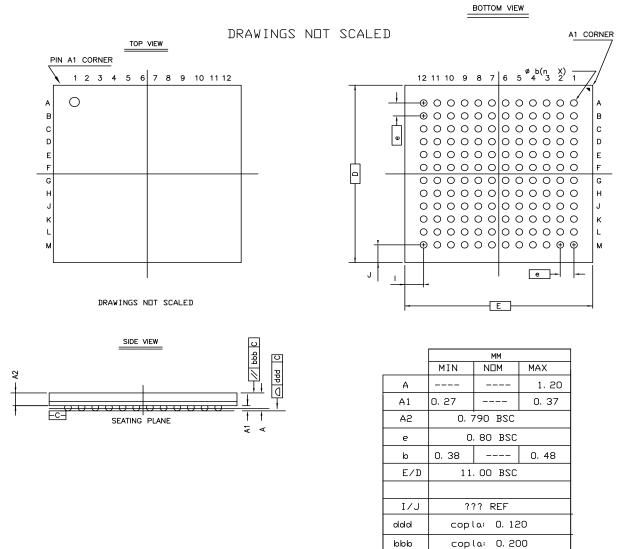

## Figure 6-3. BGA144 Pinout

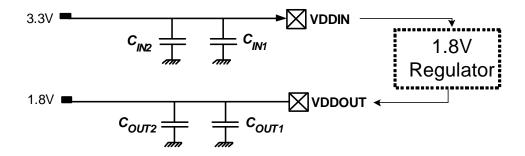

## 7.2 Voltage Regulator

#### 7.2.1 Single Power Supply

The AT32UC3A embeds a voltage regulator that converts from 3.3V to 1.8V. The regulator takes its input voltage from VDDIN, and supplies the output voltage on VDDOUT. VDDOUT should be externally connected to the 1.8V domains.

Adequate input supply decoupling is mandatory for VDDIN in order to improve startup stability and reduce source voltage drop. Two input decoupling capacitors must be placed close to the chip.

Adequate output supply decoupling is mandatory for VDDOUT to reduce ripple and avoid oscillations. The best way to achieve this is to use two capacitors in parallel between VDDOUT and GND as close to the chip as possible

Refer to Section 12.3 on page 42 for decoupling capacitors values and regulator characteristics

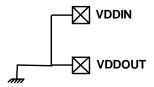

#### 7.2.2 Dual Power Supply

In case of dual power supply, VDDIN and VDDOUT should be connected to ground to prevent from leakage current.

| Table 10-8. | PDC Handshake Signals         |

|-------------|-------------------------------|

| PID Value   | Peripheral module & direction |

| 4           | USART2 - RX                   |

| 5           | USART3 - RX                   |

| 6           | TWI - RX                      |

| 7           | SPI0 - RX                     |

| 8           | SPI1 - RX                     |

| 9           | SSC - TX                      |

| 10          | USART0 - TX                   |

| 11          | USART1 - TX                   |

| 12          | USART2 - TX                   |

| 13          | USART3 - TX                   |

| 14          | TWI - TX                      |

| 15          | SPI0 - TX                     |

| 16          | SPI1 - TX                     |

| 17          | ABDAC                         |

Table 10-8.

PDC Handshake Signals

## 10.7 Peripheral Multiplexing on I/O lines

Each GPIO line can be assigned to one of 3 peripheral functions; A, B or C. The following table define how the I/O lines on the peripherals A, B and C are multiplexed by the GPIO.

Table 10-9.

GPIO Controller Function Multiplexing

| TQFP100 | VQFP144 | PIN  | GPIO Pin | Function A             | Function B      | Function C      |

|---------|---------|------|----------|------------------------|-----------------|-----------------|

| 19      | 25      | PA00 | GPIO 0   | USART0 - RXD           | TC - CLK0       |                 |

| 20      | 27      | PA01 | GPIO 1   | USART0 - TXD           | TC - CLK1       |                 |

| 23      | 30      | PA02 | GPIO 2   | USART0 - CLK           | TC - CLK2       |                 |

| 24      | 32      | PA03 | GPIO 3   | USART0 - RTS           | EIM - EXTINT[4] | DAC - DATA[0]   |

| 25      | 34      | PA04 | GPIO 4   | USART0 - CTS           | EIM - EXTINT[5] | DAC - DATAN[0]  |

| 26      | 39      | PA05 | GPIO 5   | USART1 - RXD           | PWM - PWM[4]    |                 |

| 27      | 41      | PA06 | GPIO 6   | USART1 - TXD           | PWM - PWM[5]    |                 |

| 28      | 43      | PA07 | GPIO 7   | USART1 - CLK           | PM - GCLK[0]    | SPI0 - NPCS[3]  |

| 29      | 45      | PA08 | GPIO 8   | USART1 - RTS           | SPI0 - NPCS[1]  | EIM - EXTINT[7] |

| 30      | 47      | PA09 | GPIO 9   | USART1 - CTS           | SPI0 - NPCS[2]  | MACB - WOL      |

| 31      | 48      | PA10 | GPIO 10  | SPI0 - NPCS[0]         | EIM - EXTINT[6] |                 |

| 33      | 50      | PA11 | GPIO 11  | SPI0 - MISO            | USB - USB_ID    |                 |

| 36      | 53      | PA12 | GPIO 12  | SPI0 - MOSI            | USB - USB_VBOF  |                 |

| 37      | 54      | PA13 | GPIO 13  | SPI0 - SCK             |                 |                 |

| 39      | 56      | PA14 | GPIO 14  | SSC -<br>TX_FRAME_SYNC | SPI1 - NPCS[0]  | EBI - NCS[0]    |

| 40      | 57      | PA15 | GPIO 15  | SSC - TX_CLOCK         | SPI1 - SCK      | EBI - ADDR[20]  |

Table 10-9.

GPIO Controller Function Multiplexing

| Table 10-9. | GFIO COIII |      | in manupicking | 1                      |                 |                |

|-------------|------------|------|----------------|------------------------|-----------------|----------------|

| 41          | 58         | PA16 | GPIO 16        | SSC - TX_DATA          | SPI1 - MOSI     | EBI - ADDR[21] |

| 42          | 60         | PA17 | GPIO 17        | SSC - RX_DATA          | SPI1 - MISO     | EBI - ADDR[22] |

| 43          | 62         | PA18 | GPIO 18        | SSC - RX_CLOCK         | SPI1 - NPCS[1]  | MACB - WOL     |

| 44          | 64         | PA19 | GPIO 19        | SSC -<br>RX_FRAME_SYNC | SPI1 - NPCS[2]  |                |

| 45          | 66         | PA20 | GPIO 20        | EIM - EXTINT[8]        | SPI1 - NPCS[3]  |                |

| 51          | 73         | PA21 | GPIO 21        | ADC - AD[0]            | EIM - EXTINT[0] | USB - USB_ID   |

| 52          | 74         | PA22 | GPIO 22        | ADC - AD[1]            | EIM - EXTINT[1] | USB - USB_VBOF |

| 53          | 75         | PA23 | GPIO 23        | ADC - AD[2]            | EIM - EXTINT[2] | DAC - DATA[1]  |

| 54          | 76         | PA24 | GPIO 24        | ADC - AD[3]            | EIM - EXTINT[3] | DAC - DATAN[1] |

| 55          | 77         | PA25 | GPIO 25        | ADC - AD[4]            | EIM - SCAN[0]   | EBI - NCS[0]   |

| 56          | 78         | PA26 | GPIO 26        | ADC - AD[5]            | EIM - SCAN[1]   | EBI - ADDR[20] |

| 57          | 79         | PA27 | GPIO 27        | ADC - AD[6]            | EIM - SCAN[2]   | EBI - ADDR[21] |

| 58          | 80         | PA28 | GPIO 28        | ADC - AD[7]            | EIM - SCAN[3]   | EBI - ADDR[22] |

| 83          | 122        | PA29 | GPIO 29        | TWI - SDA              | USART2 - RTS    |                |

| 84          | 123        | PA30 | GPIO 30        | TWI - SCL              | USART2 - CTS    |                |

| 65          | 88         | PB00 | GPIO 32        | MACB - TX_CLK          | USART2 - RTS    | USART3 - RTS   |

| 66          | 90         | PB01 | GPIO 33        | MACB - TX_EN           | USART2 - CTS    | USART3 - CTS   |

| 70          | 96         | PB02 | GPIO 34        | MACB - TXD[0]          | DAC - DATA[0]   |                |

| 71          | 98         | PB03 | GPIO 35        | MACB - TXD[1]          | DAC - DATAN[0]  |                |

| 72          | 100        | PB04 | GPIO 36        | MACB - CRS             | USART3 - CLK    | EBI - NCS[3]   |

| 73          | 102        | PB05 | GPIO 37        | MACB - RXD[0]          | DAC - DATA[1]   |                |

| 74          | 104        | PB06 | GPIO 38        | MACB - RXD[1]          | DAC - DATAN[1]  |                |

| 75          | 106        | PB07 | GPIO 39        | MACB - RX_ER           |                 |                |

| 76          | 111        | PB08 | GPIO 40        | MACB - MDC             |                 |                |

| 77          | 113        | PB09 | GPIO 41        | MACB - MDIO            |                 |                |

| 78          | 115        | PB10 | GPIO 42        | MACB - TXD[2]          | USART3 - RXD    | EBI - SDCK     |

| 81          | 119        | PB11 | GPIO 43        | MACB - TXD[3]          | USART3 - TXD    | EBI - SDCKE    |

| 82          | 121        | PB12 | GPIO 44        | MACB - TX_ER           | TC - CLK0       | EBI - RAS      |

| 87          | 126        | PB13 | GPIO 45        | MACB - RXD[2]          | TC - CLK1       | EBI - CAS      |

| 88          | 127        | PB14 | GPIO 46        | MACB - RXD[3]          | TC - CLK2       | EBI - SDWE     |

| 95          | 134        | PB15 | GPIO 47        | MACB - RX_DV           |                 |                |

| 96          | 136        | PB16 | GPIO 48        | MACB - COL             | USB - USB_ID    | EBI - SDA10    |

| 98          | 139        | PB17 | GPIO 49        | MACB - RX_CLK          | USB - USB_VBOF  | EBI - ADDR[23] |

| 99          | 141        | PB18 | GPIO 50        | MACB - SPEED           | ADC - TRIGGER   | PWM - PWM[6]   |

| 100         | 143        | PB19 | GPIO 51        | PWM - PWM[0]           | PM - GCLK[0]    | EIM - SCAN[4]  |

| 1           | 3          | PB20 | GPIO 52        | PWM - PWM[1]           | PM - GCLK[1]    | EIM - SCAN[5]  |

| 2           | 5          | PB21 | GPIO 53        | PWM - PWM[2]           | PM - GCLK[2]    | EIM - SCAN[6]  |

| 3           | 6          | PB22 | GPIO 54        | PWM - PWM[3]           | PM - GCLK[3]    | EIM - SCAN[7]  |

|             | 9          | PB23 | GPIO 55        | TC - A0                | USART1 - DCD    |                |

These figures represent the power consumption measured on the power supplies.

Table 12-9.

Power Consumption for Different Modes

| Mode                                                                                                                                                                               | Conditions                                                                                                                                                                                                                                     |            | Тур. | Unit |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------|------|

|                                                                                                                                                                                    | Typ : Ta =25 °C                                                                                                                                                                                                                                | f = 12 MHz | 9    | mA   |

|                                                                                                                                                                                    | CPU running from flash <sup>(1)</sup> .                                                                                                                                                                                                        | f = 24 MHz | 15   | mA   |

|                                                                                                                                                                                    | VDDIN=3.3 V. VDDCORE =1.8V.<br>CPU clocked from PLL0 at f MHz                                                                                                                                                                                  | f = 36MHz  | 20   | mA   |

|                                                                                                                                                                                    | Voltage regulator is on.                                                                                                                                                                                                                       | f = 50 MHz | 28   | mA   |

| Active                                                                                                                                                                             | <ul> <li>XIN0 : external clock. <sup>(1)</sup></li> <li>XIN1 stopped. XIN32 stopped</li> <li>PLL0 running</li> <li>All peripheral clocks activated.</li> <li>GPIOs on internal pull-up.</li> <li>JTAG unconnected with ext pull-up.</li> </ul> | f = 66 MHz | 36.3 | mA   |

|                                                                                                                                                                                    | Typ : Ta = 25 °C                                                                                                                                                                                                                               | f = 12 MHz | 5    | mA   |

|                                                                                                                                                                                    | CPU running from flash <sup>(1)</sup> .<br>VDDIN=3.3 V. VDDCORE =1.8V.                                                                                                                                                                         | f = 24 MHz | 10   | mA   |

|                                                                                                                                                                                    | CPU clocked from PLL0 at f MHz                                                                                                                                                                                                                 | f = 36MHz  | 14   | mA   |

|                                                                                                                                                                                    | Voltage regulator is on.                                                                                                                                                                                                                       | f = 50 MHz | 19   | mA   |

| Idle XIN0 : external clock.<br>XIN1 stopped. XIN32 stopped<br>PLL0 running<br>All peripheral clocks activated.<br>GPIOs on internal pull-up.<br>JTAG unconnected with ext pull-up. | f = 66 MHz                                                                                                                                                                                                                                     | 25.5       | mA   |      |

|                                                                                                                                                                                    | Typ : Ta = 25 °C<br>CPU running from flash <sup>(1)</sup> .<br>CPU clocked from PLL0 at f MHz<br>Voltage regulator is on.                                                                                                                      | f = 12 MHz | 3    | mA   |

|                                                                                                                                                                                    |                                                                                                                                                                                                                                                | f = 24 MHz | 6    | mA   |

|                                                                                                                                                                                    |                                                                                                                                                                                                                                                | f = 36MHz  | 9    | mA   |

| <b>-</b>                                                                                                                                                                           | XIN0 : external clock.                                                                                                                                                                                                                         | f = 50 MHz | 13   | mA   |

| Frozen                                                                                                                                                                             | XIN1 stopped. XIN32 stopped<br>PLL0 running<br>All peripheral clocks activated.<br>GPIOs on internal pull-up.<br>JTAG unconnected with ext pull-up.                                                                                            | f = 66 MHz | 16.8 | mA   |

|                                                                                                                                                                                    | Typ : Ta = 25 °C                                                                                                                                                                                                                               | f = 12 MHz | 1    | mA   |

|                                                                                                                                                                                    | CPU running from flash <sup>(1)</sup> .                                                                                                                                                                                                        | f = 24 MHz | 2    | mA   |

| Standby                                                                                                                                                                            | CPU clocked from PLL0 at f MHz<br>Voltage regulator is on.                                                                                                                                                                                     | f = 36MHz  | 3    | mA   |

|                                                                                                                                                                                    | XIN0 : external clock.                                                                                                                                                                                                                         | f = 50 MHz | 4    | mA   |

|                                                                                                                                                                                    | XIN1 stopped. XIN32 stopped<br>PLL0 running<br>All peripheral clocks activated.<br>GPIOs on internal pull-up.<br>JTAG unconnected with ext pull-up.                                                                                            | f = 66 MHz | 4.8  | mA   |

#### Table 12-9. Power Consumption for Different Modes

| Mode     | Conditions                                                                                                                                 | Тур.    | Unit |    |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------|---------|------|----|

|          | Typ : Ta = 25 °C.<br>CPU is in stop mode                                                                                                   | on Amp0 | 47   | uA |

| Stop     | GPIOs on internal pull-up.<br>All peripheral clocks de-activated.<br>DM and DP pins connected to ground.<br>XIN0,Xin1 and XIN2 are stopped | on Amp1 | 40   | uA |

|          | Typ : Ta = 25 °C.CPU is in deepstop mode                                                                                                   | on Amp0 | 36   | uA |

| Deepstop | GPIOs on internal pull-up.<br>All peripheral clocks de-activated.<br>DM and DP pins connected to ground.<br>XIN0,Xin1 and XIN2 are stopped | on Amp1 | 28   | uA |

|          | Typ : Ta = 25 °C. CPU is in static mode                                                                                                    | on Amp0 | 25   | uA |

| Static   | GPIOs on internal pull-up.<br>All peripheral clocks de-activated.<br>DM and DP pins connected to ground.<br>XIN0,Xin1 and XIN2 are stopped | on Amp1 | 14   | uA |

1. Core frequency is generated from XIN0 using the PLL so that 140 MHz < fpll0 < 160 MHz and 10 MHz < fxin0 < 12MHz

| Peripheral | Тур. | Unit   |

|------------|------|--------|

| GPIO       | 37   |        |

| SMC        | 10   |        |

| SDRAMC     | 4    |        |

| ADC        | 18   |        |

| EBI        | 31   |        |

| INTC       | 25   |        |

| TWI        | 14   |        |

| MACB       | 45   |        |

| PDCA       | 30   | μA/MHz |

| PWM        | 36   |        |

| RTC        | 7    |        |

| SPI        | 13   |        |

| SSC        | 13   |        |

| TC         | 10   |        |

| USART      | 35   |        |

| USB        | 45   |        |

#### Table 12-10. Power Consumption by Peripheral in Active Mode

## 12.6 Clock Characteristics

These parameters are given in the following conditions:

## **12.11 SPI Characteristics**

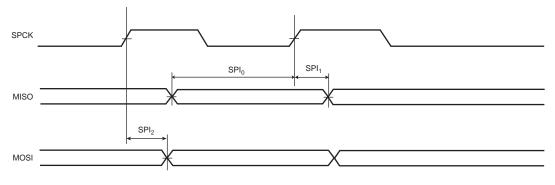

#### Table 12-30. SPI Timings

| Symbol            | Parameter                                  | Conditions                 | Min                                         | Max  | Units |

|-------------------|--------------------------------------------|----------------------------|---------------------------------------------|------|-------|

| SPI0              | MISO Setup time before SPCK rises (master) | 3.3V domain <sup>(1)</sup> | 22 + (t <sub>СРМСК</sub> )/2 <sup>(2)</sup> |      | ns    |

| SPI <sub>1</sub>  | MISO Hold time after SPCK rises (master)   | 3.3V domain <sup>(1)</sup> | 0                                           |      | ns    |

| SPI <sub>2</sub>  | SPCK rising to MOSI Delay (master)         | 3.3V domain <sup>(1)</sup> |                                             | 7    | ns    |

| SPI <sub>3</sub>  | MISO Setup time before SPCK falls (master) | 3.3V domain <sup>(1)</sup> | $22 + (t_{CPMCK})/2^{(2)}$                  |      | ns    |

| SPI4              | MISO Hold time after SPCK falls (master)   | 3.3V domain <sup>(1)</sup> | 0                                           |      | ns    |

| SPI <sub>5</sub>  | SPCK falling to MOSI Delay (master)        | 3.3V domain <sup>(1)</sup> |                                             | 7    | ns    |

| SPI <sub>6</sub>  | SPCK falling to MISO Delay (slave)         | 3.3V domain <sup>(1)</sup> |                                             | 26.5 | ns    |

| SPI7              | MOSI Setup time before SPCK rises (slave)  | 3.3V domain <sup>(1)</sup> | 0                                           |      | ns    |

| SPI <sub>8</sub>  | MOSI Hold time after SPCK rises (slave)    | 3.3V domain <sup>(1)</sup> | 1.5                                         |      | ns    |

| SPI <sub>9</sub>  | SPCK rising to MISO Delay (slave)          | 3.3V domain <sup>(1)</sup> |                                             | 27   | ns    |

| SPI <sub>10</sub> | MOSI Setup time before SPCK falls (slave)  | 3.3V domain <sup>(1)</sup> | 0                                           |      | ns    |

| SPI <sub>11</sub> | MOSI Hold time after SPCK falls (slave)    | 3.3V domain <sup>(1)</sup> | 1                                           |      | ns    |

Notes: 1. 3.3V domain:  $V_{VDDIO}$  from 3.0V to 3.6V, maximum external capacitor = 40 pF.

2.  $t_{CPMCK}$ : Master Clock period in ns.

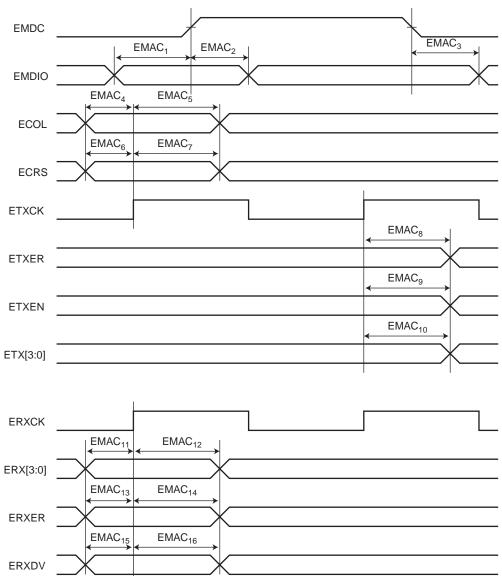

## **12.12 MACB Characteristics**

#### Table 12-31. Ethernet MAC Signals

| Symbol            | Parameter                        | Conditions                | Min (ns) | Max (ns) |

|-------------------|----------------------------------|---------------------------|----------|----------|

| EMAC <sub>1</sub> | Setup for EMDIO from EMDC rising | Load: 20pF <sup>(2)</sup> |          |          |

| EMAC <sub>2</sub> | Hold for EMDIO from EMDC rising  | Load: 20pF <sup>(2)</sup> |          |          |

| EMAC <sub>3</sub> | EMDIO toggling from EMDC falling | Load: 20pF <sup>(2)</sup> |          |          |

Notes: 1. f: MCK frequency (MHz)

2.  $V_{\text{VDDIO}}$  from 3.0V to 3.6V, maximum external capacitor = 20 pF

#### Table 12-32. Ethernet MAC MII Specific Signals

| Symbol             | Parameter                        | Conditions                | Min (ns) | Max (ns) |

|--------------------|----------------------------------|---------------------------|----------|----------|

| EMAC <sub>4</sub>  | Setup for ECOL from ETXCK rising | Load: 20pF <sup>(1)</sup> | 3        |          |

| EMAC <sub>5</sub>  | Hold for ECOL from ETXCK rising  | Load: 20pF <sup>(1)</sup> | 0        |          |

| EMAC <sub>6</sub>  | Setup for ECRS from ETXCK rising | Load: 20pF <sup>(1)</sup> | 3        |          |

| EMAC <sub>7</sub>  | Hold for ECRS from ETXCK rising  | Load: 20pF <sup>(1)</sup> | 0        |          |

| EMAC <sub>8</sub>  | ETXER toggling from ETXCK rising | Load: 20pF (1)            |          | 15       |

| EMAC <sub>9</sub>  | ETXEN toggling from ETXCK rising | Load: 20pF <sup>(1)</sup> |          | 15       |

| EMAC <sub>10</sub> | ETX toggling from ETXCK rising   | Load: 20pF <sup>(1)</sup> |          | 15       |

| EMAC <sub>11</sub> | Setup for ERX from ERXCK         | Load: 20pF <sup>(1)</sup> | 1        |          |

#### Table 12-32. Ethernet MAC MII Specific Signals

| Symbol             | Parameter                  | Conditions                | Min (ns) | Max (ns) |

|--------------------|----------------------------|---------------------------|----------|----------|

| EMAC <sub>12</sub> | Hold for ERX from ERXCK    | Load: 20pF <sup>(1)</sup> | 1.5      |          |

| EMAC <sub>13</sub> | Setup for ERXER from ERXCK | Load: 20pF <sup>(1)</sup> | 1        |          |

| EMAC <sub>14</sub> | Hold for ERXER from ERXCK  | Load: 20pF <sup>(1)</sup> | 0.5      |          |

| EMAC <sub>15</sub> | Setup for ERXDV from ERXCK | Load: 20pF <sup>(1)</sup> | 1.5      |          |

| EMAC <sub>16</sub> | Hold for ERXDV from ERXCK  | Load: 20pF <sup>(1)</sup> | 1        |          |

Note: 1.  $V_{VDDIO}$  from 3.0V to 3.6V, maximum external capacitor = 20 pF

## Figure 12-10. Ethernet MAC MII Mode

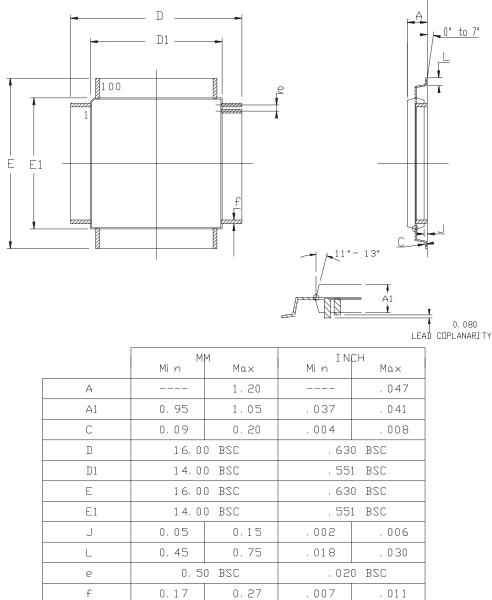

## 13.2 Package Drawings

#### Table 13-2. Device and Package Maximum Weight

| 500 mg |

|--------|

|--------|

#### Table 13-3. Package Characteristics

| Moisture Sensitivity Level | Jdec J-STD0-20D - MSL 3 |

|----------------------------|-------------------------|

|----------------------------|-------------------------|

#### Table 13-4.Package Reference

| JEDEC Drawing Reference | MS-026 |

|-------------------------|--------|

| JESD97 Classification   | E3     |

## AT32UC3A

Figure 13-3. FFBGA-144 package drawing

| Table 13-8. | Device and Package Maximum Weight |

|-------------|-----------------------------------|

|-------------|-----------------------------------|

|   | 1300 | mg |

|---|------|----|

| _ |      |    |

## Table 13-9. Package Characteristics

| Moisture Sensitivity Level MSL3 |

|---------------------------------|

|---------------------------------|

#### Table 13-10. Package Reference

| JEDEC Drawing Reference | MS-026 |

|-------------------------|--------|

| JESD97 Classification   | E3     |

## 13.3 Soldering Profile

Table 13-11 gives the recommended soldering profile from J-STD-20.

| Profile Feature                            | Green Package            |

|--------------------------------------------|--------------------------|

| Average Ramp-up Rate (217°C to Peak)       | 3°C/sec                  |

| Preheat Temperature 175°C ±25°C            | Min. 150 °C, Max. 200 °C |

| Time Maintained Above 217°C                | 60-150 sec               |

| Time within 5.C of Actual Peak Temperature | 30 sec                   |

| Peak Temperature Range                     | 260 °C                   |

| Ramp-down Rate                             | 6 °C/sec                 |

| Time 25 C to Peak Temperature              | Max. 8 minutes           |

Note: It is recommended to apply a soldering temperature higher than 250°C. A maximum of three reflow passes is allowed per component.

3. SPI Bad Serial Clock Generation on 2nd chip\_select when SCBR = 1, CPOL=1 and NCPHA=0

When multiple CS are in use, if one of the baudrate equals to 1 and one of the others doesn't equal to 1, and CPOL=1 and CPHA=0, then an aditional pulse will be generated on SCK. **Fix/workaround**

When multiple CS are in use, if one of the baudrate equals 1, the other must also equal 1 if CPOL=1 and CPHA=0.

4. SPI Glitch on RXREADY flag in slave mode when enabling the SPI or during the first transfer

In slave mode, the SPI can generate a false RXREADY signal during enabling of the SPI or during the first transfer.

#### Fix/Workaround

1. Set slave mode, set required CPOL/CPHA.

- 2. Enable SPI.

- 3. Set the polarity CPOL of the line in the opposite value of the required one.

- 4. Set the polarity CPOL to the required one.

- 5. Read the RXHOLDING register.

Transfers can now befin and RXREADY will now behave as expected.

SPI Disable does not work in Slave mode Fix/workaround Read the last received data then perform a Software reset.

#### 15.1.4 Power Manager

If the BOD level is higher than VDDCORE, the part is constantly under reset

If the BOD level is set to a value higher than VDDCORE and enabled by fuses, the part will

be in constant reset.

#### Fix/Workaround

Apply an external voltage on VDDCORE that is higher than the BOD level and is lower than VDDCORE max and disable the BOD.

- 15.1.5 PDCA

- 1. Wrong PDCA behavior when using two PDCA channels with the same PID. Fix/Workaround

The same PID should not be assigned to more than one channel.

### 15.1.6 TWI

1. The TWI RXRDY flag in SR register is not reset when a software reset is performed. Fix/Workaround

After a Software Reset, the register TWI RHR must be read.

- 15.1.7 USART

- ISO7816 info register US\_NER cannot be read The NER register always returns zero.

Fix/Workaround None

#### 15.1.8 Processor and Architecture

1. LDM instruction with PC in the register list and without ++ increments Rp

#### 15.5.4 USB

#### 1. USB No end of host reset signaled upon disconnection

In host mode, in case of an unexpected device disconnection whereas a usb reset is being sent by the usb controller, the UHCON.RESET bit may not been cleared by the hardware at the end of the reset.

#### **Fix/Workaround**

A software workaround consists in testing (by polling or interrupt) the disconnection (UHINT.DDISCI == 1) while waiting for the end of reset (UHCON.RESET == 0) to avoid being stuck.

#### 2. USBFSM and UHADDR1/2/3 registers are not available.

Do not use USBFSM register.

#### Fix/Workaround

Do not use USBFSM register and use HCON[6:0] field instead for all the pipes.

#### 15.5.5 Processor and Architecture

#### 1. Incorrect Processor ID

The processor ID reads 0x01 and not 0x02 as it should.

#### **Fix/Workaround**

None.

#### 2. Bus error should be masked in Debug mode

If a bus error occurs during debug mode, the processor will not respond to debug commands through the DINST register.

#### Fix/Workaround

A reset of the device will make the CPU respond to debug commands again.

## 3. Read Modify Write (RMW) instructions on data outside the internal RAM does not work.

Read Modify Write (RMW) instructions on data outside the internal RAM does not work.

#### Fix/Workaround

Do not perform RMW instructions on data outside the internal RAM.

## 4. CRC calculation of a locked device will calculate CRC for 512 kB of flash memory, even though the part has less flash. Fix/Workaround

The flash address space is wrapping, so it is possible to use the CRC value by calculating CRC of the flash content concatenated with itself N times. Where N is 512 kB/flash size.

#### 5. Need two NOPs instruction after instructions masking interrupts

The instructions following in the pipeline the instruction masking the interrupt through SR may behave abnormally.

#### **Fix/Workaround**

Place two NOPs instructions after each SSRF or MTSR instruction setting IxM or GM in SR.

#### 2. USART RXBREAK problem when no timeguard

In asynchronous mode the RXBREAK flag is not correctly handled when the timeguard is 0 and the break character is located just after the stop bit.

#### Fix/Workaround

If the NBSTOP is 1, timeguard should be different from 0.

#### 3. USART Handshaking: 2 characters sent / CTS rises when TX

If CTS switches from 0 to 1 during the TX of a character, if the Holding register is not empty, the TXHOLDING is also transmitted.

#### Fix/Workaround

None.

#### 4. USART PDC and TIMEGUARD not supported in MANCHESTER

Manchester encoding/decoding is not working.

#### **Fix/Workaround**

Do not use manchester encoding.

5. USART SPI mode is non functional on this revision. Fix/Workaround

Do not use the USART SPI mode.

#### 6. DCD is active High instead of Low.

In modem mode the DCD signal is assumed to be active high by the USART, butshould have been active low. **Fix/Workaround**

## Add an external inverter to the DCD line.

ISO7816 info register US\_NER cannot be read The NER register always returns zero.

Fix/Workaround None.

#### 15.5.8 Power Manager

1. Voltage regulator input and output is connected to VDDIO and VDDCORE inside the device

The voltage regulator input and output is connected to VDDIO and VDDCORE respectively inside the device.

#### Fix/Workaround

Do not supply VDDCORE externally, as this supply will work in paralell with the regulator.

#### 2. Wrong reset causes when BOD is activated

Setting the BOD enable fuse will cause the Reset Cause Register to list BOD reset as the reset source even though the part was reset by another source.

#### **Fix/Workaround**

Do not set the BOD enable fuse, but activate the BOD as soon as your program starts.

#### 3. PLL0/1 Lock control does not work

Lock Control does not work for PLL0 and PLL1.

AT32UC3A

#### Fix/Workaround

In PLL0/1 Control register, the bit 7 should be set in order to prevent unexpected behaviour.

4. Peripheral Bus A maximum frequency is 33MHz instead of 66MHz. Fix/Workaround

Do not set PBA frequency higher than 33 MHz.

#### 5. PCx pins go low in stop mode

In sleep mode stop all PCx pins will be controlled by GPIO module instead of oscillators. This can cause drive contention on the XINx in worst case.

#### Fix/Workaround

Before entering stop mode set all PCx pins to input and GPIO controlled.

6. On some rare parts, the maximum HSB and CPU speed is 50MHz instead of 66MHz. Fix/Workaround

Do not set the HSB/CPU speed higher than 50MHz when the firmware generate exceptions.

7. If the BOD level is higher than VDDCORE, the part is constantly under reset

If the BOD level is set to a value higher than VDDCORE and enabled by fuses, the part will be in constant reset.

#### Fix/Workaround

Apply an external voltage on VDDCORE that is higher than the BOD level and is lower than VDDCORE max and disable the BOD.

8. System Timer mask (Bit 16) of the PM CPUMASK register is not available. Fix/Workaround

Do not use this bit.

#### 15.5.9 HMatrix

1. HMatrix fixed priority arbitration does not work Fixed priority arbitration does not work.

#### Fix/Workaround

Use Round-Robin arbitration instead.

#### 15.5.10 ADC

1. ADC possible miss on DRDY when disabling a channel The ADC does not work properly when more than one channel is enabled.

#### Fix/Workaround

Do not use the ADC with more than one channel enabled at a time.

2. ADC OVRE flag sometimes not reset on Status Register read The OVRE flag does not clear properly if read simultaneously to an end of conversion.

Fix/Workaround None.

3. Sleep Mode activation needs additional A to D conversion

## **Table of Contents**

| 1  | Description                                       | 3  |

|----|---------------------------------------------------|----|

| 2  | Configuration Summary                             | 4  |

| 3  | Abbreviations                                     |    |

| 4  | Blockdiagram                                      | 5  |

|    | 4.1Processor and architecture                     | 6  |

| 5  | Signals Description                               |    |

| 6  | Package and Pinout                                | 13 |

| 7  | Power Considerations                              | 17 |

|    | 7.1Power Supplies                                 | 17 |

|    | 7.2Voltage Regulator                              | 18 |

|    | 7.3Analog-to-Digital Converter (A.D.C) reference. | 19 |

| 8  | I/O Line Considerations                           | 20 |

|    | 8.1JTAG pins                                      | 20 |

|    | 8.2RESET_N pin                                    | 20 |

|    | 8.3TWI pins                                       | 20 |

|    | 8.4GPIO pins                                      | 20 |

| 9  | Memories                                          | 21 |

|    | 9.1Embedded Memories                              | 21 |

|    | 9.2Physical Memory Map                            | 21 |

|    | 9.3Bus Matrix Connections                         | 22 |

| 10 | Peripherals                                       | 24 |

|    | 10.1Peripheral address map                        | 24 |

|    | 10.2CPU Local Bus Mapping                         | 25 |

|    | 10.3Interrupt Request Signal Map                  | 27 |

|    | 10.4Clock Connections                             | 29 |

|    | 10.5Nexus OCD AUX port connections                | 30 |

|    | 10.6PDC handshake signals                         | 30 |

|    | 10.7Peripheral Multiplexing on I/O lines          | 31 |

|    | 10.8Oscillator Pinout                             | 34 |

|    | 10.9USART Configuration                           | 34 |

|    | 10.10GPIO                                         | 35 |

#### Atmel Corporation

2325 Orchard Parkway San Jose, CA 95131 USA Tel: (+1)(408) 441-0311 Fax: (+1)(408) 487-2600 www.atmel.com

#### Atmel Asia Limited

Unit 1-5 & 16, 19/F BEA Tower, Millennium City 5 418 Kwun Tong Road Kwun Tong, Kowloon HONG KONG Tel: (+852) 2245-6100 Fax: (+852) 2722-1369

#### Atmel Munich GmbH

Business Campus Parkring 4 D-85748 Garching b. Munich GERMANY Tel: (+49) 89-31970-0 Fax: (+49) 89-3194621

#### Atmel Japan

16F, Shin Osaki Kangyo Bldg. 1-6-4 Osaka Shinagawa-ku Tokyo 104-0032 JAPAN Tel: (+81) 3-6417-0300 Fax: (+81) 3-6417-0370

#### © 2012 Atmel Corporation. All rights reserved.

Atmel<sup>®</sup>, Atmel logo and combinations thereof, AVR<sup>®</sup> and others are registered trademarks or trademarks of Atmel Corporation or its subsidiaries. Other terms and product names may be trademarks of others.

Disclaimer: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN THE ATMEL TERMS AND CONDITIONS OF SALES LOCATED ON THE ATMEL WEBSITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDENTAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS AND PROF-ITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and product descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically provided otherwise, Atmel products are not suit-able for, and shall not be used in, automotive applications. Atmel products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life.