Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | AVR                                                                         |

| Core Size                  | 32-Bit Single-Core                                                          |

| Speed                      | 66MHz                                                                       |

| Connectivity               | EBI/EMI, Ethernet, I <sup>2</sup> C, SPI, SSC, UART/USART, USB OTG          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 109                                                                         |

| Program Memory Size        | 256КВ (256К х 8)                                                            |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 64K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 3.6V                                                                |

| Data Converters            | A/D 8x10b                                                                   |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 144-LQFP                                                                    |

| Supplier Device Package    | 144-LQFP (20x20)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at32uc3a0256-alur |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2. Configuration Summary

| Device       | Flash      | SRAM      | Ext. Bus Interface | Ethernet<br>MAC | Package                     |

|--------------|------------|-----------|--------------------|-----------------|-----------------------------|

| AT32UC3A0512 | 512 Kbytes | 64 Kbytes | yes                | yes             | 144 pin LQFP<br>144 pin BGA |

| AT32UC3A0256 | 256 Kbytes | 64 Kbytes | yes                | yes             | 144 pin LQFP<br>144 pin BGA |

| AT32UC3A0128 | 128 Kbytes | 32 Kbytes | yes                | yes             | 144 pin LQFP<br>144 pin BGA |

| AT32UC3A1512 | 512 Kbytes | 64 Kbytes | no                 | yes             | 100 pin TQFP                |

| AT32UC3A1256 | 256 Kbytes | 64 Kbytes | no                 | yes             | 100 pin TQFP                |

| AT32UC3A1128 | 128 Kbytes | 32 Kbytes | no                 | yes             | 100 pin TQFP                |

The table below lists all AT32UC3A memory and package configurations:

# 3. Abbreviations

- GCLK: Power Manager Generic Clock

- GPIO: General Purpose Input/Output

- HSB: High Speed Bus

- MPU: Memory Protection Unit

- OCD: On Chip Debug

- PB: Peripheral Bus

- PDCA: Peripheral Direct Memory Access Controller (PDC) version A

- USBB: USB On-The-GO Controller version B

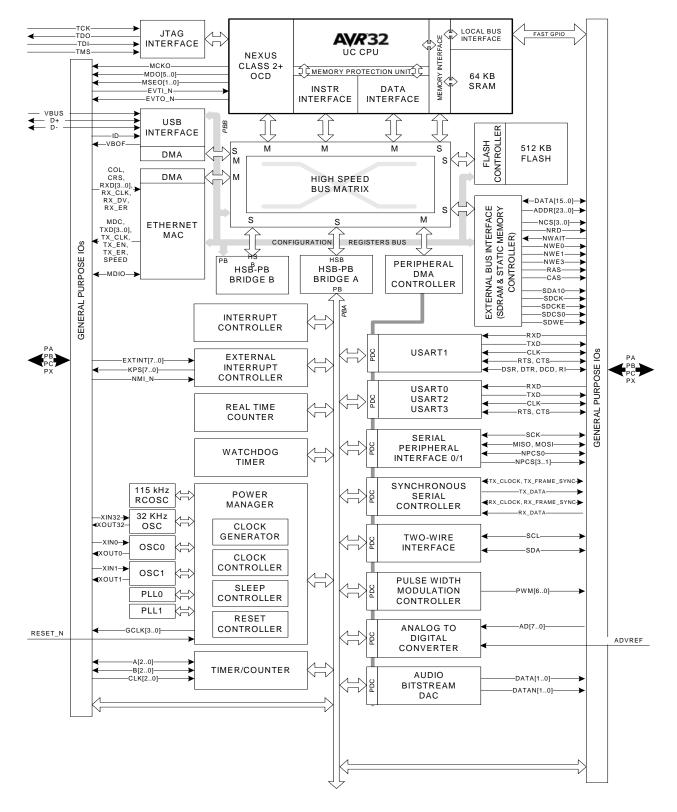

# 4. Blockdiagram

## Figure 4-1. Blockdiagram

Peripheral Bus A able to run on at divided bus speeds compared to the High Speed Bus

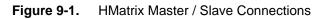

Figure 4-1 gives an overview of the bus system. All modules connected to the same bus use the same clock, but the clock to each module can be individually shut off by the Power Manager. The figure identifies the number of master and slave interfaces of each module connected to the High Speed Bus, and which DMA controller is connected to which peripheral.

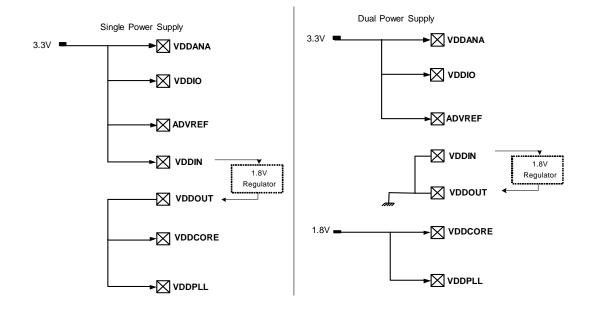

# 7. Power Considerations

## 7.1 Power Supplies

The AT32UC3A has several types of power supply pins:

- VDDIO: Powers I/O lines. Voltage is 3.3V nominal.

- VDDANA: Powers the ADC Voltage is 3.3V nominal.

- VDDIN: Input voltage for the voltage regulator. Voltage is 3.3V nominal.

- VDDCORE: Powers the core, memories, and peripherals. Voltage is 1.8V nominal.

- VDDPLL: Powers the PLL. Voltage is 1.8V nominal.

The ground pins GND are common to VDDCORE, VDDIO, VDDPLL. The ground pin for VDDANA is GNDANA.

Refer to "Power Consumption" on page 44 for power consumption on the various supply pins.

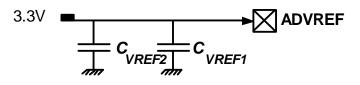

## 7.3 Analog-to-Digital Converter (A.D.C) reference.

The ADC reference (ADVREF) must be provided from an external source. Two decoupling capacitors must be used to insure proper decoupling.

Refer to Section 12.4 on page 42 for decoupling capacitors values and electrical characteristics. In case ADC is not used, the ADVREF pin should be connected to GND to avoid extra consumption.

AT32UC3A

## Table 10-1. Peripheral Address Mapping (Continued)

| Address    |        | Peripheral Name                                                     | Bus |

|------------|--------|---------------------------------------------------------------------|-----|

| 0xFFFF1C00 | USART2 | Universal Synchronous Asynchronous Receiver<br>Transmitter - USART2 | PBA |

| 0xFFFF2000 | USART3 | Universal Synchronous Asynchronous Receiver<br>Transmitter - USART3 | PBA |

| 0xFFFF2400 | SPI0   | Serial Peripheral Interface - SPI0                                  | PBA |

| 0xFFFF2800 | SPI1   | Serial Peripheral Interface - SPI1                                  | PBA |

| 0xFFFF2C00 | TWI    | Two Wire Interface - TWI                                            | PBA |

| 0xFFFF3000 | PWM    | Pulse Width Modulation Controller - PWM                             | PBA |

| 0xFFFF3400 | SSC    | Synchronous Serial Controller - SSC                                 | PBA |

| 0xFFFF3800 | тс     | Timer/Counter - TC                                                  | PBA |

| 0xFFFF3C00 | ADC    | Analog To Digital Converter - ADC                                   | PBA |

## 10.2 CPU Local Bus Mapping

Some of the registers in the GPIO module are mapped onto the CPU local bus, in addition to being mapped on the Peripheral Bus. These registers can therefore be reached both by accesses on the Peripheral Bus, and by accesses on the local bus.

Mapping these registers on the local bus allows cycle-deterministic toggling of GPIO pins since the CPU and GPIO are the only modules connected to this bus. Also, since the local bus runs at CPU speed, one write or read operation can be performed per clock cycle to the local busmapped GPIO registers.

Table 10-9.

GPIO Controller Function Multiplexing

| Table 10-9. |     | roller Functio |          | 1              |               |              |

|-------------|-----|----------------|----------|----------------|---------------|--------------|

| 7           | 11  | PB24           | GPIO 56  | TC - B0        | USART1 - DSR  |              |

| 8           | 13  | PB25           | GPIO 57  | TC - A1        | USART1 - DTR  |              |

| 9           | 14  | PB26           | GPIO 58  | TC - B1        | USART1 - RI   |              |

| 10          | 15  | PB27           | GPIO 59  | TC - A2        | PWM - PWM[4]  |              |

| 14          | 19  | PB28           | GPIO 60  | TC - B2        | PWM - PWM[5]  |              |

| 15          | 20  | PB29           | GPIO 61  | USART2 - RXD   | PM - GCLK[1]  | EBI - NCS[2] |

| 16          | 21  | PB30           | GPIO 62  | USART2 - TXD   | PM - GCLK[2]  | EBI - SDCS   |

| 17          | 22  | PB31           | GPIO 63  | USART2 - CLK   | PM - GCLK[3]  | EBI - NWAIT  |

| 63          | 85  | PC00           | GPIO 64  |                |               |              |

| 64          | 86  | PC01           | GPIO 65  |                |               |              |

| 85          | 124 | PC02           | GPIO 66  |                |               |              |

| 86          | 125 | PC03           | GPIO 67  |                |               |              |

| 93          | 132 | PC04           | GPIO 68  |                |               |              |

| 94          | 133 | PC05           | GPIO 69  |                |               |              |

|             | 1   | PX00           | GPIO 100 | EBI - DATA[10] | USART0 - RXD  |              |

|             | 2   | PX01           | GPIO 99  | EBI - DATA[9]  | USART0 - TXD  |              |

|             | 4   | PX02           | GPIO 98  | EBI - DATA[8]  | USART0 - CTS  |              |

|             | 10  | PX03           | GPIO 97  | EBI - DATA[7]  | USART0 - RTS  |              |

|             | 12  | PX04           | GPIO 96  | EBI - DATA[6]  | USART1 - RXD  |              |

|             | 24  | PX05           | GPIO 95  | EBI - DATA[5]  | USART1 - TXD  |              |

|             | 26  | PX06           | GPIO 94  | EBI - DATA[4]  | USART1 - CTS  |              |

|             | 31  | PX07           | GPIO 93  | EBI - DATA[3]  | USART1 - RTS  |              |

|             | 33  | PX08           | GPIO 92  | EBI - DATA[2]  | USART3 - RXD  |              |

|             | 35  | PX09           | GPIO 91  | EBI - DATA[1]  | USART3 - TXD  |              |

|             | 38  | PX10           | GPIO 90  | EBI - DATA[0]  | USART2 - RXD  |              |

|             | 40  | PX11           | GPIO 109 | EBI - NWE1     | USART2 - TXD  |              |

|             | 42  | PX12           | GPIO 108 | EBI - NWE0     | USART2 - CTS  |              |

|             | 44  | PX13           | GPIO 107 | EBI - NRD      | USART2 - RTS  |              |

|             | 46  | PX14           | GPIO 106 | EBI - NCS[1]   |               | TC - A0      |

|             | 59  | PX15           | GPIO 89  | EBI - ADDR[19] | USART3 - RTS  | TC - B0      |

|             | 61  | PX16           | GPIO 88  | EBI - ADDR[18] | USART3 - CTS  | TC - A1      |

|             | 63  | PX17           | GPIO 87  | EBI - ADDR[17] |               | TC - B1      |

|             | 65  | PX18           | GPIO 86  | EBI - ADDR[16] |               | TC - A2      |

|             | 67  | PX19           | GPIO 85  | EBI - ADDR[15] | EIM - SCAN[0] | TC - B2      |

|             | 87  | PX20           | GPIO 84  | EBI - ADDR[14] | EIM - SCAN[1] | TC - CLK0    |

|             | 89  | PX21           | GPIO 83  | EBI - ADDR[13] | EIM - SCAN[2] | TC - CLK1    |

|             | 91  | PX22           | GPIO 82  | EBI - ADDR[12] | EIM - SCAN[3] | TC - CLK2    |

|             | 95  | PX23           | GPIO 81  | EBI - ADDR[11] | EIM - SCAN[4] |              |

|             | 97  | PX24           | GPIO 80  | EBI - ADDR[10] | EIM - SCAN[5] |              |

|             |     |                |          | L - 1          | L-1           |              |

- Optional Manchester Encoding

- RS485 with driver control signal

- ISO7816, T = 0 or T = 1 Protocols for interfacing with smart cards

- NACK handling, error counter with repetition and iteration limit

- IrDA modulation and demodulation

- Communication at up to 115.2 Kbps

- Test Modes

- Remote Loopback, Local Loopback, Automatic Echo

- SPI Mode

- Master or Slave

- Serial Clock Programmable Phase and Polarity

- SPI Serial Clock (SCK) Frequency up to Internal Clock Frequency PBA/4

- Supports Connection of Two Peripheral DMA Controller Channels (PDC)

- Offers Buffer Transfer without Processor Intervention

#### 10.11.8 Serial Synchronous Controller

- Provides serial synchronous communication links used in audio and telecom applications (with CODECs in Master or Slave Modes, I2S, TDM Buses, Magnetic Card Reader, etc.)

- · Contains an independent receiver and transmitter and a common clock divider

- Offers a configurable frame sync and data length

- Receiver and transmitter can be programmed to start automatically or on detection of different event on the frame sync signal

- Receiver and transmitter include a data signal, a clock signal and a frame synchronization signal

- 10.11.9 Timer Counter

- Three 16-bit Timer Counter Channels

- Wide range of functions including:

- Frequency Measurement

- Event Counting

- Interval Measurement

- Pulse Generation

- Delay Timing

- Pulse Width Modulation

- Up/down Capabilities

- Each channel is user-configurable and contains:

- Three external clock inputs

- Five internal clock inputs

- Two multi-purpose input/output signals

- Two global registers that act on all three TC Channels

#### 10.11.10 Pulse Width Modulation Controller

- 7 channels, one 20-bit counter per channel

- Common clock generator, providing Thirteen Different Clocks

- A Modulo n counter providing eleven clocks

- Two independent Linear Dividers working on modulo n counter outputs

- Independent channel programming

- Independent Enable Disable Commands

- Independent Clock

- Independent Period and Duty Cycle, with Double Bufferization

- Programmable selection of the output waveform polarity

- Programmable center or left aligned output waveform

## 12.3 Regulator characteristics

Table 12-2.

Electrical characteristics

| Symbol              | Parameter                                         | Condition                                                         | Min. | Тур. | Max. | Units |

|---------------------|---------------------------------------------------|-------------------------------------------------------------------|------|------|------|-------|

| $V_{\text{VDDIN}}$  | Supply voltage (input)                            |                                                                   | 3    | 3.3  | 3.6  | V     |

| V <sub>VDDOUT</sub> | Supply voltage (output)                           |                                                                   | 1.81 | 1.85 | 1.89 | V     |

|                     | Maximum DC output current with $V_{VDDIN = 3.3V}$ |                                                                   |      |      | 100  | mA    |

| OUT                 | Maximum DC output current with $V_{VDDIN = 2.7V}$ |                                                                   |      |      | 90   | mA    |

| I <sub>SCR</sub>    | Static Current of internal regulator              | Low Power mode (stop, deep stop or static) at $T_A = 25^{\circ}C$ |      | 10   |      | μA    |

## Table 12-3.Decoupling requirements

| Symbol            | Parameter                    | Condition | Тур. | Techno. | Units |

|-------------------|------------------------------|-----------|------|---------|-------|

| C <sub>IN1</sub>  | Input Regulator Capacitor 1  |           | 1    | NPO     | nF    |

| C <sub>IN2</sub>  | Input Regulator Capacitor 2  |           | 4.7  | X7R     | uF    |

| C <sub>OUT1</sub> | Output Regulator Capacitor 1 |           | 470  | NPO     | pF    |

| C <sub>OUT2</sub> | Output Regulator Capacitor 2 |           | 2.2  | X7R     | uF    |

# 12.4 Analog characteristics

Table 12-4. Electrical characteristics

| Symbol  | Parameter                        | Condition | Min. | Тур. | Max. | Units |

|---------|----------------------------------|-----------|------|------|------|-------|

| VADVREF | Analog voltage reference (input) |           | 2.6  |      | 3.6  | V     |

## **Table 12-5.**Decoupling requirements

| Symbol             | Parameter                     | Condition | Тур. | Techno | Units |

|--------------------|-------------------------------|-----------|------|--------|-------|

| C <sub>VREF1</sub> | Voltage reference Capacitor 1 |           | 10   | -      | nF    |

| C <sub>VREF2</sub> | Voltage reference Capacitor 2 |           | 1    | -      | uF    |

12.4.1 BOD

Table 12-6.BODLEVEL Values

| BODLEVEL Value | Тур. | Тур. | Тур. | Units. |

|----------------|------|------|------|--------|

| 00 0000b       | 1.40 | 1.47 | 1.55 | V      |

| 01 0111b       | 1.45 | 1.52 | 1.6  | V      |

| 01 1111b       | 1.55 | 1.6  | 1.65 | V      |

| 10 0111b       | 1.65 | 1.69 | 1.75 | V      |

The values in Table 12-6 describes the values of the BODLEVEL in the flash FGPFR register.

## Table 12-9. Power Consumption for Different Modes

| Mode                                                                                                                                 | Conditions                                                                                                                                 |         | Тур. | Unit |

|--------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|---------|------|------|

|                                                                                                                                      | Typ : Ta = 25 °C.<br>CPU is in stop mode                                                                                                   | on Amp0 | 47   | uA   |

| Stop                                                                                                                                 | GPIOs on internal pull-up.<br>All peripheral clocks de-activated.<br>DM and DP pins connected to ground.<br>XIN0,Xin1 and XIN2 are stopped | on Amp1 | 40   | uA   |

|                                                                                                                                      | Typ : Ta = 25 °C.CPU is in deepstop mode                                                                                                   | on Amp0 | 36   | uA   |

| GPIOs on internal pull-up.DeepstopAll peripheral clocks de-activated.DM and DP pins connected to grounXIN0,Xin1 and XIN2 are stopped | All peripheral clocks de-activated.<br>DM and DP pins connected to ground.                                                                 | on Amp1 | 28   | uA   |

|                                                                                                                                      | Typ : Ta = 25 °C. CPU is in static mode                                                                                                    | on Amp0 | 25   | uA   |

| Static                                                                                                                               | GPIOs on internal pull-up.<br>All peripheral clocks de-activated.<br>DM and DP pins connected to ground.<br>XIN0,Xin1 and XIN2 are stopped | on Amp1 | 14   | uA   |

1. Core frequency is generated from XIN0 using the PLL so that 140 MHz < fpll0 < 160 MHz and 10 MHz < fxin0 < 12MHz

| Peripheral | Тур. | Unit   |

|------------|------|--------|

| GPIO       | 37   |        |

| SMC        | 10   |        |

| SDRAMC     | 4    |        |

| ADC        | 18   |        |

| EBI        | 31   |        |

| INTC       | 25   |        |

| TWI        | 14   |        |

| MACB       | 45   |        |

| PDCA       | 30   | μA/MHz |

| PWM        | 36   |        |

| RTC        | 7    |        |

| SPI        | 13   |        |

| SSC        | 13   |        |

| TC         | 10   |        |

| USART      | 35   |        |

| USB        | 45   |        |

## Table 12-10. Power Consumption by Peripheral in Active Mode

## 12.6 Clock Characteristics

These parameters are given in the following conditions:

# 12.8 ADC Characteristics

| Table 12-17. | Channel Conversion Time and ADC Clock |

|--------------|---------------------------------------|

|              |                                       |

| Parameter                       | Conditions             | Min | Тур | Max                | Units |

|---------------------------------|------------------------|-----|-----|--------------------|-------|

| ADC Clock Frequency             | 10-bit resolution mode |     |     | 5                  | MHz   |

| ADC Clock Frequency             | 8-bit resolution mode  |     |     | 8                  | MHz   |

| Startup Time                    | Return from Idle Mode  |     |     | 20                 | μs    |

| Track and Hold Acquisition Time |                        | 600 |     |                    | ns    |

| Conversion Time                 | ADC Clock = 5 MHz      |     |     | 2                  | μs    |

| Conversion Time                 | ADC Clock = 8 MHz      |     |     | 1.25               | μs    |

| Throughput Rate                 | ADC Clock = 5 MHz      |     |     | 384 <sup>(1)</sup> | kSPS  |

| Throughput Rate                 | ADC Clock = 8 MHz      |     |     | 533 <sup>(2)</sup> | kSPS  |

Notes: 1. Corresponds to 13 clock cycles at 5 MHz: 3 clock cycles for track and hold acquisition time and 10 clock cycles for conversion.

2. Corresponds to 15 clock cycles at 8 MHz: 5 clock cycles for track and hold acquisition time and 10 clock cycles for conversion.

## Table 12-18. External Voltage Reference Input

| Parameter                     | Conditions                           | Min | Тур | Max    | Units |

|-------------------------------|--------------------------------------|-----|-----|--------|-------|

| ADVREF Input Voltage Range    |                                      | 2.6 |     | VDDANA | V     |

| ADVREF Average Current        | On 13 samples with ADC Clock = 5 MHz |     | 200 | 250    | μA    |

| Current Consumption on VDDANA |                                      |     |     | 1.25   | mA    |

Note: ADVREF should be connected to GND to avoid extra consumption in case ADC is not used.

## Table 12-19. Analog Inputs

| Parameter             | Min | Тур | Max     | Units |

|-----------------------|-----|-----|---------|-------|

| Input Voltage Range   | 0   |     | VADVREF |       |

| Input Leakage Current |     |     | 1       | μA    |

| Input Capacitance     |     | 17  |         | pF    |

## Table 12-20. Transfer Characteristics in 8-bit mode

| Parameter                  | Conditions | Min  | Тур  | Max | Units |

|----------------------------|------------|------|------|-----|-------|

| Resolution                 |            |      | 8    |     | Bit   |

|                            | f=5MHz     |      |      | 0.8 | LSB   |

| Absolute Accuracy          | f=8MHz     |      |      | 1.5 | LSB   |

| Integral Non-linearity     | f=5MHz     |      | 0.35 | 0.5 | LSB   |

|                            | f=8MHz     |      | 0.5  | 1.0 | LSB   |

| Differential Non-linearity | f=5MHz     |      | 0.3  | 0.5 | LSB   |

|                            | f=8MHz     |      | 0.5  | 1.0 | LSB   |

| Offset Error               | f=5MHz     | -0.5 |      | 0.5 | LSB   |

| Gain Error                 | f=5MHz     | -0.5 |      | 0.5 | LSB   |

## 12.9 EBI Timings

These timings are given for worst case process, T = 85·C, VDDCORE = 1.65V, VDDIO = 3V and 40 pF load capacitance.

| Symbol                  | Parameter                      | Max <sup>(1)</sup>      | Units |

|-------------------------|--------------------------------|-------------------------|-------|

| 1/(t <sub>CPSMC</sub> ) | SMC Controller Clock Frequency | 1/(t <sub>cpcpu</sub> ) | MHz   |

Note: 1. The maximum frequency of the SMC interface is the same as the max frequency for the HSB.

## Table 12-23. SMC Read Signals with Hold Settings

| Symbol            | Parameter                                  | Min                                                               | Units |  |  |  |

|-------------------|--------------------------------------------|-------------------------------------------------------------------|-------|--|--|--|

|                   | NRD Controlled (READ_MODE = 1)             |                                                                   |       |  |  |  |

| SMC <sub>1</sub>  | Data Setup before NRD High                 | 12                                                                |       |  |  |  |

| SMC <sub>2</sub>  | Data Hold after NRD High                   | 0                                                                 |       |  |  |  |

| SMC <sub>3</sub>  | NRD High to NBS0/A0 Change <sup>(1)</sup>  | nrd hold length * t <sub>CPSMC</sub> - 1.3                        |       |  |  |  |

| SMC <sub>4</sub>  | NRD High to NBS1 Change <sup>(1)</sup>     | nrd hold length * t <sub>CPSMC</sub> - 1.3                        |       |  |  |  |

| SMC <sub>5</sub>  | NRD High to NBS2/A1 Change <sup>(1)</sup>  | nrd hold length * t <sub>CPSMC</sub> - 1.3                        | ns    |  |  |  |

| SMC <sub>6</sub>  | NRD High to NBS3 Change <sup>(1)</sup>     | nrd hold length * t <sub>CPSMC</sub> - 1.3                        |       |  |  |  |

| SMC <sub>7</sub>  | NRD High to A2 - A25 Change <sup>(1)</sup> | nrd hold length * t <sub>CPSMC</sub> - 1.3                        |       |  |  |  |

| SMC <sub>8</sub>  | NRD High to NCS Inactive <sup>(1)</sup>    | (nrd hold length - ncs rd hold length) * t <sub>CPSMC</sub> - 2.3 |       |  |  |  |

| SMC <sub>9</sub>  | NRD Pulse Width                            | nrd pulse length * t <sub>CPSMC</sub> - 1.4                       |       |  |  |  |

|                   | NRD C                                      | controlled (READ_MODE = 0)                                        | U     |  |  |  |

| SMC <sub>10</sub> | Data Setup before NCS High                 | 11.5                                                              |       |  |  |  |

| SMC <sub>11</sub> | Data Hold after NCS High                   | 0                                                                 |       |  |  |  |

| SMC <sub>12</sub> | NCS High to NBS0/A0 Change <sup>(1)</sup>  | ncs rd hold length * t <sub>CPSMC</sub> - 2.3                     |       |  |  |  |

| SMC <sub>13</sub> | NCS High to NBS0/A0 Change <sup>(1)</sup>  | ncs rd hold length * t <sub>CPSMC</sub> - 2.3                     |       |  |  |  |

| SMC <sub>14</sub> | NCS High to NBS2/A1 Change <sup>(1)</sup>  | ncs rd hold length * t <sub>CPSMC</sub> - 2.3                     | ns    |  |  |  |

| SMC <sub>15</sub> | NCS High to NBS3 Change <sup>(1)</sup>     | ncs rd hold length * t <sub>CPSMC</sub> - 2.3                     |       |  |  |  |

| SMC <sub>16</sub> | NCS High to A2 - A25 Change <sup>(1)</sup> | ncs rd hold length * t <sub>CPSMC</sub> - 4                       |       |  |  |  |

| SMC <sub>17</sub> | NCS High to NRD Inactive <sup>(1)</sup>    | ncs rd hold length - nrd hold length)* t <sub>CPSMC</sub> - 1.3   |       |  |  |  |

| SMC <sub>18</sub> | NCS Pulse Width                            | ncs rd pulse length * t <sub>CPSMC</sub> - 3.6                    |       |  |  |  |

Note: 1. hold length = total cycle duration - setup duration - pulse duration. "hold length" is for "ncs rd hold length" or "nrd hold length".

# 12.10 JTAG Timings

## 12.10.1 JTAG Interface Signals

## Table 12-29. JTAG Interface Timing specification

| Symbol             | Parameter                      | Conditions | Min | Max | Units |

|--------------------|--------------------------------|------------|-----|-----|-------|

| JTAG <sub>0</sub>  | TCK Low Half-period            | (1)        | 6   |     | ns    |

| JTAG <sub>1</sub>  | TCK High Half-period           | (1)        | 3   |     | ns    |

| JTAG <sub>2</sub>  | TCK Period                     | (1)        | 9   |     | ns    |

| JTAG <sub>3</sub>  | TDI, TMS Setup before TCK High | (1)        | 1   |     | ns    |

| JTAG <sub>4</sub>  | TDI, TMS Hold after TCK High   | (1)        | 0   |     | ns    |

| JTAG <sub>5</sub>  | TDO Hold Time                  | (1)        | 4   |     | ns    |

| JTAG <sub>6</sub>  | TCK Low to TDO Valid           | (1)        |     | 6   | ns    |

| JTAG <sub>7</sub>  | Device Inputs Setup Time       | (1)        |     |     | ns    |

| JTAG <sub>8</sub>  | Device Inputs Hold Time        | (1)        |     |     | ns    |

| JTAG <sub>9</sub>  | Device Outputs Hold Time       | (1)        |     |     | ns    |

| JTAG <sub>10</sub> | TCK to Device Outputs Valid    | (1)        |     |     | ns    |

Note: 1.  $V_{VDDIO}$  from 3.0V to 3.6V, maximum external capacitor = 40pF

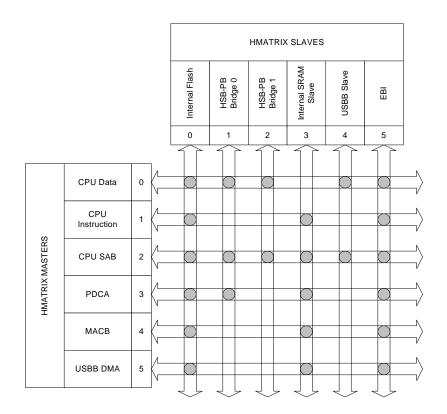

## 13.2 Package Drawings

## Table 13-2. Device and Package Maximum Weight

| 500 mg |

|--------|

|--------|

## Table 13-3. Package Characteristics

| Moisture Sensitivity Level | Jdec J-STD0-20D - MSL 3 |

|----------------------------|-------------------------|

|----------------------------|-------------------------|

## Table 13-4.Package Reference

| JEDEC Drawing Reference | MS-026 |

|-------------------------|--------|

| JESD97 Classification   | E3     |

## 13.3 Soldering Profile

Table 13-11 gives the recommended soldering profile from J-STD-20.

| Profile Feature                                          | Green Package  |  |

|----------------------------------------------------------|----------------|--|

| Average Ramp-up Rate (217°C to Peak)                     | 3°C/sec        |  |

| Preheat Temperature 175°C ±25°C Min. 150 °C, Max. 200 °C |                |  |

| Time Maintained Above 217°C                              | 60-150 sec     |  |

| Time within 5.C of Actual Peak Temperature               | 30 sec         |  |

| Peak Temperature Range                                   | 260 °C         |  |

| Ramp-down Rate                                           | 6 °C/sec       |  |

| Time 25 C to Peak Temperature                            | Max. 8 minutes |  |

Note: It is recommended to apply a soldering temperature higher than 250°C. A maximum of three reflow passes is allowed per component.

| 15.3.7  | GPIO                          | <b>Workaround/fix</b><br>The same PID should not be assigned to more than one channel.                                                                                                                                                                                                                                                                                                                              |

|---------|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         |                               | <ol> <li>Some GPIO VIH (input high voltage) are 3.6V max instead of 5V tolerant<br/>Only 11 GPIOs remain 5V tolerant (VIHmax=5V):PB01, PB02, PB03, PB10, PB19, PB20,<br/>PB21, PB22, PB23, PB27, PB28.<br/>Workaround/fix<br/>None.</li> </ol>                                                                                                                                                                      |

| 15.3.8  | USART                         |                                                                                                                                                                                                                                                                                                                                                                                                                     |

|         |                               | <ol> <li>ISO7816 info register US_NER cannot be read<br/>The NER register always returns zero.</li> <li>Fix/Workaround<br/>None.</li> </ol>                                                                                                                                                                                                                                                                         |

| 15.3.9  | тwi                           |                                                                                                                                                                                                                                                                                                                                                                                                                     |

|         |                               | <ol> <li>The TWI RXRDY flag in SR register is not reset when a software reset is performed.<br/>Fix/Workaround<br/>After a Software Reset, the register TWI RHR must be read.</li> </ol>                                                                                                                                                                                                                            |

| 15.3.10 | SDRAMC                        | Aller a Soliwale Resel, the register T WI KITK must be read.                                                                                                                                                                                                                                                                                                                                                        |

|         |                               | 1. Code execution from external SDRAM does not work<br>Code execution from SDRAM does not work.                                                                                                                                                                                                                                                                                                                     |

| 15.3.11 | Brocossor an                  | Fix/Workaround<br>Do not run code from SDRAM.                                                                                                                                                                                                                                                                                                                                                                       |

| 15.5.11 | 11 Processor and Architecture |                                                                                                                                                                                                                                                                                                                                                                                                                     |

|         |                               | <ol> <li>LDM instruction with PC in the register list and without ++ increments Rp<br/>For LDM with PC in the register list: the instruction behaves as if the ++ field is always set, ie<br/>the pointer is always updated. This happens even if the ++ field is cleared. Specifically, the<br/>increment of the pointer is done in parallel with the testing of R12.</li> <li>Fix/Workaround<br/>None.</li> </ol> |

|         |                               | <ol> <li>RETE instruction does not clear SREG[L] from interrupts.<br/>The RETE instruction clears SREG[L] as expected from exceptions.<br/>Fix/Workaround</li> </ol>                                                                                                                                                                                                                                                |

|         |                               | When using the STCOND instruction, clear SREG[L] in the stacked value of SR before returning from interrupts with RETE.                                                                                                                                                                                                                                                                                             |

|         |                               | <ol> <li>Exceptions when system stack is protected by MPU<br/>RETS behaves incorrectly when MPU is enabled and MPU is configured so that</li> </ol>                                                                                                                                                                                                                                                                 |

|         |                               | system stack is not readable in unprivileged mode.<br><b>Fix/Woraround</b><br>Warkeround 1: Make system stack readable in unprivileged mode                                                                                                                                                                                                                                                                         |

|         |                               | Workaround 1: Make system stack readable in unprivileged mode,<br>or                                                                                                                                                                                                                                                                                                                                                |

|         |                               | Workaround 2: Return from supervisor mode using rete instead of rets. This<br>requires :                                                                                                                                                                                                                                                                                                                            |

|         |                               | 1. Changing the mode bits from 001b to 110b before issuing the instruction.<br>Updating the mode bits to the desired value must be done using a single mtsr                                                                                                                                                                                                                                                         |

Updating the mode bits to the desired value must be done using a single m instruction so it is done atomically. Even if this step is described in general as not safe in the UC technical reference guide, it is safe in this very

## 15.5.4 USB

## 1. USB No end of host reset signaled upon disconnection

In host mode, in case of an unexpected device disconnection whereas a usb reset is being sent by the usb controller, the UHCON.RESET bit may not been cleared by the hardware at the end of the reset.

#### **Fix/Workaround**

A software workaround consists in testing (by polling or interrupt) the disconnection (UHINT.DDISCI == 1) while waiting for the end of reset (UHCON.RESET == 0) to avoid being stuck.

## 2. USBFSM and UHADDR1/2/3 registers are not available.

Do not use USBFSM register.

#### Fix/Workaround

Do not use USBFSM register and use HCON[6:0] field instead for all the pipes.

#### 15.5.5 Processor and Architecture

#### 1. Incorrect Processor ID

The processor ID reads 0x01 and not 0x02 as it should.

## **Fix/Workaround**

None.

#### 2. Bus error should be masked in Debug mode

If a bus error occurs during debug mode, the processor will not respond to debug commands through the DINST register.

#### Fix/Workaround

A reset of the device will make the CPU respond to debug commands again.

# 3. Read Modify Write (RMW) instructions on data outside the internal RAM does not work.

Read Modify Write (RMW) instructions on data outside the internal RAM does not work.

## Fix/Workaround

Do not perform RMW instructions on data outside the internal RAM.

# 4. CRC calculation of a locked device will calculate CRC for 512 kB of flash memory, even though the part has less flash. Fix/Workaround

The flash address space is wrapping, so it is possible to use the CRC value by calculating CRC of the flash content concatenated with itself N times. Where N is 512 kB/flash size.

#### 5. Need two NOPs instruction after instructions masking interrupts

The instructions following in the pipeline the instruction masking the interrupt through SR may behave abnormally.

#### **Fix/Workaround**

Place two NOPs instructions after each SSRF or MTSR instruction setting IxM or GM in SR.

AT32UC3A

## Fix/Workaround

In PLL0/1 Control register, the bit 7 should be set in order to prevent unexpected behaviour.

4. Peripheral Bus A maximum frequency is 33MHz instead of 66MHz. Fix/Workaround

Do not set PBA frequency higher than 33 MHz.

## 5. PCx pins go low in stop mode

In sleep mode stop all PCx pins will be controlled by GPIO module instead of oscillators. This can cause drive contention on the XINx in worst case.

#### Fix/Workaround

Before entering stop mode set all PCx pins to input and GPIO controlled.

6. On some rare parts, the maximum HSB and CPU speed is 50MHz instead of 66MHz. Fix/Workaround

Do not set the HSB/CPU speed higher than 50MHz when the firmware generate exceptions.

7. If the BOD level is higher than VDDCORE, the part is constantly under reset

If the BOD level is set to a value higher than VDDCORE and enabled by fuses, the part will be in constant reset.

## Fix/Workaround

Apply an external voltage on VDDCORE that is higher than the BOD level and is lower than VDDCORE max and disable the BOD.

8. System Timer mask (Bit 16) of the PM CPUMASK register is not available. Fix/Workaround

Do not use this bit.

#### 15.5.9 HMatrix

1. HMatrix fixed priority arbitration does not work Fixed priority arbitration does not work.

#### Fix/Workaround

Use Round-Robin arbitration instead.

## 15.5.10 ADC

1. ADC possible miss on DRDY when disabling a channel The ADC does not work properly when more than one channel is enabled.

#### Fix/Workaround

Do not use the ADC with more than one channel enabled at a time.

2. ADC OVRE flag sometimes not reset on Status Register read The OVRE flag does not clear properly if read simultaneously to an end of conversion.

Fix/Workaround None.

3. Sleep Mode activation needs additional A to D conversion

# 16. Datasheet Revision History

Please note that the referring page numbers in this section are referred to this document. The referring revision in this section are referring to the document revision.

## 16.1 Rev. K - 01/12

- 1. Update "Errata" on page 70.

- 2. Update eletrical characteristic in "DC Characteristics" on page 41.

- 3. Remove Preliminary from first page.

## 16.2 Rev. G - 01/09

- 1. Update "Errata" on page 70.

- 2. Update GPIO eletrical characteristic in "DC Characteristics" on page 41.

## 16.3 Rev. F - 08/08

- 1. Add revision J to "Errata" on page 70.

- 2. Update DMIPS number in "Features" on page 1.

- 16.4 Rev. E 04/08

- 1. Open Drain Mode removed from "General-Purpose Input/Output Controller (GPIO)" on page 151.

## 16.5 Rev. D - 04/08

- 1. Updated "Signal Description List" on page 8. Removed RXDN and TXDN from USART section.

- 2. Updated "Errata" on page 70. Rev G replaced by rev H.