#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Obsolete                                                                    |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | AVR                                                                         |

| Core Size                  | 32-Bit Single-Core                                                          |

| Speed                      | 66MHz                                                                       |

| Connectivity               | EBI/EMI, Ethernet, I <sup>2</sup> C, SPI, SSC, UART/USART, USB OTG          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 109                                                                         |

| Program Memory Size        | 512KB (512K x 8)                                                            |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 64K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 3.6V                                                                |

| Data Converters            | A/D 8x10b                                                                   |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 144-LQFP                                                                    |

| Supplier Device Package    | 144-LQFP (20x20)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at32uc3a0512-altt |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Table 5-1.Signal Description List

| Signal Name    | Function                      | Туре                  | Active<br>Level | Comments |

|----------------|-------------------------------|-----------------------|-----------------|----------|

|                | External Bus                  | s Interface - HEBI    | 1               | 1        |

| ADDR0 - ADDR23 | Address Bus                   | Output                |                 |          |

| CAS            | Column Signal                 | Output                | Low             |          |

| DATA0 - DATA15 | Data Bus                      | I/O                   |                 |          |

| NCS0 - NCS3    | Chip Select                   | Output                | Low             |          |

| NRD            | Read Signal                   | Output                | Low             |          |

| NWAIT          | External Wait Signal          | Input                 | Low             |          |

| NWE0           | Write Enable 0                | Output                | Low             |          |

| NWE1           | Write Enable 1                | Output                | Low             |          |

| NWE3           | Write Enable 3                | Output                | Low             |          |

| RAS            | Row Signal                    | Output                | Low             |          |

| SDA10          | SDRAM Address 10 Line         | Output                |                 |          |

| SDCK           | SDRAM Clock                   | Output                |                 |          |

| SDCKE          | SDRAM Clock Enable            | Output                |                 |          |

| SDCS0          | SDRAM Chip Select             | Output                | Low             |          |

| SDWE           | SDRAM Write Enable            | Output                | Low             |          |

|                | General Purpose Input/Ou      | tput 2 - GPIOA, GPI   | OB, GPIOC       |          |

| P0 - P31       | Parallel I/O Controller GPIOA | I/O                   |                 |          |

| P0 - P31       | Parallel I/O Controller GPIOB | I/O                   |                 |          |

| P0 - P5        | Parallel I/O Controller GPIOC | I/O                   |                 |          |

| P0 - P31       | Parallel I/O Controller GPIOX | I/O                   |                 |          |

|                | Serial Peripheral             | Interface - SPI0, SP  | 911             |          |

| MISO           | Master In Slave Out           | I/O                   |                 |          |

| MOSI           | Master Out Slave In           | I/O                   |                 |          |

| NPCS0 - NPCS3  | SPI Peripheral Chip Select    | I/O                   | Low             |          |

| SCK            | Clock                         | Output                |                 |          |

|                | Synchronous Se                | erial Controller - SS | С               |          |

| RX_CLOCK       | SSC Receive Clock             | I/O                   |                 |          |

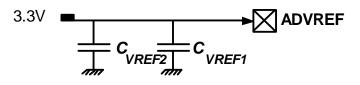

# 7.3 Analog-to-Digital Converter (A.D.C) reference.

The ADC reference (ADVREF) must be provided from an external source. Two decoupling capacitors must be used to insure proper decoupling.

Refer to Section 12.4 on page 42 for decoupling capacitors values and electrical characteristics. In case ADC is not used, the ADVREF pin should be connected to GND to avoid extra consumption.

|    | interrupt Request | l Signal Map                      |        |

|----|-------------------|-----------------------------------|--------|

| 9  | 0                 | Serial Peripheral Interface       | SPI0   |

| 10 | 0                 | Serial Peripheral Interface       | SPI1   |

| 11 | 0                 | Two-wire Interface                | TWI    |

| 12 | 0                 | Pulse Width Modulation Controller | PWM    |

| 13 | 0                 | Synchronous Serial Controller     | SSC    |

|    | 0                 | Timer/Counter                     | TC0    |

| 14 | 1                 | Timer/Counter                     | TC1    |

|    | 2                 | Timer/Counter                     | TC2    |

| 15 | 0                 | Analog to Digital Converter       | ADC    |

| 16 | 0                 | Ethernet MAC                      | MACB   |

| 17 | 0                 | USB 2.0 OTG Interface             | USBB   |

| 18 | 0                 | SDRAM Controller                  | SDRAMC |

| 19 | 0                 | Audio Bitstream DAC               | DAC    |

Table 10-3.

Interrupt Request Signal Map

# **10.4 Clock Connections**

## 10.4.1 Timer/Counters

Each Timer/Counter channel can independently select an internal or external clock source for its counter:

| Source   | Name         | Connection        |

|----------|--------------|-------------------|

| Internal | TIMER_CLOCK1 | 32 KHz Oscillator |

|          | TIMER_CLOCK2 | PBA clock / 2     |

|          | TIMER_CLOCK3 | PBA clock / 8     |

|          | TIMER_CLOCK4 | PBA clock / 32    |

|          | TIMER_CLOCK5 | PBA clock / 128   |

| External | XC0          | See Section 10.7  |

|          | XC1          |                   |

|          | XC2          |                   |

Table 10-4.

Timer/Counter clock connections

#### 10.4.2 USARTs

Each USART can be connected to an internally divided clock:

| USART | Source   | Name    | Connection    |  |  |  |  |  |

|-------|----------|---------|---------------|--|--|--|--|--|

| 0     | Internal | CLK_DIV | PBA clock / 8 |  |  |  |  |  |

| 1     |          |         |               |  |  |  |  |  |

| 2     |          |         |               |  |  |  |  |  |

| 3     |          |         |               |  |  |  |  |  |

Table 10-5. USART clock connections

### 10.4.3 SPIs

Each SPI can be connected to an internally divided clock:

| Table 10-6. | SPI | clock conn | ections |

|-------------|-----|------------|---------|

|             | 011 |            | 000000  |

| SPI | Source   | Name    | Connection     |

|-----|----------|---------|----------------|

| 0   | Internal | CLK_DIV | PBA clock or   |

| 1   |          |         | PBA clock / 32 |

## 10.5 Nexus OCD AUX port connections

If the OCD trace system is enabled, the trace system will take control over a number of pins, irrespectively of the PIO configuration. Two different OCD trace pin mappings are possible, depending on the configuration of the OCD AXS register. For details, see the AVR32 UC Technical Reference Manual.

|         | Nexus OCD ADA | port connections |

|---------|---------------|------------------|

| Pin     | AXS=0         | AXS=1            |

| EVTI_N  | PB19          | PA08             |

| MDO[5]  | PB16          | PA27             |

| MDO[4]  | PB14          | PA26             |

| MDO[3]  | PB13          | PA25             |

| MDO[2]  | PB12          | PA24             |

| MDO[1]  | PB11          | PA23             |

| MDO[0]  | PB10          | PA22             |

| EVTO_N  | PB20          | PB20             |

| MCKO    | PB21          | PA21             |

| MSEO[1] | PB04          | PA07             |

| MSEO[0] | PB17          | PA28             |

Table 10-7.

Nexus OCD AUX port connections

# 10.6 PDC handshake signals

The PDC and the peripheral modules communicate through a set of handshake signals. The following table defines the valid settings for the Peripheral Identifier (PID) in the PDC Peripheral Select Register (PSR).

|           | Table 10-6. PDC Handshake Signals |  |  |  |  |

|-----------|-----------------------------------|--|--|--|--|

| PID Value | Peripheral module & direction     |  |  |  |  |

| 0         | ADC                               |  |  |  |  |

| 1         | SSC - RX                          |  |  |  |  |

| 2         | USART0 - RX                       |  |  |  |  |

| 3         | USART1 - RX                       |  |  |  |  |

Table 10-8. PDC Handshake Signals

## 10.10 GPIO

The GPIO open drain feature (GPIO ODMER register (Open Drain Mode Enable Register)) is not available for this device.

## **10.11** Peripheral overview

### 10.11.1 External Bus Interface

- Optimized for Application Memory Space support

- Integrates Two External Memory Controllers:

- Static Memory Controller

- SDRAM Controller

- Optimized External Bus:

- 16-bit Data Bus

- 24-bit Address Bus, Up to 16-Mbytes Addressable

- Optimized pin multiplexing to reduce latencies on External Memories

- 4 SRAM Chip Selects, 1SDRAM Chip Select:

- Static Memory Controller on NCS0

- SDRAM Controller or Static Memory Controller on NCS1

- Static Memory Controller on NCS2

- Static Memory Controller on NCS3

## 10.11.2 Static Memory Controller

- 4 Chip Selects Available

- 64-Mbyte Address Space per Chip Select

- 8-, 16-bit Data Bus

- Word, Halfword, Byte Transfers

- Byte Write or Byte Select Lines

- Programmable Setup, Pulse And Hold Time for Read Signals per Chip Select

- Programmable Setup, Pulse And Hold Time for Write Signals per Chip Select

- Programmable Data Float Time per Chip Select

- Compliant with LCD Module

- External Wait Request

- Automatic Switch to Slow Clock Mode

- Asynchronous Read in Page Mode Supported: Page Size Ranges from 4 to 32 Bytes

## 10.11.3 SDRAM Controller

- Numerous Configurations Supported

- 2K, 4K, 8K Row Address Memory Parts

- SDRAM with Two or Four Internal Banks

- SDRAM with 16-bit Data Path

- Programming Facilities

- Word, Half-word, Byte Access

- Automatic Page Break When Memory Boundary Has Been Reached

- Multibank Ping-pong Access

- Timing Parameters Specified by Software

- Automatic Refresh Operation, Refresh Rate is Programmable

- Energy-saving Capabilities

- Self-refresh, Power-down and Deep Power Modes Supported

# 12.3 Regulator characteristics

Table 12-2.

Electrical characteristics

| Symbol              | Parameter                                         | Condition                                                         | Min. | Тур. | Max. | Units |

|---------------------|---------------------------------------------------|-------------------------------------------------------------------|------|------|------|-------|

| $V_{\text{VDDIN}}$  | Supply voltage (input)                            |                                                                   | 3    | 3.3  | 3.6  | V     |

| V <sub>VDDOUT</sub> | Supply voltage (output)                           |                                                                   | 1.81 | 1.85 | 1.89 | V     |

|                     | Maximum DC output current with $V_{VDDIN = 3.3V}$ |                                                                   |      |      | 100  | mA    |

| OUT                 | Maximum DC output current with $V_{VDDIN = 2.7V}$ |                                                                   |      |      | 90   | mA    |

| I <sub>SCR</sub>    | Static Current of internal regulator              | Low Power mode (stop, deep stop or static) at $T_A = 25^{\circ}C$ |      | 10   |      | μA    |

## Table 12-3.Decoupling requirements

| Symbol            | Parameter                    | Condition | Тур. | Techno. | Units |

|-------------------|------------------------------|-----------|------|---------|-------|

| C <sub>IN1</sub>  | Input Regulator Capacitor 1  |           | 1    | NPO     | nF    |

| C <sub>IN2</sub>  | Input Regulator Capacitor 2  |           | 4.7  | X7R     | uF    |

| C <sub>OUT1</sub> | Output Regulator Capacitor 1 |           | 470  | NPO     | pF    |

| C <sub>OUT2</sub> | Output Regulator Capacitor 2 |           | 2.2  | X7R     | uF    |

# 12.4 Analog characteristics

Table 12-4. Electrical characteristics

| Symbol  | Parameter                        | Condition | Min. | Тур. | Max. | Units |

|---------|----------------------------------|-----------|------|------|------|-------|

| VADVREF | Analog voltage reference (input) |           | 2.6  |      | 3.6  | V     |

## **Table 12-5.**Decoupling requirements

| Symbol             | Parameter                     | Condition | Тур. | Techno | Units |

|--------------------|-------------------------------|-----------|------|--------|-------|

| C <sub>VREF1</sub> | Voltage reference Capacitor 1 |           | 10   | -      | nF    |

| C <sub>VREF2</sub> | Voltage reference Capacitor 2 |           | 1    | -      | uF    |

12.4.1 BOD

Table 12-6.BODLEVEL Values

| BODLEVEL Value | Тур. | Тур. | Тур. | Units. |

|----------------|------|------|------|--------|

| 00 0000b       | 1.40 | 1.47 | 1.55 | V      |

| 01 0111b       | 1.45 | 1.52 | 1.6  | V      |

| 01 1111b       | 1.55 | 1.6  | 1.65 | V      |

| 10 0111b       | 1.65 | 1.69 | 1.75 | V      |

The values in Table 12-6 describes the values of the BODLEVEL in the flash FGPFR register.

# Table 12-7. BOD Timing

| Symbol           | Parameter                                                      | Test Conditions                      | Тур. | Max. | Units. |

|------------------|----------------------------------------------------------------|--------------------------------------|------|------|--------|

| T <sub>BOD</sub> | Minimum time with<br>VDDCORE < VBOD to<br>detect power failure | Falling VDDCORE<br>from 1.8V to 1.1V | 300  | 800  | ns     |

## 12.4.2 POR

## Table 12-8. Electrical Characteristic

| Symbol               | Parameter                                                                                                                            | Test Conditions                                              | Min. | Тур. | Max. | Units. |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|------|------|------|--------|

| V <sub>DDRR</sub>    | VDDCORE rise rate to ensure power-on-reset                                                                                           |                                                              | 0.01 |      |      | V/ms   |

| V <sub>SSFR</sub>    | VDDCORE fall rate to ensure power-on-reset                                                                                           |                                                              | 0.01 |      | 400  | V/ms   |

| V <sub>POR+</sub>    | Rising threshold voltage: voltage up to which device is kept under reset by POR on rising VDDCORE                                    | Rising VDDCORE:<br>V <sub>RESTART</sub> -> V <sub>POR+</sub> | 1.35 | 1.5  | 1.6  | v      |

| V <sub>POR-</sub>    | Falling threshold voltage: voltage when POR resets device on falling VDDCORE                                                         | Falling VDDCORE:<br>1.8V -> V <sub>POR+</sub>                | 1.25 | 1.3  | 1.4  | V      |

| V <sub>RESTART</sub> | On falling VDDCORE, voltage must go down to this value before supply can rise again to ensure reset signal is released at $V_{POR+}$ | Falling VDDCORE:<br>1.8V -> V <sub>RESTART</sub>             | -0.1 |      | 0.5  | v      |

| T <sub>POR</sub>     | Minimum time with VDDCORE < V <sub>POR</sub> .                                                                                       | Falling VDDCORE:<br>1.8V -> 1.1V                             |      | 15   |      | us     |

| T <sub>RST</sub>     | Time for reset signal to be propagated to system                                                                                     |                                                              |      | 200  | 400  | us     |

| Table 12-21. | Transfer | Characteristics | in | 10-bit mode |

|--------------|----------|-----------------|----|-------------|

|--------------|----------|-----------------|----|-------------|

| Parameter                  | Conditions | Min | Тур | Max | Units |

|----------------------------|------------|-----|-----|-----|-------|

| Resolution                 |            |     | 10  |     | Bit   |

| Absolute Accuracy          | f=5MHz     |     |     | 3   | LSB   |

| Integral Non-linearity     | f=5MHz     |     | 1.5 | 2   | LSB   |

| Differential Neg linearity | f=5MHz     |     | 1   | 2   | LSB   |

| Differential Non-linearity | f=2.5MHz   |     | 0.6 | 1   | LSB   |

| Offset Error               | f=5MHz     | -2  |     | 2   | LSB   |

| Gain Error                 | f=5MHz     | -2  |     | 2   | LSB   |

| Symbol            | Parameter                  | Min                        | Units |

|-------------------|----------------------------|----------------------------|-------|

|                   | NRD C                      | Controlled (READ_MODE = 1) |       |

| SMC <sub>19</sub> | Data Setup before NRD High | 13.7                       |       |

| SMC <sub>20</sub> | Data Hold after NRD High   | 1                          | ns    |

|                   | NRD C                      | Controlled (READ_MODE = 0) |       |

| SMC <sub>21</sub> | Data Setup before NCS High | 13.3                       |       |

| SMC <sub>22</sub> | Data Hold after NCS High   | 0                          | ns    |

## Table 12-24. SMC Read Signals with no Hold Settings

Table 12-25. SMC Write Signals with Hold Settings

| Symbol            | Parameter                                    | Min                                                              |    |

|-------------------|----------------------------------------------|------------------------------------------------------------------|----|

|                   | NRD C                                        | controlled (READ_MODE = 1)                                       |    |

| SMC <sub>23</sub> | Data Out Valid before NWE High               | (nwe pulse length - 1) * t <sub>CPSMC</sub> - 0.9                |    |

| SMC <sub>24</sub> | Data Out Valid after NWE High <sup>(1)</sup> | nwe hold length * t <sub>CPSMC</sub> - 6                         |    |

| SMC <sub>25</sub> | NWE High to NBS0/A0 Change <sup>(1)</sup>    | nwe hold length * t <sub>CPSMC</sub> - 1.9                       |    |

| SMC <sub>26</sub> | NWE High to NBS1 Change <sup>(1)</sup>       | nwe hold length * t <sub>CPSMC</sub> - 1.9                       |    |

| SMC <sub>29</sub> | NWE High to NBS2/A1 Change <sup>(1)</sup>    | nwe hold length * t <sub>CPSMC</sub> - 1.9                       | ns |

| SMC <sub>30</sub> | NWE High to NBS3 Change <sup>(1)</sup>       | nwe hold length * t <sub>CPSMC</sub> - 1.9                       |    |

| SMC <sub>31</sub> | NWE High to A2 - A25 Change <sup>(1)</sup>   | nwe hold length * t <sub>CPSMC</sub> - 1.7                       |    |

| SMC <sub>32</sub> | NWE High to NCS Inactive <sup>(1)</sup>      | (nwe hold length - ncs wr hold length)* t <sub>CPSMC</sub> - 2.9 |    |

| SMC <sub>33</sub> | NWE Pulse Width                              | nwe pulse length * t <sub>CPSMC</sub> - 0.9                      |    |

|                   | NRD C                                        | controlled (READ_MODE = 0)                                       | U  |

| SMC <sub>34</sub> | Data Out Valid before NCS High               | (ncs wr pulse length - 1)* t <sub>CPSMC</sub> - 4.6              |    |

| SMC <sub>35</sub> | Data Out Valid after NCS High <sup>(1)</sup> | ncs wr hold length * t <sub>CPSMC</sub> - 5.8                    | ns |

| SMC <sub>36</sub> | NCS High to NWE Inactive <sup>(1)</sup>      | (ncs wr hold length - nwe hold length)* t <sub>CPSMC</sub> - 0.6 |    |

Note: 1. hold length = total cycle duration - setup duration - pulse duration. "hold length" is for "ncs wr hold length" or "nwe hold length"

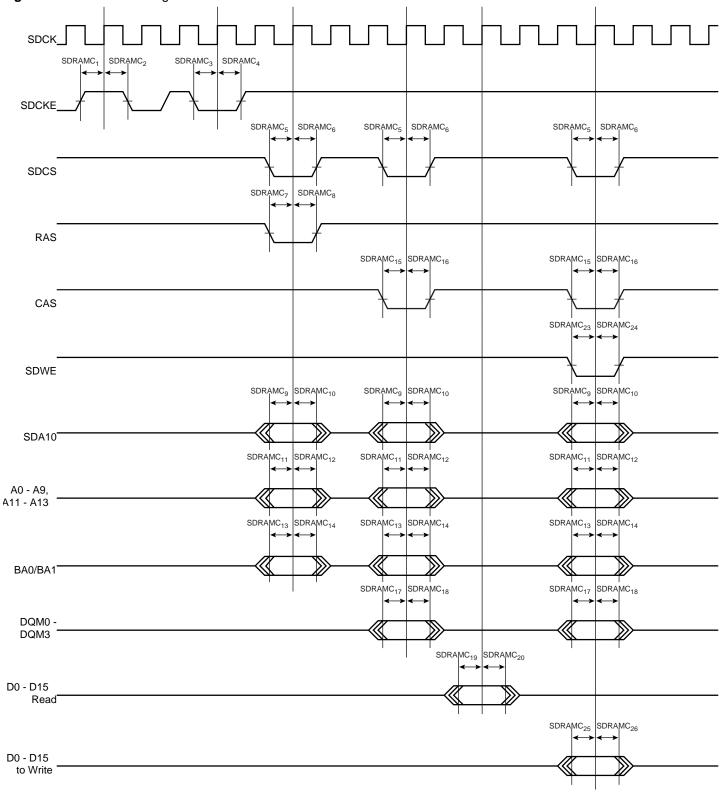

| Symbol               | Parameter                                | Min | Units |

|----------------------|------------------------------------------|-----|-------|

| SDRAMC <sub>11</sub> | Address Change before SDCK Rising Edge   | 6.2 |       |

| SDRAMC <sub>12</sub> | Address Change after SDCK Rising Edge    | 2.2 |       |

| SDRAMC <sub>13</sub> | Bank Change before SDCK Rising Edge      | 6.3 |       |

| SDRAMC <sub>14</sub> | Bank Change after SDCK Rising Edge       | 2.4 |       |

| SDRAMC <sub>15</sub> | CAS Low before SDCK Rising Edge          | 7.4 | 1     |

| SDRAMC <sub>16</sub> | CAS High after SDCK Rising Edge          | 1.9 |       |

| SDRAMC <sub>17</sub> | DQM Change before SDCK Rising Edge       | 6.4 | ]     |

| SDRAMC <sub>18</sub> | DQM Change after SDCK Rising Edge        | 2.2 | ns    |

| SDRAMC <sub>19</sub> | D0-D15 in Setup before SDCK Rising Edge  | 9   |       |

| SDRAMC <sub>20</sub> | D0-D15 in Hold after SDCK Rising Edge    | 0   |       |

| SDRAMC <sub>23</sub> | SDWE Low before SDCK Rising Edge         | 7.6 | 1     |

| SDRAMC <sub>24</sub> | SDWE High after SDCK Rising Edge         | 1.8 | 1     |

| SDRAMC <sub>25</sub> | D0-D15 Out Valid before SDCK Rising Edge | 7.1 | 1     |

| SDRAMC <sub>26</sub> | D0-D15 Out Valid after SDCK Rising Edge  | 1.5 | ]     |

| Table 12-28. | SDRAM | Clock | Signal. |

|--------------|-------|-------|---------|

|--------------|-------|-------|---------|

AT32UC3A

Figure 12-4. SDRAMC Signals relative to SDCK.

# 12.10 JTAG Timings

## 12.10.1 JTAG Interface Signals

## Table 12-29. JTAG Interface Timing specification

| Symbol             | Parameter                      | Conditions | Min | Max | Units |

|--------------------|--------------------------------|------------|-----|-----|-------|

| JTAG <sub>0</sub>  | TCK Low Half-period            | (1)        | 6   |     | ns    |

| JTAG <sub>1</sub>  | TCK High Half-period           | (1)        | 3   |     | ns    |

| JTAG <sub>2</sub>  | TCK Period                     | (1)        | 9   |     | ns    |

| JTAG <sub>3</sub>  | TDI, TMS Setup before TCK High | (1)        | 1   |     | ns    |

| JTAG <sub>4</sub>  | TDI, TMS Hold after TCK High   | (1)        | 0   |     | ns    |

| JTAG <sub>5</sub>  | TDO Hold Time                  | (1)        | 4   |     | ns    |

| JTAG <sub>6</sub>  | TCK Low to TDO Valid           | (1)        |     | 6   | ns    |

| JTAG <sub>7</sub>  | Device Inputs Setup Time       | (1)        |     |     | ns    |

| JTAG <sub>8</sub>  | Device Inputs Hold Time        | (1)        |     |     | ns    |

| JTAG <sub>9</sub>  | Device Outputs Hold Time       | (1)        |     |     | ns    |

| JTAG <sub>10</sub> | TCK to Device Outputs Valid    | (1)        |     |     | ns    |

Note: 1.  $V_{VDDIO}$  from 3.0V to 3.6V, maximum external capacitor = 40pF

# 13.3 Soldering Profile

Table 13-11 gives the recommended soldering profile from J-STD-20.

| Profile Feature                            | Green Package            |  |

|--------------------------------------------|--------------------------|--|

| Average Ramp-up Rate (217°C to Peak)       | 3°C/sec                  |  |

| Preheat Temperature 175°C ±25°C            | Min. 150 °C, Max. 200 °C |  |

| Time Maintained Above 217°C                | 60-150 sec               |  |

| Time within 5.C of Actual Peak Temperature | 30 sec                   |  |

| Peak Temperature Range                     | 260 °C                   |  |

| Ramp-down Rate                             | 6 °C/sec                 |  |

| Time 25 C to Peak Temperature              | Max. 8 minutes           |  |

Note: It is recommended to apply a soldering temperature higher than 250°C. A maximum of three reflow passes is allowed per component.

When multiple CS are in use, if one of the baudrate equals 1, the other must also equal 1 if CPOL=1 and CPHA=0.

# 4. SPI Glitch on RXREADY flag in slave mode when enabling the SPI or during the first transfer

In slave mode, the SPI can generate a false RXREADY signal during enabling of the SPI or during the first transfer.

#### **Fix/Workaround**

- 1. Set slave mode, set required CPOL/CPHA.

- 2. Enable SPI.

- 3. Set the polarity CPOL of the line in the opposite value of the required one.

- 4. Set the polarity CPOL to the required one.

- 5. Read the RXHOLDING register.

Transfers can now befin and RXREADY will now behave as expected.

## 5. SPI Disable does not work in Slave mode Fix/workaround

Read the last received data then perform a Software reset.

## 15.3.4 Power Manager

1. If the BOD level is higher than VDDCORE, the part is constantly under reset

If the BOD level is set to a value higher than VDDCORE and enabled by fuses, the part will be in constant reset.

#### **Fix/Workaround**

Apply an external voltage on VDDCORE that is higher than the BOD level and is lower than VDDCORE max and disable the BOD.

#### 15.3.5 Flashc

# 1. On AT32UC3A0512 and AT32UC3A1512, corrupted read in flash after FLASHC WP, EP, EA, WUP, EUP commands may happen

- After a FLASHC Write Page (WP) or Erase Page (EP) command applied to a page in a given half of the flash (first or last 256 kB of flash), reading (data read or code fetch) the other half of the flash may fail. This may lead to an exception or to other errors derived from this corrupted read access.

After a FLASHC Erase All (EA) command, reading (data read or code fetch) the flash may fail. This may lead to an exception or to other errors derived from this corrupted read access.

After a FLASHC Write User Page (WUP) or Erase User Page (EUP) command, reading (data read or code fetch) the second half (last 256 kB) of the flash may fail. This may lead to an exception or to other errors derived from this corrupted read access.

#### Fix/Workaround

Flashc WP, EP, EA, WUP, EUP commands: these commands must be issued from RAM or through the EBI. After these commands, read twice one flash page initialized to 00h in each half part of the flash.

15.3.6 PDCA

1. Wrong PDCA behavior when using two PDCA channels with the same PID.

4. SPI Bad Serial Clock Generation on 2nd chip\_select when SCBR = 1, CPOL=1 and NCPHA=0

When multiple CS are in use, if one of the baudrate equals to 1 and one of the others doesn't equal to 1, and CPOL=1 and CPHA=0, then an aditional pulse will be generated on SCK. **Fix/workaround**

When multiple CS are in use, if one of the baudrate equals 1, the other must also equal 1 if CPOL=1 and CPHA=0.

5. SPI Glitch on RXREADY flag in slave mode when enabling the SPI or during the first transfer

In slave mode, the SPI can generate a false RXREADY signal during enabling of the SPI or during the first transfer.

## Fix/Workaround

1. Set slave mode, set required CPOL/CPHA.

- 2. Enable SPI.

- 3. Set the polarity CPOL of the line in the opposite value of the required one.

- 4. Set the polarity CPOL to the required one.

- 5. Read the RXHOLDING register.

Transfers can now befin and RXREADY will now behave as expected.

6. SPI Disable does not work in Slave mode Fix/workaround

Read the last received data then perform a Software reset.

## 15.4.4 Power Manager

## 1. Wrong reset causes when BOD is activated

Setting the BOD enable fuse will cause the Reset Cause Register to list BOD reset as the reset source even though the part was reset by another source.

#### Fix/Workaround

Do not set the BOD enable fuse, but activate the BOD as soon as your program starts.

## 2. If the BOD level is higher than VDDCORE, the part is constantly under reset

If the BOD level is set to a value higher than VDDCORE and enabled by fuses, the part will be in constant reset.

#### **Fix/Workaround**

Apply an external voltage on VDDCORE that is higher than the BOD level and is lower than VDDCORE max and disable the BOD.

## 15.4.5 FLASHC

# 1. On AT32UC3A0512 and AT32UC3A1512, corrupted read in flash after FLASHC WP, EP, EA, WUP, EUP commands may happen

- After a FLASHC Write Page (WP) or Erase Page (EP) command applied to a page in a given half of the flash (first or last 256 kB of flash), reading (data read or code fetch) the other half of the flash may fail. This may lead to an exception or to other errors derived from this corrupted read access.

After a FLASHC Erase All (EA) command, reading (data read or code fetch) the flash may fail. This may lead to an exception or to other errors derived from this corrupted read access.

After a FLASHC Write User Page (WUP) or Erase User Page (EUP) command, reading

AT32UC3A

|         |                            | (data read or code fetch) the second half (last 256 kB) of the flash may fail. This may lead to an exception or to other errors derived from this corrupted read access.                                                                                                                                                                                                                                            |

|---------|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         |                            | <b>Fix/Workaround</b><br>Flashc WP, EP, EA, WUP, EUP commands: these commands must be issued from RAM or<br>through the EBI. After these commands, read twice one flash page initialized to 00h in each<br>half part of the flash.                                                                                                                                                                                  |

| 15.4.6  | PDCA                       |                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 15.4.7  | тш                         | <ol> <li>Wrong PDCA behavior when using two PDCA channels with the same PID.<br/>Workaround/fix<br/>The same PID should not be assigned to more than one channel.</li> </ol>                                                                                                                                                                                                                                        |

| 15.4.8  | SDRAMC                     | <ol> <li>The TWI RXRDY flag in SR register is not reset when a software reset is performed.<br/>Fix/Workaround<br/>After a Software Reset, the register TWI RHR must be read.</li> </ol>                                                                                                                                                                                                                            |

|         |                            | 1. Code execution from external SDRAM does not work<br>Code execution from SDRAM does not work.                                                                                                                                                                                                                                                                                                                     |

| 15.4.9  | GPIO                       | Fix/Workaround<br>Do not run code from SDRAM.                                                                                                                                                                                                                                                                                                                                                                       |

|         |                            | <ol> <li>Some GPIO VIH (input high voltage) are 3.6V max instead of 5V tolerant<br/>Only 11 GPIOs remain 5V tolerant (VIHmax=5V):PB01, PB02, PB03, PB10, PB19, PB20,<br/>PB21, PB22, PB23, PB27, PB28.<br/>Workaround/fix<br/>None.</li> </ol>                                                                                                                                                                      |

| 15.4.10 | USART                      | None.                                                                                                                                                                                                                                                                                                                                                                                                               |

|         |                            | <ol> <li>ISO7816 info register US_NER cannot be read<br/>The NER register always returns zero.</li> <li>Fix/Workaround<br/>None.</li> </ol>                                                                                                                                                                                                                                                                         |

| 15.4.11 | Processor and Architecture |                                                                                                                                                                                                                                                                                                                                                                                                                     |

|         |                            | <ol> <li>LDM instruction with PC in the register list and without ++ increments Rp<br/>For LDM with PC in the register list: the instruction behaves as if the ++ field is always set, ie<br/>the pointer is always updated. This happens even if the ++ field is cleared. Specifically, the<br/>increment of the pointer is done in parallel with the testing of R12.</li> <li>Fix/Workaround<br/>None.</li> </ol> |

|         |                            | <ol> <li>RETE instruction does not clear SREG[L] from interrupts.<br/>The RETE instruction clears SREG[L] as expected from exceptions.</li> <li>Fix/Workaround</li> </ol>                                                                                                                                                                                                                                           |

When using the STCOND instruction, clear SREG[L] in the stacked value of SR before returning from interrupts with RETE.

3. Exceptions when system stack is protected by MPU

# 15.5 Rev. E

## 15.5.1 SPI

## 1. SPI FDIV option does not work

Selecting clock signal using FDIV = 1 does not work as specified.

## **Fix/Workaround**

Do not set FDIV = 1.

## 2. SPI Slave / PDCA transfer: no TX UNDERRUN flag

There is no TX UNDERRUN flag available, therefore in SPI slave mode, there is no way to be informed of a character lost in transmission.

## **Fix/Workaround**

For PDCA transfer: none.

3. SPI Bad serial clock generation on 2nd chip select when SCBR=1, CPOL=1 and CNCPHA=0

When multiple CS are in use, if one of the baudrate equals to 1 and one of the others doesn't equal to 1, and CPOL=1 and CPHA=0, then an additional pulse will be generated on SCK.

## **Fix/Workaround**

When multiple CS are in use, if one of the baudrate equals to 1, the other must also equal 1 if CPOL=1 and CPHA=0.

# 4. SPI Glitch on RXREADY flag in slave mode when enabling the SPI or during the first transfer

In slave mode, the SPI can generate a false RXREADY signal during enabling of the SPI or during the first transfer.

## Fix/Workaround

- 1. Set slave mode, set required CPOL/CPHA.

- 2. Enable SPI.

- 3. Set the polarity CPOL of the line in the opposite value of the required one.

- 4. Set the polarity CPOL to the required one.

- 5. Read the RXHOLDING register.

Transfers can now befin and RXREADY will now behave as expected.

## 5. SPI CSNAAT bit 2 in register CSR0...CSR3 is not available. Fix/Workaround

Do not use this bit.

## 6. SPI disable does not work in SLAVE mode. Fix/Workaround

Read the last received data, then perform a Software Reset.

# 7. SPI Bad Serial Clock Generation on 2nd chip\_select when SCBR = 1, CPOL=1 and NCPHA=0

When multiple CS are in use, if one of the baudrate equals to 1 and one of the others doesn't equal to 1, and CPOL=1 and CPHA=0, then an aditional pulse will be generated on SCK.

## 12. CPU cannot operate on a divided slow clock (internal RC oscillator) Fix/Workaround

Do not run the CPU on a divided slow clock.

## 13. LDM instruction with PC in the register list and without ++ increments Rp

For LDM with PC in the register list: the instruction behaves as if the ++ field is always set, ie the pointer is always updated. This happens even if the ++ field is cleared. Specifically, the increment of the pointer is done in parallel with the testing of R12. **Fix/Workaround**

None.

#### 14. RETE instruction does not clear SREG[L] from interrupts.

The RETE instruction clears SREG[L] as expected from exceptions. **Fix/Workaround**

When using the STCOND instruction, clear SREG[L] in the stacked value of SR before returning from interrupts with RETE.

#### 15. Exceptions when system stack is protected by MPU

RETS behaves incorrectly when MPU is enabled and MPU is configured so that system stack is not readable in unprivileged mode.

#### **Fix/Woraround**

Workaround 1: Make system stack readable in unprivileged mode, or

Workaround 2: Return from supervisor mode using rete instead of rets. This requires :

1. Changing the mode bits from 001b to 110b before issuing the instruction. Updating the mode bits to the desired value must be done using a single mtsr instruction so it is done atomically. Even if this step is described in general as not safe in the UC technical reference guide, it is safe in this very specific case.

2. Execute the RETE instruction.

#### 15.5.6 SDRAMC

## 1. Code execution from external SDRAM does not work

Code execution from SDRAM does not work.

#### Fix/Workaround

Do not run code from SDRAM.

## 2. SDRAM SDCKE rise at the same time as SDCK while exiting self-refresh mode SDCKE rise at the same time as SDCK while exiting self-refresh mode.

#### Fix/Workaround

None.

#### 15.5.7 USART

1. USART Manchester Encoder Not Working Manchester encoding/decoding is not working.

#### Fix/Workaround

Do not use manchester encoding.

## 2. USART RXBREAK problem when no timeguard

In asynchronous mode the RXBREAK flag is not correctly handled when the timeguard is 0 and the break character is located just after the stop bit.

## Fix/Workaround

If the NBSTOP is 1, timeguard should be different from 0.

### 3. USART Handshaking: 2 characters sent / CTS rises when TX

If CTS switches from 0 to 1 during the TX of a character, if the Holding register is not empty, the TXHOLDING is also transmitted.

#### Fix/Workaround

None.

## 4. USART PDC and TIMEGUARD not supported in MANCHESTER

Manchester encoding/decoding is not working.

#### **Fix/Workaround**

Do not use manchester encoding.

5. USART SPI mode is non functional on this revision. Fix/Workaround

Do not use the USART SPI mode.

#### 6. DCD is active High instead of Low.

In modem mode the DCD signal is assumed to be active high by the USART, butshould have been active low. **Fix/Workaround**

# Add an external inverter to the DCD line.

ISO7816 info register US\_NER cannot be read The NER register always returns zero.

Fix/Workaround None.

#### 15.5.8 Power Manager

1. Voltage regulator input and output is connected to VDDIO and VDDCORE inside the device

The voltage regulator input and output is connected to VDDIO and VDDCORE respectively inside the device.

#### Fix/Workaround

Do not supply VDDCORE externally, as this supply will work in paralell with the regulator.

#### 2. Wrong reset causes when BOD is activated

Setting the BOD enable fuse will cause the Reset Cause Register to list BOD reset as the reset source even though the part was reset by another source.

#### **Fix/Workaround**

Do not set the BOD enable fuse, but activate the BOD as soon as your program starts.

#### 3. PLL0/1 Lock control does not work

Lock Control does not work for PLL0 and PLL1.

# 16.6 Rev. C - 10/07

- 1. Updated "Signal Description List" on page 8. Removed RXDN and TXDN from USART section.

- 2. Updated "Errata" on page 70. Rev G replaced by rev H.

# 16.7 Rev. B - 10/07

- 1. Updated "Features" on page 1.

- 2. Update "Blockdiagram" on page 4 with local bus.

- 3. Updated "Peripherals" on page 34 with local bus.

- 4. Add SPI feature in "Universial Synchronous/Asynchronous Receiver/Transmitter (USART)" on page 315.

- 5. Updated "USB On-The-Go Interface (USBB)" on page 517.

- 6. Updated "JTAG and Boundary Scan" on page 750 with programming procedure .

- 7. Add description for silicon Rev G.

# 16.8 Rev. A - 03/07

1. Initial revision.