#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | AVR                                                                        |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 66MHz                                                                      |

| Connectivity               | Ethernet, I <sup>2</sup> C, SPI, SSC, UART/USART, USB OTG                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 69                                                                         |

| Program Memory Size        | 256KB (256K x 8)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 64K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 3.6V                                                               |

| Data Converters            | A/D 8x10b                                                                  |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 100-TQFP                                                                   |

| Supplier Device Package    | 100-TQFP (14x14)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at32uc3a1256-aut |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1. Description

The AT32UC3A is a complete System-On-Chip microcontroller based on the AVR32 UC RISC processor running at frequencies up to 66 MHz. AVR32 UC is a high-performance 32-bit RISC microprocessor core, designed for cost-sensitive embedded applications, with particular emphasis on low power consumption, high code density and high performance.

The processor implements a Memory Protection Unit (MPU) and a fast and flexible interrupt controller for supporting modern operating systems and real-time operating systems. Higher computation capabilities are achievable using a rich set of DSP instructions.

The AT32UC3A incorporates on-chip Flash and SRAM memories for secure and fast access. For applications requiring additional memory, an external memory interface is provided on AT32UC3A0 derivatives.

The Peripheral Direct Memory Access controller (PDCA) enables data transfers between peripherals and memories without processor involvement. PDCA drastically reduces processing overhead when transferring continuous and large data streams between modules within the MCU.

The PowerManager improves design flexibility and security: the on-chip Brown-Out Detector monitors the power supply, the CPU runs from the on-chip RC oscillator or from one of external oscillator sources, a Real-Time Clock and its associated timer keeps track of the time.

The Timer/Counter includes three identical 16-bit timer/counter channels. Each channel can be independently programmed to perform frequency measurement, event counting, interval measurement, pulse generation, delay timing and pulse width modulation.

The PWM modules provides seven independent channels with many configuration options including polarity, edge alignment and waveform non overlap control. One PWM channel can trigger ADC conversions for more accurate close loop control implementations.

The AT32UC3A also features many communication interfaces for communication intensive applications. In addition to standard serial interfaces like UART, SPI or TWI, other interfaces like flexible Synchronous Serial Controller, USB and Ethernet MAC are available.

The Synchronous Serial Controller provides easy access to serial communication protocols and audio standards like I2S.

The Full-Speed USB 2.0 Device interface supports several USB Classes at the same time thanks to the rich End-Point configuration. The On-The-GO (OTG) Host interface allows device like a USB Flash disk or a USB printer to be directly connected to the processor.

The media-independent interface (MII) and reduced MII (RMII) 10/100 Ethernet MAC module provides on-chip solutions for network-connected devices.

AT32UC3A integrates a class 2+ Nexus 2.0 On-Chip Debug (OCD) System, with non-intrusive real-time trace, full-speed read/write memory access in addition to basic runtime control.

## Table 5-1.Signal Description List

| Signal Name    | Function                      | Туре                  | Active<br>Level | Comments |  |  |  |  |

|----------------|-------------------------------|-----------------------|-----------------|----------|--|--|--|--|

|                | External Bus Interface - HEBI |                       |                 |          |  |  |  |  |

| ADDR0 - ADDR23 | Address Bus                   | Output                |                 |          |  |  |  |  |

| CAS            | Column Signal                 | Output                | Low             |          |  |  |  |  |

| DATA0 - DATA15 | Data Bus                      | I/O                   |                 |          |  |  |  |  |

| NCS0 - NCS3    | Chip Select                   | Output                | Low             |          |  |  |  |  |

| NRD            | Read Signal                   | Output                | Low             |          |  |  |  |  |

| NWAIT          | External Wait Signal          | Input                 | Low             |          |  |  |  |  |

| NWE0           | Write Enable 0                | Output                | Low             |          |  |  |  |  |

| NWE1           | Write Enable 1                | Output                | Low             |          |  |  |  |  |

| NWE3           | Write Enable 3                | Output                | Low             |          |  |  |  |  |

| RAS            | Row Signal                    | Output                | Low             |          |  |  |  |  |

| SDA10          | SDRAM Address 10 Line         | Output                |                 |          |  |  |  |  |

| SDCK           | SDRAM Clock                   | Output                |                 |          |  |  |  |  |

| SDCKE          | SDRAM Clock Enable            | Output                |                 |          |  |  |  |  |

| SDCS0          | SDRAM Chip Select             | Output                | Low             |          |  |  |  |  |

| SDWE           | SDRAM Write Enable            | Output                | Low             |          |  |  |  |  |

|                | General Purpose Input/Ou      | tput 2 - GPIOA, GPI   | OB, GPIOC       |          |  |  |  |  |

| P0 - P31       | Parallel I/O Controller GPIOA | I/O                   |                 |          |  |  |  |  |

| P0 - P31       | Parallel I/O Controller GPIOB | I/O                   |                 |          |  |  |  |  |

| P0 - P5        | Parallel I/O Controller GPIOC | I/O                   |                 |          |  |  |  |  |

| P0 - P31       | Parallel I/O Controller GPIOX | I/O                   |                 |          |  |  |  |  |

|                | Serial Peripheral             | Interface - SPI0, SP  | 911             |          |  |  |  |  |

| MISO           | Master In Slave Out           | I/O                   |                 |          |  |  |  |  |

| MOSI           | Master Out Slave In           | I/O                   |                 |          |  |  |  |  |

| NPCS0 - NPCS3  | SPI Peripheral Chip Select    | I/O                   | Low             |          |  |  |  |  |

| SCK            | Clock                         | Output                |                 |          |  |  |  |  |

|                | Synchronous Se                | erial Controller - SS | С               |          |  |  |  |  |

| RX_CLOCK       | SSC Receive Clock             | I/O                   |                 |          |  |  |  |  |

|   | 1     | 2       | 3    | 4    | 5      | 6    | 7    | 8       |

|---|-------|---------|------|------|--------|------|------|---------|

| Α | VDDIO | PB07    | PB05 | PB02 | PB03   | PB01 | PC00 | PA28    |

| в | PB08  | GND     | PB06 | PB04 | VDDIO  | PB00 | PC01 | VDDPLL  |

| С | PB09  | PX33    | PA29 | PC02 | PX28   | PX26 | PX22 | PX21    |

| D | PB11  | PB13    | PB12 | PX30 | PX29   | PX25 | PX24 | PX20    |

| Е | PB10  | VDDIO   | PX32 | PX31 | VDDIO  | PX27 | PX23 | VDDANA  |

| F | PA30  | PB14    | PX34 | PB16 | тск    | GND  | GND  | PX16    |

| G | TMS   | PC03    | PX36 | PX35 | PX37   | GND  | GND  | PA16    |

| н | TDO   | VDDCORE | PX38 | PX39 | VDDIO  | PA01 | PA10 | VDDCORE |

| J | TDI   | PB17    | PB15 | PX00 | PX01   | PA00 | PA03 | PA04    |

| κ | PC05  | PC04    | PB19 | PB20 | PX02   | PB29 | PB30 | PA02    |

| L | PB21  | GND     | PB18 | PB24 | VDDOUT | PX04 | PB31 | VDDIN   |

| М | PB22  | PB23    | PB25 | PB26 | PX03   | PB27 | PB28 | RESET_N |

## Table 6-4.BGA144 Package Pinout A9..M12

|   | 9      | 10     | 11      | 12      |

|---|--------|--------|---------|---------|

| Α | PA26   | PA25   | PA24    | PA23    |

| В | PA27   | PA21   | GND     | PA22    |

| С | ADVREF | GNDANA | PX19    | PA19    |

| D | PA18   | PA20   | DP      | DM      |

| Е | PX18   | PX17   | VDDIO   | VBUS    |

| F | PA17   | PX15   | PA15    | PA14    |

| G | PA13   | PA12   | PA11    | NC      |

| н | PX11   | PA08   | VDDCORE | VDDCORE |

| J | PX14   | PA07   | PX13    | PA09    |

| к | PX08   | GND    | PA05    | PX12    |

| L | PX06   | PX10   | GND     | PA06    |

| М | PX05   | PX07   | PX09    | VDDIO   |

Note: NC is not connected.

AT32UC3A

#### 10.11.11 Ethernet 10/100 MAC

- Compatibility with IEEE Standard 802.3

- 10 and 100 Mbits per second data throughput capability

- Full- and half-duplex operations

- MII or RMII interface to the physical layer

- Register Interface to address, data, status and control registers

- DMA Interface, operating as a master on the Memory Controller

- Interrupt generation to signal receive and transmit completion

- 28-byte transmit and 28-byte receive FIFOs

- Automatic pad and CRC generation on transmitted frames

- Address checking logic to recognize four 48-bit addresses

- · Support promiscuous mode where all valid frames are copied to memory

- Support physical layer management through MDIO interface control of alarm and update time/calendar data

#### 10.11.12 Audio Bitstream DAC

- Digital Stereo DAC

- Oversampled D/A conversion architecture

- Oversampling ratio fixed 128x

- FIR equalization filter

- Digital interpolation filter: Comb4

- 3rd Order Sigma-Delta D/A converters

- Digital bitstream outputs

- Parallel interface

- Connected to Peripheral DMA Controller for background transfer without CPU intervention

## 11. Boot Sequence

This chapter summarizes the boot sequence of the AT32UC3A. The behaviour after power-up is controlled by the Power Manager. For specific details, refer to Section 13. "Power Manager (PM)" on page 53.

## 11.1 Starting of clocks

After power-up, the device will be held in a reset state by the Power-On Reset circuitry, until the power has stabilized throughout the device. Once the power has stabilized, the device will use the internal RC Oscillator as clock source.

On system start-up, the PLLs are disabled. All clocks to all modules are running. No clocks have a divided frequency, all parts of the system recieves a clock with the same frequency as the internal RC Oscillator.

## **11.2** Fetching of initial instructions

After reset has been released, the AVR32 UC CPU starts fetching instructions from the reset address, which is 0x8000\_0000. This address points to the first address in the internal Flash.

The code read from the internal Flash is free to configure the system to use for example the PLLs, to divide the frequency of the clock routed to some of the peripherals, and to gate the clocks to unused peripherals.

# **12. Electrical Characteristics**

## 12.1 Absolute Maximum Ratings\*

| Operating Temperature40.C to +85.C                                                                          |

|-------------------------------------------------------------------------------------------------------------|

| Storage Temperature60°C to +150°C                                                                           |

| Voltage on Input Pin<br>with respect to Ground except for PC00, PC01, PC02, PC03,<br>PC04, PC050.3V to 5.5V |

| Voltage on Input Pin<br>with respect to Ground for PC00, PC01, PC02, PC03, PC04,<br>PC050.3V to 3.6V        |

|                                                                                                             |

| Maximum Operating Voltage (VDDCORE, VDDPLL) 1.95V                                                           |

| Maximum Operating Voltage (VDDIO, VDDIN, VDDANA).3.6V                                                       |

| Total DC Output Current on all I/O Pin<br>for TQFP100 package                                               |

\*NOTICE: Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

These figures represent the power consumption measured on the power supplies.

Table 12-9.

Power Consumption for Different Modes

| Mode         | Conditions                                                                                                                                                                                                                                     |            | Тур. | Unit |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------|------|

|              | Typ : Ta =25 °C                                                                                                                                                                                                                                | f = 12 MHz | 9    | mA   |

|              | CPU running from flash <sup>(1)</sup> .                                                                                                                                                                                                        | f = 24 MHz | 15   | mA   |

|              | VDDIN=3.3 V. VDDCORE =1.8V.<br>CPU clocked from PLL0 at f MHz                                                                                                                                                                                  | f = 36MHz  | 20   | mA   |

|              | Voltage regulator is on.                                                                                                                                                                                                                       | f = 50 MHz | 28   | mA   |

| Active       | <ul> <li>XIN0 : external clock. <sup>(1)</sup></li> <li>XIN1 stopped. XIN32 stopped</li> <li>PLL0 running</li> <li>All peripheral clocks activated.</li> <li>GPIOs on internal pull-up.</li> <li>JTAG unconnected with ext pull-up.</li> </ul> | f = 66 MHz | 36.3 | mA   |

|              | Typ : Ta = 25 °C                                                                                                                                                                                                                               | f = 12 MHz | 5    | mA   |

|              | CPU running from flash <sup>(1)</sup> .<br>VDDIN=3.3 V. VDDCORE =1.8V.                                                                                                                                                                         | f = 24 MHz | 10   | mA   |

|              | CPU clocked from PLL0 at f MHz                                                                                                                                                                                                                 | f = 36MHz  | 14   | mA   |

|              | Voltage regulator is on.<br>XIN0 : external clock.<br>XIN1 stopped. XIN32 stopped<br>PLL0 running<br>All peripheral clocks activated.<br>GPIOs on internal pull-up.<br>JTAG unconnected with ext pull-up.                                      | f = 50 MHz | 19   | mA   |

| ldle         |                                                                                                                                                                                                                                                | f = 66 MHz | 25.5 | mA   |

|              | Typ : Ta = 25 °C                                                                                                                                                                                                                               | f = 12 MHz | 3    | mA   |

|              | CPU running from flash <sup>(1)</sup> .                                                                                                                                                                                                        | f = 24 MHz | 6    | mA   |

|              | CPU clocked from PLL0 at f MHz<br>Voltage regulator is on.                                                                                                                                                                                     | f = 36MHz  | 9    | mA   |

| <b>-</b>     | XIN0 : external clock.                                                                                                                                                                                                                         | f = 50 MHz | 13   | mA   |

| Frozen       | Frozen XIN0 : external clock.<br>XIN1 stopped. XIN32 stopped<br>PLL0 running<br>All peripheral clocks activated.<br>GPIOs on internal pull-up.<br>JTAG unconnected with ext pull-up.                                                           | f = 66 MHz | 16.8 | mA   |

|              | Typ : Ta = 25 °C                                                                                                                                                                                                                               | f = 12 MHz | 1    | mA   |

|              | CPU running from flash <sup>(1)</sup> .                                                                                                                                                                                                        | f = 24 MHz | 2    | mA   |

|              | CPU clocked from PLL0 at f MHz<br>Voltage regulator is on.                                                                                                                                                                                     | f = 36MHz  | 3    | mA   |

| Ota :: - :'' | XIN0 : external clock.                                                                                                                                                                                                                         | f = 50 MHz | 4    | mA   |

| Standby      | XIN1 stopped. XIN32 stopped<br>PLL0 running<br>All peripheral clocks activated.<br>GPIOs on internal pull-up.<br>JTAG unconnected with ext pull-up.                                                                                            | f = 66 MHz | 4.8  | mA   |

AT32UC3A

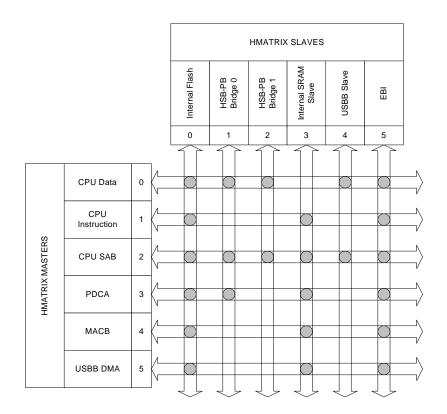

Figure 12-4. SDRAMC Signals relative to SDCK.

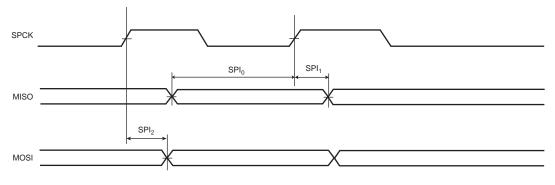

## **12.11 SPI Characteristics**

### Table 12-30. SPI Timings

| Symbol            | Parameter                                  | Conditions                 | Min                                         | Max  | Units |

|-------------------|--------------------------------------------|----------------------------|---------------------------------------------|------|-------|

| SPI0              | MISO Setup time before SPCK rises (master) | 3.3V domain <sup>(1)</sup> | 22 + (t <sub>СРМСК</sub> )/2 <sup>(2)</sup> |      | ns    |

| SPI <sub>1</sub>  | MISO Hold time after SPCK rises (master)   | 3.3V domain <sup>(1)</sup> | 0                                           |      | ns    |

| SPI <sub>2</sub>  | SPCK rising to MOSI Delay (master)         | 3.3V domain <sup>(1)</sup> |                                             | 7    | ns    |

| SPI <sub>3</sub>  | MISO Setup time before SPCK falls (master) | 3.3V domain <sup>(1)</sup> | $22 + (t_{CPMCK})/2^{(2)}$                  |      | ns    |

| SPI4              | MISO Hold time after SPCK falls (master)   | 3.3V domain <sup>(1)</sup> | 0                                           |      | ns    |

| SPI <sub>5</sub>  | SPCK falling to MOSI Delay (master)        | 3.3V domain <sup>(1)</sup> |                                             | 7    | ns    |

| SPI <sub>6</sub>  | SPCK falling to MISO Delay (slave)         | 3.3V domain <sup>(1)</sup> |                                             | 26.5 | ns    |

| SPI7              | MOSI Setup time before SPCK rises (slave)  | 3.3V domain <sup>(1)</sup> | 0                                           |      | ns    |

| SPI <sub>8</sub>  | MOSI Hold time after SPCK rises (slave)    | 3.3V domain <sup>(1)</sup> | 1.5                                         |      | ns    |

| SPI <sub>9</sub>  | SPCK rising to MISO Delay (slave)          | 3.3V domain <sup>(1)</sup> |                                             | 27   | ns    |

| SPI <sub>10</sub> | MOSI Setup time before SPCK falls (slave)  | 3.3V domain <sup>(1)</sup> | 0                                           |      | ns    |

| SPI <sub>11</sub> | MOSI Hold time after SPCK falls (slave)    | 3.3V domain <sup>(1)</sup> | 1                                           |      | ns    |

Notes: 1. 3.3V domain:  $V_{VDDIO}$  from 3.0V to 3.6V, maximum external capacitor = 40 pF.

2.  $t_{CPMCK}$ : Master Clock period in ns.

## **12.12 MACB Characteristics**

### Table 12-31. Ethernet MAC Signals

| Symbol            | Parameter                        | Conditions                | Min (ns) | Max (ns) |

|-------------------|----------------------------------|---------------------------|----------|----------|

| EMAC <sub>1</sub> | Setup for EMDIO from EMDC rising | Load: 20pF <sup>(2)</sup> |          |          |

| EMAC <sub>2</sub> | Hold for EMDIO from EMDC rising  | Load: 20pF <sup>(2)</sup> |          |          |

| EMAC <sub>3</sub> | EMDIO toggling from EMDC falling | Load: 20pF <sup>(2)</sup> |          |          |

Notes: 1. f: MCK frequency (MHz)

2.  $V_{\text{VDDIO}}$  from 3.0V to 3.6V, maximum external capacitor = 20 pF

## Table 12-32. Ethernet MAC MII Specific Signals

| Symbol             | Parameter                        | Conditions                | Min (ns) | Max (ns) |

|--------------------|----------------------------------|---------------------------|----------|----------|

| EMAC <sub>4</sub>  | Setup for ECOL from ETXCK rising | Load: 20pF <sup>(1)</sup> | 3        |          |

| EMAC <sub>5</sub>  | Hold for ECOL from ETXCK rising  | Load: 20pF <sup>(1)</sup> | 0        |          |

| EMAC <sub>6</sub>  | Setup for ECRS from ETXCK rising | Load: 20pF <sup>(1)</sup> | 3        |          |

| EMAC <sub>7</sub>  | Hold for ECRS from ETXCK rising  | Load: 20pF <sup>(1)</sup> | 0        |          |

| EMAC <sub>8</sub>  | ETXER toggling from ETXCK rising | Load: 20pF (1)            |          | 15       |

| EMAC <sub>9</sub>  | ETXEN toggling from ETXCK rising | Load: 20pF <sup>(1)</sup> |          | 15       |

| EMAC <sub>10</sub> | ETX toggling from ETXCK rising   | Load: 20pF <sup>(1)</sup> |          | 15       |

| EMAC <sub>11</sub> | Setup for ERX from ERXCK         | Load: 20pF <sup>(1)</sup> | 1        |          |

## 15.2 Rev. J

15.2.1 PWM

## 1. PWM channel interrupt enabling triggers an interrupt

When enabling a PWM channel that is configured with center aligned period (CALG=1), an interrupt is signalled.

#### Fix/Workaround

When using center aligned mode, enable the channel and read the status before channel interrupt is enabled.

#### 2. PWM counter restarts at 0x0001

The PWM counter restarts at 0x0001 and not 0x0000 as specified. Because of this the first PWM period has one more clock cycle.

Fix/Workaround

- The first period is 0x0000, 0x0001, ..., period

- Consecutive periods are 0x0001, 0x0002, ..., period

#### 3. PWM update period to a 0 value does not work

It is impossible to update a period equal to 0 by the using the PWM update register (PWM\_CUPD).

#### **Fix/Workaround**

Do not update the PWM\_CUPD register with a value equal to 0.

#### 15.2.2 ADC

### 1. Sleep Mode activation needs additional A to D conversion

If the ADC sleep mode is activated when the ADC is idle the ADC will not enter sleep mode before after the next AD conversion.

#### Fix/Workaround

Activate the sleep mode in the mode register and then perform an AD conversion.

15.2.3 SPI

### 1. SPI Slave / PDCA transfer: no TX UNDERRUN flag

There is no TX UNDERRUN flag available, therefore in SPI slave mode, there is no way to be informed of a character lost in transmission.

### Fix/Workaround

For PDCA transfer: none.

### 2. SPI FDIV option does not work

Selecting clock signal using FDIV = 1 does not work as specified.

#### **Fix/Workaround**

Do not set FDIV = 1.

3. SPI Bad Serial Clock Generation on 2nd chip\_select when SCBR = 1, CPOL=1 and NCPHA=0

When multiple CS are in use, if one of the baudrate equals to 1 and one of the others doesn't equal to 1, and CPOL=1 and CPHA=0, then an aditional pulse will be generated on SCK. **Fix/workaround**

When multiple CS are in use, if one of the baudrate equals 1, the other must also equal 1 if CPOL=1 and CPHA=0.

# 4. SPI Glitch on RXREADY flag in slave mode when enabling the SPI or during the first transfer

In slave mode, the SPI can generate a false RXREADY signal during enabling of the SPI or during the first transfer.

#### **Fix/Workaround**

- 1. Set slave mode, set required CPOL/CPHA.

- 2. Enable SPI.

- 3. Set the polarity CPOL of the line in the opposite value of the required one.

- 4. Set the polarity CPOL to the required one.

- 5. Read the RXHOLDING register.

Transfers can now befin and RXREADY will now behave as expected.

#### 5. SPI Disable does not work in Slave mode Fix/workaround

Read the last received data then perform a Software reset.

#### 15.3.4 Power Manager

1. If the BOD level is higher than VDDCORE, the part is constantly under reset

If the BOD level is set to a value higher than VDDCORE and enabled by fuses, the part will be in constant reset.

#### **Fix/Workaround**

Apply an external voltage on VDDCORE that is higher than the BOD level and is lower than VDDCORE max and disable the BOD.

#### 15.3.5 Flashc

# 1. On AT32UC3A0512 and AT32UC3A1512, corrupted read in flash after FLASHC WP, EP, EA, WUP, EUP commands may happen

- After a FLASHC Write Page (WP) or Erase Page (EP) command applied to a page in a given half of the flash (first or last 256 kB of flash), reading (data read or code fetch) the other half of the flash may fail. This may lead to an exception or to other errors derived from this corrupted read access.

After a FLASHC Erase All (EA) command, reading (data read or code fetch) the flash may fail. This may lead to an exception or to other errors derived from this corrupted read access.

After a FLASHC Write User Page (WUP) or Erase User Page (EUP) command, reading (data read or code fetch) the second half (last 256 kB) of the flash may fail. This may lead to an exception or to other errors derived from this corrupted read access.

#### Fix/Workaround

Flashc WP, EP, EA, WUP, EUP commands: these commands must be issued from RAM or through the EBI. After these commands, read twice one flash page initialized to 00h in each half part of the flash.

15.3.6 PDCA

1. Wrong PDCA behavior when using two PDCA channels with the same PID.

## 15.4 Rev. H

15.4.1 PWM

## 1. PWM channel interrupt enabling triggers an interrupt

When enabling a PWM channel that is configured with center aligned period (CALG=1), an interrupt is signalled.

#### Fix/Workaround

When using center aligned mode, enable the channel and read the status before channel interrupt is enabled.

#### 2. PWM counter restarts at 0x0001

The PWM counter restarts at 0x0001 and not 0x0000 as specified. Because of this the first PWM period has one more clock cycle.

Fix/Workaround

- The first period is 0x0000, 0x0001, ..., period

- Consecutive periods are 0x0001, 0x0002, ..., period

#### 3. PWM update period to a 0 value does not work

It is impossible to update a period equal to 0 by the using the PWM update register (PWM\_CUPD).

#### **Fix/Workaround**

Do not update the PWM\_CUPD register with a value equal to 0.

15.4.2 ADC

### 1. Sleep Mode activation needs additional A to D conversion

If the ADC sleep mode is activated when the ADC is idle the ADC will not enter sleep mode before after the next AD conversion.

### Fix/Workaround

Activate the sleep mode in the mode register and then perform an AD conversion.

15.4.3 SPI

### 1. SPI Slave / PDCA transfer: no TX UNDERRUN flag

There is no TX UNDERRUN flag available, therefore in SPI slave mode, there is no way to be informed of a character lost in transmission.

### Fix/Workaround

For PDCA transfer: none.

## 2. SPI FDIV option does not work

Selecting clock signal using FDIV = 1 does not work as specified.

#### **Fix/Workaround**

Do not set FDIV = 1

# 3. SPI disable does not work in SLAVE mode. Fix/Workaround

Read the last received data, then perform a Software Reset.

AT32UC3A

#### Fix/workaround

When multiple CS are in use, if one of the baudrate equals 1, the other must also equal 1 if CPOL=1 and CPHA=0.

#### 15.5.2 PWM

#### 1. PWM counter restarts at 0x0001

The PWM counter restarts at 0x0001 and not 0x0000 as specified. Because of this the first PWM period has one more clock cycle.

#### Fix/Workaround

- The first period is 0x0000, 0x0001, ..., period

- Consecutive periods are 0x0001, 0x0002, ..., period

#### 2. PWM channel interrupt enabling triggers an interrupt

When enabling a PWM channel that is configured with center aligned period (CALG=1), an interrupt is signalled.

#### **Fix/Workaround**

When using center aligned mode, enable the channel and read the status before channel interrupt is enabled.

#### 3. PWM update period to a 0 value does not work

It is impossible to update a period equal to 0 by the using the PWM update register (PWM\_CUPD).

#### **Fix/Workaround**

Do not update the PWM\_CUPD register with a value equal to 0.

#### 4. PWM channel status may be wrong if disabled before a period has elapsed

Before a PWM period has elapsed, the read channel status may be wrong. The CHIDx-bit for a PWM channel in the PWM Enable Register will read '1' for one full PWM period even if the channel was disabled before the period elapsed. It will then read '0' as expected.

#### Fix/Workaround

Reading the PWM channel status of a disabled channel is only correct after a PWM period has elapsed.

#### 15.5.3 SSC

#### 1. SSC does not trigger RF when data is low

The SSC cannot transmit or receive data when CKS = CKDIV and CKO = none, in TCMR or RCMR respectively.

#### **Fix/Workaround**

Set CKO to a value that is not "none" and bypass the output of the TK/RK pin with the PIO.

#### 2. SSC Data is not sent unless clock is set as output

The SSC cannot transmit or receive data when CKS = CKDIV and CKO = none, in TCMR or RCMR respectively.

#### Fix/Workaround

Set CKO to a value that is not "none" and bypass the output of the TK/RK pin with the PIO.

If the ADC sleep mode is activated when the ADC is idle the ADC will not enter sleep mode before after the next AD conversion.

#### Fix/Workaround

Activate the sleep mode in the mode register and then perform an AD conversion.

#### 15.5.11 ABDAC

Audio Bitstream DAC is not functional. Fix/Workaround

Do not use the ABDAC on revE.

#### 15.5.12 FLASHC

- The address of Flash General Purpose Fuse Register Low (FGPFRLO) is 0xFFFE140C on revE instead of 0xFFFE1410. Fix/Workaround None.

- The command Quick Page Read User Page(QPRUP) is not functional. Fix/Workaround None.

- 3. PAGEN Semantic Field for Program GP Fuse Byte is WriteData[7:0], ByteAddress[1:0] on revision E instead of WriteData[7:0], ByteAddress[2:0]. Fix/Workaround

None.

4. On AT32UC3A0512 and AT32UC3A1512, corrupted read in flash after FLASHC WP, EP, EA, WUP, EUP commands may happen

- After a FLASHC Write Page (WP) or Erase Page (EP) command applied to a page in a given half of the flash (first or last 256 kB of flash), reading (data read or code fetch) the other half of the flash may fail. This may lead to an exception or to other errors derived from this corrupted read access.

After a FLASHC Erase All (EA) command, reading (data read or code fetch) the flash may fail. This may lead to an exception or to other errors derived from this corrupted read access.

After a FLASHC Write User Page (WUP) or Erase User Page (EUP) command, reading (data read or code fetch) the second half (last 256 kB) of the flash may fail. This may lead to an exception or to other errors derived from this corrupted read access.

#### Fix/Workaround

Flashc WP, EP, EA, WUP, EUP commands: these commands must be issued from RAM or through the EBI. After these commands, read twice one flash page initialized to 00h in each half part of the flash.

15.5.13 RTC

1. Writes to control (CTRL), top (TOP) and value (VAL) in the RTC are discarded if the RTC peripheral bus clock (PBA) is divided by a factor of four or more relative to the HSB clock.

#### Fix/Workaround

Do not write to the RTC registers using the peripheral bus clock (PBA) divided by a factor of four or more relative to the HSB clock.

| 15.5.14 | OCD  | <ol> <li>The RTC CLKEN bit (bit number 16) of CTRL register is not available.<br/>Fix/Workaround<br/>Do not use the CLKEN bit of the RTC on Rev E.</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|---------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         |      | <ol> <li>Stalled memory access instruction writeback fails if followed by a HW breakpoint.<br/>Consider the following assembly code sequence:<br/>A<br/>B<br/>If a hardware breakpoint is placed on instruction B, and instruction A is a memory access<br/>instruction, register file updates from instruction A can be discarded.<br/>Fix/Workaround<br/>Do not place hardware breakpoints, use software breakpoints instead.<br/>Alternatively, place a hardware breakpoint on the instruction before the memory<br/>access instruction and then single step over the memory access instruction.</li> </ol> |

| 15.5.15 | PDCA |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|         |      | <ol> <li>Wrong PDCA behavior when using two PDCA channels with the same PID.<br/>Workaround/fix<br/>The same PID should not be assigned to more than one channel.</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 15.5.16 | TWI  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|         |      | <ol> <li>The TWI RXRDY flag in SR register is not reset when a software reset is performed.<br/>Fix/Workaround<br/>After a Software Reset, the register TWI RHR must be read.</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                       |

## 16.6 Rev. C - 10/07

- 1. Updated "Signal Description List" on page 8. Removed RXDN and TXDN from USART section.

- 2. Updated "Errata" on page 70. Rev G replaced by rev H.

## 16.7 Rev. B - 10/07

- 1. Updated "Features" on page 1.

- 2. Update "Blockdiagram" on page 4 with local bus.

- 3. Updated "Peripherals" on page 34 with local bus.

- 4. Add SPI feature in "Universial Synchronous/Asynchronous Receiver/Transmitter (USART)" on page 315.

- 5. Updated "USB On-The-Go Interface (USBB)" on page 517.

- 6. Updated "JTAG and Boundary Scan" on page 750 with programming procedure .

- 7. Add description for silicon Rev G.

## 16.8 Rev. A - 03/07

1. Initial revision.

# **Table of Contents**

| 1  | Description                                       | 3  |

|----|---------------------------------------------------|----|

| 2  | Configuration Summary                             | 4  |

| 3  | Abbreviations                                     | 4  |

| 4  | Blockdiagram                                      | 5  |

|    | 4.1Processor and architecture                     | 6  |

| 5  | Signals Description                               | 8  |

| 6  | Package and Pinout                                | 13 |

| 7  | Power Considerations                              | 17 |

|    | 7.1Power Supplies                                 | 17 |

|    | 7.2Voltage Regulator                              | 18 |

|    | 7.3Analog-to-Digital Converter (A.D.C) reference. | 19 |

| 8  | I/O Line Considerations                           | 20 |

|    | 8.1JTAG pins                                      | 20 |

|    | 8.2RESET_N pin                                    | 20 |

|    | 8.3TWI pins                                       | 20 |

|    | 8.4GPIO pins                                      | 20 |

| 9  | Memories                                          | 21 |

|    | 9.1Embedded Memories                              | 21 |

|    | 9.2Physical Memory Map                            | 21 |

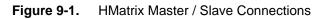

|    | 9.3Bus Matrix Connections                         | 22 |

| 10 | Peripherals                                       | 24 |

|    | 10.1Peripheral address map                        | 24 |

|    | 10.2CPU Local Bus Mapping                         | 25 |

|    | 10.3Interrupt Request Signal Map                  | 27 |

|    | 10.4Clock Connections                             | 29 |

|    | 10.5Nexus OCD AUX port connections                | 30 |

|    | 10.6PDC handshake signals                         | 30 |

|    | 10.7Peripheral Multiplexing on I/O lines          | 31 |

|    | 10.8Oscillator Pinout                             | 34 |

|    | 10.9USART Configuration                           | 34 |

|    | 10.10GPIO                                         | 35 |

#### Atmel Corporation

2325 Orchard Parkway San Jose, CA 95131 USA Tel: (+1)(408) 441-0311 Fax: (+1)(408) 487-2600 www.atmel.com

#### Atmel Asia Limited

Unit 1-5 & 16, 19/F BEA Tower, Millennium City 5 418 Kwun Tong Road Kwun Tong, Kowloon HONG KONG Tel: (+852) 2245-6100 Fax: (+852) 2722-1369

#### Atmel Munich GmbH

Business Campus Parkring 4 D-85748 Garching b. Munich GERMANY Tel: (+49) 89-31970-0 Fax: (+49) 89-3194621

#### Atmel Japan

16F, Shin Osaki Kangyo Bldg. 1-6-4 Osaka Shinagawa-ku Tokyo 104-0032 JAPAN Tel: (+81) 3-6417-0300 Fax: (+81) 3-6417-0370

#### © 2012 Atmel Corporation. All rights reserved.

Atmel<sup>®</sup>, Atmel logo and combinations thereof, AVR<sup>®</sup> and others are registered trademarks or trademarks of Atmel Corporation or its subsidiaries. Other terms and product names may be trademarks of others.

Disclaimer: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN THE ATMEL TERMS AND CONDITIONS OF SALES LOCATED ON THE ATMEL WEBSITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDENTAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS AND PROF-ITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and product descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically provided otherwise, Atmel products are not suit-able for, and shall not be used in, automotive applications. Atmel products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life.