#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | AVR                                                                        |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 66MHz                                                                      |

| Connectivity               | Ethernet, I <sup>2</sup> C, SPI, SSC, UART/USART, USB OTG                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 69                                                                         |

| Program Memory Size        | 512KB (512K x 8)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 64K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 3.6V                                                               |

| Data Converters            | A/D 8x10b                                                                  |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 100-TQFP                                                                   |

| Supplier Device Package    | 100-TQFP (14x14)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at32uc3a1512-aut |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 4.1 Processor and architecture

## 4.1.1 AVR32 UC CPU

## • 32-bit load/store AVR32A RISC architecture.

- 15 general-purpose 32-bit registers.

- 32-bit Stack Pointer, Program Counter and Link Register reside in register file.

- Fully orthogonal instruction set.

- Privileged and unprivileged modes enabling efficient and secure Operating Systems.

- Innovative instruction set together with variable instruction length ensuring industry leading code density.

- DSP extention with saturating arithmetic, and a wide variety of multiply instructions.

- 3 stage pipeline allows one instruction per clock cycle for most instructions.

- Byte, half-word, word and double word memory access.

- Multiple interrupt priority levels.

- MPU allows for operating systems with memory protection.

## 4.1.2 Debug and Test system

- IEEE1149.1 compliant JTAG and boundary scan

- Direct memory access and programming capabilities through JTAG interface

- Extensive On-Chip Debug features in compliance with IEEE-ISTO 5001-2003 (Nexus 2.0) Class 2+ - Low-cost NanoTrace supported.

- Auxiliary port for high-speed trace information

- Hardware support for 6 Program and 2 data breakpoints

- Unlimited number of software breakpoints supported

- Advanced Program, Data, Ownership, and Watchpoint trace supported

#### 4.1.3 Peripheral DMA Controller

- Transfers from/to peripheral to/from any memory space without intervention of the processor.

- Next Pointer Support, forbids strong real-time constraints on buffer management.

- Fifteen channels

- Two for each USART

- Two for each Serial Synchronous Controller

- Two for each Serial Peripheral Interface

- One for each ADC

- Two for each TWI Interface

#### 4.1.4 Bus system

- High Speed Bus (HSB) matrix with 6 Masters and 6 Slaves handled

- Handles Requests from the CPU Data Fetch, CPU Instruction Fetch, PDCA, USBB, Ethernet Controller, CPU SAB, and to internal Flash, internal SRAM, Peripheral Bus A, Peripheral Bus B, EBI.

- Round-Robin Arbitration (three modes supported: no default master, last accessed default master, fixed default master)

- Burst Breaking with Slot Cycle Limit

- One Address Decoder Provided per Master

## Table 5-1.Signal Description List

| Signal Name       | Function                          | Туре            | Active<br>Level | Comments |

|-------------------|-----------------------------------|-----------------|-----------------|----------|

| MSEO0 - MSEO1     | Trace Frame Control               | Output          |                 |          |

| EVTI_N            | Event In                          | Output          | Low             |          |

| EVTO_N            | Event Out                         | Output          | Low             |          |

|                   | Power Manage                      | er - PM         |                 |          |

| GCLK0 - GCLK3     | Generic Clock Pins                | Output          |                 |          |

| RESET_N           | Reset Pin                         | Input           | Low             |          |

|                   | Real Time Coun                    | ter - RTC       |                 |          |

| RTC_CLOCK         | RTC clock                         | Output          |                 |          |

|                   | Watchdog Time                     | er - WDT        |                 | 1        |

| WDTEXT            | External Watchdog Pin             | Output          |                 |          |

|                   | External Interrupt Co             | ontroller - EIC |                 | 1        |

| EXTINT0 - EXTINT7 | External Interrupt Pins           | Input           |                 |          |

| KPS0 - KPS7       | Keypad Scan Pins                  | Output          |                 |          |

| NMI_N             | Non-Maskable Interrupt Pin        | Input           | Low             |          |

|                   | Ethernet MAC                      | - MACB          |                 |          |

| COL               | Collision Detect                  | Input           |                 |          |

| CRS               | Carrier Sense and Data Valid      | Input           |                 |          |

| MDC               | Management Data Clock             | Output          |                 |          |

| MDIO              | Management Data Input/Output      | I/O             |                 |          |

| RXD0 - RXD3       | Receive Data                      | Input           |                 |          |

| RX_CLK            | Receive Clock                     | Input           |                 |          |

| RX_DV             | Receive Data Valid                | Input           |                 |          |

| RX_ER             | Receive Coding Error              | Input           |                 |          |

| SPEED             | Speed                             |                 |                 |          |

| TXD0 - TXD3       | Transmit Data                     | Output          |                 |          |

| TX_CLK            | Transmit Clock or Reference Clock | Output          |                 |          |

| TX_EN             | Transmit Enable                   | Output          |                 |          |

| TX_ER             | Transmit Coding Error             | Output          |                 |          |

## Table 5-1.Signal Description List

| Signal Name                   | Function                                 | Туре                | Active<br>Level | Comments |  |

|-------------------------------|------------------------------------------|---------------------|-----------------|----------|--|

| External Bus Interface - HEBI |                                          |                     |                 |          |  |

| ADDR0 - ADDR23                | Address Bus                              | Output              |                 |          |  |

| CAS                           | Column Signal                            | Output              | Low             |          |  |

| DATA0 - DATA15                | Data Bus                                 | I/O                 |                 |          |  |

| NCS0 - NCS3                   | Chip Select                              | Output              | Low             |          |  |

| NRD                           | Read Signal                              | Output              | Low             |          |  |

| NWAIT                         | External Wait Signal                     | Input               | Low             |          |  |

| NWE0                          | Write Enable 0                           | Output              | Low             |          |  |

| NWE1                          | Write Enable 1                           | Output              | Low             |          |  |

| NWE3                          | Write Enable 3                           | Output              | Low             |          |  |

| RAS                           | Row Signal                               | Output              | Low             |          |  |

| SDA10                         | SDRAM Address 10 Line                    | Output              |                 |          |  |

| SDCK                          | SDRAM Clock                              | Output              |                 |          |  |

| SDCKE                         | SDRAM Clock Enable                       | Output              |                 |          |  |

| SDCS0                         | SDRAM Chip Select                        | Output              | Low             |          |  |

| SDWE                          | SDRAM Write Enable                       | Output              | Low             |          |  |

|                               | General Purpose Input/Ou                 | tput 2 - GPIOA, GPI | OB, GPIOC       |          |  |

| P0 - P31                      | Parallel I/O Controller GPIOA            | I/O                 |                 |          |  |

| P0 - P31                      | Parallel I/O Controller GPIOB            | I/O                 |                 |          |  |

| P0 - P5                       | Parallel I/O Controller GPIOC            | I/O                 |                 |          |  |

| P0 - P31                      | Parallel I/O Controller GPIOX            | I/O                 |                 |          |  |

|                               | Serial Peripheral Interface - SPI0, SPI1 |                     |                 |          |  |

| MISO                          | Master In Slave Out                      | I/O                 |                 |          |  |

| MOSI                          | Master Out Slave In                      | I/O                 |                 |          |  |

| NPCS0 - NPCS3                 | SPI Peripheral Chip Select               | I/O                 | Low             |          |  |

| SCK                           | Clock                                    | Output              |                 |          |  |

|                               | Synchronous Serial Controller - SSC      |                     |                 |          |  |

| RX_CLOCK                      | SSC Receive Clock                        | I/O                 |                 |          |  |

## Table 6-1.TQFP100 Package Pinout

| 23 | PA02 |

|----|------|

| 24 | PA03 |

| 25 | PA04 |

| 48 | DM  |  |  |  |

|----|-----|--|--|--|

| 49 | DP  |  |  |  |

| 50 | GND |  |  |  |

| 73 | PB05 |

|----|------|

| 74 | PB06 |

| 75 | PB07 |

|    |      |

| 98  | PB17 |

|-----|------|

| 99  | PB18 |

| 100 | PB19 |

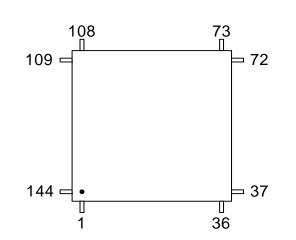

## Figure 6-2. LQFP144 Pinout

## Table 6-2.VQFP144 Package Pinout

| 1  | PX00   |

|----|--------|

| 2  | PX01   |

| 3  | PB20   |

| 4  | PX02   |

| 5  | PB21   |

| 6  | PB22   |

| 7  | VDDIO  |

| 8  | GND    |

| 9  | PB23   |

| 10 | PX03   |

| 11 | PB24   |

| 12 | PX04   |

| 13 | PB25   |

| 14 | PB26   |

| 15 | PB27   |

| 16 | VDDOUT |

| 17 | VDDIN  |

| 18 | GND    |

| 19 | PB28   |

| 20 | PB29   |

| 21 | PB30   |

| erino | ut      |

|-------|---------|

| 37    | GND     |

| 38    | PX10    |

| 39    | PA05    |

| 40    | PX11    |

| 41    | PA06    |

| 42    | PX12    |

| 43    | PA07    |

| 44    | PX13    |

| 45    | PA08    |

| 46    | PX14    |

| 47    | PA09    |

| 48    | PA10    |

| 49    | N/C     |

| 50    | PA11    |

| 51    | VDDCORE |

| 52    | GND     |

| 53    | PA12    |

| 54    | PA13    |

| 55    | VDDCORE |

| 56    | PA14    |

| 57    | PA15    |

|       |         |

| 73 | PA21   |

|----|--------|

| 74 | PA22   |

| 75 | PA23   |

| 76 | PA24   |

| 77 | PA25   |

| 78 | PA26   |

| 79 | PA27   |

| 80 | PA28   |

| 81 | VDDANA |

| 82 | ADVREF |

| 83 | GNDANA |

| 84 | VDDPLL |

| 85 | PC00   |

| 86 | PC01   |

| 87 | PX20   |

| 88 | PB00   |

| 89 | PX21   |

| 90 | PB01   |

| 91 | PX22   |

| 92 | VDDIO  |

| 93 | VDDIO  |

| 109 | GND   |

|-----|-------|

| 110 | PX30  |

| 111 | PB08  |

| 112 | PX31  |

| 113 | PB09  |

| 114 | PX32  |

| 115 | PB10  |

| 116 | VDDIO |

| 117 | GND   |

| 118 | PX33  |

| 119 | PB11  |

| 120 | PX34  |

| 121 | PB12  |

| 122 | PA29  |

| 123 | PA30  |

| 124 | PC02  |

| 125 | PC03  |

| 126 | PB13  |

| 127 | PB14  |

| 128 | TMS   |

| 129 | TCK   |

# 10. Peripherals

## 10.1 Peripheral address map

Table 10-1.

Peripheral Address Mapping

| Address    |         | Peripheral Name                                                     | Bus |

|------------|---------|---------------------------------------------------------------------|-----|

|            |         | 1                                                                   |     |

| 0xE0000000 | USBB    | USBB Slave Interface - USBB                                         | HSB |

| 0xFFFE0000 | USBB    | USBB Configuration Interface - USBB                                 | PBB |

| 0xFFFE1000 | HMATRIX | HMATRIX Configuration Interface - HMATRIX                           | PBB |

| 0xFFFE1400 | FLASHC  | Flash Controller - FLASHC                                           | PBB |

| 0xFFFE1800 | MACB    | MACB Configuration Interface - MACB                                 | PBB |

| 0xFFFE1C00 | SMC     | Static Memory Controller Configuration Interface -                  | PBB |

| 0xFFFE2000 | SDRAMC  | SDRAM Controller Configuration Interface -<br>SDRAMC                | PBB |

| 0xFFFF0000 | PDCA    | Peripheral DMA Interface - PDCA                                     | PBA |

| 0xFFFF0800 | INTC    | Interrupt Controller Interface - INTC                               | PBA |

| 0xFFFF0C00 | РМ      | Power Manager - PM                                                  | PBA |

| 0xFFFF0D00 | RTC     | Real Time Clock - RTC                                               | PBA |

| 0xFFFF0D30 | WDT     | WatchDog Timer - WDT                                                | PBA |

| 0xFFFF0D80 | EIC     | External Interrupt Controller - EIC                                 | PBA |

| 0xFFFF1000 | GPIO    | General Purpose IO Controller - GPIO                                | PBA |

| 0xFFFF1400 | USART0  | Universal Synchronous Asynchronous Receiver<br>Transmitter - USART0 | PBA |

| 0xFFFF1800 | USART1  | Universal Synchronous Asynchronous Receiver<br>Transmitter - USART1 | PBA |

| l          |         | 1                                                                   |     |

| Port | Register                             | Mode        | Local Bus<br>Address | Access     |

|------|--------------------------------------|-------------|----------------------|------------|

| 3    | Output Driver Enable Register (ODER) | WRITE       | 0x4000_0340          | Write-only |

|      |                                      | SET         | 0x4000_0344          | Write-only |

|      |                                      | CLEAR       | 0x4000_0348          | Write-only |

|      |                                      | TOGGLE      | 0x4000_034C          | Write-only |

|      | WRITE                                | 0x4000_0350 | Write-only           |            |

|      | SET                                  | 0x4000_0354 | Write-only           |            |

|      |                                      | CLEAR       | 0x4000_0358          | Write-only |

|      |                                      | TOGGLE      | 0x4000_035C          | Write-only |

|      | Pin Value Register (PVR)             | -           | 0x4000_0360          | Read-only  |

Table 10-2.

Local bus mapped GPIO registers

## 10.3 Interrupt Request Signal Map

The various modules may output Interrupt request signals. These signals are routed to the Interrupt Controller (INTC), described in a later chapter. The Interrupt Controller supports up to 64 groups of interrupt requests. Each group can have up to 32 interrupt request signals. All interrupt signals in the same group share the same autovector address and priority level. Refer to the documentation for the individual submodules for a description of the semantics of the different interrupt requests.

The interrupt request signals are connected to the INTC as follows.

| Group                                                                                                                                                                                                                                                                                                 | Line | Module                                          | Signal              |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------------------------------------------------|---------------------|

| 0                                                                                                                                                                                                                                                                                                     | 0    | AVR32 UC CPU with optional MPU and optional OCD | SYSBLOCK<br>COMPARE |

|                                                                                                                                                                                                                                                                                                       | 0    | External Interrupt Controller                   | EIC 0               |

|                                                                                                                                                                                                                                                                                                       | 1    | External Interrupt Controller                   | EIC 1               |

|                                                                                                                                                                                                                                                                                                       | 2    | External Interrupt Controller                   | EIC 2               |

| 3       External Interrupt Controller         4       External Interrupt Controller         1       5       External Interrupt Controller         6       External Interrupt Controller         7       External Interrupt Controller         8       Real Time Counter         9       Power Manager |      | External Interrupt Controller                   | EIC 3               |

|                                                                                                                                                                                                                                                                                                       |      | EIC 4                                           |                     |

|                                                                                                                                                                                                                                                                                                       |      | External Interrupt Controller                   | EIC 5               |

|                                                                                                                                                                                                                                                                                                       |      | External Interrupt Controller                   | EIC 6               |

|                                                                                                                                                                                                                                                                                                       |      | External Interrupt Controller                   | EIC 7               |

|                                                                                                                                                                                                                                                                                                       |      | Real Time Counter                               | RTC                 |

|                                                                                                                                                                                                                                                                                                       |      | PM                                              |                     |

|                                                                                                                                                                                                                                                                                                       | 10   | Frequency Meter                                 | FREQM               |

Table 10-3.

Interrupt Request Signal Map

Table 10-9.

GPIO Controller Function Multiplexing

| Table 10-9. | GFIO COIII |      | in manupicking | 1                      |                 |                |

|-------------|------------|------|----------------|------------------------|-----------------|----------------|

| 41          | 58         | PA16 | GPIO 16        | SSC - TX_DATA          | SPI1 - MOSI     | EBI - ADDR[21] |

| 42          | 60         | PA17 | GPIO 17        | SSC - RX_DATA          | SPI1 - MISO     | EBI - ADDR[22] |

| 43          | 62         | PA18 | GPIO 18        | SSC - RX_CLOCK         | SPI1 - NPCS[1]  | MACB - WOL     |

| 44          | 64         | PA19 | GPIO 19        | SSC -<br>RX_FRAME_SYNC | SPI1 - NPCS[2]  |                |

| 45          | 66         | PA20 | GPIO 20        | EIM - EXTINT[8]        | SPI1 - NPCS[3]  |                |

| 51          | 73         | PA21 | GPIO 21        | ADC - AD[0]            | EIM - EXTINT[0] | USB - USB_ID   |

| 52          | 74         | PA22 | GPIO 22        | ADC - AD[1]            | EIM - EXTINT[1] | USB - USB_VBOF |

| 53          | 75         | PA23 | GPIO 23        | ADC - AD[2]            | EIM - EXTINT[2] | DAC - DATA[1]  |

| 54          | 76         | PA24 | GPIO 24        | ADC - AD[3]            | EIM - EXTINT[3] | DAC - DATAN[1] |

| 55          | 77         | PA25 | GPIO 25        | ADC - AD[4]            | EIM - SCAN[0]   | EBI - NCS[0]   |

| 56          | 78         | PA26 | GPIO 26        | ADC - AD[5]            | EIM - SCAN[1]   | EBI - ADDR[20] |

| 57          | 79         | PA27 | GPIO 27        | ADC - AD[6]            | EIM - SCAN[2]   | EBI - ADDR[21] |

| 58          | 80         | PA28 | GPIO 28        | ADC - AD[7]            | EIM - SCAN[3]   | EBI - ADDR[22] |

| 83          | 122        | PA29 | GPIO 29        | TWI - SDA              | USART2 - RTS    |                |

| 84          | 123        | PA30 | GPIO 30        | TWI - SCL              | USART2 - CTS    |                |

| 65          | 88         | PB00 | GPIO 32        | MACB - TX_CLK          | USART2 - RTS    | USART3 - RTS   |

| 66          | 90         | PB01 | GPIO 33        | MACB - TX_EN           | USART2 - CTS    | USART3 - CTS   |

| 70          | 96         | PB02 | GPIO 34        | MACB - TXD[0]          | DAC - DATA[0]   |                |

| 71          | 98         | PB03 | GPIO 35        | MACB - TXD[1]          | DAC - DATAN[0]  |                |

| 72          | 100        | PB04 | GPIO 36        | MACB - CRS             | USART3 - CLK    | EBI - NCS[3]   |

| 73          | 102        | PB05 | GPIO 37        | MACB - RXD[0]          | DAC - DATA[1]   |                |

| 74          | 104        | PB06 | GPIO 38        | MACB - RXD[1]          | DAC - DATAN[1]  |                |

| 75          | 106        | PB07 | GPIO 39        | MACB - RX_ER           |                 |                |

| 76          | 111        | PB08 | GPIO 40        | MACB - MDC             |                 |                |

| 77          | 113        | PB09 | GPIO 41        | MACB - MDIO            |                 |                |

| 78          | 115        | PB10 | GPIO 42        | MACB - TXD[2]          | USART3 - RXD    | EBI - SDCK     |

| 81          | 119        | PB11 | GPIO 43        | MACB - TXD[3]          | USART3 - TXD    | EBI - SDCKE    |

| 82          | 121        | PB12 | GPIO 44        | MACB - TX_ER           | TC - CLK0       | EBI - RAS      |

| 87          | 126        | PB13 | GPIO 45        | MACB - RXD[2]          | TC - CLK1       | EBI - CAS      |

| 88          | 127        | PB14 | GPIO 46        | MACB - RXD[3]          | TC - CLK2       | EBI - SDWE     |

| 95          | 134        | PB15 | GPIO 47        | MACB - RX_DV           |                 |                |

| 96          | 136        | PB16 | GPIO 48        | MACB - COL             | USB - USB_ID    | EBI - SDA10    |

| 98          | 139        | PB17 | GPIO 49        | MACB - RX_CLK          | USB - USB_VBOF  | EBI - ADDR[23] |

| 99          | 141        | PB18 | GPIO 50        | MACB - SPEED           | ADC - TRIGGER   | PWM - PWM[6]   |

| 100         | 143        | PB19 | GPIO 51        | PWM - PWM[0]           | PM - GCLK[0]    | EIM - SCAN[4]  |

| 1           | 3          | PB20 | GPIO 52        | PWM - PWM[1]           | PM - GCLK[1]    | EIM - SCAN[5]  |

| 2           | 5          | PB21 | GPIO 53        | PWM - PWM[2]           | PM - GCLK[2]    | EIM - SCAN[6]  |

| 3           | 6          | PB22 | GPIO 54        | PWM - PWM[3]           | PM - GCLK[3]    | EIM - SCAN[7]  |

|             | 9          | PB23 | GPIO 55        | TC - A0                | USART1 - DCD    |                |

## 10.10 GPIO

The GPIO open drain feature (GPIO ODMER register (Open Drain Mode Enable Register)) is not available for this device.

## **10.11** Peripheral overview

## 10.11.1 External Bus Interface

- Optimized for Application Memory Space support

- Integrates Two External Memory Controllers:

- Static Memory Controller

- SDRAM Controller

- Optimized External Bus:

- 16-bit Data Bus

- 24-bit Address Bus, Up to 16-Mbytes Addressable

- Optimized pin multiplexing to reduce latencies on External Memories

- 4 SRAM Chip Selects, 1SDRAM Chip Select:

- Static Memory Controller on NCS0

- SDRAM Controller or Static Memory Controller on NCS1

- Static Memory Controller on NCS2

- Static Memory Controller on NCS3

## 10.11.2 Static Memory Controller

- 4 Chip Selects Available

- 64-Mbyte Address Space per Chip Select

- 8-, 16-bit Data Bus

- Word, Halfword, Byte Transfers

- Byte Write or Byte Select Lines

- Programmable Setup, Pulse And Hold Time for Read Signals per Chip Select

- Programmable Setup, Pulse And Hold Time for Write Signals per Chip Select

- Programmable Data Float Time per Chip Select

- Compliant with LCD Module

- External Wait Request

- Automatic Switch to Slow Clock Mode

- Asynchronous Read in Page Mode Supported: Page Size Ranges from 4 to 32 Bytes

## 10.11.3 SDRAM Controller

- Numerous Configurations Supported

- 2K, 4K, 8K Row Address Memory Parts

- SDRAM with Two or Four Internal Banks

- SDRAM with 16-bit Data Path

- Programming Facilities

- Word, Half-word, Byte Access

- Automatic Page Break When Memory Boundary Has Been Reached

- Multibank Ping-pong Access

- Timing Parameters Specified by Software

- Automatic Refresh Operation, Refresh Rate is Programmable

- Energy-saving Capabilities

- Self-refresh, Power-down and Deep Power Modes Supported

## **12. Electrical Characteristics**

## 12.1 Absolute Maximum Ratings\*

| Operating Temperature40.C to +85.C                                                                          |

|-------------------------------------------------------------------------------------------------------------|

| Storage Temperature60°C to +150°C                                                                           |

| Voltage on Input Pin<br>with respect to Ground except for PC00, PC01, PC02, PC03,<br>PC04, PC050.3V to 5.5V |

| Voltage on Input Pin<br>with respect to Ground for PC00, PC01, PC02, PC03, PC04,<br>PC050.3V to 3.6V        |

|                                                                                                             |

| Maximum Operating Voltage (VDDCORE, VDDPLL) 1.95V                                                           |

| Maximum Operating Voltage (VDDIO, VDDIN, VDDANA).3.6V                                                       |

| Total DC Output Current on all I/O Pin<br>for TQFP100 package                                               |

\*NOTICE: Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

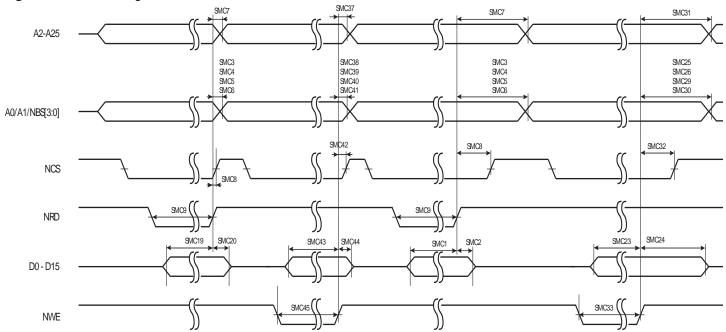

## 12.9 EBI Timings

These timings are given for worst case process, T = 85·C, VDDCORE = 1.65V, VDDIO = 3V and 40 pF load capacitance.

| Symbol                  | Parameter                      | Max <sup>(1)</sup>      | Units |

|-------------------------|--------------------------------|-------------------------|-------|

| 1/(t <sub>CPSMC</sub> ) | SMC Controller Clock Frequency | 1/(t <sub>cpcpu</sub> ) | MHz   |

Note: 1. The maximum frequency of the SMC interface is the same as the max frequency for the HSB.

## Table 12-23. SMC Read Signals with Hold Settings

| Symbol            | Parameter                                  | Min                                                             | Units |

|-------------------|--------------------------------------------|-----------------------------------------------------------------|-------|

|                   | NRD C                                      | ontrolled (READ_MODE = 1)                                       |       |

| SMC <sub>1</sub>  | Data Setup before NRD High                 | 12                                                              |       |

| SMC <sub>2</sub>  | Data Hold after NRD High                   | 0                                                               |       |

| SMC <sub>3</sub>  | NRD High to NBS0/A0 Change <sup>(1)</sup>  | nrd hold length * t <sub>CPSMC</sub> - 1.3                      |       |

| SMC <sub>4</sub>  | NRD High to NBS1 Change <sup>(1)</sup>     | nrd hold length * t <sub>CPSMC</sub> - 1.3                      |       |

| SMC <sub>5</sub>  | NRD High to NBS2/A1 Change <sup>(1)</sup>  | nrd hold length * t <sub>CPSMC</sub> - 1.3                      | ns    |

| SMC <sub>6</sub>  | NRD High to NBS3 Change <sup>(1)</sup>     | nrd hold length * t <sub>CPSMC</sub> - 1.3                      |       |

| SMC <sub>7</sub>  | NRD High to A2 - A25 Change <sup>(1)</sup> | nrd hold length * t <sub>CPSMC</sub> - 1.3                      |       |

| SMC <sub>8</sub>  | NRD High to NCS Inactive <sup>(1)</sup>    | (nrd hold length - ncs rd hold length) * $t_{CPSMC}$ - 2.3      |       |

| SMC <sub>9</sub>  | NRD Pulse Width                            | nrd pulse length * t <sub>CPSMC</sub> - 1.4                     |       |

|                   | NRD C                                      | ontrolled (READ_MODE = 0)                                       | I     |

| SMC <sub>10</sub> | Data Setup before NCS High                 | 11.5                                                            |       |

| SMC <sub>11</sub> | Data Hold after NCS High                   | 0                                                               |       |

| SMC <sub>12</sub> | NCS High to NBS0/A0 Change <sup>(1)</sup>  | ncs rd hold length * t <sub>CPSMC</sub> - 2.3                   |       |

| SMC <sub>13</sub> | NCS High to NBS0/A0 Change <sup>(1)</sup>  | ncs rd hold length * t <sub>CPSMC</sub> - 2.3                   |       |

| SMC <sub>14</sub> | NCS High to NBS2/A1 Change <sup>(1)</sup>  | ncs rd hold length * t <sub>CPSMC</sub> - 2.3                   | ns    |

| SMC <sub>15</sub> | NCS High to NBS3 Change <sup>(1)</sup>     | ncs rd hold length * t <sub>CPSMC</sub> - 2.3                   |       |

| SMC <sub>16</sub> | NCS High to A2 - A25 Change <sup>(1)</sup> | ncs rd hold length * t <sub>CPSMC</sub> - 4                     |       |

| SMC <sub>17</sub> | NCS High to NRD Inactive <sup>(1)</sup>    | ncs rd hold length - nrd hold length)* t <sub>CPSMC</sub> - 1.3 |       |

| SMC <sub>18</sub> | NCS Pulse Width                            | ncs rd pulse length * t <sub>CPSMC</sub> - 3.6                  |       |

Note: 1. hold length = total cycle duration - setup duration - pulse duration. "hold length" is for "ncs rd hold length" or "nrd hold length".

## Figure 12-3. SMC Signals for NRD and NRW Controlled Accesses.

## 12.9.1 SDRAM Signals

These timings are given for 10 pF load on SDCK and 40 pF on other signals.

| Table 12-27. | SDRAM Clock Signal. |

|--------------|---------------------|

|--------------|---------------------|

| Symbol                   | Parameter                        | Max <sup>(1)</sup>      | Units |

|--------------------------|----------------------------------|-------------------------|-------|

| 1/(t <sub>CPSDCK</sub> ) | SDRAM Controller Clock Frequency | 1/(t <sub>cpcpu</sub> ) | MHz   |

Note: 1. The maximum frequency of the SDRAMC interface is the same as the max frequency for the HSB.

## Table 12-28. SDRAM Clock Signal.

| Symbol               | Parameter                            | Min | Units |

|----------------------|--------------------------------------|-----|-------|

| SDRAMC <sub>1</sub>  | SDCKE High before SDCK Rising Edge   | 7.4 | ns    |

| SDRAMC <sub>2</sub>  | SDCKE Low after SDCK Rising Edge     | 3.2 |       |

| SDRAMC <sub>3</sub>  | SDCKE Low before SDCK Rising Edge    | 7   |       |

| SDRAMC <sub>4</sub>  | SDCKE High after SDCK Rising Edge    | 2.9 |       |

| SDRAMC <sub>5</sub>  | SDCS Low before SDCK Rising Edge     | 7.5 |       |

| SDRAMC <sub>6</sub>  | SDCS High after SDCK Rising Edge     | 1.6 |       |

| SDRAMC <sub>7</sub>  | RAS Low before SDCK Rising Edge      | 7.2 |       |

| SDRAMC <sub>8</sub>  | RAS High after SDCK Rising Edge      | 2.3 |       |

| SDRAMC <sub>9</sub>  | SDA10 Change before SDCK Rising Edge | 7.6 |       |

| SDRAMC <sub>10</sub> | SDA10 Change after SDCK Rising Edge  | 1.9 |       |

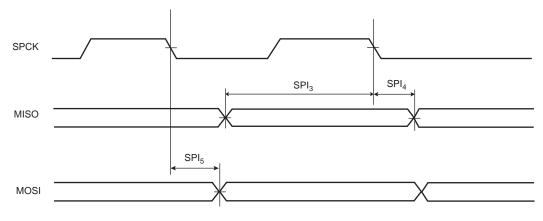

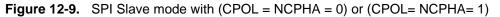

Figure 12-7. SPI Master mode with (CPOL=0 and NCPHA=1) or (CPOL=1 and NCPHA=0)

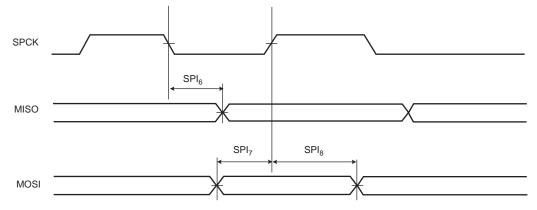

Figure 12-8. SPI Slave mode with (CPOL=0 and NCPHA=1) or (CPOL=1 and NCPHA=0)

For LDM with PC in the register list: the instruction behaves as if the ++ field is always set, ie the pointer is always updated. This happens even if the ++ field is cleared. Specifically, the increment of the pointer is done in parallel with the testing of R12. **Fix/Workaround** None.

When multiple CS are in use, if one of the baudrate equals 1, the other must also equal 1 if CPOL=1 and CPHA=0.

# 4. SPI Glitch on RXREADY flag in slave mode when enabling the SPI or during the first transfer

In slave mode, the SPI can generate a false RXREADY signal during enabling of the SPI or during the first transfer.

## **Fix/Workaround**

- 1. Set slave mode, set required CPOL/CPHA.

- 2. Enable SPI.

- 3. Set the polarity CPOL of the line in the opposite value of the required one.

- 4. Set the polarity CPOL to the required one.

- 5. Read the RXHOLDING register.

Transfers can now befin and RXREADY will now behave as expected.

## 5. SPI Disable does not work in Slave mode Fix/workaround

Read the last received data then perform a Software reset.

## 15.2.4 Power Manager

| 1. | If the BOD level is higher than VDDCORE, the part is constantly under reset                |

|----|--------------------------------------------------------------------------------------------|

|    | If the BOD level is set to a value higher than VDDCORE and enabled by fuses, the part will |

|    | be in constant reset.                                                                      |

## Fix/Workaround

Apply an external voltage on VDDCORE that is higher than the BOD level and is lower than VDDCORE max and disable the BOD.

## 15.2.5 PDCA

1. Wrong PDCA behavior when using two PDCA channels with the same PID. Fix/Workaround

The same PID should not be assigned to more than one channel.

- 15.2.6 TWI

- 1. The TWI RXRDY flag in SR register is not reset when a software reset is performed. Fix/Workaround

After a Software Reset, the register TWI RHR must be read.

## 15.2.7 SDRAMC

1. Code execution from external SDRAM does not work Code execution from SDRAM does not work.

## Fix/Workaround

Do not run code from SDRAM.

## 15.2.8 GPIO

PA29 (TWI SDA) and PA30 (TWI SCL) GPIO VIH (input high voltage) is 3.6V max instead of 5V tolerant The following GPIOs are not 5V tolerant : PA29 and PA30. Fix/Workaround

None.

#### 15.2.9 USART

ISO7816 info register US\_NER cannot be read The NER register always returns zero.

Fix/Workaround None

## 15.2.10 Processor and Architecture

1. LDM instruction with PC in the register list and without ++ increments Rp For LDM with PC in the register list: the instruction behaves as if the ++ field is always set, ie the pointer is always updated. This happens even if the ++ field is cleared. Specifically, the increment of the pointer is done in parallel with the testing of R12.

Fix/Workaround

None.

#### 2. RETE instruction does not clear SREG[L] from interrupts.

The RETE instruction clears  $\mbox{SREG}[L]$  as expected from exceptions.  $\mbox{Fix/Workaround}$

When using the STCOND instruction, clear SREG[L] in the stacked value of SR before returning from interrupts with RETE.

#### 3. Exceptions when system stack is protected by MPU

RETS behaves incorrectly when MPU is enabled and MPU is configured so that system stack is not readable in unprivileged mode.

## **Fix/Woraround**

Workaround 1: Make system stack readable in unprivileged mode, or

Workaround 2: Return from supervisor mode using rete instead of rets. This requires :

1. Changing the mode bits from 001b to 110b before issuing the instruction. Updating the mode bits to the desired value must be done using a single mtsr instruction so it is done atomically. Even if this step is described in general as not safe in the UC technical reference guide, it is safe in this very specific case.

2. Execute the RETE instruction.

# AT32UC3A

specific case. 2. Execute the RETE instruction.

## 15.5.4 USB

## 1. USB No end of host reset signaled upon disconnection

In host mode, in case of an unexpected device disconnection whereas a usb reset is being sent by the usb controller, the UHCON.RESET bit may not been cleared by the hardware at the end of the reset.

## **Fix/Workaround**

A software workaround consists in testing (by polling or interrupt) the disconnection (UHINT.DDISCI == 1) while waiting for the end of reset (UHCON.RESET == 0) to avoid being stuck.

## 2. USBFSM and UHADDR1/2/3 registers are not available.

Do not use USBFSM register.

## Fix/Workaround

Do not use USBFSM register and use HCON[6:0] field instead for all the pipes.

#### 15.5.5 Processor and Architecture

#### 1. Incorrect Processor ID

The processor ID reads 0x01 and not 0x02 as it should.

## **Fix/Workaround**

None.

#### 2. Bus error should be masked in Debug mode

If a bus error occurs during debug mode, the processor will not respond to debug commands through the DINST register.

#### Fix/Workaround

A reset of the device will make the CPU respond to debug commands again.

# 3. Read Modify Write (RMW) instructions on data outside the internal RAM does not work.

Read Modify Write (RMW) instructions on data outside the internal RAM does not work.

## Fix/Workaround

Do not perform RMW instructions on data outside the internal RAM.

## 4. CRC calculation of a locked device will calculate CRC for 512 kB of flash memory, even though the part has less flash. Fix/Workaround

The flash address space is wrapping, so it is possible to use the CRC value by calculating CRC of the flash content concatenated with itself N times. Where N is 512 kB/flash size.

## 5. Need two NOPs instruction after instructions masking interrupts

The instructions following in the pipeline the instruction masking the interrupt through SR may behave abnormally.

## **Fix/Workaround**

Place two NOPs instructions after each SSRF or MTSR instruction setting IxM or GM in SR.

If the ADC sleep mode is activated when the ADC is idle the ADC will not enter sleep mode before after the next AD conversion.

## Fix/Workaround

Activate the sleep mode in the mode register and then perform an AD conversion.

#### 15.5.11 ABDAC

Audio Bitstream DAC is not functional. Fix/Workaround

Do not use the ABDAC on revE.

#### 15.5.12 FLASHC

- The address of Flash General Purpose Fuse Register Low (FGPFRLO) is 0xFFFE140C on revE instead of 0xFFFE1410. Fix/Workaround None.

- The command Quick Page Read User Page(QPRUP) is not functional. Fix/Workaround None.

- 3. PAGEN Semantic Field for Program GP Fuse Byte is WriteData[7:0], ByteAddress[1:0] on revision E instead of WriteData[7:0], ByteAddress[2:0]. Fix/Workaround

None.

4. On AT32UC3A0512 and AT32UC3A1512, corrupted read in flash after FLASHC WP, EP, EA, WUP, EUP commands may happen

- After a FLASHC Write Page (WP) or Erase Page (EP) command applied to a page in a given half of the flash (first or last 256 kB of flash), reading (data read or code fetch) the other half of the flash may fail. This may lead to an exception or to other errors derived from this corrupted read access.

After a FLASHC Erase All (EA) command, reading (data read or code fetch) the flash may fail. This may lead to an exception or to other errors derived from this corrupted read access.

After a FLASHC Write User Page (WUP) or Erase User Page (EUP) command, reading (data read or code fetch) the second half (last 256 kB) of the flash may fail. This may lead to an exception or to other errors derived from this corrupted read access.

## Fix/Workaround

Flashc WP, EP, EA, WUP, EUP commands: these commands must be issued from RAM or through the EBI. After these commands, read twice one flash page initialized to 00h in each half part of the flash.

15.5.13 RTC

1. Writes to control (CTRL), top (TOP) and value (VAL) in the RTC are discarded if the RTC peripheral bus clock (PBA) is divided by a factor of four or more relative to the HSB clock.

#### Fix/Workaround

Do not write to the RTC registers using the peripheral bus clock (PBA) divided by a factor of four or more relative to the HSB clock.

## 16. Datasheet Revision History

Please note that the referring page numbers in this section are referred to this document. The referring revision in this section are referring to the document revision.

## 16.1 Rev. K - 01/12

- 1. Update "Errata" on page 70.

- 2. Update eletrical characteristic in "DC Characteristics" on page 41.

- 3. Remove Preliminary from first page.

## 16.2 Rev. G - 01/09

- 1. Update "Errata" on page 70.

- 2. Update GPIO eletrical characteristic in "DC Characteristics" on page 41.

## 16.3 Rev. F - 08/08

- 1. Add revision J to "Errata" on page 70.

- 2. Update DMIPS number in "Features" on page 1.

- 16.4 Rev. E 04/08

- 1. Open Drain Mode removed from "General-Purpose Input/Output Controller (GPIO)" on page 151.

## 16.5 Rev. D - 04/08

- 1. Updated "Signal Description List" on page 8. Removed RXDN and TXDN from USART section.

- 2. Updated "Errata" on page 70. Rev G replaced by rev H.

# AT32UC3A