Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                                     |

|----------------------------|-----------------------------------------------------------------------------------------------------|

| Product Status             | Active                                                                                              |

| Core Processor             | ARM® Cortex®-M4                                                                                     |

| Core Size                  | 32-Bit Single-Core                                                                                  |

| Speed                      | 80MHz                                                                                               |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, IrDA, LINbus, MMC/SD, QSPI, SAI, SPI, SWPMI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, LCD, PWM, WDT                                                          |

| Number of I/O              | 52                                                                                                  |

| Program Memory Size        | 1MB (1M x 8)                                                                                        |

| Program Memory Type        | FLASH                                                                                               |

| EEPROM Size                | -                                                                                                   |

| RAM Size                   | 320K x 8                                                                                            |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.6V                                                                                        |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                                               |

| Oscillator Type            | Internal                                                                                            |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                                   |

| Mounting Type              | Surface Mount                                                                                       |

| Package / Case             | 64-LQFP                                                                                             |

| Supplier Device Package    | 64-LQFP (10x10)                                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l4a6rgt6                               |

Figure 14. STM32L4A6Vx WLCSP100 pinout<sup>(1)</sup>

|   |        |      | J    |      |      |           |       |       |            |                    |

|---|--------|------|------|------|------|-----------|-------|-------|------------|--------------------|

|   | 1      | 2    | 3    | 4    | 5    | 6         | 7     | 8     | 9          | 10                 |

| Α | VDDUSB | PA15 | PD1  | VDD  | PG10 | VDDIO2    | PB6   | PB9   | vss        | VDD                |

| В | vss    | PA14 | PD0  | PD4  | PG9  | PG12      | PB5   | PB8   | PE2        | PE3                |

| С | PA12   | PA13 | PC11 | PC12 | PD7  | PB3       | PB4   | PE4   | PC13       | VBAT               |

| D | PA11   | PA10 | PA9  | PC10 | PD6  | PG11      | PB7   | PE5   | vss        | PC14-<br>OSC32_IN  |

| E | PC8    | PC9  | PA8  | PD2  | PD5  | рнз-воото | PE6   | NRST  | VDD        | PC15-<br>OSC32_OUT |

| F | VDD    | PC6  | PC7  | PD15 | PB2  | PA4       | PC3   | PC1   | PC0        | PH0-OSC_IN         |

| G | PD10   | PD9  | PD14 | PE13 | PE12 | PA5       | VREF+ | VREF- | PA0        | PH1-<br>OSC_OUT    |

| н | PB15   | PB14 | PD8  | PE15 | PE10 | PC4       | PA2   | PA1   | VSSA/VREF- | PC2                |

| J | PB12   | PB13 | PB11 | PE14 | PE9  | PB0       | PA7   | VDD   | PA3        | VDDA               |

| к | VDD    | vss  | PB10 | PE11 | PE8  | PE7       | PB1   | PC5   | PA6        | vss                |

|   |        |      |      |      |      |           |       |       |            |                    |

1. The above figure shows the package top view.

Figure 15. STM32L4A6Vx, external SMPS device, WLCSP100 pinout<sup>(1)</sup>

|   |        |      |      | ., 02110 |      |        | ,         |      |                    | P C C.            |

|---|--------|------|------|----------|------|--------|-----------|------|--------------------|-------------------|

|   | 1      | 2    | 3    | 4        | 5    | 6      | 7         | 8    | 9                  | 10                |

| A | VDDUSB | PA15 | PD1  | VDD      | PG10 | VDDIO2 | PB6       | PB9  | VDD12              | VDD               |

| В | vss    | PA14 | PD0  | PD5      | PD6  | PG12   | PB7       | PB8  | vss                | PE3               |

| С | PA12   | PA13 | PC10 | PC12     | PD4  | PD7    | PB5       | PE2  | PC13               | VBAT              |

| D | PA11   | PA10 | PA9  | PC11     | PD2  | PG9    | РН3-ВООТ0 | PE6  | PC15-<br>OSC32_OUT | PC14-<br>OSC32_IN |

| E | PC8    | PC9  | PA8  | PC7      | PG11 | PB4    | PE4       | PE5  | VDD                | vss               |

| F | VDD    | PD15 | PD14 | PC6      | PB3  | PC3    | PC1       | NRST | PH1-<br>OSC_OUT    | PH0-OSC_IN        |

| G | PD10   | PD9  | PD8  | PE14     | PE13 | PA7    | PA1       | PA0  | PC2                | PC0               |

| н | PB14   | PB13 | PB15 | PE15     | PE10 | PB0    | PA4       | PA2  | VSSA/VREF-         | VREF+             |

| J | PB12   | VDD  | PB11 | PE12     | PE9  | PB2    | PA5       | VDD  | PA3                | VDDA              |

| к | VDD12  | vss  | PB10 | PE11     | PE8  | PE7    | PB1       | PC4  | PA6                | vss               |

|   |        |      |      |          |      |        |           |      |                    |                   |

1. The above figure shows the package top view.

577

DS11584 Rev 7

Table 16. Alternate function AF0 to AF7<sup>(1)</sup> (continued)

|        |      | AF0     | AF1                   | AF2          | AF3                                   | AF4                 | AF5                     | AF6                                       | AF7        |

|--------|------|---------|-----------------------|--------------|---------------------------------------|---------------------|-------------------------|-------------------------------------------|------------|

| P      | ort  | SYS_AF  | TIM1/2/5/8/<br>LPTIM1 | TIM1/2/3/4/5 | SPI2/USART2/<br>CAN2/TIM8/<br>QUADSPI | I2C1/2/3/4/<br>DCMI | SPI1/2/DCMI/<br>QUADSPI | SPI3/I2C3/<br>DFSDM/<br>COMP1/<br>QUADSPI | USART1/2/3 |

|        | PC0  | -       | LPTIM1_IN1            | I2C4_SCL     | -                                     | I2C3_SCL            | -                       | DFSDM1_<br>DATIN4                         | -          |

|        | PC1  | TRACED0 | LPTIM1_OUT            | I2C4_SDA     | SPI2_MOSI                             | I2C3_SDA            | -                       | DFSDM1_CKIN4                              | -          |

|        | PC2  | -       | LPTIM1_IN2            | -            | -                                     | -                   | SPI2_MISO               | DFSDM1_<br>CKOUT                          | -          |

|        | PC3  | -       | LPTIM1_ETR            | -            | -                                     | -                   | SPI2_MOSI               | -                                         | -          |

|        | PC4  | -       | -                     | -            | -                                     | -                   | -                       | -                                         | USART3_TX  |

|        | PC5  | -       | -                     | -            | -                                     | -                   | -                       | -                                         | USART3_RX  |

|        | PC6  | -       | -                     | TIM3_CH1     | TIM8_CH1                              | -                   | -                       | DFSDM1_CKIN3                              | -          |

|        | PC7  | -       | -                     | TIM3_CH2     | TIM8_CH2                              | -                   | -                       | DFSDM1_<br>DATIN3                         | -          |

| Port C | PC8  | -       | -                     | TIM3_CH3     | TIM8_CH3                              | -                   | -                       | -                                         | -          |

|        | PC9  | -       | TIM8_BKIN2            | TIM3_CH4     | TIM8_CH4                              | DCMI_D3             | -                       | I2C3_SDA                                  | -          |

|        | PC10 | TRACED1 | -                     | -            | -                                     | -                   | -                       | SPI3_SCK                                  | USART3_TX  |

|        | PC11 | -       | -                     | -            | -                                     | -                   | QUADSPI_BK<br>2_NCS     | SPI3_MISO                                 | USART3_RX  |

|        | PC12 | TRACED3 | -                     | -            | -                                     | -                   | -                       | SPI3_MOSI                                 | USART3_CK  |

|        | PC13 | -       | -                     | -            | -                                     | -                   | -                       | -                                         | -          |

|        | PC14 | -       | -                     | -            | -                                     | -                   | -                       | -                                         | -          |

|        | PC15 | -       | -                     | -            | -                                     | -                   | -                       | -                                         | -          |

Table 17. Alternate function AF8 to AF15<sup>(1)</sup> (continued)

|        |      | AF8                          | AF9        | AF10                             | AF11      | AF12                             | AF13                | AF14                     | AF15     |

|--------|------|------------------------------|------------|----------------------------------|-----------|----------------------------------|---------------------|--------------------------|----------|

| P      | ort  | UART4/5/<br>LPUART1/<br>CAN2 | CAN1/TSC   | CAN2/<br>OTG_FS/DCMI/<br>QUADSPI | LCD       | SDMMC/<br>COMP1/2/FM<br>C/SWPMI1 | SAI1/2              | TIM2/15/16/17/<br>LPTIM2 | EVENOUT  |

|        | PB0  | -                            | -          | QUADSPI_BK1_IO1                  | LCD_SEG5  | COMP1_OUT                        | SAI1_EXTCLK         | -                        | EVENTOUT |

|        | PB1  | LPUART1_RT<br>S_DE           | -          | QUADSPI_BK1_IO0                  | LCD_SEG6  | -                                | -                   | LPTIM2_IN1               | EVENTOUT |

|        | PB2  | -                            | -          | -                                | LCD_VLCD  | -                                | -                   | -                        | EVENTOUT |

|        | PB3  | -                            | -          | OTG_FS_CRS_SYNC                  | LCD_SEG7  | -                                | SAI1_SCK_B          | -                        | EVENTOUT |

|        | PB4  | UART5_RTS_<br>DE             | TSC_G2_IO1 | DCMI_D12                         | LCD_SEG8  | -                                | SAI1_MCLK_B         | TIM17_BKIN               | EVENTOUT |

|        | PB5  | UART5_CTS                    | TSC_G2_IO2 | DCMI_D10                         | LCD_SEG9  | COMP2_OUT                        | SAI1_SD_B           | TIM16_BKIN               | EVENTOUT |

|        | PB6  | CAN2_TX TSC_G2_IO3           |            | DCMI_D5                          | -         | TIM8_BKIN2_<br>COMP2             | SAI1_FS_B           | TIM16_CH1N               | EVENTOUT |

| Port B | PB7  | UART4_CTS                    | TSC_G2_IO4 | DCMI_VSYNC                       | LCD_SEG21 | FMC_NL                           | TIM8_BKIN_C<br>OMP1 | TIM17_CH1N               | EVENTOUT |

|        | PB8  | -                            | CAN1_RX    | DCMI_D6                          | LCD_SEG16 | SDMMC1_D4                        | SAI1_MCLK_A         | TIM16_CH1                | EVENTOUT |

|        | PB9  | -                            | CAN1_TX    | DCMI_D7                          | LCD_COM3  | SDMMC1_D5                        | SAI1_FS_A           | TIM17_CH1                | EVENTOUT |

|        | PB10 | LPUART1_RX                   | TSC_SYNC   | QUADSPI_CLK                      | LCD_SEG10 | COMP1_OUT                        | SAI1_SCK_A          | -                        | EVENTOUT |

|        | PB11 | LPUART1_TX                   | -          | QUADSPI_BK1_NCS                  | LCD_SEG11 | COMP2_OUT                        | -                   | -                        | EVENTOUT |

|        | PB12 | LPUART1_RT<br>S_DE           | TSC_G1_IO1 | CAN2_RX                          | LCD_SEG12 | SWPMI1_IO                        | SAI2_FS_A           | TIM15_BKIN               | EVENTOUT |

|        | PB13 | LPUART1_CT<br>S              | TSC_G1_IO2 | CAN2_TX                          | LCD_SEG13 | SWPMI1_TX                        | SAI2_SCK_A          | TIM15_CH1N               | EVENTOUT |

|        | PB14 | -                            | TSC_G1_IO3 | -                                | LCD_SEG14 | SWPMI1_RX                        | SAI2_MCLK_A         | TIM15_CH1                | EVENTOUT |

|        | PB15 | -                            | TSC_G1_IO4 | -                                | LCD_SEG15 | SWPMI1_SUS<br>PEND               | SAI2_SD_A           | TIM15_CH2                | EVENTOUT |

# 6.3.2 Operating conditions at power-up / power-down

The parameters given in *Table 23* are derived from tests performed under the ambient temperature condition summarized in *Table 22*.

Table 23. Operating conditions at power-up / power-down<sup>(1)</sup>

| Symbol              | Parameter                         | Conditions | Min | Max | Unit  |

|---------------------|-----------------------------------|------------|-----|-----|-------|

| t <sub>VDD</sub>    | V <sub>DD</sub> rise time rate    |            | 0   | ∞   | ue/\/ |

|                     | V <sub>DD</sub> fall time rate    | -          | 10  | ∞   | μs/V  |

|                     | V <sub>DDA</sub> rise time rate   |            | 0   | ∞   | μοΔ/  |

| t <sub>VDDA</sub>   | V <sub>DDA</sub> fall time rate   | -          | 10  | ∞   | μs/V  |

| +                   | V <sub>DDUSB</sub> rise time rate |            | 0   | ∞   | μs/V  |

| <sup>t</sup> VDDUSB | V <sub>DDUSB</sub> fall time rate | -          | 10  | ∞   | μ5/ ν |

| t <sub>VDDIO2</sub> | V <sub>DDIO2</sub> rise time rate |            | 0   | ∞   | ue/\/ |

|                     | V <sub>DDIO2</sub> fall time rate | -          | 10  | ∞   | µs/V  |

<sup>1.</sup> At Power up, the  $V_{DD12}$  voltage should not be forced externally

The requirements for power-up/down sequence specified in *Section 3.10.1: Power supply schemes* must be respected.

# 6.3.3 Embedded reset and power control block characteristics

The parameters given in *Table 24* are derived from tests performed under the ambient temperature conditions summarized in *Table 22: General operating conditions*.

Table 24. Embedded reset and power control block characteristics

| Symbol                               | Parameter                                  | Conditions <sup>(1)</sup> | Min  | Тур  | Max  | Unit |

|--------------------------------------|--------------------------------------------|---------------------------|------|------|------|------|

| t <sub>RSTTEMPO</sub> <sup>(2)</sup> | Reset temporization after BOR0 is detected | V <sub>DD</sub> rising    | -    | 250  | 400  | μs   |

| V <sub>BOR0</sub> (2)                | Brown-out reset threshold 0                | Rising edge               | 1.62 | 1.66 | 1.7  | V    |

| VBOR0`                               | Brown-out reset timeshold o                | Falling edge              | 1.6  | 1.64 | 1.69 | V    |

| V                                    | Brown-out reset threshold 1                | Rising edge               | 2.06 | 2.1  | 2.14 | V    |

| V <sub>BOR1</sub>                    | Brown-out reset timeshold i                | Falling edge              | 1.96 | 2    | 2.04 | V    |

|                                      | Brown-out reset threshold 2                | Rising edge               | 2.26 | 2.31 | 2.35 | V    |

| V <sub>BOR2</sub>                    | Brown-out reset timeshold 2                | Falling edge              | 2.16 | 2.20 | 2.24 | V    |

| V                                    | Brown-out reset threshold 3                | Rising edge               | 2.56 | 2.61 | 2.66 | V    |

| V <sub>BOR3</sub>                    | Brown-out reset timeshold 3                | Falling edge              | 2.47 | 2.52 | 2.57 | V    |

| V                                    | Drown out road throshold 4                 | Rising edge               | 2.85 | 2.90 | 2.95 | V    |

| V <sub>BOR4</sub>                    | Brown-out reset threshold 4                | Falling edge              | 2.76 | 2.81 | 2.86 | V    |

| V                                    | Programmable voltage                       | Rising edge               | 2.1  | 2.15 | 2.19 | V    |

| V <sub>PVD0</sub>                    | detector threshold 0                       | Falling edge              | 2    | 2.05 | 2.1  |      |

120/273 DS11584 Rev 7

Table 44. Current consumption in Stop 2 mode (continued)

|                             |                                                  | Conditions                                        |                 |       |       | TYP   |        | (      | ,     |       | MAX <sup>(1)</sup> |        |        |      |

|-----------------------------|--------------------------------------------------|---------------------------------------------------|-----------------|-------|-------|-------|--------|--------|-------|-------|--------------------|--------|--------|------|

| Symbol                      | Parameter                                        | -                                                 | V <sub>DD</sub> | 25 °C | 55 °C | 85 °C | 105 °C | 125 °C | 25 °C | 55 °C | 85 °C              | 105 °C | 125 °C | Unit |

|                             |                                                  |                                                   | 1.8 V           | 2.97  | 7.46  | 26.2  | 61.4   | 139    | 6.1   | 17.2  | 64.8               | 155.4  | 354    |      |

|                             |                                                  | RTC clocked by LSI,                               | 2.4 V           | 3.09  | 7.61  | 26.5  | 62.3   | 140    | 6.2   | 17.5  | 65.7               | 157.6  | 360    |      |

|                             |                                                  | LCD disabled                                      | 3 V             | 3.15  | 7.81  | 27    | 63.5   | 144    | 6.5   | 17.9  | 67.2               | 160.6  | 367    |      |

|                             |                                                  |                                                   | 3.6 V           | 3.4   | 8.05  | 27.7  | 65.2   | 147    | 7.1   | 18.7  | 69.0               | 164.9  | 376    |      |

|                             |                                                  |                                                   | 1.8 V           | 2.98  | 7.31  | 25.5  | 60     | 135    | 5.5   | 16.8  | 65.1               | 155.8  | 355    |      |

|                             | Supply current in<br>Stop 2 mode,<br>RTC enabled | RTC clocked by LSI,<br>LCD enabled <sup>(3)</sup> | 2.4 V           | 3.10  | 7.46  | 25.8  | 60.7   | 137    | 5.8   | 17.1  | 66.3               | 158.2  | 360    |      |

|                             |                                                  |                                                   | 3 V             | 3.23  | 7.63  | 26.4  | 62.1   | 141    | 6.2   | 17.5  | 67.6               | 161.4  | 367    |      |

| I <sub>DD_ALL</sub> (Stop 2 |                                                  |                                                   | 3.6 V           | 3.47  | 7.95  | 27.1  | 63.6   | 144    | 6.58  | 18.3  | 69.5               | 165.5  | 376    |      |

| with RTC)                   |                                                  |                                                   | 1.8 V           | 2.93  | 7.52  | 26.2  | 61.4   | 139    | -     | -     | -                  | -      | -      | μA   |

|                             |                                                  | RTC clocked by LSE bypassed at                    | 2.4 V           | 3.1   | 7.68  | 26.6  | 62.1   | 140    | -     | -     | -                  | -      | -      |      |

|                             |                                                  | 32768Hz,LCD disabled                              | 3 V             | 3.3   | 7.81  | 26.9  | 63.4   | 143    | -     | -     | -                  | -      | -      |      |

|                             |                                                  |                                                   | 3.6 V           | 3.48  | 8.07  | 27.6  | 65.0   | 146    | -     | -     | -                  | -      | -      |      |

|                             |                                                  | DTC algaland by LCE                               | 1.8 V           | 2.86  | 7.48  | 26.2  | 61.4   | -      | -     | -     | -                  | -      | -      |      |

|                             |                                                  | RTC clocked by LSE quartz <sup>(3)</sup>          | 2.4 V           | 3.01  | 7.56  | 26.5  | 62.2   | -      | -     | -     | -                  | -      | -      |      |

|                             |                                                  | in low drive mode,                                | 3 V             | 3.18  | 7.65  | 26.8  | 63.5   | -      | -     | -     | -                  | -      | -      |      |

|                             |                                                  | LCD disabled                                      | 3.6 V           | 3.31  | 7.94  | 27.5  | 65.1   | -      | ı     | -     | ı                  | -      | -      |      |

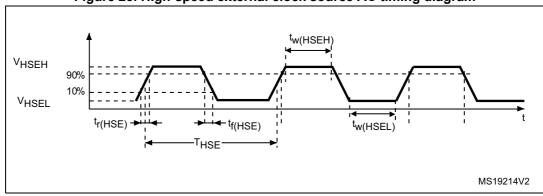

Figure 23. High-speed external clock source AC timing diagram

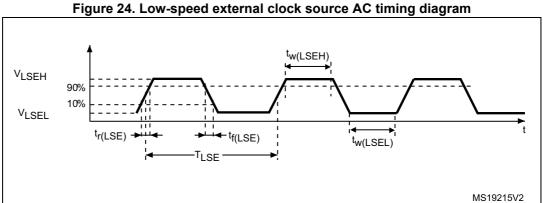

## Low-speed external user clock generated from an external source

In bypass mode the LSE oscillator is switched off and the input pin is a standard GPIO.

The external clock signal has to respect the I/O characteristics in Section 6.3.14. However, the recommended clock input waveform is shown in Figure 24.

|                      | iano co. zon opera externa acor ereas enaracioneste |            |                        |        |                        |      |  |  |  |  |  |  |

|----------------------|-----------------------------------------------------|------------|------------------------|--------|------------------------|------|--|--|--|--|--|--|

| Symbol               | Parameter                                           | Conditions | Min                    | Тур    | Max                    | Unit |  |  |  |  |  |  |

| f <sub>LSE_ext</sub> | User external clock source frequency                | -          | -                      | 32.768 | 1000                   | kHz  |  |  |  |  |  |  |

| V <sub>LSEH</sub>    | OSC32_IN input pin high level voltage               | -          | 0.7 V <sub>DDIOx</sub> | -      | $V_{DDIOx}$            | V    |  |  |  |  |  |  |

| $V_{LSEL}$           | OSC32_IN input pin low level voltage                | -          | $V_{SS}$               | ı      | 0.3 V <sub>DDIOx</sub> | ٧    |  |  |  |  |  |  |

| t <sub>w(LSEL)</sub> | OSC32_IN high or low time                           | -          | 250                    | -      | -                      | ns   |  |  |  |  |  |  |

Table 55. Low-speed external user clock characteristics<sup>(1)</sup>

<sup>1.</sup> Guaranteed by design.

| Table 60. HSI48 | 3 oscillator | characteristics <sup>(1)</sup> | (continued) |

|-----------------|--------------|--------------------------------|-------------|

|-----------------|--------------|--------------------------------|-------------|

| Symbol                | Parameter                                                                  | Conditions | Min | Тур                    | Max | Unit |

|-----------------------|----------------------------------------------------------------------------|------------|-----|------------------------|-----|------|

| N <sub>T</sub> jitter | Next transition jitter<br>Accumulated jitter on 28 cycles <sup>(4)</sup>   | -          | -   | +/-0.15 <sup>(2)</sup> | -   | ns   |

| P <sub>T</sub> jitter | Paired transition jitter<br>Accumulated jitter on 56 cycles <sup>(4)</sup> | -          | -   | +/-0.25 <sup>(2)</sup> | -   | ns   |

- 1.  $V_{DD}$  = 3 V, TA = -40 to 125°C unless otherwise specified.

- 2. Guaranteed by design.

- 3. Guaranteed by characterization results.

- 4. Jitter measurement are performed without clock source activated in parallel.

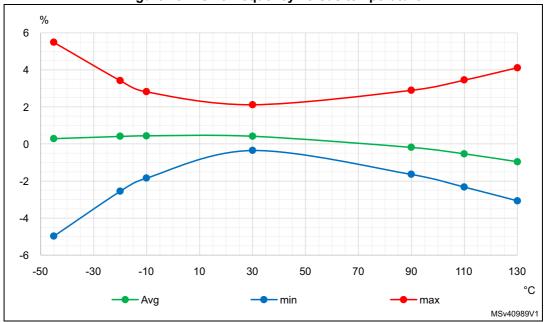

Figure 29. HSI48 frequency versus temperature

## Low-speed internal (LSI) RC oscillator

Table 61. LSI oscillator characteristics<sup>(1)</sup>

| Symbol                                 | Parameter                         | Conditions                                      | Min   | Тур | Max   | Unit |

|----------------------------------------|-----------------------------------|-------------------------------------------------|-------|-----|-------|------|

| f                                      | LSI Frequency                     | V <sub>DD</sub> = 3.0 V, T <sub>A</sub> = 30 °C | 31.04 | -   | 32.96 | kHz  |

| f <sub>LSI</sub>                       | LSI Frequency                     | $V_{DD}$ = 1.62 to 3.6 V, $T_A$ = -40 to 125 °C | 29.5  | -   | 34    | KΠZ  |

| t <sub>SU</sub> (LSI) <sup>(2)</sup>   | LSI oscillator start-<br>up time  | -                                               | -     | 80  | 130   | μs   |

| t <sub>STAB</sub> (LSI) <sup>(2)</sup> | LSI oscillator stabilization time | 5% of final frequency                           | -     | 125 | 180   | μs   |

| I <sub>DD</sub> (LSI) <sup>(2)</sup>   | LSI oscillator power consumption  | -                                               | -     | 110 | 180   | nA   |

- 1. Guaranteed by characterization results.

- 2. Guaranteed by design.

# 6.3.18 Analog-to-Digital converter characteristics

Unless otherwise specified, the parameters given in *Table 76* are preliminary values derived from tests performed under ambient temperature,  $f_{PCLK}$  frequency and  $V_{DDA}$  supply voltage conditions summarized in *Table 22: General operating conditions*.

Note: It is recommended to perform a calibration after each power-up.

Table 76. ADC characteristics<sup>(1) (2)</sup>

| Symbol                          | Parameter                                  | Conditions                                        | Min Ty |                  | Max               | Unit                 |

|---------------------------------|--------------------------------------------|---------------------------------------------------|--------|------------------|-------------------|----------------------|

| V <sub>DDA</sub>                | Analog supply voltage                      | -                                                 | 1.62   | 1.62 - 3.0       |                   | V                    |

| V                               | Positive reference voltage                 | V <sub>DDA</sub> ≥ 2 V                            | 2      | -                | $V_{DDA}$         | V                    |

| V <sub>REF+</sub>               | Positive reference voltage                 | V <sub>DDA</sub> < 2 V                            |        | $V_{DDA}$        |                   | V                    |

| V <sub>REF-</sub>               | Negative reference voltage                 | -                                                 |        | V <sub>SSA</sub> |                   | V                    |

| £                               | ADC aloak from one                         | Range 1                                           | 0.14   | -                | 80                | MUT                  |

| f <sub>ADC</sub>                | ADC clock frequency                        | Range 2                                           | 0.14   | -                | 26                | - MHz                |

|                                 |                                            | Resolution = 12 bits                              | -      | -                | 5.33              |                      |

|                                 | Sampling rate for FAST                     | Resolution = 10 bits                              | -      | -                | 6.15              |                      |

|                                 | channels                                   | Resolution = 8 bits                               | -      | -                | 7.27              |                      |

|                                 |                                            | Resolution = 6 bits                               | -      | -                | 8.88              | Mana                 |

| f <sub>s</sub>                  |                                            | Resolution = 12 bits                              | -      | -                | 4.21              | - Msps               |

|                                 | Sampling rate for SLOW channels            | Resolution = 10 bits                              | -      | -                | 4.71              |                      |

|                                 |                                            | Resolution = 8 bits                               | -      | -                | 5.33              |                      |

|                                 |                                            | Resolution = 6 bits                               | -      | -                | 6.15              |                      |

| f <sub>TRIG</sub>               | External trigger frequency                 | f <sub>ADC</sub> = 80 MHz<br>Resolution = 12 bits | -      | -                | 5.33              | MHz                  |

|                                 |                                            | Resolution = 12 bits                              | -      | -                | 15                | 1/f <sub>ADC</sub>   |

| V <sub>AIN</sub> <sup>(3)</sup> | Conversion voltage range(2)                | -                                                 | 0      | -                | V <sub>REF+</sub> | V                    |

| R <sub>AIN</sub>                | External input impedance                   | -                                                 | -      | -                | 50                | kΩ                   |

| C <sub>ADC</sub>                | Internal sample and hold capacitor         | -                                                 | -      | 5                | -                 | pF                   |

| t <sub>STAB</sub>               | Power-up time                              | -                                                 |        | 1                |                   | conversion cycle     |

| 4                               | Calibration time                           | f <sub>ADC</sub> = 80 MHz                         |        | 1.45             |                   | μs                   |

| t <sub>CAL</sub>                | Calibration time                           | -                                                 |        | 116              |                   | 1/f <sub>ADC</sub>   |

|                                 | Trigger conversion                         | CKMODE = 00                                       | 1.5    | 2                | 2.5               |                      |

|                                 | Trigger conversion latency Regular and     | CKMODE = 01                                       | -      | -                | 2.0               | 1 /f                 |

| t <sub>LATR</sub>               | injected channels without conversion abort | CKMODE = 10                                       | -      | -                | 2.25              | - 1/f <sub>ADC</sub> |

|                                 | COLINGISION ADOLL                          | CKMODE = 11                                       | -      | -                | 2.125             |                      |

Table 78. ADC accuracy - limited test conditions 1<sup>(1)(2)(3)</sup>

| Sym-<br>bol | Parameter               | Conditions <sup>(4)</sup>                                                                                                         |                          |                          |      | Тур  | Max | Unit |

|-------------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------|--------------------------|--------------------------|------|------|-----|------|

|             |                         |                                                                                                                                   | Single                   | Fast channel (max speed) | -    | 4    | 5   |      |

| Total       |                         |                                                                                                                                   | Slow channel (max speed) | -                        | 4    | 5    |     |      |

| ET          | unadjusted<br>error     |                                                                                                                                   | Differential             | Fast channel (max speed) | -    | 3.5  | 4.5 |      |

|             |                         |                                                                                                                                   | Differential             | Slow channel (max speed) | -    | 3.5  | 4.5 |      |

|             |                         |                                                                                                                                   | Single                   | Fast channel (max speed) | -    | 1    | 2.5 |      |

| EO          | Offset                  |                                                                                                                                   | ended                    | Slow channel (max speed) | -    | 1    | 2.5 |      |

|             | error                   |                                                                                                                                   | Differential             | Fast channel (max speed) | -    | 1.5  | 2.5 |      |

|             |                         |                                                                                                                                   | Dillerential             | Slow channel (max speed) | -    | 1.5  | 2.5 |      |

|             |                         |                                                                                                                                   | Single                   | Fast channel (max speed) | -    | 2.5  | 4.5 |      |

| EG          | Gain orror              |                                                                                                                                   | ended                    | Slow channel (max speed) | -    | 2.5  | 4.5 | LCD  |

| EG          | Gain enoi               | Differential linearity error  ADC clock frequency ≤ 80 MHz, Sampling rate ≤ 5.33 Msps, V <sub>DDA</sub> = VREF+ = 3 V, TA = 25 °C | Differential             | Fast channel (max speed) | -    | 2.5  | 3.5 |      |

|             |                         |                                                                                                                                   | Dillerential             | Slow channel (max speed) | -    | 2.5  | 3.5 |      |

|             |                         |                                                                                                                                   | Single<br>ended          | Fast channel (max speed) | -    | 1    | 1.5 |      |

| ED          | Differential            |                                                                                                                                   |                          | Slow channel (max speed) | -    | 1    | 1.5 |      |

|             | 1                       |                                                                                                                                   | Differential             | Fast channel (max speed) | -    | 1    | 1.2 |      |

|             |                         |                                                                                                                                   |                          | Slow channel (max speed) | -    | 1    | 1.2 |      |

|             |                         |                                                                                                                                   | Single<br>ended          | Fast channel (max speed) | -    | 1.5  | 2.5 |      |

| EL          | Integral                |                                                                                                                                   |                          | Slow channel (max speed) | -    | 1.5  | 2.5 |      |

| EL          | _                       |                                                                                                                                   | Differential             | Fast channel (max speed) | -    | 1    | 2   |      |

|             |                         |                                                                                                                                   |                          | Slow channel (max speed) | -    | 1    | 2   |      |

|             |                         |                                                                                                                                   | Single                   | Fast channel (max speed) | 10.4 | 10.5 | -   |      |

| ENOB        | Effective number of     |                                                                                                                                   | ended                    | Slow channel (max speed) | 10.4 | 10.5 | -   | bits |

| LINOB       | bits                    |                                                                                                                                   | Differential             | Fast channel (max speed) | 10.8 | 10.9 | -   | טונס |

|             |                         |                                                                                                                                   | Dillerential             | Slow channel (max speed) | 10.8 | 10.9 | -   |      |

|             | Cianal to               |                                                                                                                                   | Single                   | Fast channel (max speed) | 64.4 | 65   | -   |      |

| SINAD       | Signal-to-<br>noise and |                                                                                                                                   | ended                    | Slow channel (max speed) | 64.4 | 65   | -   |      |

| SINAD       | distortion              |                                                                                                                                   | Differential             | Fast channel (max speed) | 66.8 | 67.4 | -   | 1    |

| ratio       |                         | Dillerential                                                                                                                      | Slow channel (max speed) | 66.8                     | 67.4 | -    | ЧD  |      |

|             |                         |                                                                                                                                   | Single                   | Fast channel (max speed) | 65   | 66   | -   | dB   |

| SNR         | Signal-to-              |                                                                                                                                   | ended                    | Slow channel (max speed) | 65   | 66   | -   | 1    |

| SINK        | noise ratio             |                                                                                                                                   | D:#                      | Fast channel (max speed) | 67   | 68   | -   |      |

|             |                         |                                                                                                                                   | Differential             | Slow channel (max speed) | 67   | 68   | -   |      |

Table 80. ADC accuracy - limited test conditions  $3^{(1)(2)(3)}$  (continued)

| Sym-<br>bol | Parameter                                  | Conditions <sup>(4)</sup>                                               |                          |                          | Min | Тур | Max | Unit |

|-------------|--------------------------------------------|-------------------------------------------------------------------------|--------------------------|--------------------------|-----|-----|-----|------|

|             |                                            | ADC clock frequency ≤                                                   | Single                   | Fast channel (max speed) | -   | -69 | -67 |      |

| Total       | 80 MHz,<br>Il Sampling rate ≤ 5.33 Msps, L | ended                                                                   | Slow channel (max speed) | -                        | -71 | -67 |     |      |

| THD         | harmonic distortion                        | $1.65 \text{ V} \le \text{V}_{\text{DDA}} = \text{V}_{\text{REF+}} \le$ |                          | Fast channel (max speed) | -   | -72 | -71 | dB   |

| distortion  |                                            | Differential                                                            | Slow channel (max speed) | -                        | -72 | -71 |     |      |

- 1. Guaranteed by design.

- 2. ADC DC accuracy values are measured after internal calibration.

- ADC accuracy vs. negative Injection Current: Injecting negative current on any analog input pins should be avoided as this

significantly reduces the accuracy of the conversion being performed on another analog input. It is recommended to add a

Schottky diode (pin to ground) to analog pins which may potentially inject negative current.

- 4. The I/O analog switch voltage booster is enable when  $V_{DDA}$  < 2.4 V (BOOSTEN = 1 in the SYSCFG\_CFGR1 when  $V_{DDA}$  < 2.4 V). It is disable when  $V_{DDA} \ge 2.4$  V. No oversampling.

188/273 DS11584 Rev 7

Table 85. COMP characteristics<sup>(1)</sup> (continued)

| Symbol                  | Parameter                                    | Co                       | Conditions                                        |   |      | Max | Unit |

|-------------------------|----------------------------------------------|--------------------------|---------------------------------------------------|---|------|-----|------|

| I <sub>DDA</sub> (COMP) |                                              | Ultra-low-<br>power mode | Static                                            | - | 400  | 600 |      |

|                         | Comparator consumption from V <sub>DDA</sub> |                          | With 50 kHz<br>±100 mV overdrive<br>square signal | - | 1200 | 1   | nA   |

|                         |                                              | Medium mode              | Static                                            | - | 5    | 7   |      |

|                         |                                              |                          | With 50 kHz<br>±100 mV overdrive<br>square signal | - | 6    | -   | μA   |

|                         |                                              |                          | Static                                            | - | 70   | 100 | μΑ   |

|                         |                                              | High-speed mode          | With 50 kHz<br>±100 mV overdrive<br>square signal | ı | 75   | ı   |      |

| l <sub>bias</sub>       | Comparator input bias current                |                          | -                                                 | - | _(4) | nA  |      |

- 1. Guaranteed by design, unless otherwise specified.

- 2. Refer to Table 25: Embedded internal voltage reference.

- 3. Guaranteed by characterization results.

- 4. Mostly I/O leakage when used in analog mode. Refer to I<sub>lkg</sub> parameter in Table 70: I/O static characteristics.

# 6.3.22 Operational amplifiers characteristics

Table 86. OPAMP characteristics<sup>(1)</sup>

| Symbol                       | Parameter                                                                        | Conditions                |   | Тур | Max              | Unit  |  |

|------------------------------|----------------------------------------------------------------------------------|---------------------------|---|-----|------------------|-------|--|

| $V_{DDA}$                    | Analog supply voltage                                                            | -                         |   | -   | 3.6              | V     |  |

| CMIR                         | Common mode input range                                                          | -                         |   | -   | V <sub>DDA</sub> | V     |  |

| \/I                          | Input offset                                                                     | 25 °C, No Load on output. | - | -   | ±1.5             | m\/   |  |

| VI <sub>OFFSET</sub>         | voltage                                                                          | All voltage/Temp.         | - | -   | ±3               | mV    |  |

| A\/  .                       | Input offset voltage drift                                                       | Normal mode               | - | ±5  | -                | μV/°C |  |

| ΔVI <sub>OFFSET</sub>        |                                                                                  | Low-power mode            | - | ±10 | -                | μν/ Ο |  |

| TRIMOFFSETP<br>TRIMLPOFFSETP | Offset trim step<br>at low common<br>input voltage<br>(0.1 x V <sub>DDA</sub> )  | -                         | 1 | 0.8 | 1.1              | mV    |  |

| TRIMOFFSETN<br>TRIMLPOFFSETN | Offset trim step<br>at high common<br>input voltage<br>(0.9 x V <sub>DDA</sub> ) | -                         | - | 1   | 1.35             | 111.0 |  |

## 6.3.25 LCD controller characteristics

The devices embed a built-in step-up converter to provide a constant LCD reference voltage independently from the  $V_{DD}$  voltage. An external capacitor  $C_{\text{ext}}$  must be connected to the VLCD pin to decouple this converter.

Table 90. LCD controller characteristics<sup>(1)</sup>

| Symbol                          | Parameter                                                      | Conditions                                 | Min  | Тур  | Max | Unit      |

|---------------------------------|----------------------------------------------------------------|--------------------------------------------|------|------|-----|-----------|

| V <sub>LCD</sub>                | LCD external voltage                                           |                                            |      | -    | 3.6 |           |

| V <sub>LCD0</sub>               | LCD internal reference volta                                   | LCD internal reference voltage 0           |      |      | -   |           |

| V <sub>LCD1</sub>               | LCD internal reference volta                                   | -                                          | 2.76 | -    |     |           |

| V <sub>LCD2</sub>               | LCD internal reference volta                                   | -                                          | 2.89 | -    |     |           |

| V <sub>LCD3</sub>               | LCD internal reference volta                                   | LCD internal reference voltage 3           |      |      |     | V         |

| V <sub>LCD4</sub>               | LCD internal reference volta                                   | ge 4                                       | -    | 3.19 | -   |           |

| V <sub>LCD5</sub>               | LCD internal reference volta                                   | -                                          |      | 3.32 | -   |           |

| V <sub>LCD6</sub>               | LCD internal reference volta                                   | ge 6                                       | -    | 3.46 | -   |           |

| V <sub>LCD7</sub>               | LCD internal reference volta                                   | ge 7                                       | -    | 3.62 | -   |           |

|                                 | V <sub>LCD</sub> external capacitance                          | Buffer OFF<br>(BUFEN=0 is LCD_CR register) | 0.2  | -    | 2   |           |

| C <sub>ext</sub>                |                                                                | Buffer ON (BUFEN=1 is LCD_CR register)     | 1    | -    | 2   | μF        |

| (2)                             | Supply current from V <sub>DD</sub> at V <sub>DD</sub> = 2.2 V | Buffer OFF<br>(BUFEN=0 is LCD_CR register) | -    | 3    | -   |           |

| I <sub>LCD</sub> <sup>(2)</sup> | Supply current from V <sub>DD</sub> at V <sub>DD</sub> = 3.0 V | Buffer OFF<br>(BUFEN=0 is LCD_CR register) | -    | 1.5  | -   | μΑ        |

|                                 |                                                                | Buffer OFF<br>(BUFFEN = 0, PON = 0)        | -    | 0.5  | -   |           |

|                                 | Supply current from V <sub>LCD</sub> (V <sub>LCD</sub> = 3 V)  | Buffer ON<br>(BUFFEN = 1, 1/2 Bias)        | -    | 0.6  | -   |           |

| I <sub>VLCD</sub>               |                                                                | Buffer ON<br>(BUFFEN = 1, 1/3 Bias)        | -    | 0.8  | -   | - μA<br>- |

|                                 |                                                                | Buffer ON<br>(BUFFEN = 1, 1/4 Bias)        | -    | 1    | -   |           |

| R <sub>HN</sub>                 | Total High Resistor value for                                  | -                                          | 5.5  | -    | МΩ  |           |

| R <sub>LN</sub>                 | Total Low Resistor value for                                   | High drive resistive network               | -    | 240  | -   | kΩ        |

## 6.3.27 Timer characteristics

The parameters given in the following tables are guaranteed by design.

Refer to *Section 6.3.14: I/O port characteristics* for details on the input/output alternate function characteristics (output compare, input capture, external clock, PWM output).

208/273 DS11584 Rev 7

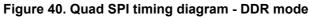

$t_{(\mathsf{CK})}$  $t_{\text{w}(\text{CKH})}$  $t_{\text{w}(\text{CKL})}$  $t_{\text{f(CK)}}$ Clock t<sub>v(OUT)</sub>  $\overset{t_{h(OUT)}}{\longleftrightarrow}$ Data output D0 D1 D2  $t_{\text{s}(\text{IN})}$  $t_{h(IN)} \\$ Data input D0 D1 D2 MSv36878V1

Figure 39. Quad SPI timing diagram - SDR mode

#### **SAI** characteristics

Unless otherwise specified, the parameters given in *Table 99* for SAI are derived from tests performed under the ambient temperature, f<sub>PCLKx</sub> frequency and V<sub>DD</sub> supply voltage conditions summarized in *Table 22: General operating conditions*, with the following configuration:

- Output speed is set to OSPEEDRy[1:0] = 10

- Capacitive load C = 30 pF

- Measurement points are done at CMOS levels: 0.5 x V<sub>DD</sub>

Refer to Section 6.3.14: I/O port characteristics for more details on the input/output alternate function characteristics (CK,SD,FS).

Table 99. SAI characteristics<sup>(1)</sup>

| Symbol                   | Parameter                          | Conditions                                                                  |      | Max    | Unit |  |

|--------------------------|------------------------------------|-----------------------------------------------------------------------------|------|--------|------|--|

| f <sub>MCLK</sub>        | SAI Main clock output              | -                                                                           | -    | 50     | MHz  |  |

|                          |                                    | Master transmitter<br>2.7 V ≤ V <sub>DD</sub> ≤ 3.6 V<br>Voltage Range 1    | -    | 21.5   |      |  |

|                          |                                    | Master transmitter<br>1.71 V ≤ V <sub>DD</sub> ≤ 3.6 V<br>Voltage Range 1   |      |        |      |  |

|                          |                                    | Master receiver<br>Voltage Range 1                                          | -    | 25     | 1    |  |

| f <sub>CK</sub>          | SAI clock frequency <sup>(2)</sup> | Slave transmitter 2.7 V $\leq$ V <sub>DD</sub> $\leq$ 3.6 V Voltage Range 1 | - 20 |        | MHz  |  |

|                          |                                    | Slave transmitter<br>1.71 V ≤ V <sub>DD</sub> ≤ 3.6 V<br>Voltage Range 1    | -    | - 13.5 |      |  |

|                          |                                    | Slave receiver<br>Voltage Range 1                                           | -    | 25     |      |  |

|                          |                                    | Voltage Range 2                                                             | -    | 13     |      |  |

|                          |                                    | 1.08 V ≤ V <sub>DD</sub> ≤ 1.32 V                                           | -    | 7      |      |  |

| +                        | FS valid time                      | Master mode<br>2.7 V ≤ V <sub>DD</sub> ≤ 3.6 V                              | -    | 22     | ns   |  |

| t <sub>v(FS)</sub>       | rs valid time                      | Master mode 1.71 V $\leq$ V <sub>DD</sub> $\leq$ 3.6 V                      | -    | 40     | 115  |  |

| t <sub>h(FS)</sub>       | FS hold time                       | Master mode                                                                 | 10   | -      | ns   |  |

| t <sub>su(FS)</sub>      | FS setup time                      | Slave mode                                                                  | 1    | -      | ns   |  |

| t <sub>h(FS)</sub>       | FS hold time                       | Slave mode                                                                  | 2    | -      | ns   |  |

| t <sub>su(SD_A_MR)</sub> | Data input setup time              | Master receiver                                                             | 1    | -      | ns   |  |

| t <sub>su(SD_B_SR)</sub> | Data input setup tillie            | Slave receiver                                                              | 1    | -      | 113  |  |

| t <sub>h(SD_A_MR)</sub>  | Data input hold time               | Master receiver                                                             | 5    | -      | ns   |  |

| t <sub>h(SD_B_SR)</sub>  | Data input noid time               | Slave receiver                                                              | 2    | -      | 110  |  |

DS11584 Rev 7 217/273

Package information STM32L4A6xG

Figure 64. UFBGA169, external SMPS device, marking (package top view

1. Parts marked as ES or E or accompanied by an Engineering Sample notification letter are not yet qualified and therefore not approved for use in production. ST is not responsible for any consequences resulting from such use. In no event will ST be liable for the customer using any of these engineering samples in production. ST's Quality department must be contacted prior to any decision to use these engineering samples to run a qualification activity.

Package information STM32L4A6xG

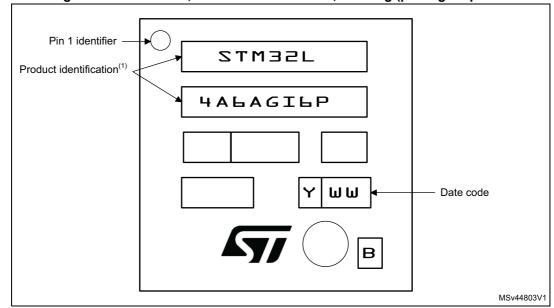

Table 125. LQFP144 - 144-pin, 20 x 20 mm low-profile quad flat package mechanical data

| Symbol |        | millimeters |        | inches <sup>(1)</sup> |        |        |

|--------|--------|-------------|--------|-----------------------|--------|--------|

| Symbol | Min    | Тур         | Max    | Min                   | Тур    | Max    |

| Α      | -      | -           | 1.600  | -                     | -      | 0.0630 |

| A1     | 0.050  | -           | 0.150  | 0.0020                | -      | 0.0059 |

| A2     | 1.350  | 1.400       | 1.450  | 0.0531                | 0.0551 | 0.0571 |

| b      | 0.170  | 0.220       | 0.270  | 0.0067                | 0.0087 | 0.0106 |

| С      | 0.090  | -           | 0.200  | 0.0035                | -      | 0.0079 |

| D      | 21.800 | 22.000      | 22.200 | 0.8583                | 0.8661 | 0.8740 |

| D1     | 19.800 | 20.000      | 20.200 | 0.7795                | 0.7874 | 0.7953 |

| D3     | -      | 17.500      | -      | -                     | 0.6890 | -      |

| E      | 21.800 | 22.000      | 22.200 | 0.8583                | 0.8661 | 0.8740 |

| E1     | 19.800 | 20.000      | 20.200 | 0.7795                | 0.7874 | 0.7953 |

| E3     | -      | 17.500      | -      | -                     | 0.6890 | -      |

| е      | -      | 0.500       | -      | -                     | 0.0197 | -      |

| L      | 0.450  | 0.600       | 0.750  | 0.0177                | 0.0236 | 0.0295 |

| L1     | -      | 1.000       | -      | -                     | 0.0394 | -      |

| k      | 0°     | 3.5°        | 7°     | 0°                    | 3.5°   | 7°     |

| ccc    | -      | -           | 0.080  | -                     | -      | 0.0031 |

<sup>1.</sup> Values in inches are converted from mm and rounded to 4 decimal digits.

Figure 66. LQFP144 - 144-pin,20 x 20 mm low-profile quad flat package recommended footprint

1. Dimensions are expressed in millimeters.

STM32L4A6xG Package information

Figure 75. LQFP100 marking (package top view)

Parts marked as ES or E or accompanied by an Engineering Sample notification letter are not yet qualified

and therefore not approved for use in production. ST is not responsible for any consequences resulting

from such use. In no event will ST be liable for the customer using any of these engineering samples in

production. ST's Quality department must be contacted prior to any decision to use these engineering

samples to run a qualification activity.

DS11584 Rev 7 259/273

Package information STM32L4A6xG

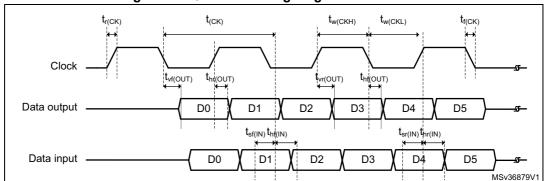

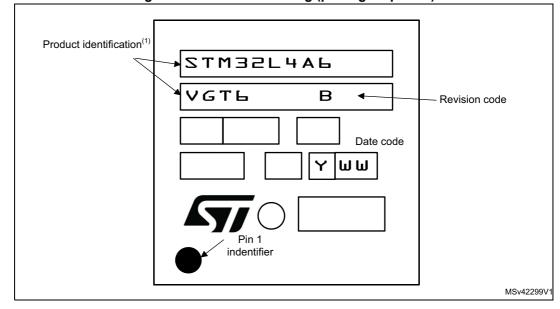

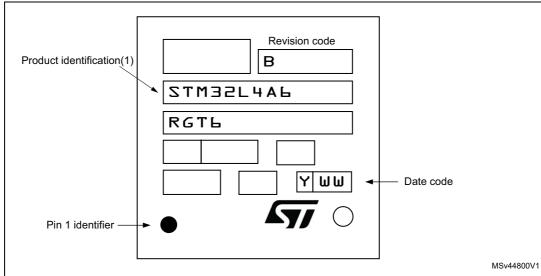

Figure 82. LQFP64 marking (package top view)

Parts marked as ES or E or accompanied by an Engineering Sample notification letter are not yet qualified

and therefore not approved for use in production. ST is not responsible for any consequences resulting

from such use. In no event will ST be liable for the customer using any of these engineering samples in

production. ST's Quality department must be contacted prior to any decision to use these engineering

samples to run a qualification activity.