Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                                     |

|----------------------------|-----------------------------------------------------------------------------------------------------|

| Product Status             | Active                                                                                              |

| Core Processor             | ARM® Cortex®-M4                                                                                     |

| Core Size                  | 32-Bit Single-Core                                                                                  |

| Speed                      | 80MHz                                                                                               |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, IrDA, LINbus, MMC/SD, QSPI, SAI, SPI, SWPMI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, LCD, PWM, WDT                                                          |

| Number of I/O              | 52                                                                                                  |

| Program Memory Size        | 1MB (1M x 8)                                                                                        |

| Program Memory Type        | FLASH                                                                                               |

| EEPROM Size                | -                                                                                                   |

| RAM Size                   | 320K x 8                                                                                            |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.6V                                                                                        |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                                               |

| Oscillator Type            | Internal                                                                                            |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                                                  |

| Mounting Type              | Surface Mount                                                                                       |

| Package / Case             | 64-LQFP                                                                                             |

| Supplier Device Package    | 64-LQFP (10x10)                                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l4a6rgt7tr                             |

|                            |                                                                                                     |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 3.4 Embedded Flash memory

STM32L4A6xG devices feature 1 Mbyte of embedded Flash memory available for storing programs and data. The Flash memory is divided into two banks allowing read-while-write operations. This feature allows to perform a read operation from one bank while an erase or program operation is performed to the other bank. The dual bank boot is also supported. Each bank contains 256 pages of 2 Kbyte.

Flexible protections can be configured thanks to option bytes:

- Readout protection (RDP) to protect the whole memory. Three levels are available:

- Level 0: no readout protection

- Level 1: memory readout protection: the Flash memory cannot be read from or written to if either debug features are connected, boot in RAM or bootloader is selected

- Level 2: chip readout protection: debug features (Cortex-M4 JTAG and serial wire), boot in RAM and bootloader selection are disabled (JTAG fuse). This selection is irreversible.

| Area      | Protection<br>level | U    | ser executio | on                 | Debug, boot from RAM or boot<br>from system memory (loader) |       |                    |  |  |

|-----------|---------------------|------|--------------|--------------------|-------------------------------------------------------------|-------|--------------------|--|--|

|           |                     | Read | Write        | Erase              | Read                                                        | Write | Erase              |  |  |

| Main      | 1                   | Yes  | Yes          | Yes                | No                                                          | No    | No                 |  |  |

| memory    | 2                   | Yes  | Yes          | Yes                | N/A                                                         | N/A   | N/A                |  |  |

| System    | 1                   | Yes  | No           | No                 | Yes                                                         | No    | No                 |  |  |

| memory    | 2                   | Yes  | No           | No                 | N/A                                                         | N/A   | N/A                |  |  |

| Option    | 1                   | Yes  | Yes          | Yes                | Yes                                                         | Yes   | Yes                |  |  |

| bytes     | 2                   | Yes  | No           | No                 | N/A                                                         | N/A   | N/A                |  |  |

| Backup    | 1                   | Yes  | Yes          | N/A <sup>(1)</sup> | No                                                          | No    | N/A <sup>(1)</sup> |  |  |

| registers | 2                   | Yes  | Yes          | N/A                | N/A                                                         | N/A   | N/A                |  |  |

| SRAM2     | 1                   | Yes  | Yes          | Yes <sup>(1)</sup> | No                                                          | No    | No <sup>(1)</sup>  |  |  |

| STAIVIZ   | 2                   | Yes  | Yes          | Yes                | N/A                                                         | N/A   | N/A                |  |  |

Table 3. Access status versus readout protection level and execution modes

1. Erased when RDP change from Level 1 to Level 0.

- Write protection (WRP): the protected area is protected against erasing and programming. Two areas per bank can be selected, with 2-Kbyte granularity.

- Proprietary code readout protection (PCROP): a part of the flash memory can be

protected against read and write from third parties. The protected area is execute-only:

it can only be reached by the STM32 CPU, as an instruction code, while all other

accesses (DMA, debug and CPU data read, write and erase) are strictly prohibited.

One area per bank can be selected, with 64-bit granularity. An additional option bit

(PCROP\_RDP) allows to select if the PCROP area is erased or not when the RDP

protection is changed from Level 1 to Level 0.

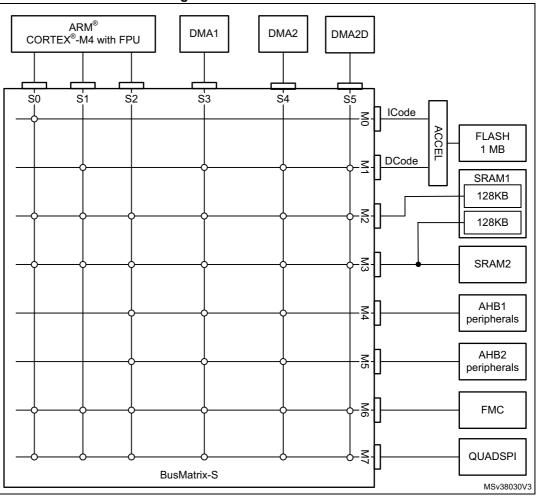

# 3.6 Multi-AHB bus matrix

The 32-bit multi-AHB bus matrix interconnects all the masters (CPU, DMAs and the DMA2D) and the slaves (Flash memory, RAM, FMC, QUADSPI, AHB and APB peripherals) and ensures a seamless and efficient operation even when several high speed peripherals work simultaneously.

Figure 2. Multi-AHB bus matrix

# 3.7 Firewall

The device embeds a Firewall which protects code sensitive and secure data from any access performed by a code executed outside of the protected areas.

Each illegal access generates a reset which kills immediately the detected intrusion.

By default, the microcontroller is in Run mode after a system or a power Reset. It is up to the user to select one of the low-power modes described below:

Sleep mode

In Sleep mode, only the CPU is stopped. All peripherals continue to operate and can wake up the CPU when an interrupt/event occurs.

Low-power run mode

This mode is achieved with V<sub>CORE</sub> supplied by the low-power regulator to minimize the regulator's operating current. The code can be executed from SRAM or from Flash, and the CPU frequency is limited to 2 MHz. The peripherals with independent clock can be clocked by HSI16.

### Low-power sleep mode

This mode is entered from the low-power run mode. Only the CPU clock is stopped. When wakeup is triggered by an event or an interrupt, the system reverts to the lowpower run mode.

### Stop 0, Stop 1 and Stop 2 modes

Stop mode achieves the lowest power consumption while retaining the content of SRAM and registers. All clocks in the V<sub>CORE</sub> domain are stopped, the PLL, the MSI RC, the HSI16 RC and the HSE crystal oscillators are disabled. The LSE or LSI is still running.

The RTC can remain active (Stop mode with RTC, Stop mode without RTC).

Some peripherals with wakeup capability can enable the HSI16 RC during Stop mode to detect their wakeup condition.

Three Stop modes are available: Stop 0, Stop 1 and Stop 2 modes. In Stop 2 mode, most of the V<sub>CORE</sub> domain is put in a lower leakage mode.

Stop 1 offers the largest number of active peripherals and wakeup sources, a smaller wakeup time but a higher consumption than Stop 2. In Stop 0 mode, the main regulator remains ON, allowing a very fast wakeup time but with much higher consumption.

The system clock when exiting from Stop 0, Stop 1 or Stop 2 modes can be either MSI up to 48 MHz or HSI16, depending on software configuration.

### Standby mode

The Standby mode is used to achieve the lowest power consumption with BOR. The internal regulator is switched off so that the V<sub>CORF</sub> domain is powered off. The PLL, the MSI RC, the HSI16 RC and the HSE crystal oscillators are also switched off.

The RTC can remain active (Standby mode with RTC, Standby mode without RTC).

The brown-out reset (BOR) always remains active in Standby mode.

The state of each I/O during standby mode can be selected by software: I/O with internal pull-up, internal pull-down or floating.

After entering Standby mode, SRAM1 and register contents are lost except for registers in the Backup domain and Standby circuitry. Optionally, SRAM2 can be retained in Standby mode, supplied by the low-power Regulator (Standby with SRAM2 retention mode).

The device exits Standby mode when an external reset (NRST pin), an IWDG reset, WKUP pin event (configurable rising or falling edge), or an RTC event occurs (alarm, periodic wakeup, timestamp, tamper) or a failure is detected on LSE (CSS on LSE).

The system clock after wakeup is MSI up to 8 MHz.

# 3.32 Universal synchronous/asynchronous receiver transmitter (USART)

The STM32L4A6xG devices have three embedded universal synchronous receiver transmitters (USART1, USART2 and USART3) and two universal asynchronous receiver transmitters (UART4, UART5).

These interfaces provide asynchronous communication, IrDA SIR ENDEC support, multiprocessor communication mode, single-wire half-duplex communication mode and have LIN Master/Slave capability. They provide hardware management of the CTS and RTS signals, and RS485 Driver Enable. They are able to communicate at speeds of up to 10Mbit/s.

USART1, USART2 and USART3 also provide Smart Card mode (ISO 7816 compliant) and SPI-like communication capability.

All USART have a clock domain independent from the CPU clock, allowing the USARTx (x=1,2,3,4,5) to wake up the MCU from Stop mode using baudrates up to 204 Kbaud. The wake up events from Stop mode are programmable and can be:

- Start bit detection

- Any received data frame

- A specific programmed data frame

All USART interfaces can be served by the DMA controller.

| USART modes/features <sup>(1)</sup>   | USART1 | USART2      | USART3  | UART4     | UART5 | LPUART1 |

|---------------------------------------|--------|-------------|---------|-----------|-------|---------|

| Hardware flow control for modem       | Х      | Х           | Х       | Х         | Х     | Х       |

| Continuous communication using DMA    | Х      | Х           | Х       | Х         | Х     | Х       |

| Multiprocessor communication          | Х      | Х           | Х       | Х         | Х     | Х       |

| Synchronous mode                      | Х      | Х           | Х       | -         | -     | -       |

| Smartcard mode                        | Х      | Х           | Х       | -         | -     | -       |

| Single-wire half-duplex communication | Х      | Х           | Х       | Х         | Х     | Х       |

| IrDA SIR ENDEC block                  | Х      | Х           | Х       | Х         | Х     | -       |

| LIN mode                              | Х      | Х           | Х       | Х         | Х     | -       |

| Dual clock domain                     | Х      | Х           | Х       | Х         | Х     | Х       |

| Wakeup from Stop 0 / Stop 1 modes     | Х      | Х           | Х       | Х         | Х     | Х       |

| Wakeup from Stop 2 mode               | -      | -           | -       | -         | -     | Х       |

| Receiver timeout interrupt            | Х      | Х           | Х       | Х         | Х     | -       |

| Modbus communication                  | Х      | Х           | Х       | Х         | х     | -       |

| Auto baud rate detection              |        | X (4 modes) |         |           |       |         |

| Driver Enable                         | Х      | Х           | Х       | Х         | Х     | Х       |

| LPUART/USART data length              |        | •           | 7, 8 ar | nd 9 bits | •     | •       |

Table 12. STM32L4A6xG USART/UART/LPUART features

1. X = supported.

| Na        | me                   | Abbreviation                                                   | Definition                                                                      |  |  |  |  |  |  |

|-----------|----------------------|----------------------------------------------------------------|---------------------------------------------------------------------------------|--|--|--|--|--|--|

| Pin r     | name                 | Unless otherwise specified ir<br>reset is the same as the actu | h brackets below the pin name, the pin function during and after<br>al pin name |  |  |  |  |  |  |

|           |                      | S                                                              | Supply pin                                                                      |  |  |  |  |  |  |

| Pin       | type                 | I                                                              | Input only pin                                                                  |  |  |  |  |  |  |

|           |                      | I/O                                                            | Input / output pin                                                              |  |  |  |  |  |  |

|           |                      | FT                                                             | 5 V tolerant I/O                                                                |  |  |  |  |  |  |

|           |                      | TT                                                             | 3.6 V tolerant I/O                                                              |  |  |  |  |  |  |

|           |                      | RST                                                            | Bidirectional reset pin with embedded weak pull-up resistor                     |  |  |  |  |  |  |

|           |                      |                                                                | Option for TT or FT I/Os                                                        |  |  |  |  |  |  |

| I/O str   | ructure              | _f <sup>(1)</sup>                                              | I/O, Fm+ capable                                                                |  |  |  |  |  |  |

|           |                      | _l <sup>(2)</sup>                                              | I/O, with LCD function supplied by V <sub>LCD</sub>                             |  |  |  |  |  |  |

|           |                      | _u <sup>(3)</sup>                                              | I/O, with USB function supplied by V <sub>DDUSB</sub>                           |  |  |  |  |  |  |

|           |                      | _a <sup>(4)</sup>                                              | I/O, with Analog switch function supplied by $V_{DDA}$                          |  |  |  |  |  |  |

|           |                      | _s <sup>(5)</sup>                                              | I/O supplied only by $V_{DDIO2}$                                                |  |  |  |  |  |  |

| No        | otes                 | Unless otherwise specified b                                   | y a note, all I/Os are set as analog inputs during and after reset.             |  |  |  |  |  |  |

| Pin       | Alternate functions  | Functions selected through (                                   | GPIOx_AFR registers                                                             |  |  |  |  |  |  |

| functions | Additional functions | Functions directly selected/e                                  | nabled through peripheral registers                                             |  |  |  |  |  |  |

| Table 14. Legend/abbreviations used in the | pinout table  |

|--------------------------------------------|---------------|

| Table 141 Eegena/abbrettatione acea in the | piniout tubio |

1. The related I/O structures in *Table 15* are: FT\_f, FT\_fa, FT\_fl, FT\_fla.

2. The related I/O structures in *Table 15* are: FT\_I, FT\_fI, FT\_lu.

3. The related I/O structures in *Table 15* are: FT\_u, FT\_lu.

4. The related I/O structures in *Table 15* are: FT\_a, FT\_la, FT\_fa, FT\_fla, TT\_a, TT\_la.

5. The related I/O structures in *Table 15* are: FT\_s, FT\_fs.

সি

DS11584 Rev 7

71/273

|        | Table 15. STM32L4A6xG pin definitions (continued) |               |         |          |               |         |              |          |               |                                       |          |               |            |                                                                |                      |

|--------|---------------------------------------------------|---------------|---------|----------|---------------|---------|--------------|----------|---------------|---------------------------------------|----------|---------------|------------|----------------------------------------------------------------|----------------------|

|        |                                                   |               |         | Pin N    | umber         | ·       |              |          |               |                                       |          |               |            | Pin functi                                                     | ons                  |

| LQFP64 | WLCSP100                                          | WLCSP100_SMPS | LQFP100 | UFBGA132 | UFBGA132_SMPS | LQFP144 | LQFP144_SMPS | UFBGA169 | UFBGA169_SMPS | Pin name<br>(function after<br>reset) | Pin type | I/O structure | Notes      | Alternate functions                                            | Additional functions |

| 4      | E10                                               | D9            | 9       | E1       | E1            | 9       | 9            | G1       | G1            | PC15-<br>OSC32_OUT<br>(PC15)          | I/O      | FT            | (1)<br>(2) | EVENTOUT                                                       | OSC32_OUT            |

| -      | -                                                 | -             | -       | D6       | D6            | 10      | 10           | F5       | F5            | PF0                                   | I/O      | FT_f          | -          | I2C2_SDA, FMC_A0, EVENTOUT                                     | -                    |

| -      | -                                                 | -             | -       | D5       | D5            | 11      | 11           | F4       | F4            | PF1                                   | I/O      | FT_f          | -          | I2C2_SCL, FMC_A1, EVENTOUT                                     | -                    |

| -      | -                                                 | -             | -       | D4       | D4            | 12      | 12           | F3       | F3            | PF2                                   | I/O      | FT            | -          | I2C2_SMBA, FMC_A2,<br>EVENTOUT                                 | -                    |

| -      | -                                                 | -             | -       | E4       | E4            | 13      | 13           | G3       | G3            | PF3                                   | I/O      | FT_a          | -          | FMC_A3, EVENTOUT                                               | ADC3_IN6             |

| -      | -                                                 | -             | -       | F3       | F3            | 14      | 14           | G4       | G4            | PF4                                   | I/O      | FT_a          | -          | FMC_A4, EVENTOUT                                               | ADC3_IN7             |

| -      | -                                                 | -             | -       | F4       | F4            | 15      | 15           | G5       | G5            | PF5                                   | I/O      | FT_a          | -          | FMC_A5, EVENTOUT                                               | ADC3_IN8             |

| -      | D9                                                | E10           | 10      | F2       | F2            | 16      | 16           | F2       | F2            | VSS                                   | S        | -             | -          | -                                                              | -                    |

| -      | E9                                                | E9            | 11      | G2       | G2            | 17      | 17           | G2       | G2            | VDD                                   | S        | -             | -          | -                                                              | -                    |

| -      | -                                                 | -             | -       | -        | -             | 18      | 18           | -        | -             | PF6                                   | I/O      | FT_a          | -          | TIM5_ETR, TIM5_CH1,<br>QUADSPI_BK1_IO3, SAI1_SD_B,<br>EVENTOUT | ADC3_IN9             |

| -      | -                                                 | -             | -       | -        | -             | 19      | 19           | -        | -             | PF7                                   | I/O      | FT_a          | -          | TIM5_CH2, QUADSPI_BK1_IO2,<br>SAI1_MCLK_B, EVENTOUT            | ADC3_IN10            |

| -      | -                                                 | -             | -       | -        | -             | 20      | 20           | -        | -             | PF8                                   | I/O      | FT_a          | -          | TIM5_CH3, QUADSPI_BK1_IO0,<br>SAI1_SCK_B, EVENTOUT             | ADC3_IN11            |

82/273

# DS11584 Rev 7

|        |          |               |         | Pin N    | umber         | ,       |              |          |               | wi32L4A6xG pi                         |          |               |       | Pin function                                                                                                                                               | ons                  |

|--------|----------|---------------|---------|----------|---------------|---------|--------------|----------|---------------|---------------------------------------|----------|---------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| LQFP64 | WLCSP100 | WLCSP100_SMPS | LQFP100 | UFBGA132 | UFBGA132_SMPS | LQFP144 | LQFP144_SMPS | UFBGA169 | UFBGA169_SMPS | Pin name<br>(function after<br>reset) | Pin type | I/O structure | Notes | Alternate functions                                                                                                                                        | Additional functions |

| 38     | F3       | E4            | 64      | E11      | E11           | 97      | 97           | G12      | G12           | PC7                                   | I/O      | FT_I          | -     | TIM3_CH2, TIM8_CH2,<br>DFSDM1_DATIN3, TSC_G4_IO2,<br>DCMI_D1, LCD_SEG25,<br>SDMMC1_D7, SAI2_MCLK_B,<br>EVENTOUT                                            | -                    |

| 39     | E1       | E1            | 65      | E10      | E10           | 98      | 98           | G10      | G10           | PC8                                   | I/O      | FT_I          | -     | TIM3_CH3, TIM8_CH3,<br>TSC_G4_IO3, DCMI_D2,<br>LCD_SEG26, SDMMC1_D0,<br>EVENTOUT                                                                           | -                    |

| 40     | E2       | E2            | 66      | D12      | D12           | 99      | 99           | G9       | G9            | PC9                                   | I/O      | FT_fl         | -     | TIM8_BKIN2, TIM3_CH4,<br>TIM8_CH4, DCMI_D3, I2C3_SDA,<br>TSC_G4_IO4, OTG_FS_NOE,<br>LCD_SEG27, SDMMC1_D1,<br>SAI2_EXTCLK,<br>TIM8_BKIN2_COMP1,<br>EVENTOUT | -                    |

| 41     | E3       | E3            | 67      | D11      | D11           | 100     | 100          | G8       | G8            | PA8                                   | I/O      | FT_I          | -     | MCO, TIM1_CH1, USART1_CK,<br>OTG_FS_SOF, LCD_COM0,<br>SWPMI1_IO, SAI1_SCK_A,<br>LPTIM2_OUT, EVENTOUT                                                       | -                    |

| 42     | D3       | D3            | 68      | D10      | D10           | 101     | 101          | F10      | F10           | PA9                                   | I/O      | FT_lu         | -     | TIM1_CH2, SPI2_SCK, DCMI_D0,<br>USART1_TX, LCD_COM1,<br>SAI1_FS_A, TIM15_BKIN,<br>EVENTOUT                                                                 | OTG_FS_VBUS          |

| 43     | D2       | D2            | 69      | C12      | C12           | 102     | 102          | F9       | F9            | PA10                                  | I/O      | FT_lu         | -     | TIM1_CH3, DCMI_D1,<br>USART1_RX, OTG_FS_ID,<br>LCD_COM2, SAI1_SD_A,<br>TIM17_BKIN, EVENTOUT                                                                | -                    |

### Table 15. STM32L4A6xG pin definitions (continued)

| S          |

|------------|

| -          |

| _          |

| <          |

|            |

| ω          |

| N          |

|            |

| 4          |

| -          |

| ₽          |

| 5          |

| 0)         |

| ×          |

| ~          |

| $\sim$     |

| <b>U</b> 7 |

|            |

Pinouts and pin description

|        |      |                              | т          | able 17. Alternate fur           | nction AF8 to | AF15 <sup>(1)</sup> (contir      | nued)               |                          |          |

|--------|------|------------------------------|------------|----------------------------------|---------------|----------------------------------|---------------------|--------------------------|----------|

|        |      | AF8                          | AF9        | AF10                             | AF11          | AF12                             | AF13                | AF14                     | AF15     |

| P      | ort  | UART4/5/<br>LPUART1/<br>CAN2 | CAN1/TSC   | CAN2/<br>OTG_FS/DCMI/<br>QUADSPI | LCD           | SDMMC/<br>COMP1/2/FM<br>C/SWPMI1 | SAI1/2              | TIM2/15/16/17/<br>LPTIM2 | EVENOUT  |

|        | PB0  | -                            | -          | QUADSPI_BK1_IO1                  | LCD_SEG5      | COMP1_OUT                        | SAI1_EXTCLK         | -                        | EVENTOUT |

|        | PB1  | LPUART1_RT<br>S_DE           | -          | QUADSPI_BK1_IO0                  | LCD_SEG6      | -                                | -                   | LPTIM2_IN1               | EVENTOUT |

|        | PB2  | -                            | -          | -                                | LCD_VLCD      | -                                | -                   | -                        | EVENTOUT |

|        | PB3  | -                            | -          | OTG_FS_CRS_SYNC                  | LCD_SEG7      | -                                | SAI1_SCK_B          | -                        | EVENTOUT |

|        | PB4  | UART5_RTS_<br>DE             | TSC_G2_IO1 | DCMI_D12                         | LCD_SEG8      | -                                | SAI1_MCLK_B         | TIM17_BKIN               | EVENTOUT |

|        | PB5  | UART5_CTS                    | TSC_G2_IO2 | DCMI_D10                         | LCD_SEG9      | COMP2_OUT                        | SAI1_SD_B           | TIM16_BKIN               | EVENTOUT |

|        | PB6  | CAN2_TX                      | TSC_G2_IO3 | DCMI_D5                          | -             | TIM8_BKIN2_<br>COMP2             | SAI1_FS_B           | TIM16_CH1N               | EVENTOUT |

| Port B | PB7  | UART4_CTS                    | TSC_G2_IO4 | DCMI_VSYNC                       | LCD_SEG21     | FMC_NL                           | TIM8_BKIN_C<br>OMP1 | TIM17_CH1N               | EVENTOUT |

|        | PB8  | -                            | CAN1_RX    | DCMI_D6                          | LCD_SEG16     | SDMMC1_D4                        | SAI1_MCLK_A         | TIM16_CH1                | EVENTOUT |

|        | PB9  | -                            | CAN1_TX    | DCMI_D7                          | LCD_COM3      | SDMMC1_D5                        | SAI1_FS_A           | TIM17_CH1                | EVENTOUT |

|        | PB10 | LPUART1_RX                   | TSC_SYNC   | QUADSPI_CLK                      | LCD_SEG10     | COMP1_OUT                        | SAI1_SCK_A          | -                        | EVENTOUT |

|        | PB11 | LPUART1_TX                   | -          | QUADSPI_BK1_NCS                  | LCD_SEG11     | COMP2_OUT                        | -                   | -                        | EVENTOUT |

|        | PB12 | LPUART1_RT<br>S_DE           | TSC_G1_IO1 | CAN2_RX                          | LCD_SEG12     | SWPMI1_IO                        | SAI2_FS_A           | TIM15_BKIN               | EVENTOUT |

|        | PB13 | LPUART1_CT<br>S              | TSC_G1_IO2 | CAN2_TX                          | LCD_SEG13     | SWPMI1_TX                        | SAI2_SCK_A          | TIM15_CH1N               | EVENTOUT |

|        | PB14 | -                            | TSC_G1_IO3 | -                                | LCD_SEG14     | SWPMI1_RX                        | SAI2_MCLK_A         | TIM15_CH1                | EVENTOUT |

|        | PB15 | -                            | TSC_G1_IO4 | -                                | LCD_SEG15     | SWPMI1_SUS<br>PEND               | SAI2_SD_A           | TIM15_CH2                | EVENTOUT |

|        |      | •                            | •          |                                  | -             |                                  | •                   |                          |          |

DS11584 Rev 7

5

101/273

### Table 34. Typical current consumption in Run, with different codes running from Flash, ART enable (Cache ON Prefetch OFF) and power supplied (by external SMPS (V<sub>DD12</sub> = 1.05 V)

| (by | external | SMPS | $(v_{DD12} =$ | 1.05 V | ) |

|-----|----------|------|---------------|--------|---|

|     |          | (4)  |               |        |   |

|                     | Parameter         | Conditions <sup>(1)</sup>                                 |                        |                             |       |      | TYP   |        |

|---------------------|-------------------|-----------------------------------------------------------|------------------------|-----------------------------|-------|------|-------|--------|

| Symbol              |                   | -                                                         | Voltage<br>scaling     | Code                        | 25 °C | Unit | 25 °C | Unit   |

|                     |                   | $f_{HCLK} = f_{HSE}$ up to                                | Ν                      | Reduced code <sup>(2)</sup> | 1.04  |      | 40    |        |

|                     | Supply current in | 48 MHz included,<br>bypass mode PLL<br>ON above<br>48 MHz | <sub>LK</sub> = 26 MHz | Coremark                    | 1.17  |      | 45    | µA/MHz |

| I <sub>DD_ALL</sub> |                   |                                                           |                        | Dhrystone 2.1               | 1.22  | mA   | 47    |        |

| (Run)               | Run mode          |                                                           |                        | Fibonacci                   | 1.14  |      | 44    |        |

|                     |                   | all peripherals                                           |                        | While(1)                    | 0.96  |      | 37    |        |

1. All values are obtained by calculation based on measurements done without SMPS and using following parameters: SMPS input = 3.3 V, SMPS efficiency = 85%,  $V_{DD12}$  = 1.05 V

2. Reduced code used for characterization results provided in Table 26, Table 28, Table 30.

# Table 35. Typical current consumption in Run and Low-power run modes, with different codesrunning from Flash, ART disable

|                                |                                  |                                                                     | Conditio                              | ns                              | TYP   |      | TYP   |        |

|--------------------------------|----------------------------------|---------------------------------------------------------------------|---------------------------------------|---------------------------------|-------|------|-------|--------|

| Symbol                         | Parameter                        | -                                                                   | Voltage<br>scaling                    | Code                            | 25 °C | Unit | 25 °C | Unit   |

|                                |                                  |                                                                     | N<br>T                                | Reduced code <sup>(1)</sup>     | 3.1   |      | 119   |        |

| I <sub>DD_ALL</sub>            |                                  |                                                                     | s 2<br>5 MHz                          | Coremark                        | 2.85  |      | 110   |        |

|                                |                                  | f <sub>HCLK</sub> = f <sub>HSE</sub> up to                          | Range :<br>∟k = 26                    | Dhrystone 2.1                   | 2.86  | mA   | 110   | µA/MHz |

|                                | <b>a</b> .                       | 48 MHz included,                                                    | Ra<br>fHCLK                           | Fibonacci                       | 2.63  |      | 101   |        |

|                                | Supply<br>current in<br>Run mode | bypass mode<br>PLL ON above<br>48 MHz<br>all peripherals<br>disable | <sup>f</sup> HC                       | While(1)                        | 2.42  |      | 93.1  |        |

| (Run)                          |                                  |                                                                     | Range 1<br>f <sub>HCLK</sub> = 80 MHz | Reduced code <sup>(1)</sup>     | 10    |      | 125   | µA/MHz |

|                                |                                  |                                                                     |                                       | Coremark                        | 9.33  | mA   | 117   |        |

|                                |                                  |                                                                     |                                       | Dhrystone 2.1                   | 9.4   |      | 118   |        |

|                                |                                  |                                                                     |                                       | Fibonacci                       | 8.66  |      | 108   |        |

|                                |                                  |                                                                     | f <sub>H0</sub>                       | While(1)                        | 8.61  |      | 108   |        |

|                                |                                  |                                                                     |                                       | Reduced code <sup>(1)</sup> 378 |       |      | 189   |        |

|                                | Supply                           | £ _£ _0.M                                                           |                                       | Coremark                        | 412   |      | 206   | μA/MHz |

| I <sub>DD_ALL</sub><br>(LPRun) | current in<br>Low-power          | f <sub>HCLK</sub> = f <sub>MSI</sub> = 2 MI<br>all peripherals disa |                                       | Dhrystone 2.1                   | 418   | μA   | 209   |        |

| ()                             | run                              |                                                                     |                                       | Fibonacci                       | 392   |      | 196   |        |

|                                |                                  |                                                                     |                                       | While(1)                        | 266   |      | 133   |        |

1. Reduced code used for characterization results provided in Table 26, Table 28, Table 30.

|                                |                                                                                                          |                                                                     | anning n                            | rom SRAW1                   |       |      |       |        |  |

|--------------------------------|----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|-------------------------------------|-----------------------------|-------|------|-------|--------|--|

|                                |                                                                                                          |                                                                     | Conditio                            | ons                         | TYP   |      | TYP   |        |  |

| Symbol                         | Parameter                                                                                                | -                                                                   | Voltage<br>scaling                  | Code                        | 25 °C | Unit | 25 °C | Unit   |  |

|                                |                                                                                                          |                                                                     | 부                                   | Reduced code <sup>(1)</sup> | 2.72  |      | 105   |        |  |

|                                |                                                                                                          |                                                                     | : 2<br>3 MHz                        | Coremark                    | 2.72  |      | 105   |        |  |

|                                |                                                                                                          | f <sub>HCLK</sub> = f <sub>HSE</sub> up to                          | Range 2<br>f <sub>HCLK</sub> = 26 I | Dhrystone 2.1               | 2.65  | mA   | 102   | µA/MHz |  |

|                                |                                                                                                          | 48 MHz included,                                                    |                                     | Fibonacci                   | 2.47  |      | 95    |        |  |

| I <sub>DD ALL</sub>            | IDD_ALL<br>(Run)Supply<br>current in<br>Run modebypass mode<br>PLL ON above<br>48 MHz all<br>peripherals | fHc                                                                 | While(1)                            | 2.37                        |       | 91   |       |        |  |

| (Rūn)                          |                                                                                                          | e 1<br>D MHz                                                        | Reduced code <sup>(1)</sup>         | 9.71                        |       | 121  |       |        |  |

|                                |                                                                                                          |                                                                     | Coremark                            | 9.7                         |       | 121  |       |        |  |

|                                |                                                                                                          | disable                                                             | Range <sub>-</sub><br>LK = 80       | Dhrystone 2.1               | 9.48  | mA   | 119   | µA/MHz |  |

|                                |                                                                                                          |                                                                     | Ra<br>fhcLk <sup>1</sup>            | Fibonacci                   | 8.79  |      | 110   |        |  |

|                                |                                                                                                          |                                                                     | fHc                                 | While(1)                    | 8.45  |      | 106   |        |  |

|                                |                                                                                                          |                                                                     |                                     | Reduced code <sup>(1)</sup> | 258   |      | 129   |        |  |

|                                | Supply                                                                                                   | £ £ 0.14                                                            | 1_                                  | Coremark                    | 268   |      | 134   |        |  |

| I <sub>DD_ALL</sub><br>(LPRun) | current in<br>Low-power                                                                                  | f <sub>HCLK</sub> = f <sub>MSI</sub> = 2 MH<br>all peripherals disa |                                     | Dhrystone 2.1               | 240   | μA   | 120   | µA/MHz |  |

| (2 (01))                       | run                                                                                                      |                                                                     |                                     | Fibonacci                   | 230   |      | 115   |        |  |

|                                |                                                                                                          |                                                                     |                                     | While(1)                    | 255   |      | 128   |        |  |

# Table 38. Typical current consumption in Run and Low-power run modes, with different codesrunning from SRAM1

1. Reduced code used for characterization results provided in *Table 26*, *Table 28*, *Table 30*.

| Table 39. Typical current consumption in Run, with different codesrunning from |

|--------------------------------------------------------------------------------|

| SRAM1 and power supplied by external SMPS (V <sub>DD12</sub> = 1.10 V)         |

|         |                      | Co                                                                            | nditions <sup>(1)</sup> |                             | TYP   | _    | TYP   |        |  |

|---------|----------------------|-------------------------------------------------------------------------------|-------------------------|-----------------------------|-------|------|-------|--------|--|

| Symbol  | Parameter            | -                                                                             | Voltage<br>scaling      | Code                        | 25 °C | Unit | 25 °C | Unit   |  |

|         |                      |                                                                               | MHz                     | Reduced code <sup>(2)</sup> | 1.17  |      | 45    |        |  |

|         |                      |                                                                               | = 26 M                  | Coremark                    | 1.17  |      | 45    |        |  |

|         |                      | f <sub>HCLK</sub> = f <sub>HSE</sub> up to<br>48 MHz included,<br>bypass mode |                         | Dhrystone 2.1               | 1.14  | mA   | 44    |        |  |

|         |                      |                                                                               | fHCLK "                 | Fibonacci                   | 1.07  |      | 41    |        |  |

| IDD_ALL | Supply<br>current in |                                                                               | fHo                     | While(1)                    | 1.02  |      | 39    | µA/MHz |  |

| (Rūn)   | Run mode             | PLL ON above                                                                  | 주                       | Reduced code <sup>(1)</sup> | 3.49  | ШA   | 44    |        |  |

|         |                      | 48 MHz all peripherals disable                                                | 80 MHz                  | Coremark                    | 3.49  |      | 44    |        |  |

|         |                      |                                                                               | = 80                    | Dhrystone 2.1               | 3.41  |      | 43    |        |  |

|         |                      |                                                                               |                         | Fibonacci                   | 3.16  |      | 39    |        |  |

|         |                      |                                                                               | fнськ                   | While(1)                    | 3.04  |      | 38    |        |  |

All values are obtained by calculation based on measurements done without SMPS and using following parameters: SMPS input = 3.3 V, SMPS efficiency = 85%, V<sub>DD12</sub> = 1.10 V

2. Reduced code used for characterization results provided in *Table 26, Table 28, Table 30*.

| Table 40. Typical current consumption in Run, with different codesrunning from |

|--------------------------------------------------------------------------------|

| SRAM1 and power supplied by external SMPS (V <sub>DD12</sub> = 1.05 V)         |

|                              |            | Co                                         | nditions <sup>(1)</sup> |                             | ТҮР   |      | ТҮР   |        |

|------------------------------|------------|--------------------------------------------|-------------------------|-----------------------------|-------|------|-------|--------|

| Symbol                       | Parameter  | -                                          | Voltage<br>scaling      | Code                        | 25 °C | Unit | 25 °C | Unit   |

|                              |            | f <sub>HCLK</sub> = f <sub>HSE</sub> up to | MHz                     | Reduced code <sup>(2)</sup> | 1.07  |      | 41    |        |

|                              | Supply     | 48 MHz included,                           |                         | Coremark                    | 1.07  |      | 41    |        |

| I <sub>DD_ALL</sub><br>(Run) | current in | bypass mode<br>PLL ON above                | = 26                    | Dhrystone 2.1               | 1.04  | mA   | 40    | µA/MHz |

| (                            | Run mode   | 48 MHz all                                 | -<br>Носк               | Fibonacci                   | 0.97  |      | 37    |        |

|                              |            | peripherals disable                        | fHc                     | While(1)                    | 0.93  |      | 36    |        |

All values are obtained by calculation based on measurements done without SMPS and using following parameters: SMPS input = 3.3 V, SMPS efficiency = 85%, V<sub>DD12</sub> = 1.05 V

2. Reduced code used for characterization results provided in Table 26, Table 28, Table 30.

|                                  | Т                              | able 43. Cur   | rent con           | sumptior          | in Lov | v-powe | er sleep | modes  | , Flash | in pow | er-dowi | n                  |        |        |      |

|----------------------------------|--------------------------------|----------------|--------------------|-------------------|--------|--------|----------|--------|---------|--------|---------|--------------------|--------|--------|------|

|                                  |                                | Conditions     |                    |                   |        |        | ТҮР      |        |         |        |         | MAX <sup>(1)</sup> |        |        |      |

| Symbol                           | Parameter                      | -              | Voltage<br>scaling | f <sub>HCLK</sub> | 25 °C  | 55 °C  | 85 °C    | 105 °C | 125 °C  | 25 °C  | 55 °C   | 85 °C              | 105 °C | 125 °C | Unit |

|                                  |                                |                |                    |                   | 92.7   | 124    | 258      | 487    | 968     | 105    | 224     | 474                | 969    | 2006   |      |

| I <sub>DD_ALL</sub><br>(LPSleep) | Supply current<br>in low-power | THCLK = TMSI   |                    | 1 MHz             | 63.5   | 97.5   | 223      | 460    | 951     | 75     | 193     | 446                | 942    | 1975   | uА   |

| (LPSleep)                        | sleep mode                     | all peripheral | s disable          | 400 kHz           | 42.6   | 75.6   | 207      | 443    | 947     | 54     | 171     | 426                | 923    | 1955   | μΛ   |

|                                  |                                |                |                    | 100 kHz           | 31.2   | 67.6   | 199      | 437    | 905     | 44     | 162     | 420                | 916    | 1947   |      |

1. Guaranteed by characterization results, unless otherwise specified.

| 0             | Demonstern        | Conditions                                              | ТҮР      |       |       | MAX <sup>(1)</sup> |        |        |       |       |       |        |        |     |

|---------------|-------------------|---------------------------------------------------------|----------|-------|-------|--------------------|--------|--------|-------|-------|-------|--------|--------|-----|

| Symbol Parame | Parameter         | -                                                       | $V_{DD}$ | 25 °C | 55 °C | 85 °C              | 105 °C | 125 °C | 25 °C | 55 °C | 85 °C | 105 °C | 125 °C | Uni |

|               |                   |                                                         | 1.8 V    | 2.57  | 6.86  | 25.2               | 60.1   | 135    | 5.3   | 16.4  | 64    | 154.6  | 353    |     |

|               |                   | LCD disabled                                            | 2.4 V    | 2.62  | 6.91  | 25.5               | 60.6   | 137    | 5.3   | 16.6  | 64.9  | 156.7  | 359    |     |

|               |                   |                                                         | 3 V      | 2.69  | 6.93  | 25.7               | 61.5   | 140    | 5.4   | 16.9  | 66.3  | 159.7  | 366    | uA  |

|               | Supply current in |                                                         | 3.6 V    | 2.7   | 7.08  | 26.3               | 62.9   | 143    | 5.4   | 17.4  | 67.8  | 163.8  | 375    |     |

| (Stop 2)      | RTC disabled      | op 2 mode,<br>TC disabled<br>LCD enabled <sup>(2)</sup> | 1.8 V    | 2.92  | 7.19  | 25.3               | 59.5   | 135    | 5.3   | 16.6  | 64.8  | 155.6  | 355    | μΑ  |

|               |                   |                                                         | 2.4 V    | 2.99  | 7.3   | 25.6               | 60.3   | 136    | 5.5   | 16.8  | 65.9  | 157.9  | 360    |     |

|               | clocked by LSI    | 3 V                                                     | 3.04     | 7.41  | 26.1  | 61.7               | 140    | 5.9    | 17.3  | 67.1  | 160.8 | 367    |        |     |

|               |                   | 3.6 V                                                   | 3.31     | 7.7   | 26.8  | 63.2               | 143    | 6.2    | 17.9  | 69.1  | 165.0 | 376    |        |     |

#### Table 44. Current consumption in Stop 2 mode

138/273

### 6.3.9 PLL characteristics

The parameters given in *Table 62* are derived from tests performed under temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 22: General operating conditions*.

| Symbol                 | Parameter                      | Conditions              | Min    | Тур | Max | Unit  |  |

|------------------------|--------------------------------|-------------------------|--------|-----|-----|-------|--|

| £                      | PLL input clock <sup>(2)</sup> | -                       | 4      | -   | 16  | MHz   |  |

| f <sub>PLL_IN</sub>    | PLL input clock duty cycle     | -                       | 45     | -   | 55  | %     |  |

| f                      | PLL multiplier output clock P  | Voltage scaling Range 1 | 2.0645 | -   | 80  |       |  |

| <sup>f</sup> PLL_P_OUT |                                | Voltage scaling Range 2 | 2.0645 | -   | 26  | MHz   |  |

| f                      | PLL multiplier output clock Q  | Voltage scaling Range 1 | 8      | -   | 80  | MHz   |  |

| <sup>†</sup> PLL_Q_OUT |                                | Voltage scaling Range 2 | 8      | -   | 26  | IVIHZ |  |

| £                      | PLL multiplier output clock R  | Voltage scaling Range 1 | 8      | -   | 80  | MHz   |  |

| f <sub>PLL_R_OUT</sub> |                                | Voltage scaling Range 2 | 8      | -   | 26  |       |  |

| f                      | PLL VCO output                 | Voltage scaling Range 1 | 64     | -   | 344 | MHz   |  |

| fvco_out               |                                | Voltage scaling Range 2 | 64     | -   | 128 |       |  |

| t <sub>LOCK</sub>      | PLL lock time                  | -                       | -      | 15  | 40  | μs    |  |

| Jitter                 | RMS cycle-to-cycle jitter      | - System clock 80 MHz   | -      | 40  | -   | +00   |  |

| Jillei                 | RMS period jitter              |                         | -      | 30  | -   | ±ps   |  |

|                        |                                | VCO freq = 64 MHz       | -      | 150 | 200 |       |  |

|                        | PLL power consumption on       | VCO freq = 96 MHz       | -      | 200 | 260 |       |  |

| I <sub>DD</sub> (PLL)  | V <sub>DD</sub> <sup>(1)</sup> | VCO freq = 192 MHz      | -      | 300 | 380 | μA    |  |

|                        |                                | VCO freq = 344 MHz      | -      | 520 | 650 |       |  |

| Table 62. PLL, PLLSAI1, PLLSAI2 characteristics <sup>(1)</sup> | Table 62. PLL, | PLLSAI1. | PLLSAI2 | characteristics <sup>(1)</sup> |

|----------------------------------------------------------------|----------------|----------|---------|--------------------------------|

|----------------------------------------------------------------|----------------|----------|---------|--------------------------------|

1. Guaranteed by design.

2. Take care of using the appropriate division factor M to obtain the specified PLL input clock values. The M factor is shared between the 3 PLLs.

## 6.3.10 Flash memory characteristics

### Table 63. Flash memory characteristics<sup>(1)</sup>

| Symbol                              | Parameter               | Conditions         | Тур   | Max   | Unit |

|-------------------------------------|-------------------------|--------------------|-------|-------|------|

| t <sub>prog</sub>                   | 64-bit programming time | -                  | 81.69 | 90.76 | μs   |

| +                                   | one row (32 double      | normal programming | 2.61  | 2.90  |      |

| <sup>lprog_row</sup> word) programm | word) programming time  | fast programming   | 1.91  | 2.12  |      |

| +                                   | one page (2 Kbyte)      | normal programming | 20.91 | 23.24 | ms   |

| <sup>L</sup> prog_page              | programming time        | fast programming   | 15.29 | 16.98 |      |

| t <sub>ERASE</sub>                  | Page (2 KB) erase time  | -                  | 22.02 | 24.47 |      |

| t                                   | one bank (512 Kbyte)    | normal programming | 5.35  | 5.95  | s    |

| <sup>l</sup> prog_bank              | programming time        | fast programming   | 3.91  | 4.35  | 3    |

| Speed | Symbol | Parameter                 | Conditions                                 | Min | Max | Unit   |  |  |  |

|-------|--------|---------------------------|--------------------------------------------|-----|-----|--------|--|--|--|

|       |        |                           | C=50 pF, 2.7 V≤V <sub>DDIOx</sub> ≤3.6 V   | -   | 5   |        |  |  |  |

|       |        |                           | C=50 pF, 1.62 V≤V <sub>DDIOx</sub> ≤2.7 V  | -   | 1   |        |  |  |  |

|       | Fmax   | Maximum fraguanay         | C=50 pF, 1.08 V≤V <sub>DDIOx</sub> ≤1.62 V | -   | 0.1 | MHz    |  |  |  |

|       | FIIIdX | Maximum frequency         | C=10 pF, 2.7 V≤V <sub>DDIOx</sub> ≤3.6 V   | -   | 10  | IVILIZ |  |  |  |

|       |        |                           | C=10 pF, 1.62 V≤V <sub>DDIOx</sub> ≤2.7 V  | -   | 1.5 |        |  |  |  |

| 00    |        |                           | C=10 pF, 1.08 V≤V <sub>DDIOx</sub> ≤1.62 V | -   | 0.1 | 1      |  |  |  |

| 00    |        |                           | C=50 pF, 2.7 V≤V <sub>DDIOx</sub> ≤3.6 V   | -   | 25  |        |  |  |  |

|       |        |                           | C=50 pF, 1.62 V≤V <sub>DDIOx</sub> ≤2.7 V  | -   | 52  |        |  |  |  |

|       | Tr/Tf  | Output rise and fall time | C=50 pF, 1.08 V≤V <sub>DDIOx</sub> ≤1.62 V | -   | 140 | ns     |  |  |  |

|       | 11/11  |                           | C=10 pF, 2.7 V≤V <sub>DDIOx</sub> ≤3.6 V   | -   | 17  |        |  |  |  |

|       |        |                           | C=10 pF, 1.62 V≤V <sub>DDIOx</sub> ≤2.7 V  | -   | 37  |        |  |  |  |

|       |        |                           | C=10 pF, 1.08 V≤V <sub>DDIOx</sub> ≤1.62 V | -   | 110 |        |  |  |  |

|       |        |                           | C=50 pF, 2.7 V≤V <sub>DDIOx</sub> ≤3.6 V   | -   | 25  |        |  |  |  |

|       |        |                           | C=50 pF, 1.62 V≤V <sub>DDIOx</sub> ≤2.7 V  | -   | 10  |        |  |  |  |

|       | Fmax   | Maximum frequency         | C=50 pF, 1.08 V≤V <sub>DDIOx</sub> ≤1.62 V | -   | 1   | - MHz  |  |  |  |

|       | THIAN  | Maximum nequency          | C=10 pF, 2.7 V≤V <sub>DDIOx</sub> ≤3.6 V   | -   | 50  |        |  |  |  |

|       |        |                           | C=10 pF, 1.62 V≤V <sub>DDIOx</sub> ≤2.7 V  | -   | 15  |        |  |  |  |

| 01    |        |                           | C=10 pF, 1.08 V≤V <sub>DDIOx</sub> ≤1.62 V | -   | 1   |        |  |  |  |

| 01    |        |                           | C=50 pF, 2.7 V≤V <sub>DDIOx</sub> ≤3.6 V   | -   | 9   |        |  |  |  |

|       |        |                           | C=50 pF, 1.62 V≤V <sub>DDIOx</sub> ≤2.7 V  | -   | 16  | 1      |  |  |  |

|       | Tr/Tf  | Output rise and fall time | C=50 pF, 1.08 V≤V <sub>DDIOx</sub> ≤1.62 V | -   | 40  | 200    |  |  |  |

|       | 11/11  |                           | C=10 pF, 2.7 V≤V <sub>DDIOx</sub> ≤3.6 V   | -   | 4.5 | ns     |  |  |  |

|       |        |                           | C=10 pF, 1.62 V≤V <sub>DDIOx</sub> ≤2.7 V  | -   | 9   |        |  |  |  |

|       |        |                           | C=10 pF, 1.08 V≤V <sub>DDIOx</sub> ≤1.62 V | -   | 21  |        |  |  |  |

| Table 72. I/O AC char | racteristics <sup>(1)(2)</sup> |

|-----------------------|--------------------------------|

| Table 72. I/O AC char | racteristics                   |

- 2. The I/O analog switch voltage booster is enable when V<sub>DDA</sub> < 2.4 V (BOOSTEN = 1 in the SYSCFG\_CFGR1 when V<sub>DDA</sub> < 2.4V). It is disable when V<sub>DDA</sub>  $\geq$  2.4 V.

- 3. Fast channels are: PC0, PC1, PC2, PC3, PA0.

- 4. Slow channels are: all ADC inputs except the fast channels.

| Symbol                  | Parameter                                                            | Conditions                                                                                                                                                           |                                                                                                |            | Тур        | Мах | Unit  |  |

|-------------------------|----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|------------|------------|-----|-------|--|

| <u></u>                 | Gain margin                                                          | Normal mode                                                                                                                                                          | -                                                                                              | 13         | -          |     |       |  |

| GM                      |                                                                      | Low-power mode                                                                                                                                                       | -                                                                                              | 20         | -          | dB  |       |  |

| twakeup                 | Wake up time<br>from OFF state.                                      | Normal mode                                                                                                                                                          | $C_{LOAD} \le 50 \text{ pf},$<br>$R_{LOAD} \ge 4 \text{ k}\Omega$<br>follower<br>configuration | -          | 5          | 10  | 116   |  |

|                         |                                                                      | $\label{eq:Low-power mode} \begin{array}{l} C_{LOAD} \leq 50 \mbox{ pf}, \\ R_{LOAD} \geq 20 \mbox{ k}\Omega \\ \mbox{follower} \\ \mbox{configuration} \end{array}$ |                                                                                                | -          | 10         | 30  | - µs  |  |

|                         | OPAMP input<br>bias current                                          | General purpose input (all packages except UFBGA132 and UFBGA169 only)                                                                                               |                                                                                                | -          | -          | (3) |       |  |

| I <sub>bias</sub>       |                                                                      | Dedicated input<br>(UFBGA132 and<br>UFBGA169 only)                                                                                                                   | T <sub>J</sub> ≤ 75 °C                                                                         | -          | -          | 1   | nA    |  |

|                         |                                                                      |                                                                                                                                                                      | T <sub>J</sub> ≤ 85 °C                                                                         | -          | -          | 3   |       |  |

|                         |                                                                      |                                                                                                                                                                      | T <sub>J</sub> ≤ 105 °C                                                                        | -          | -          | 8   |       |  |

|                         |                                                                      |                                                                                                                                                                      | T <sub>J</sub> ≤ 125 °C                                                                        | -          | -          | 15  |       |  |

|                         | Non inverting<br>gain value                                          |                                                                                                                                                                      | -                                                                                              | -          | 2          | -   |       |  |

| PGA gain <sup>(2)</sup> |                                                                      |                                                                                                                                                                      |                                                                                                | -          | 4          | -   |       |  |

|                         |                                                                      |                                                                                                                                                                      |                                                                                                | -          | 8          | -   |       |  |

|                         |                                                                      |                                                                                                                                                                      |                                                                                                | -          | 16         | -   |       |  |

|                         | R2/R1 internal<br>resistance<br>values in PGA<br>mode <sup>(4)</sup> | PGA Gain = 2                                                                                                                                                         |                                                                                                | -          | 80/80      | -   | κΩ/κΩ |  |

| R <sub>network</sub>    |                                                                      | PGA Gain = 4                                                                                                                                                         |                                                                                                | -          | 120/<br>40 | -   |       |  |

|                         |                                                                      | PGA Gain = 8                                                                                                                                                         | -                                                                                              | 140/<br>20 | -          |     |       |  |

|                         |                                                                      | PGA Gain = 16                                                                                                                                                        | -                                                                                              | 150/<br>10 | -          |     |       |  |

| Delta R                 | Resistance<br>variation (R1 or<br>R2)                                | -                                                                                                                                                                    |                                                                                                | -15        | -          | 15  | %     |  |

| PGA gain error          | PGA gain error                                                       | -                                                                                                                                                                    |                                                                                                | -1         | -          | 1   | %     |  |

|                         | PGA bandwidth<br>for different non<br>inverting gain                 | Gain = 2                                                                                                                                                             | -                                                                                              | -          | GBW/<br>2  | -   | – MHz |  |

| PGA BW                  |                                                                      | Gain = 4                                                                                                                                                             | -                                                                                              | -          | GBW/<br>4  | -   |       |  |

|                         |                                                                      | Gain = 8                                                                                                                                                             | -                                                                                              | -          | GBW/<br>8  | -   |       |  |

|                         |                                                                      | Gain = 16 -                                                                                                                                                          |                                                                                                | -          | GBW/<br>16 | -   |       |  |

| Table 86. | OPAMP characteristics <sup>(1)</sup> | (continued) |

|-----------|--------------------------------------|-------------|

|           |                                      | (continueu) |

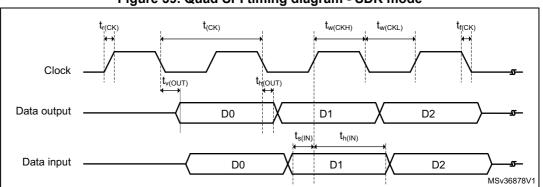

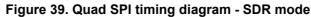

### Figure 40. Quad SPI timing diagram - DDR mode

# 7.5 WLCSP100 package information

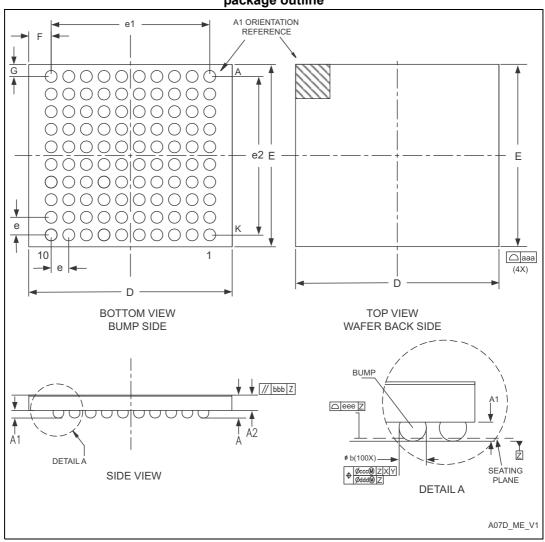

Figure 76.WLCSP – 100 ball, 4.618 x 4.142 mm, 0.4 mm pitch wafer level chip scale package outline

1. Drawing is not to scale.

- 2. Dimension is measured at the maximum bump diameter parallel to primary datum Z.

- 3. Primary datum Z and seating plane are defined by the spherical crowns of the bump.

- 4. Bump position designation per JESD 95-1, SPP-010.

| Symbol | millimeters |       |       | inches <sup>(1)</sup> |        |        |  |

|--------|-------------|-------|-------|-----------------------|--------|--------|--|

|        | Min         | Тур   | Мах   | Min                   | Тур    | Мах    |  |

| E3     | -           | 7.500 | -     | -                     | 0.2953 | -      |  |

| е      | -           | 0.500 | -     | -                     | 0.0197 | -      |  |

| К      | 0°          | 3.5°  | 7°    | 0°                    | 3.5°   | 7°     |  |

| L      | 0.450       | 0.600 | 0.750 | 0.0177                | 0.0236 | 0.0295 |  |

| L1     | -           | 1.000 | -     | -                     | 0.0394 | -      |  |

| CCC    | -           | -     | 0.080 | -                     | -      | 0.0031 |  |

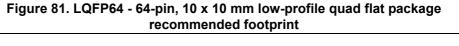

# Table 131. LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat package mechanical data (continued)

1. Values in inches are converted from mm and rounded to 4 decimal digits.

1. Dimensions are expressed in millimeters.

### **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

DS11584 Rev 7

The following examples show how to calculate the temperature range needed for a given application.

### Example 1: High-performance application

Assuming the following application conditions:

Maximum ambient temperature  $T_{Amax}$  = 82 °C (measured according to JESD51-2),  $I_{DDmax}$  = 50 mA,  $V_{DD}$  = 3.5 V, maximum 20 I/Os used at the same time in output at low level with  $I_{OL}$  = 8 mA,  $V_{OL}$ = 0.4 V and maximum 8 I/Os used at the same time in output at low level with  $I_{OL}$  = 20 mA,  $V_{OL}$ = 1.3 V

P<sub>INTmax</sub> = 50 mA × 3.5 V= 175 mW

P<sub>IOmax</sub> = 20 × 8 mA × 0.4 V + 8 × 20 mA × 1.3 V = 272 mW

This gives:  $P_{INTmax}$  = 175 mW and  $P_{IOmax}$  = 272 mW:

P<sub>Dmax</sub> = 175 + 272 = 447 mW

Using the values obtained in *Table 132*  $T_{Jmax}$  is calculated as follows:

– For LQFP100, 42 °C/W

T<sub>Jmax</sub> = 82 °C + (42 °C/W × 447 mW) = 82 °C + 18.774 °C = 100.774 °C

This is within the range of the suffix 6 version parts ( $-40 < T_J < 105$  °C) see Section 8: Ordering information.

In this case, parts must be ordered at least with the temperature range suffix 6 (see Part numbering).

Note: With this given  $P_{Dmax}$  we can find the  $T_{Amax}$  allowed for a given device temperature range (order code suffix 6 or 3).

Suffix 6:  $T_{Amax} = T_{Jmax} - (42^{\circ}C/W \times 447 \text{ mW}) = 105-18.774 = 86.226 ^{\circ}C$ Suffix 3:  $T_{Amax} = T_{Jmax} - (42^{\circ}C/W \times 447 \text{ mW}) = 130-18.774 = 111.226 ^{\circ}C$

### Example 2: High-temperature application

Using the same rules, it is possible to address applications that run at high ambient temperatures with a low dissipation, as long as junction temperature  $T_J$  remains within the specified range.

Assuming the following application conditions:

Maximum ambient temperature  $T_{Amax}$  = 100 °C (measured according to JESD51-2), I<sub>DDmax</sub> = 20 mA, V<sub>DD</sub> = 3.5 V, maximum 20 I/Os used at the same time in output at low level with I<sub>OL</sub> = 8 mA, V<sub>OL</sub>= 0.4 V

P<sub>INTmax</sub> = 20 mA × 3.5 V= 70 mW

$P_{IOmax} = 20 \times 8 \text{ mA} \times 0.4 \text{ V} = 64 \text{ mW}$

This gives:  $P_{INTmax}$  = 70 mW and  $P_{IOmax}$  = 64 mW:

```

P<sub>Dmax</sub> = 70 + 64 = 134 mW

```

Thus: P<sub>Dmax</sub> = 134 mW

Using the values obtained in *Table 132*  $T_{Jmax}$  is calculated as follows:

For LQFP100, 42 °C/W

T<sub>.lmax</sub> = 100 °C + (42 °C/W × 134 mW) = 100 °C + 5.628 °C = 105.628 °C

This is above the range of the suffix 6 version parts ( $-40 < T_{J} < 105 \text{ °C}$ ).