#### NXP USA Inc. - SPC5602DF1MLH4R Datasheet

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | e200z0h                                                                 |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 48MHz                                                                   |

| Connectivity               | CANbus, LINbus, SCI, SPI                                                |

| Peripherals                | DMA, POR, PWM, WDT                                                      |

| Number of I/O              | 45                                                                      |

| Program Memory Size        | 256KB (256K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 4K x 16                                                                 |

| RAM Size                   | 16K × 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                               |

| Data Converters            | A/D 16x12b                                                              |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 64-LQFP                                                                 |

| Supplier Device Package    | 64-LQFP (10x10)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/spc5602df1mlh4r |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1 Introduction

### 1.1 Document overview

This document describes the device features and highlights the important electrical and physical characteristics.

# 1.2 Description

These 32-bit automotive microcontrollers are a family of system-on-chip (SoC) devices designed to be central to the development of the next wave of central vehicle body controller, smart junction box, front module, peripheral body, door control and seat control applications.

This family is one of a series of next-generation integrated automotive microcontrollers based on the Power Architecture technology and designed specifically for embedded applications.

The advanced and cost-efficient e200z0h host processor core of this automotive controller family complies with the Power Architecture technology and only implements the VLE (variable-length encoding) APU (auxiliary processing unit), providing improved code density. It operates at speeds of up to 48 MHz and offers high performance processing optimized for low power consumption. It capitalizes on the available development infrastructure of current Power Architecture devices and is supported with software drivers, operating systems and configuration code to assist with the user's implementations.

The device platform has a single level of memory hierarchy and can support a wide range of on-chip static random access memory (SRAM) and internal flash memory.

| Feature                               | Device        |               |               |               |  |  |  |

|---------------------------------------|---------------|---------------|---------------|---------------|--|--|--|

| reature                               | MPC5601DxLH   | MPC5601DxLL   | MPC5602DxLH   | MPC5602DxLL   |  |  |  |

| CPU                                   |               | e20           | 0z0h          | I             |  |  |  |

| Execution speed                       |               | Static – up   | to 48 MHz     |               |  |  |  |

| Code flash memory                     | 128           | KB            | 256           | S KB          |  |  |  |

| Data flash memory                     |               | 64 KB (4      | × 16 KB)      |               |  |  |  |

| SRAM                                  | 12            | КВ            | 16            | KB            |  |  |  |

| eDMA                                  |               | 16            | ch            |               |  |  |  |

| ADC (12-bit)                          | 16 ch         | 16 ch 33 ch   |               | 33 ch         |  |  |  |

| СТU                                   |               | 16            | ch            | I             |  |  |  |

| Total timer I/O <sup>1</sup><br>eMIOS | 14 ch, 16-bit | 28 ch, 16-bit | 14 ch, 16-bit | 28 ch, 16-bit |  |  |  |

| • Type X <sup>2</sup>                 | 2 ch 5 ch     |               | 2 ch          | 5 ch          |  |  |  |

| • Type Y <sup>3</sup>                 | —             | 9 ch          | —             | 9 ch          |  |  |  |

| • Type G <sup>4</sup>                 | 7 ch          | 7 ch          | 7 ch          | 7 ch          |  |  |  |

| • Type H <sup>5</sup>                 | 4 ch          | 7 ch          | 4 ch          | 7 ch          |  |  |  |

| SCI (LINFlex)                         |               |               | 3             | I             |  |  |  |

| SPI (DSPI)                            |               |               | 2             |               |  |  |  |

| CAN (FlexCAN)                         |               |               | 1             |               |  |  |  |

| GPIO <sup>6</sup>                     | 45            | 79            | 45            | 79            |  |  |  |

#### Table 1. MPC5602D device comparison

MPC5602D Microcontroller Data Sheet, Rev. 6

| Block                                         | Function                                                                                                                                                                                                                         |

|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Real-time counter (RTC)                       | Provides a free-running counter and interrupt generation capability that can be used for timekeeping applications                                                                                                                |

| Reset generation module<br>(MC_RGM)           | Centralizes reset sources and manages the device reset sequence of the device                                                                                                                                                    |

| Static random-access memory (SRAM)            | Provides storage for program code, constants, and variables                                                                                                                                                                      |

| System integration unit lite (SIUL)           | Provides control over all the electrical pad controls and up 32 ports with 16 bits of bidirectional, general-purpose input and output signals and supports up to 32 external interrupts with trigger event configuration         |

| System status and configuration module (SSCM) | Provides system configuration and status data (such as memory size and status, device mode and security status), device identification data, debug status port enable and selection, and bus and peripheral abort enable/disable |

| System timer module (STM)                     | Provides a set of output compare events to support AUTOSAR (Automotive Open System Architecture) and operating system tasks                                                                                                      |

| Software watchdog timer (SWT)                 | Provides protection from runaway code                                                                                                                                                                                            |

| Wakeup unit (WKPU)                            | Supports up to 18 external sources that can generate interrupts or wakeup events, of which 1 can cause non-maskable interrupt requests or wakeup events.                                                                         |

Table 2. MPC5602D series block summary (continued)

# **3** Package pinouts and signal descriptions

### 3.1 Package pinouts

The available LQFP pinouts are provided in the following figures. For pin signal descriptions, please refer to Table 5.

|                    |         |                                    |                                            |                                    |                                   |             | T<br>ition             | Pin n   | umber    |

|--------------------|---------|------------------------------------|--------------------------------------------|------------------------------------|-----------------------------------|-------------|------------------------|---------|----------|

| Port pin           | PCR     | Alternate<br>function <sup>1</sup> | Function                                   | Peripheral                         | I/O<br>direction <sup>2</sup>     | Pad<br>type | RESET<br>configuration | 64 LQFP | 100 LQFP |

| PB[15]             | PCR[31] | AF0<br>AF1<br>AF2<br>AF3           | GPIO[31]<br>E0UC[7]<br>—<br>CS4_0          | SIUL<br>eMIOS_0<br>—<br>DSPI_0     | I/O<br>I/O<br>—<br>O              | J           | Tristate               | 42      | 67       |

|                    |         | —                                  | ADC1_X[3]                                  | ADC                                | I                                 |             |                        |         |          |

|                    |         |                                    |                                            | Port                               | С                                 |             |                        |         |          |

| PC[0] <sup>6</sup> | PCR[32] | AF0<br>AF1<br>AF2<br>AF3           | GPIO[32]<br>—<br>TDI<br>—                  | SIUL<br>—<br>JTAGC<br>—            | I/O<br>—<br>I<br>—                | М           | Input, weak<br>pull-up | 59      | 87       |

| PC[1] <sup>6</sup> | PCR[33] | AF0<br>AF1<br>AF2<br>AF3           | GPIO[33]<br><br>TDO<br>                    | SIUL<br>—<br>JTAGC<br>—            | I/O<br>—<br>—<br>—                | F           | Tristate               | 54      | 82       |

| PC[2]              | PCR[34] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[34]<br>SCK_1<br>—<br>EIRQ[5]          | SIUL<br>DSPI_1<br>—<br>SIUL        | I/O<br>I/O<br>—<br>I              | Μ           | Tristate               | 50      | 78       |

| PC[3]              | PCR[35] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[35]<br>CS0_1<br>MA[0]<br>—<br>EIRQ[6] | SIUL<br>DSPI_1<br>ADC<br>—<br>SIUL | I/O<br>I/O<br>O<br>I              | S           | Tristate               | 49      | 77       |

| PC[4]              | PCR[36] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[36]<br>—<br>—<br>SIN_1<br>EIRQ[18]    | SIUL<br>—<br>—<br>DSPI_1<br>SIUL   | I/O<br>—<br>—<br>—<br>—<br>—<br>— | Μ           | Tristate               | 62      | 92       |

| PC[5]              | PCR[37] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[37]<br>SOUT_1<br>—<br>EIRQ[7]         | SIUL<br>DSPI_1<br>—<br>SIUL        | I/O<br>O<br>—<br>I                | М           | Tristate               | 61      | 91       |

| PC[6]              | PCR[38] | AF0<br>AF1<br>AF2<br>AF3           | GPIO[38]<br>LIN1TX<br>—<br>—               | SIUL<br>LINFlex_1<br>—             | I/O<br>O<br>—                     | S           | Tristate               | 16      | 25       |

Table 5. Functional port pin descriptions (continued)

#### Package pinouts and signal descriptions

|          |         |                                    |                                                                  |                                                |                                |             | T<br>ttion             | Pin n   | umber    |

|----------|---------|------------------------------------|------------------------------------------------------------------|------------------------------------------------|--------------------------------|-------------|------------------------|---------|----------|

| Port pin | PCR     | Alternate<br>function <sup>1</sup> | Function                                                         | Peripheral                                     | I/O<br>direction <sup>2</sup>  | Pad<br>type | RESET<br>configuration | 64 LQFP | 100 LQFP |

| PC[7]    | PCR[39] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[39]<br>—<br>—<br>LIN1RX<br>WKPU[12] <sup>3</sup>            | SIUL<br>—<br>—<br>LINFlex_1<br>WKPU            | I/O<br>—<br>—<br>—<br>I<br>I   | S           | Tristate               | 17      | 26       |

| PC[8]    | PCR[40] | AF0<br>AF1<br>AF2<br>AF3           | GPIO[40]<br>LIN2TX<br>E0UC[3]<br>—                               | SIUL<br>LINFlex_2<br>eMIOS_0<br>—              | I/O<br>O<br>I/O<br>—           | S           | Tristate               | 63      | 99       |

| PC[9]    | PCR[41] | AF0<br>AF1<br>AF2<br>AF3<br>—<br>— | GPIO[41]<br>—<br>E0UC[7]<br>—<br>LIN2RX<br>WKPU[13] <sup>3</sup> | SIUL<br>—<br>eMIOS_0<br>—<br>LINFlex_2<br>WKPU | I/O<br>—<br>I/O<br>—<br>I<br>I | S           | Tristate               | 2       | 2        |

| PC[10]   | PCR[42] | AF0<br>AF1<br>AF2<br>AF3           | GPIO[42]<br>—<br>—<br>MA[1]                                      | SIUL<br>—<br>ADC                               | I/O<br>—<br>—<br>O             | М           | Tristate               | 13      | 22       |

| PC[11]   | PCR[43] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[43]<br>—<br>—<br>MA[2]<br>WKPU[5] <sup>3</sup>              | SIUL<br>—<br>ADC<br>WKPU                       | I/O<br>—<br>—<br>—<br>0<br>I   | S           | Tristate               | _       | 21       |

| PC[12]   | PCR[44] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[44]<br>E0UC[12]<br><br>EIRQ[19]                             | SIUL<br>eMIOS_0<br>—<br>SIUL                   | I/O<br>I/O<br>—<br>I           | М           | Tristate               | _       | 97       |

| PC[13]   | PCR[45] | AF0<br>AF1<br>AF2<br>AF3           | GPIO[45]<br>E0UC[13]<br>—                                        | SIUL<br>eMIOS_0<br>—                           | I/O<br>I/O<br>—                | S           | Tristate               | _       | 98       |

| PC[14]   | PCR[46] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[46]<br>E0UC[14]<br><br>EIRQ[8]                              | SIUL<br>eMIOS_0<br>—<br>SIUL                   | I/O<br>I/O<br>—<br>I           | S           | Tristate               | _       | 3        |

| PC[15]   | PCR[47] | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[47]<br>E0UC[15]<br><br>EIRQ[20]                             | SIUL<br>eMIOS_0<br>—<br>SIUL                   | I/O<br>I/O<br>—<br>I           | Μ           | Tristate               | _       | 4        |

Table 5. Functional port pin descriptions (continued)

<sup>6</sup> Out of reset all the functional pins except PC[0:1] and PH[9:10] are available to the user as GPIO.

PC[0:1] are available as JTAG pins (TDI and TDO respectively).

PH[9:10] are available as JTAG pins (TCK and TMS respectively).

If the user configures these JTAG pins in GPIO mode the device is no longer compliant with IEEE 1149.1 2001.

# 4 Electrical characteristics

### 4.1 Introduction

This section contains electrical characteristics of the device as well as temperature and power considerations.

This product contains devices to protect the inputs against damage due to high static voltages. However, it is advisable to take precautions to avoid application of any voltage higher than the specified maximum rated voltages.

To enhance reliability, unused inputs can be driven to an appropriate logic voltage level ( $V_{DD}$  or  $V_{SS}$ ). This can be done by the internal pull-up or pull-down, which is provided by the product for most general purpose pins.

The parameters listed in the following tables represent the characteristics of the device and its demands on the system.

In the tables where the device logic provides signals with their respective timing characteristics, the symbol "CC" for Controller Characteristics is included in the Symbol column.

In the tables where the external system must provide signals with their respective timing characteristics to the device, the symbol "SR" for System Requirement is included in the Symbol column.

## 4.2 Parameter classification

The electrical parameters shown in this supplement are guaranteed by various methods. To give the customer a better understanding, the classifications listed in Table 6 are used and the parameters are tagged accordingly in the tables where appropriate.

| Classification tag | Tag description                                                                                                                                                                                                        |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Р                  | Those parameters are guaranteed during production testing on each individual device.                                                                                                                                   |

| С                  | Those parameters are achieved by the design characterization by measuring a statistically relevant sample size across process variations.                                                                              |

| Т                  | Those parameters are achieved by design characterization on a small sample size from typical devices under typical conditions unless otherwise noted. All values shown in the typical column are within this category. |

| D                  | Those parameters are derived mainly from simulations.                                                                                                                                                                  |

#### Table 6. Parameter classifications

#### NOTE

The classification is shown in the column labeled "C" in the parameter tables where appropriate.

## 4.3 NVUSRO register

Bit values in the Non-Volatile User Options (NVUSRO) Register control portions of the device configuration, namely electrical parameters such as high voltage supply and oscillator margin, as well as digital functionality (watchdog enable/disable after reset).

For a detailed description of the NVUSRO register, please refer to the device reference manual.

## 4.3.1 NVUSRO[PAD3V5V] field description

The DC electrical characteristics are dependent on the PAD3V5V bit value. Table 7 shows how NVUSRO[PAD3V5V] controls the device configuration.

| Value <sup>1</sup> | Description                  |

|--------------------|------------------------------|

| 0                  | High voltage supply is 5.0 V |

| 1                  | High voltage supply is 3.3 V |

#### Table 7. PAD3V5V field description

Default manufacturing value is '1'. Value can be programmed by customer in Shadow Flash.

### 4.3.2 NVUSRO[OSCILLATOR\_MARGIN] field description

The fast external crystal oscillator consumption is dependent on the OSCILLATOR\_MARGIN bit value. Table 8 shows how NVUSRO[OSCILLATOR\_MARGIN] controls the device configuration.

#### Table 8. OSCILLATOR\_MARGIN field description

| Value <sup>1</sup> | Description                                 |

|--------------------|---------------------------------------------|

| 0                  | Low consumption configuration (4 MHz/8 MHz) |

| 1                  | High margin configuration (4 MHz/16 MHz)    |

Default manufacturing value is '1'. Value can be programmed by customer in Shadow Flash.

### 4.3.3 NVUSRO[WATCHDOG\_EN] field description

The watchdog enable/disable configuration after reset is dependent on the WATCHDOG\_EN bit value. Table 8 shows how NVUSRO[WATCHDOG\_EN] controls the device configuration.

#### Table 9. WATCHDOG\_EN field description

| Value <sup>1</sup> | Description          |

|--------------------|----------------------|

| 0                  | Disable after reset) |

| 1                  | Enable after reset   |

<sup>1</sup> Default manufacturing value is '1'. Value can be programmed by customer in Shadow Flash.

## 4.4 Absolute maximum ratings

#### Table 10. Absolute maximum ratings

| Symbol             |    | Parameter                                                                                     | Conditions | Va                    | Unit                  |      |

|--------------------|----|-----------------------------------------------------------------------------------------------|------------|-----------------------|-----------------------|------|

| Gymbe              | ,, | i arameter                                                                                    | Conditions | Min                   | 0                     | Onit |

| V <sub>SS</sub>    | SR | Digital ground on VSS_HV pins                                                                 | _          | 0                     | 0                     | V    |

| V <sub>DD</sub>    |    | Voltage on VDD_HV pins with respect to ground (V <sub>SS</sub> )                              | _          | -0.3                  | 6.0                   | V    |

| V <sub>SS_LV</sub> | SR | Voltage on VSS_LV (low voltage digital supply) pins with respect to ground (V <sub>SS</sub> ) | _          | V <sub>SS</sub> – 0.1 | V <sub>SS</sub> + 0.1 | V    |

| Sumbo                |    | Deremeter                                                                           | O an altheory                              | Va                   | Unit                  |      |

|----------------------|----|-------------------------------------------------------------------------------------|--------------------------------------------|----------------------|-----------------------|------|

| Symbo                |    | Parameter                                                                           | Conditions                                 | Min                  | Max                   | Onit |

| V <sub>DD_BV</sub>   |    | Voltage on VDD_BV (regulator supply) pin                                            | _                                          | -0.3                 | 6.0                   | V    |

|                      |    | with respect to ground $(V_{SS})$                                                   | Relative to V <sub>DD</sub>                | $V_{DD} - 0.3$       | V <sub>DD</sub> + 0.3 |      |

| V <sub>SS_ADC</sub>  |    | Voltage on VSS_HV_ADC (ADC reference) pin with respect to ground (V <sub>SS</sub> ) | _                                          | V <sub>SS</sub> -0.1 | V <sub>SS</sub> + 0.1 | V    |

| V <sub>DD_ADC</sub>  |    | Voltage on VDD_HV_ADC (ADC                                                          | —                                          | -0.3                 | 6.0                   | V    |

|                      |    | reference) pin with respect to ground ( $V_{SS}$ )                                  | Relative to V <sub>DD</sub>                | $V_{DD} - 0.3$       | V <sub>DD</sub> + 0.3 |      |

| V <sub>IN</sub> SR   |    | R Voltage on any GPIO pin with respect to ground (V <sub>SS</sub> )                 | —                                          | -0.3                 | 6.0                   | V    |

|                      |    |                                                                                     | Relative to V <sub>DD</sub>                | $V_{DD}-0.3$         | V <sub>DD</sub> + 0.3 |      |

| I <sub>INJPAD</sub>  |    | Injected input current on any pin during overload condition                         | _                                          | -10                  | 10                    | mA   |

| I <sub>INJSUM</sub>  |    | Absolute sum of all injected input currents during overload condition               | _                                          | -50                  | 50                    | mA   |

| I <sub>AVGSEG</sub>  |    | Sum of all the static I/O current within a                                          | V <sub>DD</sub> = 5.0 V ± 10%, PAD3V5V = 0 | —                    | 70                    | mA   |

|                      |    | supply segment <sup>1</sup>                                                         | V <sub>DD</sub> = 3.3 V ± 10%, PAD3V5V = 1 | —                    | 64                    |      |

| ICORELV              | SR | Low voltage static current sink through VDD_BV                                      | _                                          |                      | 150                   | mA   |

| T <sub>STORAGE</sub> | SR | Storage temperature                                                                 | _                                          | -55                  | 150                   | °C   |

<sup>1</sup> Supply segments are described in Section 4.7.5, I/O pad current specification.

#### NOTE

Stresses exceeding the recommended absolute maximum ratings may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification are not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. During overload conditions ( $V_{IN} > V_{DD}$  or  $V_{IN} < V_{SS}$ ), the voltage on pins with respect to ground ( $V_{SS}$ ) must not exceed the recommended values.

## 4.5 Recommended operating conditions

| Symbol | C | Parameter | er Conditions | Va  | lue |

|--------|---|-----------|---------------|-----|-----|

| Symbol | C | Falameter |               | Min | Ν   |

#### Table 11. Recommended operating conditions (3.3 V)

|                                 |    |   |                                                                                                  |   | Min                   | Мах                   |   |

|---------------------------------|----|---|--------------------------------------------------------------------------------------------------|---|-----------------------|-----------------------|---|

| V <sub>SS</sub>                 | SR | — | Digital ground on VSS_HV pins                                                                    | _ | 0                     | 0                     | V |

| V <sub>DD</sub> <sup>1</sup>    | SR | _ | Voltage on VDD_HV pins with respect to ground (V <sub>SS</sub> )                                 | — | 3.0                   | 3.6                   | V |

| V <sub>SS_LV</sub> <sup>2</sup> | SR |   | Voltage on VSS_LV (low voltage digital supply)<br>pins with respect to ground (V <sub>SS</sub> ) | _ | V <sub>SS</sub> - 0.1 | V <sub>SS</sub> + 0.1 | V |

Unit

| Symbo                           |    | С | Parameter                                                                              | Conditions                   | Va                   | lue                   | Unit |

|---------------------------------|----|---|----------------------------------------------------------------------------------------|------------------------------|----------------------|-----------------------|------|

| Symbo                           | 1  | C | Falameter                                                                              |                              |                      | Max                   | Unit |

| V <sub>DD_BV</sub> <sup>3</sup> | SR | — | Voltage on VDD_BV pin (regulator supply) with                                          | —                            | 3.0                  | 3.6                   | V    |

|                                 |    |   | respect to ground (V <sub>SS</sub> )                                                   | Relative to V <sub>DD</sub>  | $V_{DD} - 0.1$       | V <sub>DD</sub> + 0.1 |      |

| $V_{SS\_ADC}$                   | SR |   | Voltage on VSS_HV_ADC (ADC reference) pin<br>with respect to ground (V <sub>SS</sub> ) | —                            | V <sub>SS</sub> -0.1 | V <sub>SS</sub> + 0.1 | V    |

| $V_{\text{DD}\_\text{ADC}}{}^4$ | SR | — | Voltage on VDD_HV_ADC pin (ADC reference)                                              | _                            | 3.0 <sup>5</sup>     | 3.6                   | V    |

|                                 |    |   | with respect to ground ( $V_{SS}$ )                                                    | Relative to V <sub>DD</sub>  | $V_{DD} - 0.1$       | V <sub>DD</sub> + 0.1 |      |

| V <sub>IN</sub>                 | SR |   | Voltage on any GPIO pin with respect to ground                                         | —                            | $V_{SS} - 0.1$       | —                     | V    |

|                                 |    |   | (V <sub>SS</sub> )                                                                     | Relative to $V_{DD}$         | —                    | V <sub>DD</sub> + 0.1 |      |

| I <sub>INJPAD</sub>             | SR |   | Injected input current on any pin during overload condition                            | —                            | -5                   | 5                     | mA   |

| I <sub>INJSUM</sub>             | SR |   | Absolute sum of all injected input currents during overload condition                  | —                            | -50                  | 50                    | mA   |

| $TV_DD$                         | SR | _ | V <sub>DD</sub> slope to ensure correct power up <sup>6</sup>                          | _                            | —                    | 0.25                  | V/µs |

| T <sub>A C-Grade</sub><br>Part  | SR | _ | Ambient temperature under bias                                                         | $f_{CPU} \le 48 \text{ MHz}$ | -40                  | 85                    | °C   |

| T <sub>J C-Grade</sub><br>Part  | SR | _ | Junction temperature under bias                                                        |                              | -40                  | 110                   |      |

| T <sub>A V</sub> -Grade<br>Part | SR | — | Ambient temperature under bias                                                         |                              | -40                  | 105                   |      |

| T <sub>J V</sub> -Grade<br>Part | SR | — | Junction temperature under bias                                                        |                              | -40                  | 130                   |      |

| T <sub>A M</sub> -Grade<br>Part | SR | — | Ambient temperature under bias                                                         | 1                            | -40                  | 125                   |      |

| T <sub>J M</sub> -Grade<br>Part | SR |   | Junction temperature under bias                                                        |                              | -40                  | 150                   |      |

Table 11. Recommended operating conditions (3.3 V) (continued)

<sup>1</sup> 100 nF capacitance needs to be provided between each V<sub>DD</sub>/V<sub>SS</sub> pair.

<sup>2</sup> 330 nF capacitance needs to be provided between each V<sub>DD\_LV</sub>/V<sub>SS\_LV</sub> supply pair.

<sup>3</sup> 470 nF capacitance needs to be provided between V<sub>DD\_BV</sub> and the nearest V<sub>SS\_LV</sub> (higher value may be needed depending on external regulator characteristics).

$^4$  100 nF capacitance needs to be provided between  $V_{DD\_ADC}/V_{SS\_ADC}$  pair.

<sup>5</sup> Full electrical specification cannot be guaranteed when voltage drops below 3.0 V. In particular, ADC electrical characteristics and I/Os DC electrical specification may not be guaranteed. When voltage drops below V<sub>LVDHVL</sub>, device is reset.

<sup>6</sup> Guaranteed by device validation

| Γ | Symbol             |   | Parameter                     | Conditions | Val | Unit |      |

|---|--------------------|---|-------------------------------|------------|-----|------|------|

|   | Symbol             | C | i didificiti                  | Conditions | Min | Мах  | onic |

|   | V <sub>SS</sub> SR |   | Digital ground on VSS_HV pins | _          | 0   | 0    | V    |

| Table 12. Recommended operating condition | ons (5.0 V) |

|-------------------------------------------|-------------|

|-------------------------------------------|-------------|

|        |                      | 100 LQFF | P/64 LQFP |         |

|--------|----------------------|----------|-----------|---------|

| Pad    | Weigl                | nt 5 V   | Weigh     | t 3.3 V |

|        | SRC <sup>2</sup> = 0 | SRC = 1  | SRC = 0   | SRC = 1 |

| PB[3]  | 9%                   | 9%       | 10%       | 10%     |

| PC[9]  | 8%                   | 8%       | 10%       | 10%     |

| PC[14] | 8%                   | 8%       | 10%       | 10%     |

| PC[15] | 8%                   | 11%      | 9%        | 10%     |

| PA[2]  | 8%                   | 8%       | 9%        | 9%      |

| PE[0]  | 7%                   | 7%       | 9%        | 9%      |

| PA[1]  | 7%                   | 7%       | 8%        | 8%      |

| PE[1]  | 7%                   | 10%      | 8%        | 8%      |

| PE[8]  | 6%                   | 9%       | 8%        | 8%      |

| PE[9]  | 6%                   | 6%       | 7%        | 7%      |

| PE[10] | 6%                   | 6%       | 7%        | 7%      |

| PA[0]  | 5%                   | 7%       | 6%        | 7%      |

| PE[11] | 5%                   | 5%       | 6%        | 6%      |

| PC[11] | 7%                   | 7%       | 9%        | 9%      |

| PC[10] | 8%                   | 11%      | 9%        | 10%     |

| PB[0]  | 8%                   | 11%      | 9%        | 10%     |

| PB[1]  | 8%                   | 8%       | 10%       | 10%     |

| PC[6]  | 8%                   | 8%       | 10%       | 10%     |

| PC[7]  | 8%                   | 8%       | 10%       | 10%     |

| PA[15] | 8%                   | 11%      | 9%        | 10%     |

| PA[14] | 7%                   | 11%      | 9%        | 9%      |

| PA[4]  | 7%                   | 7%       | 8%        | 8%      |

| PA[13] | 7%                   | 10%      | 8%        | 9%      |

| PA[12] | 7%                   | 7%       | 8%        | 8%      |

| PB[9]  | 1%                   | 1%       | 1%        | 1%      |

| PB[8]  | 1%                   | 1%       | 1%        | 1%      |

| PB[10] | 5%                   | 5%       | 6%        | 6%      |

| PD[0]  | 1%                   | 1%       | 1%        | 1%      |

| PD[1]  | 1%                   | 1%       | 1%        | 1%      |

| PD[2]  | 1%                   | 1%       | 1%        | 1%      |

| PD[3]  | 1%                   | 1%       | 1%        | 1%      |

| PD[4]  | 1%                   | 1%       | 1%        | 1%      |

Table 21. I/O weight<sup>1</sup>

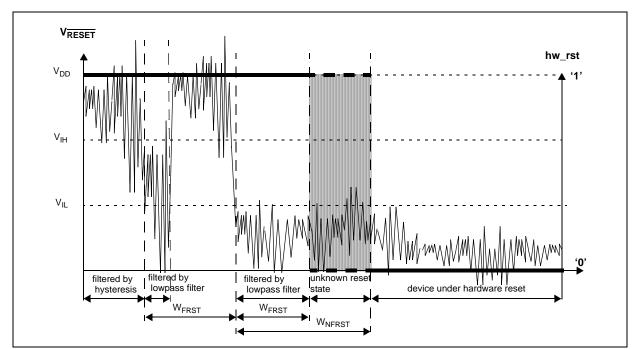

Figure 6. Noise filtering on reset signal

| Symb             |    | ol C Parameter |                                            | Conditions <sup>1</sup>                                                                             |                     | Value |                       | Unit |

|------------------|----|----------------|--------------------------------------------|-----------------------------------------------------------------------------------------------------|---------------------|-------|-----------------------|------|

| Cynis            |    |                |                                            | Conditions                                                                                          | Min                 | Тур   | Мах                   | onn  |

| V <sub>IH</sub>  | SR | Ρ              | Input High Level CMOS<br>(Schmitt Trigger) | _                                                                                                   | 0.65V <sub>DD</sub> | _     | V <sub>DD</sub> + 0.4 | V    |

| V <sub>IL</sub>  | SR | Ρ              | Input low Level CMOS<br>(Schmitt Trigger)  | _                                                                                                   | -0.4                | _     | 0.35V <sub>DD</sub>   | V    |

| V <sub>HYS</sub> | СС | С              | Input hysteresis CMOS<br>(Schmitt Trigger) | _                                                                                                   | 0.1V <sub>DD</sub>  | _     | —                     | V    |

| V <sub>OL</sub>  | СС | Ρ              | Output low level                           | Push Pull, $I_{OL} = 2 \text{ mA}$ ,<br>V <sub>DD</sub> = 5.0 V ± 10%, PAD3V5V = 0<br>(recommended) | —                   | —     | 0.1V <sub>DD</sub>    | V    |

|                  |    |                |                                            | Push Pull, $I_{OL} = 1 \text{ mA}$ ,<br>V <sub>DD</sub> = 5.0 V ± 10%, PAD3V5V = 1 <sup>2</sup>     | —                   | _     | 0.1V <sub>DD</sub>    |      |

|                  |    |                |                                            | Push Pull, $I_{OL} = 1 \text{ mA}$ ,<br>V <sub>DD</sub> = 3.3 V ± 10%, PAD3V5V = 1<br>(recommended) | —                   | _     | 0.5                   |      |

Table 22. Reset electrical characteristics

| Symbol                 | Symbol |   | Parameter                                   | Conditions <sup>1</sup> |      | Value |      | Unit  |

|------------------------|--------|---|---------------------------------------------|-------------------------|------|-------|------|-------|

| Cymber                 |        | С | , arantetor                                 | Contaitions             | Min  | Тур   | Мах  | 01111 |

| V <sub>PORUP</sub>     | SR     | Ρ | Supply for functional POR module            | T <sub>A</sub> = 25 °C, | 1.0  |       | 5.5  | V     |

| V <sub>PORH</sub>      | СС     | Ρ | Power-on reset threshold                    | after trimming          | 1.5  |       | 2.6  | V     |

| V <sub>LVDHV3H</sub>   | СС     | Т | LVDHV3 low voltage detector high threshold  |                         |      |       | 2.95 | V     |

| V <sub>LVDHV3L</sub>   | СС     | Ρ | LVDHV3 low voltage detector low threshold   |                         | 2.6  |       | 2.9  | V     |

| V <sub>LVDHV3BH</sub>  | СС     | Ρ | LVDHV3B low voltage detector high threshold |                         |      |       | 2.95 | V     |

| V <sub>LVDHV3BL</sub>  | СС     | Ρ | LVDHV3B low voltage detector low threshold  |                         | 2.6  |       | 2.9  | V     |

| V <sub>LVDHV5H</sub>   | СС     | Т | LVDHV5 low voltage detector high threshold  |                         |      |       | 4.5  | V     |

| V <sub>LVDHV5L</sub>   | СС     | Ρ | LVDHV5 low voltage detector low threshold   |                         | 3.8  |       | 4.4  | V     |

| V <sub>LVDLVCORL</sub> | СС     | Ρ | LVDLVCOR low voltage detector low threshold |                         | 1.08 | —     | 1.16 | V     |

| V <sub>LVDLVBKPL</sub> | СС     | Ρ | LVDLVBKP low voltage detector low threshold |                         | 1.08 |       | 1.16 | V     |

Table 24. Low voltage detector electrical characteristics

$^{1}$  V<sub>DD</sub> = 3.3 V ± 10% / 5.0 V ± 10%, T<sub>A</sub> = -40 to 125 °C, unless otherwise specified

### 4.10 Power consumption

Table 25 provides DC electrical characteristics for significant application modes. These values are indicative values; actual consumption depends on the application.

| Table 25. Power consumption on VDD_BV and VDD_HV | Table 25 | . Power | consumption | on VDD_E | 3V and VDD_H | V |

|--------------------------------------------------|----------|---------|-------------|----------|--------------|---|

|--------------------------------------------------|----------|---------|-------------|----------|--------------|---|

| Symbol                          |    | с | Parameter                           | Conditions <sup>1</sup>     |                         |     | Value |                   | Unit |

|---------------------------------|----|---|-------------------------------------|-----------------------------|-------------------------|-----|-------|-------------------|------|

| Gymbol                          |    | Ŭ | i didineter                         | Conditions                  |                         | Min | Тур   | Max               | onn  |

| I <sub>DDMAX</sub> <sup>2</sup> | СС | D | RUN mode maximum<br>average current | _                           |                         | _   | 90    | 130 <sup>3</sup>  | mA   |

| I <sub>DDRUN</sub> 4            | СС | Т | RUN mode typical                    | f <sub>CPU</sub> = 8 MHz    |                         |     | 7     | —                 | mA   |

|                                 |    | Т | average current <sup>5</sup>        | f <sub>CPU</sub> = 16 MHz   |                         | _   | 18    |                   |      |

|                                 |    | Т |                                     | f <sub>CPU</sub> = 32 MHz   |                         | _   | 29    |                   |      |

|                                 |    | Ρ |                                     | f <sub>CPU</sub> = 48 MHz   |                         | _   | 40    | 100               |      |

| IDDHALT                         | СС | С | HALT mode current <sup>6</sup>      |                             | T <sub>A</sub> = 25 °C  | _   | 8     | 15                | mA   |

|                                 |    | Ρ |                                     | (128 kHz) running           | T <sub>A</sub> = 125 °C | _   | 14    | 25                |      |

| IDDSTOP                         | СС | Ρ | STOP mode current <sup>7</sup>      | Slow internal RC oscillator | T <sub>A</sub> = 25 °C  | _   | 180   | 700 <sup>8</sup>  | μA   |

|                                 |    | D |                                     | (128 kHz) running           | T <sub>A</sub> = 55 °C  |     | 500   | —                 |      |

|                                 |    | D |                                     |                             | T <sub>A</sub> = 85 °C  | _   | 1     | 6 <sup>(8)</sup>  | mA   |

|                                 |    | D |                                     |                             | T <sub>A</sub> = 105 °C | —   | 2     | 9 <sup>(8)</sup>  |      |

|                                 |    | Ρ |                                     |                             | T <sub>A</sub> = 125 °C | _   | 4.5   | 12 <sup>(8)</sup> |      |

| Symbol               |    | с                       | Parameter                         | Conditions <sup>1</sup> |                         |     | Value |      | Unit |

|----------------------|----|-------------------------|-----------------------------------|-------------------------|-------------------------|-----|-------|------|------|

| Gymbol               |    | U                       | Parameter Conditions              |                         |                         | Min | Тур   | Max  | onn  |

| I <sub>DDSTDBY</sub> | СС | Ρ                       | STANDBY mode current <sup>9</sup> |                         | T <sub>A</sub> = 25 °C  |     | 30    | 100  | μA   |

|                      |    | D                       |                                   |                         | T <sub>A</sub> = 55 °C  |     | 75    | _    |      |

|                      |    | D                       |                                   |                         | T <sub>A</sub> = 85 °C  |     | 180   | 700  |      |

|                      |    | D                       |                                   |                         | T <sub>A</sub> = 105 °C | _   | 315   | 1000 |      |

|                      | P  | T <sub>A</sub> = 125 °C |                                   | 560                     | 1700                    |     |       |      |      |

Table 25. Power consumption on VDD\_BV and VDD\_HV (continued) (continued)

$^{1}$  V<sub>DD</sub> = 3.3 V  $\pm$  10% / 5.0 V  $\pm$  10%, T<sub>A</sub> = –40 to 125 °C, unless otherwise specified

<sup>2</sup> Running consumption does not include I/Os toggling which is highly dependent on the application. The given value is thought to be a worst case value with all peripherals running, and code fetched from code flash while modify operation ongoing on data flash. Notice that this value can be significantly reduced by application: switch off not used peripherals (default), reduce peripheral frequency through internal prescaler, fetch from RAM most used functions, use low power mode when possible.

- <sup>3</sup> Higher current may be sinked by device during power-up and standby exit. Please refer to in-rush average current on Table 23.

- <sup>4</sup> RUN current measured with typical application with accesses on both flash memory and SRAM.

- <sup>5</sup> Only for the "P" classification: Code fetched from SRAM: serial IPs CAN and LIN in loop-back mode, DSPI as Master, PLL as system clock (3 × Multiplier) peripherals on (eMIOS/CTU/ADC) and running at maximum frequency, periodic SW/WDG timer reset enabled.

- <sup>6</sup> Data flash power down. Code flash in low power. SIRC (128 kHz) and FIRC (16 MHz) on. 10 MHz XTAL clock. FlexCAN: 0 ON (clocked but no reception or transmission). LINFlex: instances: 0, 1, 2 ON (clocked but no reception or transmission), instance: 3 clocks gated. eMIOS: instance: 0 ON (16 channels on PA[0]–PA[11] and PC[12]–PC[15]) with PWM 20 kHz, instance: 1 clock gated. DSPI: instance: 0 (clocked but no communication). RTC/API ON.PIT ON. STM ON. ADC ON but no conversion except 2 analog watchdogs.

- <sup>7</sup> Only for the "P" classification: No clock, FIRC (16 MHz) off, SIRC (128 kHz) on, PLL off, HPVreg off, ULPVreg/LPVreg on. All possible peripherals off and clock gated. Flash in power down mode.

- <sup>8</sup> When going from RUN to STOP mode and the core consumption is > 6 mA, it is normal operation for the main regulator module to be kept on by the on-chip current monitoring circuit. This is most likely to occur with junction temperatures exceeding 125 °C and under these circumstances, it is possible for the current to initially exceed the maximum STOP specification by up to 2 mA. After entering stop, the application junction temperature will reduce to the ambient level and the main regulator will be automatically switched off when the load current is below 6 mA.

- <sup>9</sup> Only for the "P" classification: ULPVreg on, HP/LPVreg off, 16 KB SRAM on, device configured for minimum consumption, all possible modules switched off.

### 4.11 Flash memory electrical characteristics

The data flash operation depends strongly on the code flash operation. If code flash is switched-off, the data flash is disabled.

### 4.11.1 Program/Erase characteristics

Table 26 shows the program and erase characteristics.

| Symbo              | 0  | с | Parameter                                                                               | Parameter Conditions <sup>1</sup> |            |     | Valu | 9   | Unit |

|--------------------|----|---|-----------------------------------------------------------------------------------------|-----------------------------------|------------|-----|------|-----|------|

| Gymb               |    | Ŭ | i didineter                                                                             |                                   |            | Min | Тур  | Max |      |

| I <sub>FLPW</sub>  | СС |   | Sum of the current consumption on $V_{DDHV}$ and $V_{DDBV}$ during flash low-power mode | _                                 | Code flash |     | —    | 910 | μA   |

| I <sub>CFPWD</sub> | СС |   | Sum of the current consumption on                                                       | —                                 | Code flash |     | —    | 125 | μA   |

| I <sub>DFPWD</sub> | СС | D | V <sub>DDHV</sub> and V <sub>DDBV</sub> during<br>flash power-down mode                 |                                   | Data flash |     | —    | 25  | μA   |

Table 30. Flash power supply DC electrical characteristics

$^1~$  V\_{DD} = 3.3 V  $\pm$  10% / 5.0 V  $\pm$  10%, T\_A = -40 to 125 °C, unless otherwise specified

### 4.11.3 Start-up/Switch-off timings

| Table 31. Start-up | time/Switch-off | time |

|--------------------|-----------------|------|

|--------------------|-----------------|------|

| Symbol                  |                                              | с | Parameter                                                  | Conditions <sup>1</sup> |     | Value |                  | Unit |

|-------------------------|----------------------------------------------|---|------------------------------------------------------------|-------------------------|-----|-------|------------------|------|

| Cymbol                  |                                              |   | i didineter                                                | Conditions              | Min | Тур   | Мах              |      |

| t <sub>FLARSTEXIT</sub> | CC                                           | Т | Delay for flash module to exit reset mode                  | Code flash              | —   | —     | 125              | μs   |

|                         |                                              |   |                                                            | Data flash              |     |       | 150              | μs   |

| t <sub>FLALPEXIT</sub>  | СС                                           | Т | Delay for flash module to exit low-power mode <sup>2</sup> | Code flash              | —   | —     | 0.5              | μs   |

| t <sub>FLAPDEXIT</sub>  | СС                                           | Т | Delay for flash module to exit power-down                  | Code flash              |     | _     | 30               | μs   |

|                         |                                              |   | mode                                                       | Data flash              |     | —     | 30 <sup>3</sup>  | μs   |

| t <sub>FLALPENTRY</sub> | CC                                           | Т | Delay for flash module to enter low-power mode             | Code flash              | —   | —     | 0.5              | μs   |

| t <sub>FLAPDENTRY</sub> | PDENTRY CC T Delay for flash module to enter |   | Delay for flash module to enter                            | Code flash              |     | —     | 1.5              | μs   |

|                         |                                              |   | power-down mode                                            | Data flash              | —   | —     | 4 <sup>(3)</sup> | μs   |

$\overline{1}$  V<sub>DD</sub> = 3.3 V ± 10% / 5.0 V ± 10%, T<sub>A</sub> = -40 to 125 °C, unless otherwise specified

<sup>2</sup> Data flash does not support low-power mode

<sup>3</sup> If code flash is already switched-on.

# 4.12 Electromagnetic compatibility (EMC) characteristics

Susceptibility tests are performed on a sample basis during product characterization.

### 4.12.1 Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user apply EMC software optimization and prequalification tests in relation with the EMC level requested for his application.

• Software recommendations – The software flowchart must include the management of runaway conditions such as:

٠

- Corrupted program counter

- Unexpected reset

- Critical data corruption (control registers...)

- Prequalification trials Most of the common failures (unexpected reset and program counter corruption) can be reproduced by manually forcing a low state on the reset pin or the oscillator pins for 1 second.

To complete these trials, ESD stress can be applied directly on the device. When unexpected behavior is detected, the software can be hardened to prevent unrecoverable errors occurring.

### 4.12.2 Electromagnetic interference (EMI)

The product is monitored in terms of emission based on a typical application. This emission test conforms to the IEC 61967-1 standard, which specifies the general conditions for EMI measurements.

| Symbol             |    | С | Parameter             | Conditions                                                                   |                               |     | Value |         |          |

|--------------------|----|---|-----------------------|------------------------------------------------------------------------------|-------------------------------|-----|-------|---------|----------|

|                    |    | C | Farameter             | Conditions                                                                   |                               | Min | Тур   | Typ Max |          |

| _                  | SR |   | Scan range            | _                                                                            |                               |     | _     | 1000    | MHz      |

| f <sub>CPU</sub>   | SR |   | Operating frequency   | _                                                                            |                               |     | 48    |         | MHz      |

| V <sub>DD_LV</sub> | SR |   | LV operating voltages | _                                                                            |                               | —   | 1.28  | —       | V        |

| S <sub>EMI</sub>   | СС | Т | Peak level            | 100 LQFP package                                                             | No PLL frequency modulation   | —   |       | 18      | dBµ<br>V |

|                    |    |   |                       | $  _{0000} = 0         /  _{0011} = 40        /                            $ | ± 2% PLL frequency modulation | _   |       | 14      | dBµ<br>V |

Table 32. EMI radiated emission measurement<sup>1 2</sup>

<sup>1</sup> EMI testing and I/O port waveforms per IEC 61967-1, -2, -4

<sup>2</sup> For information on conducted emission and susceptibility measurement (norm IEC 61967-4), please contact your local marketing representative.

### 4.12.3 Absolute maximum ratings (electrical sensitivity)

Based on two different tests (ESD and LU) using specific measurement methods, the product is stressed in order to determine its performance in terms of electrical sensitivity.

### 4.12.3.1 Electrostatic discharge (ESD)

Electrostatic discharges (a positive then a negative pulse separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts  $\times$  (n + 1) supply pin). This test conforms to the AEC-Q100-002/-003/-011 standard.

| Symbol                |    | С | Ratings                                               | Conditions                                           | Class | Max value     | Unit |

|-----------------------|----|---|-------------------------------------------------------|------------------------------------------------------|-------|---------------|------|

| V <sub>ESD(HBM)</sub> | СС |   | Electrostatic discharge voltage<br>(Human Body Model) | $T_A = 25 \text{ °C}$<br>conforming to AEC-Q100-002  | H1C   | H1C 2000      |      |

| V <sub>ESD(MM)</sub>  | СС |   | Electrostatic discharge voltage<br>(Machine Model)    | T <sub>A</sub> = 25 °C<br>conforming to AEC-Q100-003 | M2    | 200           | V    |

| V <sub>ESD(CDM)</sub> | СС |   | Electrostatic discharge voltage                       | $T_{A} = 25 ^{\circ}C$                               | СЗА   | 500           | V    |

|                       |    |   | (Charged Device Model)                                | conforming to AEC-Q100-011                           |       | 750 (corners) | V    |

| Table 33. ESD absolute maximum ratings <sup>1 2</sup> |  |

|-------------------------------------------------------|--|

|-------------------------------------------------------|--|

<sup>1</sup> All ESD testing is in conformity with CDF-AEC-Q100 Stress Test Qualification for Automotive Grade Integrated Circuits.

<sup>2</sup> A device will be defined as a failure if after exposure to ESD pulses the device no longer meets the device specification requirements. Complete DC parametric and functional testing shall be performed per applicable device specification at room temperature followed by hot temperature, unless specified otherwise in the device specification.

### 4.12.3.2 Static latch-up (LU)

Two complementary static tests are required on six parts to assess the latch-up performance:

- A supply overvoltage is applied to each power supply pin.

- A current injection is applied to each input, output and configurable I/O pin.

These tests are compliant with the EIA/JESD 78 IC latch-up standard.

#### Table 34. Latch-up results

| Syn | nbol | С | Parameter             | Conditions                                   | Class      |

|-----|------|---|-----------------------|----------------------------------------------|------------|

| LU  | CC   | Т | Static latch-up class | $T_A = 125 \text{ °C}$ conforming to JESD 78 | II level A |

| Nominal<br>frequency<br>(MHz) | NDK crystal<br>reference | Crystal<br>equivalent<br>series<br>resistance<br>(ESR) Ω | Crystal<br>motional<br>capacitance<br>(C <sub>m</sub> ) fF | Crystal<br>motional<br>inductance<br>(L <sub>m</sub> ) mH | Load on<br>xtalin/xtalout<br>C <sub>1</sub> = C <sub>2</sub> (pF) <sup>1</sup> | Shunt<br>capacitance<br>between xtalout<br>and xtalin<br>C0 <sup>2</sup> (pF) |

|-------------------------------|--------------------------|----------------------------------------------------------|------------------------------------------------------------|-----------------------------------------------------------|--------------------------------------------------------------------------------|-------------------------------------------------------------------------------|

| 4                             | NX8045GB                 | 300                                                      | 2.68                                                       | 591.0                                                     | 21                                                                             | 2.93                                                                          |

| 8                             | NX5032GA                 | 300                                                      | 2.46                                                       | 160.7                                                     | 17                                                                             | 3.01                                                                          |

| 10                            |                          | 150                                                      | 2.93                                                       | 86.6                                                      | 15                                                                             | 2.91                                                                          |

| 12                            |                          | 120                                                      | 3.11                                                       | 56.5                                                      | 15                                                                             | 2.93                                                                          |

| 16                            |                          | 120                                                      | 3.90                                                       | 25.3                                                      | 10                                                                             | 3.00                                                                          |

#### Table 35. Crystal description

<sup>1</sup> The values specified for C1 and C2 are the same as used in simulations. It should be ensured that the testing includes all the parasitics (from the board, probe, crystal, etc.) as the AC / transient behavior depends upon them.

<sup>2</sup> The value of C0 specified here includes 2 pF additional capacitance for parasitics (to be seen with bond-pads, package, etc.).

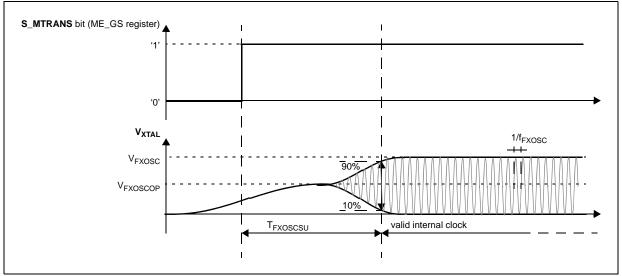

Figure 10. Fast external crystal oscillator (4 to 16 MHz) timing diagram

| Symbol                          |    | с | Deremeter                                         | Conditions <sup>1</sup>                                             |                     | Value |                      | Unit |

|---------------------------------|----|---|---------------------------------------------------|---------------------------------------------------------------------|---------------------|-------|----------------------|------|

| Symbol                          |    | C | Parameter                                         | Conditions                                                          | Min                 | Тур   | Max                  | Unit |

| f <sub>FXOSC</sub>              | SR |   | Fast external crystal oscillator frequency        | _                                                                   | 4.0                 | _     | 16.0                 | MHz  |

| g <sub>m</sub> Fxosc            | СС | С | Fast external crystal oscillator transconductance | $V_{DD} = 3.3 V \pm 10\%$ ,<br>PAD3V5V = 1<br>OSCILLATOR_MARGIN = 0 | 2.2                 |       | 8.2                  | mA/V |

|                                 | СС | Ρ |                                                   | $V_{DD} = 5.0 V \pm 10\%$ ,<br>PAD3V5V = 0<br>OSCILLATOR_MARGIN = 0 | 2.0                 |       | 7.4                  |      |

|                                 | СС | С |                                                   | $V_{DD} = 3.3 V \pm 10\%$ ,<br>PAD3V5V = 1<br>OSCILLATOR_MARGIN = 1 | 2.7                 |       | 9.7                  |      |

|                                 | СС | С |                                                   | $V_{DD} = 5.0 V \pm 10\%$ ,<br>PAD3V5V = 0<br>OSCILLATOR_MARGIN = 1 | 2.5                 | _     | 9.2                  |      |

| V <sub>FXOSC</sub>              | СС | Т | Oscillation amplitude at EXTAL                    | f <sub>OSC</sub> = 4 MHz,<br>OSCILLATOR_MARGIN = 0                  | 1.3                 | _     | —                    | V    |

|                                 |    |   |                                                   | f <sub>OSC</sub> = 16 MHz,<br>OSCILLATOR_MARGIN = 1                 | 1.3                 | _     | —                    |      |

| V <sub>FXOSCOP</sub>            | CC | Ρ | Oscillation operating point                       | _                                                                   | —                   | 0.95  |                      | V    |

| I <sub>FXOSC</sub> <sup>2</sup> | СС | Т | Fast external crystal<br>oscillator consumption   | —                                                                   | —                   | 2     | 3                    | mA   |

| t <sub>FXOSCSU</sub>            | СС | Т | Fast external crystal<br>oscillator start-up time | f <sub>OSC</sub> = 4 MHz,<br>OSCILLATOR_MARGIN = 0                  | —                   |       | 6                    | ms   |

|                                 |    |   |                                                   | f <sub>OSC</sub> = 16 MHz,<br>OSCILLATOR_MARGIN = 1                 | —                   | _     | 1.8                  |      |

| V <sub>IH</sub>                 | SR | Ρ | Input high level CMOS<br>(Schmitt Trigger)        | Oscillator bypass mode                                              | 0.65V <sub>DD</sub> | _     | V <sub>DD</sub> +0.4 | V    |

| V <sub>IL</sub>                 | SR | Ρ | Input low level CMOS<br>(Schmitt Trigger)         | Oscillator bypass mode                                              | -0.4                |       | 0.35V <sub>DD</sub>  | V    |

$^{1}$  V<sub>DD</sub> = 3.3 V ± 10% / 5.0 V ± 10%, T<sub>A</sub> = -40 to 125 °C, unless otherwise specified

<sup>2</sup> Stated values take into account only analog module consumption but not the digital contributor (clock tree and enabled peripherals)

| Symbol                |    | с | Parameter                                                                                                                                               | C.                                | onditions <sup>1</sup> | Value |      |     | Unit |

|-----------------------|----|---|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|------------------------|-------|------|-----|------|

| Cymbol                |    | Ŭ | i didineter                                                                                                                                             |                                   |                        | Min   | Тур  | Мах | onne |

| I <sub>FIRCSTOP</sub> | CC | Т | Fast internal RC oscillator high                                                                                                                        | T <sub>A</sub> = 25 °C            | sysclk = off           |       | 500  |     | μA   |

|                       |    |   | frequency and system clock<br>current in stop mode                                                                                                      |                                   | sysclk = 2 MHz         |       | 600  |     |      |

|                       |    |   |                                                                                                                                                         |                                   | sysclk = 4 MHz         |       | 700  |     |      |

|                       |    |   |                                                                                                                                                         |                                   | sysclk = 8 MHz         |       | 900  |     |      |

|                       |    |   |                                                                                                                                                         |                                   | sysclk = 16 MHz        |       | 1250 | -   |      |

| t <sub>FIRCSU</sub>   | СС | С | Fast internal RC oscillator start-up time                                                                                                               | $V_{DD} = 5.0 \text{ V} \pm 10\%$ |                        | _     | 1.1  | 2.0 | μs   |

| Δ <sub>FIRCPRE</sub>  | СС | С | Fast internal RC oscillator<br>precision after software<br>trimming of f <sub>FIRC</sub>                                                                | T <sub>A</sub> = 25 °C            |                        | -1    | _    | 1   | %    |

| $\Delta_{FIRCTRIM}$   | СС | С | Fast internal RC oscillator<br>trimming step                                                                                                            | T <sub>A</sub> = 25 °C            |                        | —     | 1.6  |     | %    |

|                       | СС | С | Fast internal RC oscillator<br>variation in temperature and<br>supply with respect to $f_{FIRC}$ at<br>$T_A = 55$ °C in high-frequency<br>configuration |                                   | _                      | -5    |      | 5   | %    |

Table 38. Fast internal RC oscillator (16 MHz) electrical characteristics (continued)

$^{1}$  V<sub>DD</sub> = 3.3 V  $\pm$  10% / 5.0 V  $\pm$  10%, T<sub>A</sub> = –40 to 125 °C, unless otherwise specified.

<sup>2</sup> This does not include consumption linked to clock tree toggling and peripherals consumption when RC oscillator is ON.

# 4.16 Slow internal RC oscillator (128 kHz) electrical characteristics

The device provides a 128 kHz slow internal RC oscillator (SIRC). This can be used as the reference clock for the RTC module.

Table 39. Slow internal RC oscillator (128 kHz) electrical characteristics

| Symbol                          |    | с | C Parameter                                                                        | Conditions <sup>1</sup>                                |     | Unit |     |     |

|---------------------------------|----|---|------------------------------------------------------------------------------------|--------------------------------------------------------|-----|------|-----|-----|

| Cymbol                          |    | Ŭ | i di dificici                                                                      | Conditions                                             | Min | Тур  | Max |     |

| f <sub>SIRC</sub>               | СС |   | Slow internal RC oscillator low                                                    | T <sub>A</sub> = 25 °C, trimmed                        |     | 128  |     | kHz |

|                                 | SR | _ | frequency                                                                          | _                                                      | 100 | _    | 150 |     |

| I <sub>SIRC</sub> <sup>2,</sup> | СС |   | Slow internal RC oscillator low<br>frequency current                               | T <sub>A</sub> = 25 °C, trimmed                        |     |      | 5   | μA  |

| t <sub>SIRCSU</sub>             | СС |   | Slow internal RC oscillator start-up time                                          | $T_A = 25 \text{ °C}, V_{DD} = 5.0 \text{ V} \pm 10\%$ | _   | 8    | 12  | μs  |

| ∆ <sub>SIRCPRE</sub>            | CC |   | Slow internal RC oscillator precision after software trimming of f <sub>SIRC</sub> | T <sub>A</sub> = 25 °C                                 | -2  | _    | 2   | %   |

|                                 | СС | С | Slow internal RC oscillator trimming step                                          | —                                                      |     | 2.7  | _   |     |

### 4.17.2 Input impedance and ADC accuracy

In the following analysis, the input circuit corresponding to the precise channels is considered.

To preserve the accuracy of the A/D converter, it is necessary that analog input pins have low AC impedance. Placing a capacitor with good high frequency characteristics at the input pin of the device can be effective: the capacitor should be as large as possible, ideally infinite. This capacitor contributes to attenuating the noise present on the input pin; furthermore, it sources charge during the sampling phase, when the analog signal source is a high-impedance source.

A real filter can typically be obtained by using a series resistance with a capacitor on the input pin (simple RC filter). The RC filtering may be limited according to the value of source impedance of the transducer or circuit supplying the analog signal to be measured. The filter at the input pins must be designed taking into account the dynamic characteristics of the input signal (bandwidth) and the equivalent input impedance of the ADC itself.

In fact a current sink contributor is represented by the charge sharing effects with the sampling capacitance: being  $C_S$  and  $C_{p2}$  substantially two switched capacitances, with a frequency equal to the conversion rate of the ADC, it can be seen as a resistive path to ground. For instance, assuming a conversion rate of 1 MHz, with  $C_S+C_{p2}$  equal to 3 pF, a resistance of 330 k $\Omega$  is obtained ( $R_{EQ} = 1 / (f_c \times (C_S+C_{p2}))$ ), where  $f_c$  represents the conversion rate at the considered channel). To minimize the error induced by the voltage partitioning between this resistance (sampled voltage on  $C_S+C_{p2}$ ) and the sum of  $R_S + R_F$ , the external circuit must be designed to respect the Equation 4:

Eqn. 4

$$V_A \bullet \frac{R_S + R_F}{R_{EQ}} < \frac{1}{2}LSB$$

Equation 4 generates a constraint for external network design, in particular on a resistive path.

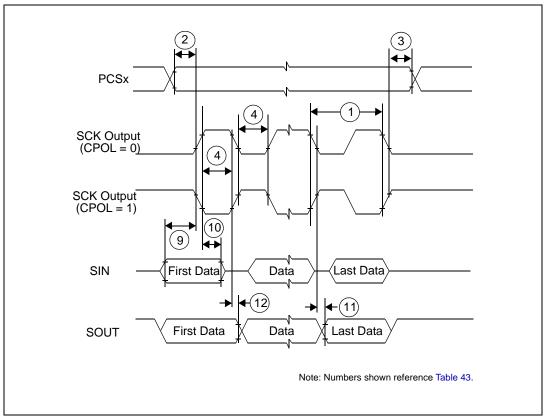

Figure 16. DSPI classic SPI timing – master, CPHA = 0