Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                |

| Core Processor             | HC05                                                                    |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 4MHz                                                                    |

| Connectivity               | -                                                                       |

| Peripherals                | POR, WDT                                                                |

| Number of I/O              | 14                                                                      |

| Program Memory Size        | 1.2KB (1.2K x 8)                                                        |

| Program Memory Type        | OTP                                                                     |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 64 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                               |

| Data Converters            | -                                                                       |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                                          |

| Supplier Device Package    | 20-SOIC                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc68hc705j1acdw |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Technical Data — MC68HC705J1A

# **List of Sections**

| Section 1. General Description21                      |

|-------------------------------------------------------|

| Section 2. Memory33                                   |

| Section 3. Central Processor Unit (CPU)45             |

| Section 4. Resets and Interrupts                      |

| Section 5. Low-Power Modes79                          |

| Section 6. Parallel Input/Output (I/O) Ports87        |

| Section 7. Computer Operating Properly (COP) Module97 |

| Section 8. External Interrupt Module (IRQ)101         |

| Section 9. Multifunction Timer Module                 |

| Section 10. Electrical Specifications117              |

| Section 11. Mechanical Specifications                 |

| Section 12. Ordering Information                      |

| Appendix A. MC68HRC705J1A137                          |

| Appendix B. MC68HSC705J1A141                          |

| Appendix C. MC68HSR705J1A145                          |

| Index                                                 |

MC68HC705J1A — Rev. 4.0

**Memory**

Technical Data

MC68HC705J1A — Rev. 4.0

## **Central Processor Unit (CPU)**

# 3.5 CPU Registers

The M68HC05 CPU contains five registers that control and monitor microcontroller unit (MCU) operation:

- Accumulator

- Index register

- Stack pointer

- Program counter

- Condition code register

CPU registers are not memory mapped.

#### 3.5.1 Accumulator

The accumulator (A) is a general-purpose 8-bit register. The CPU uses the accumulator to hold operands and results of ALU operations.

Figure 3-2. Accumulator (A)

## 3.5.2 Index Register

In the indexed addressing (X) modes, the CPU uses the byte in the index register to determine the conditional address of the operand. The index register also can serve as a temporary storage location or a counter.

Figure 3-3. Index Register (X)

## **Central Processor Unit (CPU)**

#### 3.6 Instruction Set

The MCU instruction set has 62 instructions and uses eight addressing modes.

#### 3.6.1 Addressing Modes

The CPU uses eight addressing modes for flexibility in accessing data. The addressing modes provide eight different ways for the CPU to find the data required to execute an instruction. The eight addressing modes are:

- Inherent

- Immediate

- Direct

- Extended

- Indexed, no offset

- Indexed, 8-bit offset

- Indexed, 16-bit offset

- Relative

#### 3.6.1.1 Inherent

Inherent instructions are those that have no operand, such as return from interrupt (RTI) and stop (STOP). Some of the inherent instructions act on data in the CPU registers, such as set carry flag (SEC) and increment accumulator (INCA). Inherent instructions require no operand address and are one byte long.

#### 3.6.1.2 Immediate

Immediate instructions are those that contain a value to be used in an operation with the value in the accumulator or index register. Immediate instructions require no operand address and are two bytes long. The opcode is the first byte, and the immediate data value is the second byte.

**Technical Data**

MC68HC705J1A — Rev. 4.0

# Central Processor Unit (CPU)

**Table 3-3. Jump and Branch Instructions**

| Instruction                    | Mnemonic |

|--------------------------------|----------|

| Branch if carry bit clear      | BCC      |

| Branch if carry bit set        | BCS      |

| Branch if equal                | BEQ      |

| Branch if half-carry bit clear | внсс     |

| Branch if half-carry bit set   | BHCS     |

| Branch if higher               | BHI      |

| Branch if higher or same       | BHS      |

| Branch if IRQ pin high         | BIH      |

| Branch if IRQ pin low          | BIL      |

| Branch if lower                | BLO      |

| Branch if lower or same        | BLS      |

| Branch if interrupt mask clear | ВМС      |

| Branch if minus                | BMI      |

| Branch if interrupt mask set   | BMS      |

| Branch if not equal            | BNE      |

| Branch if plus                 | BPL      |

| Branch always                  | BRA      |

| Branch if bit clear            | BRCLR    |

| Branch never                   | BRN      |

| Branch if bit set              | BRSET    |

| Branch to subroutine           | BSR      |

| Unconditional jump             | JMP      |

| Jump to subroutine             | JSR      |

Central Processor Unit (CPU) Instruction Set

#### 3.6.2.4 Bit Manipulation Instructions

The CPU can set or clear any writable bit in the first 256 bytes of memory, which includes I/O registers and on-chip RAM locations. The CPU can also test and branch based on the state of any bit in any of the first 256 memory locations.

Table 3-4. Bit Manipulation Instructions

| Instruction         | Mnemonic |

|---------------------|----------|

| Bit clear           | BCLR     |

| Branch if bit clear | BRCLR    |

| Branch if bit set   | BRSET    |

| Bit set             | BSET     |

**NOTE:** Do not use bit manipulation instructions on registers with write-only bits.

# Central Processor Unit (CPU)

#### 3.6.2.5 Control Instructions

These instructions act on CPU registers and control CPU operation during program execution.

**Table 3-5. Control Instructions**

| Instruction                            | Mnemonic |

|----------------------------------------|----------|

| Clear carry bit                        | CLC      |

| Clear interrupt mask                   | CLI      |

| No operation                           | NOP      |

| Reset stack pointer                    | RSP      |

| Return from interrupt                  | RTI      |

| Return from subroutine                 | RTS      |

| Set carry bit                          | SEC      |

| Set interrupt mask                     | SEI      |

| Stop oscillator and enable IRQ pin     | STOP     |

| Software interrupt                     | SWI      |

| Transfer accumulator to index register | TAX      |

| Transfer index register to accumulator | TXA      |

| Stop CPU clock and enable interrupts   | WAIT     |

Central Processor Unit (CPU) Instruction Set Summary

Table 3-6. Instruction Set Summary (Sheet 5 of 6)

| Source                                                             | Operation Description                               |                                                                                                                                                                                                                                        |   | Effect<br>n CCF |          |   |          |                                       |                                  | Opcode                           | Operand                    | Cycles |

|--------------------------------------------------------------------|-----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----------------|----------|---|----------|---------------------------------------|----------------------------------|----------------------------------|----------------------------|--------|

| Form                                                               |                                                     | ·                                                                                                                                                                                                                                      | Н | I               | N        | Z | С        | Adc                                   | o                                | Ope                              | ડ                          |        |

| ROL opr<br>ROLA<br>ROLX<br>ROL opr,X<br>ROL ,X                     | Rotate Byte Left through Carry Bit                  | b7 b0                                                                                                                                                                                                                                  |   | _               | ţ        | ţ | <b>‡</b> | DIR<br>INH<br>INH<br>IX1<br>IX        | 39<br>49<br>59<br>69<br>79       | dd<br>ff                         | 5<br>3<br>3<br>6<br>5      |        |

| ROR opr<br>RORA<br>RORX<br>ROR opr,X<br>ROR ,X                     | Rotate Byte Right through Carry Bit                 | b7 b0                                                                                                                                                                                                                                  |   | _               | <b>‡</b> | ţ | <b>‡</b> | DIR<br>INH<br>INH<br>IX1<br>IX        | 36<br>46<br>56<br>66<br>76       | dd<br>ff                         | 5<br>3<br>3<br>6<br>5      |        |

| RSP                                                                | Reset Stack Pointer                                 | SP ← \$00FF                                                                                                                                                                                                                            |   | _               | _        | _ | _        | INH                                   | 9C                               |                                  | 2                          |        |

| RTI                                                                | Return from Interrupt                               | $\begin{split} & SP \leftarrow (SP) + 1;  Pull  (CCR) \\ & SP \leftarrow (SP) + 1;  Pull  (A) \\ & SP \leftarrow (SP) + 1;  Pull  (X) \\ & SP \leftarrow (SP) + 1;  Pull  (PCH) \\ & SP \leftarrow (SP) + 1;  Pull  (PCL) \end{split}$ |   | ‡               | ‡        | ‡ | <b>‡</b> | INH                                   | 80                               |                                  | 9                          |        |

| RTS                                                                | Return from Subroutine                              | $ \begin{array}{c} SP \leftarrow (SP) + 1;  Pull  (PCH) \\ SP \leftarrow (SP) + 1;  Pull  (PCL) \end{array} $                                                                                                                          |   | _               | _        | _ | _        | INH                                   | 81                               |                                  | 6                          |        |

| SBC #opr<br>SBC opr<br>SBC opr<br>SBC opr,X<br>SBC opr,X<br>SBC ,X | Subtract Memory Byte and Carry Bit from Accumulator | $A \leftarrow (A) - (M) - (C)$                                                                                                                                                                                                         |   |                 | <b>‡</b> | ţ | <b>‡</b> | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX | A2<br>B2<br>C2<br>D2<br>E2<br>F2 | ii<br>dd<br>hh II<br>ee ff<br>ff | 2<br>3<br>4<br>5<br>4<br>3 |        |

| SEC                                                                | Set Carry Bit                                       | C ← 1                                                                                                                                                                                                                                  | _ | _               | _        | _ | 1        | INH                                   | 99                               |                                  | 2                          |        |

| SEI                                                                | Set Interrupt Mask                                  | I ← 1                                                                                                                                                                                                                                  | _ | 1               | _        | _ | _        | INH                                   | 9B                               |                                  | 2                          |        |

| STA opr<br>STA opr<br>STA opr,X<br>STA opr,X<br>STA ,X             | Store Accumulator in Memory                         | M ← (A)                                                                                                                                                                                                                                |   | _               | ţ        | ţ | _        | DIR<br>EXT<br>IX2<br>IX1<br>IX        | B7<br>C7<br>D7<br>E7<br>F7       | dd<br>hh II<br>ee ff<br>ff       | 4<br>5<br>6<br>5<br>4      |        |

| STOP                                                               | Stop Oscillator and Enable IRQ Pin                  |                                                                                                                                                                                                                                        | _ | 0               | _        | _ | _        | INH                                   | 8E                               |                                  | 2                          |        |

| STX opr<br>STX opr<br>STX opr,X<br>STX opr,X<br>STX ,X             | Store Index Register In Memory                      | $M \leftarrow (X)$                                                                                                                                                                                                                     |   | _               | <b>‡</b> | ţ | _        | DIR<br>EXT<br>IX2<br>IX1<br>IX        | BF<br>CF<br>DF<br>EF<br>FF       | dd<br>hh II<br>ee ff<br>ff       | 4<br>5<br>6<br>5<br>4      |        |

| SUB #opr<br>SUB opr<br>SUB opr<br>SUB opr,X<br>SUB opr,X<br>SUB ,X | Subtract Memory Byte from Accumulator               | $A \leftarrow (A) - (M)$                                                                                                                                                                                                               | _ | _               | ‡        | ‡ | <b>‡</b> | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX | A0<br>B0<br>C0<br>D0<br>E0<br>F0 | ii<br>dd<br>hh II<br>ee ff<br>ff | 2<br>3<br>4<br>5<br>4<br>3 |        |

MC68HC705J1A — Rev. 4.0

# **Central Processor Unit (CPU)**

Table 3-6. Instruction Set Summary (Sheet 6 of 6)

| Source<br>Form                                 | Operation                              | Description                                                                                                                                                                                                                                                                                                                                                                  |   | Ef<br>on  |   | ct<br>CF | 2 | Address<br>Mode                | Opcode                     | Operand  | Cycles                |

|------------------------------------------------|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----------|---|----------|---|--------------------------------|----------------------------|----------|-----------------------|

| 1 01111                                        |                                        |                                                                                                                                                                                                                                                                                                                                                                              |   | H I N Z C |   | β¥       | o | ď                              | ပ်                         |          |                       |

| SWI                                            | Software Interrupt                     | $\begin{array}{c} PC \leftarrow (PC) + 1;  Push  (PCL) \\ SP \leftarrow (SP) - 1;  Push  (PCH) \\ SP \leftarrow (SP) - 1;  Push  (X) \\ SP \leftarrow (SP) - 1;  Push  (A) \\ SP \leftarrow (SP) - 1;  Push  (CCR) \\ SP \leftarrow (SP) - 1;  I \leftarrow 1 \\ PCH \leftarrow Interrupt  Vector  High  Byte \\ PCL \leftarrow Interrupt  Vector  Low  Byte \\ \end{array}$ |   | 1         |   |          |   | INH                            | 83                         |          | 10                    |

| TAX                                            | Transfer Accumulator to Index Register | X ← (A)                                                                                                                                                                                                                                                                                                                                                                      | _ | _         | _ | _        | _ | INH                            | 97                         |          | 2                     |

| TST opr<br>TSTA<br>TSTX<br>TST opr,X<br>TST ,X | Test Memory Byte for Negative or Zero  | (M) – \$00                                                                                                                                                                                                                                                                                                                                                                   |   |           | t | <b>‡</b> | _ | DIR<br>INH<br>INH<br>IX1<br>IX | 3D<br>4D<br>5D<br>6D<br>7D | dd<br>ff | 4<br>3<br>3<br>5<br>4 |

| TXA                                            | Transfer Index Register to Accumulator | A ← (X)                                                                                                                                                                                                                                                                                                                                                                      | _ | _         | _ | -        | - | INH                            | 9F                         |          | 2                     |

| WAIT                                           | Stop CPU Clock and Enable Interrupts   |                                                                                                                                                                                                                                                                                                                                                                              | _ | 1         |   | _        | _ | INH                            | 8F                         |          | 2                     |

| Α     | Accumulator                                                         | opr          | Operand (one or two bytes)           |

|-------|---------------------------------------------------------------------|--------------|--------------------------------------|

| С     | Carry/borrow flag                                                   | PC           | Program counter                      |

| CCR   | Condition code register                                             | PCH          | Program counter high byte            |

| dd    | Direct address of operand                                           | PCL          | Program counter low byte             |

| dd rr | Direct address of operand and relative offset of branch instruction | REL          | Relative addressing mode             |

| DIR   | Direct addressing mode                                              | rel          | Relative program counter offset byte |

| ee ff | High and low bytes of offset in indexed, 16-bit offset addressing   | rr           | Relative program counter offset byte |

| EXT   | Extended addressing mode                                            | SP           | Stack pointer                        |

| ff    | Offset byte in indexed, 8-bit offset addressing                     | Χ            | Index register                       |

| Н     | Half-carry flag                                                     | Z            | Zero flag                            |

| hh II | High and low bytes of operand address in extended addressing        | #            | Immediate value                      |

| I     | Interrupt mask                                                      | ^            | Logical AND                          |

| ii    | Immediate operand byte                                              | <b>V</b>     | Logical OR                           |

| IMM   | Immediate addressing mode                                           | $\oplus$     | Logical EXCLUSIVE OR                 |

| INH   | Inherent addressing mode                                            | ()           | Contents of                          |

| IX    | Indexed, no offset addressing mode                                  | <b>-(</b> )  | Negation (two's complement)          |

| IX1   | Indexed, 8-bit offset addressing mode                               | $\leftarrow$ | Loaded with                          |

| IX2   | Indexed, 16-bit offset addressing mode                              | ?            | If                                   |

| M     | Memory location                                                     | :            | Concatenated with                    |

| N     | Negative flag                                                       | <b>‡</b>     | Set or cleared                       |

| n     | Any bit                                                             | _            | Not affected                         |

|       |                                                                     |              |                                      |

# 3.8 Opcode Map

See Table 3-7.

Central Processor Unit (CPU)

## Parallel Input/Output (I/O) Ports

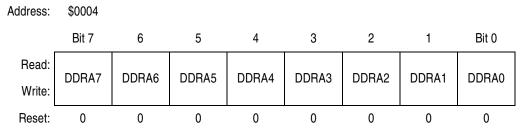

#### 6.3.2 Data Direction Register A

Data direction register A (DDRA) determines whether each port A pin is an input or an output.

Figure 6-3. Data Direction Register A (DDRA)

DDRA[7:0] — Data Direction Register A Bits

These read/write bits control port A data direction. Reset clears DDRA[7:0], configuring all port A pins as inputs.

- 1 = Corresponding port A pin configured as output

- 0 = Corresponding port A pin configured as input

**NOTE:** Avoid glitches on port A pins by writing to the port A data register before changing data direction register A bits from 0 to 1.

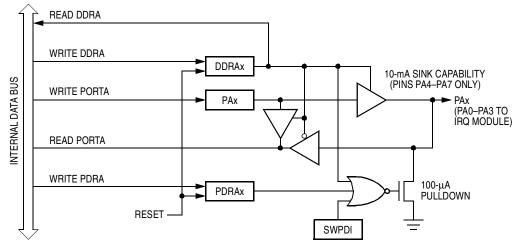

Figure 6-4 shows the I/O logic of port A.

Figure 6-4. Port A I/O Circuitry

## External Interrupt Module (IRQ)

# 8.3.1 IRQ/V<sub>PP</sub> Pin

An interrupt signal on the  $\overline{\text{IRQ}}/\text{V}_{PP}$  pin latches an external interrupt request. The LEVEL bit in the mask option register provides negative edge-sensitive triggering or both negative edge-sensitive and low level-sensitive triggering for the interrupt function.

If edge- and level-sensitive triggering is selected, a falling edge or a low level on the  $\overline{IRQ}/V_{PP}$  pin latches an external interrupt request. Edge- and level-sensitive triggering allows the use of multiple wired-OR external interrupt sources. An external interrupt request is latched as long as any source is holding the  $\overline{IRQ}/V_{PP}$  pin low.

If level-sensitive triggering is selected, the  $\overline{IRQ}/V_{PP}$  input requires an external resistor to  $V_{DD}$  for wired-OR operation. If the  $\overline{IRQ}/V_{PP}$  pin is not used, it must be tied to the  $V_{DD}$  supply.

If edge-sensitive-only triggering is selected, a falling edge on the  $\overline{IRQ}/V_{PP}$  pin latches an external interrupt request. A subsequent external interrupt request can be latched only after the voltage level on the  $\overline{IRQ}/V_{PP}$  pin returns to logic 1 and then falls again to logic 0.

The  $\overline{IRQ}/V_{PP}$  pin contains an internal Schmitt trigger as part of its input to improve noise immunity. The voltage on this pin can affect the mode of operation and should not exceed  $V_{DD}$ .

#### 8.3.2 Optional External Interrupts

The inputs for the lower four bits of port A (PA0–PA3) can be connected to the IRQ pin input of the CPU if enabled by the PIRQ bit in the mask option register. This capability allows keyboard scan applications where the transitions or levels on the I/O pins will behave the same as the IRQ/V<sub>PP</sub> pin except for the inverted phase (logic 1, rising edge). The active state of the IRQ/V<sub>PP</sub> pin is a logic 0 (falling edge).

The PA0–PA3 pins are selected as a group to function as IRQ interrupts and are enabled by the IRQE bit in the IRQ status and control register. The PA0–PA3 pins can be positive-edge triggered only or positive-edge and high-level triggered.

**Technical Data**

MC68HC705J1A — Rev. 4.0

## Technical Data — MC68HC705J1A

# Section 9. Multifunction Timer Module

#### 9.1 Contents

| 9.2   | Introduction    |

|-------|-----------------|

| 9.3   | Operation       |

| 9.4   | Interrupts      |

| 9.5.1 | I/O Registers   |

|       | Low-Power Modes |

#### 9.2 Introduction

The multifunction timer provides a timing reference with programmable real-time interrupt (RTI) capability. **Figure 9-1** shows the timer organization.

#### Features include:

- Timer overflow

- Four selectable interrupt rates

- Computer operating properly (COP) watchdog timer

## **Multifunction Timer Module**

interrupt request to be generated. To prevent this occurrence, clear the COP timer before changing RT1 and RT0.

Table 9-1. Real-Time Interrupt Rate Selection

| RT1:RT0 | Number<br>of Cycles<br>to RTI | RTI<br>Period <sup>(1)</sup> | Number<br>of Cycles<br>to COP Reset | COP Timeout<br>Period <sup>(1)</sup> |

|---------|-------------------------------|------------------------------|-------------------------------------|--------------------------------------|

| 0 0     | 2 <sup>14</sup> = 16,384      | 8.2 ms                       | $2^{17} = 131,072$                  | 65.5 ms                              |

| 0 1     | $2^{15} = 32,768$             | 16.4 ms                      | $2^{18} = 262,144$                  | 131.1 ms                             |

| 1 0     | $2^{16} = 65,536$             | 32.8 ms                      | $2^{19} = 524,288$                  | 262.1 ms                             |

| 1 1     | $2^{17} = 131,072$            | 65.5 ms                      | $2^{20} = 1,048,576$                | 524.3 ms                             |

<sup>1.</sup> At 2-MHz bus, 4-MHz XTAL, 0.5 µs per cycle

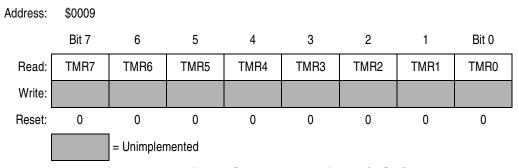

#### 9.5.2 Timer Counter Register

A 15-stage ripple counter is the core of the timer. The value of the first eight stages is readable at any time from the read-only timer counter register (TCR) shown in **Figure 9-4**.

Figure 9-4. Timer Counter Register (TCR)

Power-on clears the entire counter chain and the internal clock begins clocking the counter. After 4064 cycles (or 16 cycles if the SOSCD bit in the mask option register is set), the power-on reset circuit is released, clearing the counter again and allowing the MCU to come out of reset.

A timer overflow function at the eighth counter stage allows a timer interrupt every 1024 internal clock cycles.

# **Multifunction Timer Module**

reescale Semiconductor, Inc

## MC68HSC705J1A

#### **B.3 5.0-Volt DC Electrical Characteristics**

| Characteristic                                            | Symbol          | Min | Тур          | Max         | Unit |

|-----------------------------------------------------------|-----------------|-----|--------------|-------------|------|

| Supply current (f <sub>OP</sub> = 4.0 MHz)<br>Run<br>Wait | I <sub>DD</sub> |     | 4.25<br>0.57 | 7.0<br>3.25 | mA   |

#### **B.4 3.3-Volt DC Electrical Characteristics**

| Characteristic                                      | Symbol          | Min | Тур         | Max          | Unit |

|-----------------------------------------------------|-----------------|-----|-------------|--------------|------|

| Supply current (f <sub>OP</sub> = 2.1 MHz) Run Wait | I <sub>DD</sub> |     | 1.4<br>0.28 | 4.25<br>1.75 | mA   |

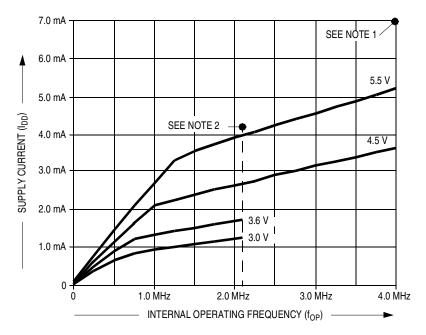

## **B.5 Typical Supply Currents**

#### Notes:

- 1. At V<sub>DD</sub> = 5.0 V, high-speed devices are specified and tested for I<sub>DD</sub>  $\leq$  7.0 mA @ f<sub>OP</sub> = 4.0 MHz.

- 2. At  $V_{DD}$  = 3.3 V, high-speed devices are specified and tested for  $I_{DD}$   $\leq$  4.25 mA @ f<sub>OP</sub> = 2.1 MHz.

Figure B-1. Typical High-Speed Operating  $I_{DD}$  (25°C)

## MC68HSR705J1A

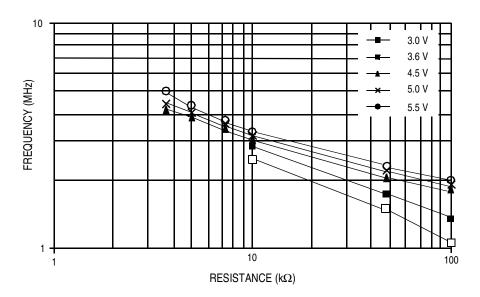

# C.4 Typical Internal Operating Frequency at 25°C for High-Speed RC Oscillator Option

Figure C-1. Typical Internal Operating Frequency at 25°C for High-Speed RC Oscillator Option

For lower frequency operation characteristics, refer to **Appendix A. MC68HRC705J1A**.

**NOTE:** Tolerance for resistance is ±50 percent. When selecting resistor size, consider the tolerance to ensure that resulting oscillator frequency does not exceed the maximum operating frequency.

**Technical Data**

Index

# Freescale Semiconductor, Inc.

| CPU registers                                       |

|-----------------------------------------------------|

| accumulator register (A)48                          |

| index register (X)                                  |

| program counter register (PC)                       |

| stack pointer register (SP)                         |

|                                                     |

| D                                                   |

| data direction registers                            |

| data direction register A (DDRA)                    |

| data direction register B (DDRB)                    |

| data-retention mode                                 |

|                                                     |

| E                                                   |

| ELAT bit                                            |

| electrical specifications                           |

| control timing                                      |

| DC electrical characteristics                       |

| driver characteristics                              |

| maximum ratings                                     |

| MC68HSC705J1A (high-speed option)                   |

| MC68HSR705J1A (high-speed RC oscillator option) 145 |

| operating temperature range                         |

| port A                                              |

| port B                                              |

| power considerations                                |

| thermal resistance                                  |

| typical supply currents                             |

| electrostatic damage                                |

| EPGM bit                                            |

| EPMSEC bit                                          |

| EPROM                                               |

|                                                     |

| EPROM security programmable option                  |

| EPROM/OTPROM                                        |

| erasing                                             |

| programming                                         |

| programming characteristics                         |

| programming register (EPROG)                        |

|                                                     |

| MC68HC705J1A — Rev. 4.0                             |

Index

| I/O circuitry                      | 3 |

|------------------------------------|---|

| pin operation                      | 4 |

| pins                               | 1 |

| port B data register (PORTB)92     |   |

| pulldown register (PDRB)           | 4 |

| power dissipation                  | 0 |

| power-on reset                     | 1 |

| program counter (PC)               | 0 |

| programmable options2              | 5 |

| programming model (CPU)            | 7 |

| pulldown register A (PDRA)9        |   |

| pulldown register B (PDRB)         |   |

| pulldown resistors                 |   |

| programmable option                | 5 |

|                                    |   |

| R                                  |   |

| RAM                                | 7 |

| stack RAM                          | 6 |

| registers                          |   |

| CPU                                |   |

| I/O register summary               |   |

| parallel I/O port register summary |   |

| RESET pin                          | 2 |

| resets                             | 0 |

| COP register (COPR)                |   |

| COP watchdog reset                 |   |

| external reset                     |   |

| external reset timing              |   |

| illegal address                    |   |

| power-on reset (POR)               |   |

| power-on reset timing              |   |

| reset sources                      |   |

| reset/interrupt vector addresses   | 1 |

| resistors (pulldown)               | _ |

| programmable option                |   |

| RT1, RT0 bits                      | 3 |

MC68HC705J1A — Rev. 4.0

Index

| V                   |    |

|---------------------|----|

| V <sub>DD</sub> pin | 25 |

| V <sub>SS</sub> pin | 25 |

| W                   |    |

| WAIT instruction    | 06 |

| wait mode           |    |

| effects on timer    | 15 |

| Z                   |    |

| Z hit               | 51 |

MC68HC705J1A — Rev. 4.0