Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                      |

|----------------------------|----------------------------------------------------------------------|

| Product Status             | Obsolete                                                             |

| Core Processor             | HC05                                                                 |

| Core Size                  | 8-Bit                                                                |

| Speed                      | 4MHz                                                                 |

| Connectivity               | -                                                                    |

| Peripherals                | POR, WDT                                                             |

| Number of I/O              | 14                                                                   |

| Program Memory Size        | 1.2KB (1.2K x 8)                                                     |

| Program Memory Type        | ОТР                                                                  |

| EEPROM Size                | -                                                                    |

| RAM Size                   | 64 x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                            |

| Data Converters            | -                                                                    |

| Oscillator Type            | Internal                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                        |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                                       |

| Supplier Device Package    | 20-SOIC                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc705j1acdwe |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Table of Contents

| 6.1                                              | Contents87                                                                                                                                                                              |

|--------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6.2                                              | Introduction                                                                                                                                                                            |

| 6.3<br>6.3.1<br>6.3.2<br>6.3.3<br>6.3.4<br>6.3.5 | Port A                                                                                                                                                                                  |

| 6.4<br>6.4.1<br>6.4.2<br>6.4.3                   | Port B.92Port B Data Register.92Data Direction Register B.93Pulldown Register B.94                                                                                                      |

| 6.5                                              | 5.0-Volt I/O Port Electrical Characteristics                                                                                                                                            |

| 6.6                                              | 3.3-Volt I/O Port Electrical Characteristics                                                                                                                                            |

|                                                  |                                                                                                                                                                                         |

|                                                  | Section 7. Computer Operating Properly (COP) Module                                                                                                                                     |

| 7.1                                              |                                                                                                                                                                                         |

| 7.1<br>7.2                                       | (COP) Module                                                                                                                                                                            |

|                                                  | (COP) Module  Contents                                                                                                                                                                  |

| 7.2<br>7.3<br>7.3.1<br>7.3.2                     | (COP) Module         Contents       .97         Introduction       .97         Operation       .98         COP Watchdog Timeout       .98         COP Watchdog Timeout Period       .98 |

| 7.2<br>7.3<br>7.3.1<br>7.3.2<br>7.3.3            | Contents                                                                                                                                                                                |

**Table of Contents**

| Appendix B. MC68HSC705J1 | Α |

|--------------------------|---|

|--------------------------|---|

| B.1 | Contents                                                                            |

|-----|-------------------------------------------------------------------------------------|

| B.2 | Introduction141                                                                     |

| B.3 | 5.0-Volt DC Electrical Characteristics142                                           |

| B.4 | 3.3-Volt DC Electrical Characteristics142                                           |

| B.5 | Typical Supply Currents                                                             |

| B.6 | Package Types and Order Numbers144                                                  |

|     | Appendix C. MC68HSR705J1A                                                           |

| C.1 | Contents                                                                            |

| C.2 | Introduction                                                                        |

| C.3 | RC Oscillator Connections (External Resistor)145                                    |

| C.4 | Typical Internal Operating Frequency at 25°C for High-Speed RC Oscillator Option146 |

| C.5 | RC Oscillator Connections (No External Resistor)                                    |

| C.6 | Typical Internal Operating Frequency versus Temperature (No External Resistor)      |

| C.7 | Package Types and Order Numbers149                                                  |

|     | Index                                                                               |

|     | Index 151                                                                           |

MC68HC705J1A — Rev. 4.0

### **General Description**

#### 1.3 Features

#### Features of the MC68HC705J1A include:

- Peripheral modules:

- 15-stage multifunction timer

- Computer operating properly (COP) watchdog

- 14 bidirectional input/output (I/O) lines, including:

- 10-mA sink capability on four I/O pins

- Mask option register (MOR) and software programmable pulldowns on all I/O pins

- MOR selectable interrupt on four I/O pins, a keyboard scan feature

- MOR selectable sensitivity on external interrupt (edge- and level-sensitive or edge-sensitive only)

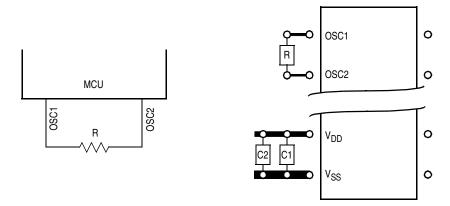

- On-chip oscillator with connections for:

- Crystal

- Ceramic resonator

- Resistor-capacitor (RC) oscillator

- External clock

- 1240 bytes of EPROM/OTPROM, including eight bytes for user vectors

- 64 bytes of user random-access memory (RAM)

- Memory-mapped I/O registers

- Fully static operation with no minimum clock speed

- Power-saving stop, halt, wait, and data-retention modes

- External interrupt mask bit and acknowledge bit

- Illegal address reset

- Internal steering diode and pullup resistor from RESET pin to V<sub>DD</sub>

### **General Description**

1.5.2.3 RC Oscillator

Refer to Appendix A. MC68HRC705J1A and Appendix C. MC68HSR705J1A.

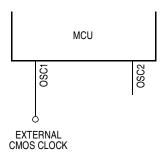

#### 1.5.2.4 External Clock

An external clock from another complementary metal-oxide semiconductor (CMOS)-compatible device can be connected to the OSC1 input, with the OSC2 input not connected, as shown in Figure 1-8. This configuration is possible regardless of whether the crystal/ceramic resonator or the RC oscillator is enabled.

Figure 1-8. External Clock Connections

### 1.6 RESET

Applying a logic 0 to the  $\overline{\text{RESET}}$  pin forces the MCU to a known startup state. An internal reset also pulls the  $\overline{\text{RESET}}$  pin low. An internal resistor to  $V_{DD}$  pulls the  $\overline{\text{RESET}}$  pin high. A steering diode between the  $\overline{\text{RESET}}$  and  $V_{DD}$  pins discharges any  $\overline{\text{RESET}}$  pin voltage when power is removed from the MCU. The  $\overline{\text{RESET}}$  pin contains an internal Schmitt trigger to improve its noise immunity as an input. Refer to **Section 4. Resets and Interrupts** for more information.

**General Description**

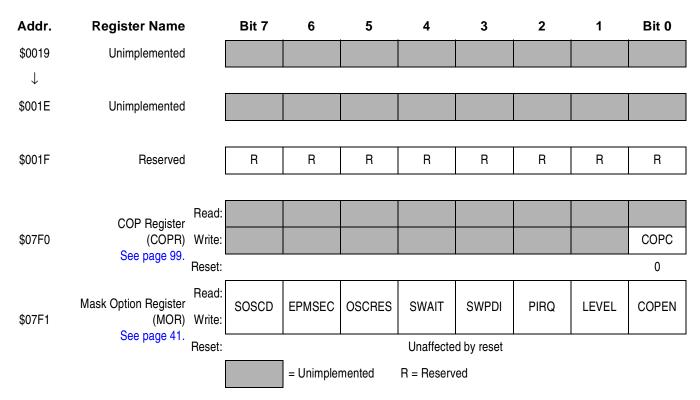

Figure 2-2. I/O Register Summary (Sheet 3 of 3)

#### 2.5 **RAM**

The 64 addresses from \$00C0 to \$00FF serve as both the user RAM and the stack RAM. Before processing an interrupt, the central processor unit (CPU) uses five bytes of the stack to save the contents of the CPU registers. During a subroutine call, the CPU uses two bytes of the stack to store the return address. The stack pointer decrements when the CPU stores a byte on the stack and increments when the CPU retrieves a byte from the stack.

#### **NOTE:**

Be careful when using nested subroutines or multiple interrupt levels. The CPU may overwrite data in the RAM during a subroutine or during the interrupt stacking operation.

Central Processor Unit (CPU)

CPU Registers

### H — Half-Carry Flag

The CPU sets the half-carry flag when a carry occurs between bits 3 and 4 of the accumulator during an ADD (add without carry) or ADC (add with carry) operation. The half-carry flag is required for binary-coded decimal (BCD) arithmetic operations.

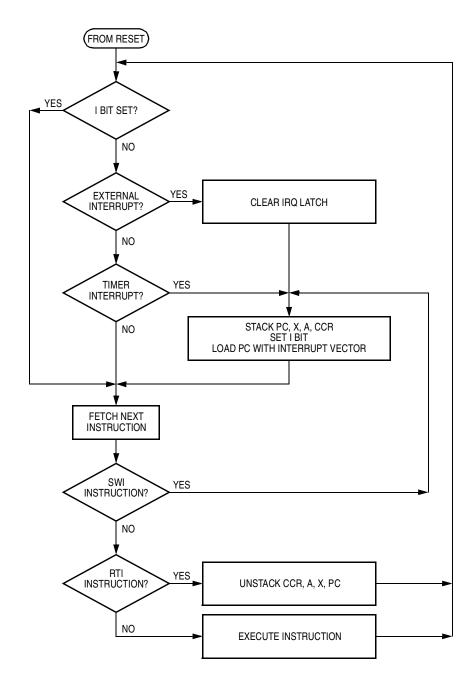

#### I — Interrupt Mask Bit

Setting the interrupt mask disables interrupts. If an interrupt request occurs while the interrupt mask is logic 0, the CPU saves the CPU registers on the stack, sets the interrupt mask, and then fetches the interrupt vector. If an interrupt request occurs while the interrupt mask is logic 1, the interrupt request is latched. Normally, the CPU processes the latched interrupt request as soon as the interrupt mask is cleared again.

A return-from-interrupt instruction (RTI) unstacks the CPU registers, restoring the interrupt mask to its cleared state. After any reset, the interrupt mask is set and can be cleared only by a software instruction.

### N — Negative Flag

The CPU sets the negative flag when an ALU operation produces a negative result.

#### Z — Zero Flag

The CPU sets the zero flag when an ALU operation produces a result of \$00.

#### C — Carry/Borrow Flag

The CPU sets the carry/borrow flag when an addition operation produces a carry out of bit 7 of the accumulator or when a subtraction operation requires a borrow. Some logical operations and data manipulation instructions also clear or set the carry/borrow flag.

MC68HC705J1A — Rev. 4.0

Central Processor Unit (CPU) Instruction Set Summary

# 3.7 Instruction Set Summary

Table 3-6. Instruction Set Summary (Sheet 1 of 6)

| Source<br>Form                                                       | Operation                             | Description                           | Effect on CCR |   |          |   | <b>!</b> | Address<br>Mode                                                         | Opcode                           | Operand                                | Cycles                     |

|----------------------------------------------------------------------|---------------------------------------|---------------------------------------|---------------|---|----------|---|----------|-------------------------------------------------------------------------|----------------------------------|----------------------------------------|----------------------------|

| FOIIII                                                               |                                       |                                       |               |   | N        | Z | С        | Adc                                                                     | op                               | obe                                    | ပ်                         |

| ADC #opr<br>ADC opr<br>ADC opr,X<br>ADC opr,X<br>ADC opr,X<br>ADC ,X | Add with Carry                        | $A \leftarrow (A) + (M) + (C)$        | ‡             | _ | <b>‡</b> | ţ | ‡        | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX                                   | A9<br>B9<br>C9<br>D9<br>E9<br>F9 | ii<br>dd<br>hh II<br>ee ff<br>ff       | 2<br>3<br>4<br>5<br>4<br>3 |

| ADD #opr<br>ADD opr<br>ADD opr,X<br>ADD opr,X<br>ADD opr,X<br>ADD ,X | Add without Carry                     | A ← (A) + (M)                         | t             | _ | <b>‡</b> | ţ | ‡        | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX                                   | AB<br>BB<br>CB<br>DB<br>EB<br>FB | ii<br>dd<br>hh II<br>ee ff<br>ff       | 2<br>3<br>4<br>5<br>4<br>3 |

| AND #opr<br>AND opr<br>AND opr,<br>AND opr,X<br>AND opr,X<br>AND ,X  | Logical AND                           | $A \leftarrow (A) \wedge (M)$         |               | _ | <b>‡</b> | ţ | _        | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX                                   | A4<br>B4<br>C4<br>D4<br>E4<br>F4 | ii<br>dd<br>hh II<br>ee ff<br>ff       | 2<br>3<br>4<br>5<br>4<br>3 |

| ASL opr<br>ASLA<br>ASLX<br>ASL opr,X<br>ASL ,X                       | Arithmetic Shift Left (Same as LSL)   | C ←                                   | _             | _ | <b>‡</b> | ţ | ‡        | DIR<br>INH<br>INH<br>IX1<br>IX                                          | 38<br>48<br>58<br>68<br>78       | dd<br>ff                               | 5<br>3<br>3<br>6<br>5      |

| ASR opr<br>ASRA<br>ASRX<br>ASR opr,X<br>ASR ,X                       | Arithmetic Shift Right                | b7 b0                                 | _             | _ | ‡        | ţ | ‡        | DIR<br>INH<br>INH<br>IX1<br>IX                                          | 37<br>47<br>57<br>67<br>77       | dd<br>ff                               | 5<br>3<br>3<br>6<br>5      |

| BCC rel                                                              | Branch if Carry Bit Clear             | $PC \leftarrow (PC) + 2 + rel? C = 0$ | _             | _ | _        |   | _        | REL                                                                     | 24                               | rr                                     | 3                          |

| BCLR n opr                                                           | Clear Bit n                           | Mn ← 0                                | _             | _ | _        |   |          | DIR (b0) DIR (b1) DIR (b2) DIR (b3) DIR (b4) DIR (b5) DIR (b6) DIR (b7) | 13<br>15<br>17<br>19<br>1B<br>1D | dd<br>dd<br>dd<br>dd<br>dd<br>dd<br>dd | 5 5 5 5 5 5 5 5 5          |

| BCS rel                                                              | Branch if Carry Bit Set (Same as BLO) | PC ← (PC) + 2 + rel? C = 1            | 1-            | _ | _        | _ | _        | REL                                                                     | 25                               | rr                                     | 3                          |

| BEQ rel                                                              | Branch if Equal                       | PC ← (PC) + 2 + rel? Z = 1            | <u> </u>      | _ | _        | _ | <u> </u> | REL                                                                     | 27                               | rr                                     | 3                          |

| BHCC rel                                                             | Branch if Half-Carry Bit Clear        | PC ← (PC) + 2 + rel? H = 0            | -             | _ | _        | _ | <u> </u> | REL                                                                     | 28                               | rr                                     | 3                          |

| BHCS rel                                                             | Branch if Half-Carry Bit Set          | PC ← (PC) + 2 + rel? H = 1            | -             | _ | _        | _ | <u> </u> | REL                                                                     | 29                               | rr                                     | 3                          |

MC68HC705J1A — Rev. 4.0

# Central Processor Unit (CPU)

Table 3-6. Instruction Set Summary (Sheet 4 of 6)

| Source                                                             | Operation Description                | Description                                                                                                                                                                                           |   |   |          |   |   | Effect on CCR                         |                                  |                                  |                            |  |  | Opcode | Operand | Cycles |

|--------------------------------------------------------------------|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|----------|---|---|---------------------------------------|----------------------------------|----------------------------------|----------------------------|--|--|--------|---------|--------|

| Form                                                               | Operation                            | Description                                                                                                                                                                                           | Н | I | N        | Z | С | Add                                   | odo                              | Ope                              | S                          |  |  |        |         |        |

| JMP opr<br>JMP opr<br>JMP opr,X<br>JMP opr,X<br>JMP ,X             | Unconditional Jump                   | PC ← Jump Address                                                                                                                                                                                     |   | _ | _        | _ | _ | DIR<br>EXT<br>IX2<br>IX1<br>IX        | BC<br>CC<br>DC<br>EC<br>FC       | dd<br>hh II<br>ee ff<br>ff       | 2<br>3<br>4<br>3<br>2      |  |  |        |         |        |

| JSR opr<br>JSR opr<br>JSR opr,X<br>JSR opr,X<br>JSR ,X             | Jump to Subroutine                   | $PC \leftarrow (PC) + n (n = 1, 2, or 3)$ $Push (PCL); SP \leftarrow (SP) - 1$ $Push (PCH); SP \leftarrow (SP) - 1$ $PC \leftarrow Effective Address$                                                 |   | _ | _        | _ |   | DIR<br>EXT<br>IX2<br>IX1<br>IX        | BD<br>CD<br>DD<br>ED<br>FD       | dd<br>hh II<br>ee ff<br>ff       | 5<br>6<br>7<br>6<br>5      |  |  |        |         |        |

| LDA #opr<br>LDA opr<br>LDA opr<br>LDA opr,X<br>LDA opr,X<br>LDA ,X | Load Accumulator with Memory Byte    | A ← (M)                                                                                                                                                                                               |   | _ | <b>‡</b> | t | _ | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX | A6<br>B6<br>C6<br>D6<br>E6<br>F6 | ii<br>dd<br>hh II<br>ee ff<br>ff | 2<br>3<br>4<br>5<br>4<br>3 |  |  |        |         |        |

| LDX #opr<br>LDX opr<br>LDX opr<br>LDX opr,X<br>LDX opr,X<br>LDX ,X | Load Index Register with Memory Byte | X ← (M)                                                                                                                                                                                               | _ |   | ‡        | ‡ | _ | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX | AE<br>BE<br>CE<br>DE<br>EE<br>FE | ii<br>dd<br>hh II<br>ee ff<br>ff | 2<br>3<br>4<br>5<br>4<br>3 |  |  |        |         |        |

| LSL opr<br>LSLA<br>LSLX<br>LSL opr,X<br>LSL ,X                     | Logical Shift Left (Same as ASL)     | C - 0 b0                                                                                                                                                                                              |   | _ | <b>‡</b> | t | ‡ | DIR<br>INH<br>INH<br>IX1<br>IX        | 38<br>48<br>58<br>68<br>78       | dd<br>ff                         | 5 3 3 6 5                  |  |  |        |         |        |

| LSR opr<br>LSRA<br>LSRX<br>LSR opr,X<br>LSR ,X                     | Logical Shift Right                  | 0                                                                                                                                                                                                     |   | _ | 0        | t | ‡ | DIR<br>INH<br>INH<br>IX1<br>IX        | 34<br>44<br>54<br>64<br>74       | dd<br>ff                         | 5<br>3<br>3<br>6<br>5      |  |  |        |         |        |

| MUL                                                                | Unsigned Multiply                    | $X : A \leftarrow (X) \times (A)$                                                                                                                                                                     | 0 | _ | _        | _ | 0 | INH                                   | 42                               |                                  | 11                         |  |  |        |         |        |

| NEG opr<br>NEGA<br>NEGX<br>NEG opr,X<br>NEG ,X                     | Negate Byte (Two's Complement)       | $\begin{array}{c} M \leftarrow -(M) = \$00 - (M) \\ A \leftarrow -(A) = \$00 - (A) \\ X \leftarrow -(X) = \$00 - (X) \\ M \leftarrow -(M) = \$00 - (M) \\ M \leftarrow -(M) = \$00 - (M) \end{array}$ | _ | _ | <b>‡</b> | 1 | ‡ | DIR<br>INH<br>INH<br>IX1<br>IX        | 30<br>40<br>50<br>60<br>70       | dd<br>ff                         | 5 3 3 6 5                  |  |  |        |         |        |

| NOP                                                                | No Operation                         |                                                                                                                                                                                                       | - | _ | _        | - | - | INH                                   | 9D                               |                                  | 2                          |  |  |        |         |        |

| ORA #opr<br>ORA opr<br>ORA opr<br>ORA opr,X<br>ORA opr,X<br>ORA ,X | Logical OR Accumulator with Memory   | $A \leftarrow (A) \vee (M)$                                                                                                                                                                           |   |   | ‡        | t | _ | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX | AA<br>BA<br>CA<br>DA<br>EA<br>FA | ii<br>dd<br>hh II<br>ee ff<br>ff | 2<br>3<br>4<br>5<br>4<br>3 |  |  |        |         |        |

## **Resets and Interrupts**

Figure 4-7. Interrupt Flowchart

# **Computer Operating Properly (COP) Module**

#### 7.6 Low-Power Modes

The STOP and WAIT instructions have these effects on the COP watchdog.

### 7.6.1 Stop Mode

The STOP instruction clears the COP watchdog counter and disables the clock to the COP watchdog.

NOTE:

To prevent the STOP instruction from disabling the COP watchdog, program the stop-to-wait conversion bit (SWAIT) in the mask option register to logic 1.

Upon exit from stop mode by external reset:

- The counter begins counting from \$0000.

- The counter is cleared again after the oscillator stabilization delay and begins counting from \$0000 again.

Upon exit from stop mode by external interrupt:

- The counter begins counting from \$0000.

- The counter is not cleared again after the oscillator stabilization delay and continues counting throughout the oscillator stabilization delay.

NOTE:

Immediately after exiting stop mode by external interrupt, service the COP to ensure a full COP timeout period.

#### 7.6.2 Wait Mode

The WAIT instruction has no effect on the COP watchdog.

**NOTE:**

To prevent a COP timeout during wait mode, exit wait mode periodically to service the COP.

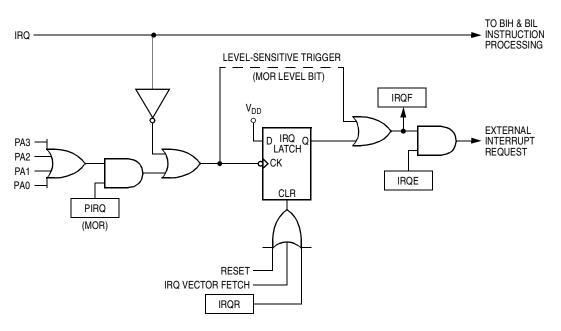

### External Interrupt Module (IRQ)

### 8.3 Operation

The interrupt request/programming voltage pin  $(\overline{IRQ}/V_{PP})$  and port A pins 0–3 (PA0–PA3) provide external interrupts. The PIRQ bit in the mask option register (MOR) enables PA0–PA3 as IRQ interrupt sources, which are combined into a single ORing function to be latched by the IRQ latch. **Figure 8-1** shows the structure of the IRQ module.

After completing its current instruction, the CPU tests the IRQ latch. If the IRQ latch is set, the CPU then tests the I bit in the condition code register and the IRQE bit in the IRQ status and control register. If the I bit is clear and the IRQE bit is set, the CPU then begins the interrupt sequence. This interrupt is serviced by the interrupt service routine located at \$07FA and \$07FB.

The CPU clears the IRQ latch while it fetches the interrupt vector, so that another external interrupt request can be latched during the interrupt service routine. As soon as the I bit is cleared during the return from interrupt, the CPU can recognize the new interrupt request. **Figure 8-2** shows the sequence of events caused by an interrupt.

Figure 8-1. IRQ Module Block Diagram

External Interrupt Module (IRQ)

### **Multifunction Timer Module**

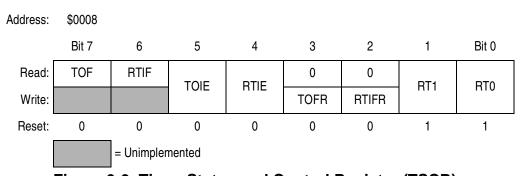

## 9.4 Interrupts

These timer sources can generate interrupts:

- Timer overflow flag (TOF) The TOF bit is set when the first eight stages of the counter roll over from \$FF to \$00. The timer overflow interrupt enable bit, TOIE, enables TOF interrupt requests.

- Real-time interrupt flag (RTIF) The RTIF bit is set when the selected RTI output becomes active. The real-time interrupt enable bit, RTIE, enables RTIF interrupt requests.

### 9.5 I/O Registers

These registers control and monitor the timer operation:

- Timer status and control register (TSCR)

- Timer counter register (TCR)

### 9.5.1 Timer Status and Control Register

The read/write timer status and control register (TSCR) performs these functions:

- Flags timer interrupts

- Enables timer interrupts

- Resets timer interrupt flags

- Selects real-time interrupt rates

Figure 9-3. Timer Status and Control Register (TSCR)

### **Multifunction Timer Module**

interrupt request to be generated. To prevent this occurrence, clear the COP timer before changing RT1 and RT0.

Table 9-1. Real-Time Interrupt Rate Selection

| RT1:RT0 | Number<br>of Cycles<br>to RTI | RTI<br>Period <sup>(1)</sup> | Number<br>of Cycles<br>to COP Reset | COP Timeout<br>Period <sup>(1)</sup> |

|---------|-------------------------------|------------------------------|-------------------------------------|--------------------------------------|

| 0 0     | 2 <sup>14</sup> = 16,384      | 8.2 ms                       | $2^{17} = 131,072$                  | 65.5 ms                              |

| 0 1     | $2^{15} = 32,768$             | 16.4 ms                      | $2^{18} = 262,144$                  | 131.1 ms                             |

| 1 0     | $2^{16} = 65,536$             | 32.8 ms                      | $2^{19} = 524,288$                  | 262.1 ms                             |

| 1 1     | $2^{17} = 131,072$            | 65.5 ms                      | $2^{20} = 1,048,576$                | 524.3 ms                             |

<sup>1.</sup> At 2-MHz bus, 4-MHz XTAL, 0.5 µs per cycle

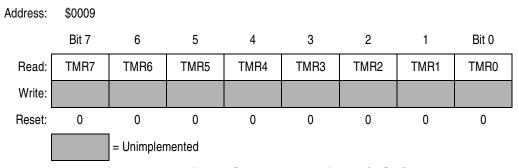

### 9.5.2 Timer Counter Register

A 15-stage ripple counter is the core of the timer. The value of the first eight stages is readable at any time from the read-only timer counter register (TCR) shown in **Figure 9-4**.

Figure 9-4. Timer Counter Register (TCR)

Power-on clears the entire counter chain and the internal clock begins clocking the counter. After 4064 cycles (or 16 cycles if the SOSCD bit in the mask option register is set), the power-on reset circuit is released, clearing the counter again and allowing the MCU to come out of reset.

A timer overflow function at the eighth counter stage allows a timer interrupt every 1024 internal clock cycles.

Electrical Specifications

Operating Temperature Range

## 10.4 Operating Temperature Range

| Package Type                                                        | Symbol         | Value<br>(T <sub>L</sub> to T <sub>H</sub> ) | Unit |

|---------------------------------------------------------------------|----------------|----------------------------------------------|------|

| MC68HC705J1AP <sup>(1)</sup> , DW <sup>(2)</sup> , S <sup>(3)</sup> | T <sub>A</sub> | 0 to 70                                      | °C   |

| MC68HC705J1AC <sup>(4)</sup> P, CDW, CS                             | T <sub>A</sub> | -40 to +85                                   | °C   |

| MC68HC705J1AV <sup>(5)</sup> P, VDW, VS                             | T <sub>A</sub> | -40 to +105                                  | °C   |

- 1. P = plastic dual in-line package (PDIP)

- 2. DW = small outline integrated circuit (SOIC)

- 3. S = ceramic DIP (cerdip)

- 4. C = extended temperature range

- 5. V = automotive temperature range

### 10.5 Thermal Characteristics

| Characteristic                                                                                             | Symbol            | Value | Unit |

|------------------------------------------------------------------------------------------------------------|-------------------|-------|------|

| Thermal resistance MC68HC705J1AP <sup>(1)</sup> MC68HC705J1ADW <sup>(2)</sup> MC68HC705J1AS <sup>(3)</sup> | $\theta_{\sf JA}$ | 60    | °C/W |

- 1. P = plastic dual in-line package (PDIP)

- 2. DW = small outline integrated circuit (SOIC)

- 3. S = ceramic DIP (cerdip)

Electrical Specifications 5.0-Volt DC Electrical Characteristics

#### 10.7 5.0-Volt DC Electrical Characteristics

| Characteristic <sup>(1)</sup>                                                                                                              | Symbol                             | Min                       | Typ <sup>(2)</sup>        | Max                     | Unit                 |

|--------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|---------------------------|---------------------------|-------------------------|----------------------|

| Output voltage $I_{Load} = 10.0 \ \mu A$ $I_{Load} = -10.0 \ \mu A$                                                                        | V <sub>OL</sub><br>V <sub>OH</sub> | <br>V <sub>DD</sub> – 0.1 | _                         | 0.1                     | V                    |

| Output high voltage<br>(I <sub>Load</sub> = -0.8 mA) PA0-PA7, PB0-PB5                                                                      | V <sub>OH</sub>                    | V <sub>DD</sub> – 0.8     | _                         | _                       | V                    |

| Output low voltage (I <sub>Load</sub> = 1.6 mA) PA0–PA3, PB0–PB5 (I <sub>Load</sub> = 10.0 mA) PA4–PA7                                     | V <sub>OL</sub>                    | _                         | _                         | 0.4<br>0.4              | V                    |

| Input high voltage PA0–PA7, PB0–PB5, IRQ/V <sub>PP</sub> , RESET, OSC1                                                                     | V <sub>IH</sub>                    | $0.7 \times V_{DD}$       | _                         | V <sub>DD</sub>         | V                    |

| Input low voltage PA0-PA7, PB0-PB5, IRQ/V <sub>PP</sub> , RESET, OSC1                                                                      | V <sub>IL</sub>                    | V <sub>SS</sub>           | _                         | $0.2 \times V_{DD}$     | V                    |

| Supply current Run mode <sup>(3)</sup> Wait mode <sup>(4)</sup> Stop mode <sup>(5)</sup> 25°C                                              | I <sub>DD</sub>                    |                           | 3.5<br>0.45<br>0.2<br>2.0 | 6.0<br>2.75<br>10<br>20 | mA<br>mA<br>μA<br>μA |

| <ul> <li>-40 to 105°C</li> <li>I/O ports hi-z leakage current</li> <li>PA0-PA7, PB0-PB5 (without individual pulldown activated)</li> </ul> | I <sub>IL</sub>                    | _                         | 0.2                       | ±1                      | μΑ                   |

| Input pulldown current PA0–PA7, PB0–PB5 (with individual pulldown activated)                                                               | I <sub>IL</sub>                    | 35                        | 80                        | 200                     | μΑ                   |

| Input pullup current RESET                                                                                                                 | I <sub>IL</sub>                    | -15                       | -35                       | -85                     | μΑ                   |

| Input current <sup>(6)</sup> RESET, IRQ/V <sub>PP</sub> , OSC1                                                                             | I <sub>In</sub>                    | _                         | 0.2                       | ±1                      | μΑ                   |

| Capacitance Ports (as inputs or outputs) RESET, IRQ/V <sub>PP</sub> , OSC1, OSC2                                                           | C <sub>Out</sub>                   |                           |                           | 12<br>8                 | pF                   |

| Crystal/ceramic resonator oscillator mode internal resistor OSC1 to OSC2 <sup>(7)</sup>                                                    | R <sub>osc</sub>                   | 1.0                       | 2.0                       | 3.0                     | МΩ                   |

- 1.  $V_{DD}$  = 5.0 Vdc  $\pm$  10%,  $V_{SS}$  = 0 Vdc,  $T_A$  = -40°C to +105°C, unless otherwise noted

- 2. Typical values at midpoint of voltage range, 25°C only

- 3. Run mode  $I_{DD}$  is measured using external square wave clock source ( $f_{osc} = 4.2$  MHz); all inputs 0.2 V from rail; no dc loads; less than 50 pF on all outputs;  $C_L = 20$  pF on OSC2

- 4. Wait mode  $I_{DD}$ : only timer system active. Wait mode is affected linearly by OSC2 capacitance. Wait mode is measured with all ports configured as inputs;  $V_{IL} = 0.2 \text{ V}$ ;  $V_{IH} = V_{DD} 0.2 \text{ V}$ . Wait mode  $I_{DD}$  is measured using external square wave clock source ( $f_{osc} = 4.2 \text{ MHz}$ ); all inputs 0.2 V from rail; no dc loads; less than 50 pF on all outputs;  $C_L = 20 \text{ pF}$  on OSC2.

- 5. Stop mode  $I_{DD}$  is measured with OSC1 =  $V_{SS}$ . Stop mode  $I_{DD}$  is measured with all ports configured as inputs;  $V_{IL} = 0.2 \text{ V}$ ;  $V_{IH} = V_{DD} 0.2 \text{ V}$

- 6. Only input high current rated to +1  $\mu$ A on RESET.

- The R<sub>osc</sub> value selected for RC oscillator versions of this device is unspecified. See Appendix C. MC68HSR705J1A for additional information.

MC68HC705J1A — Rev. 4.0

#### Technical Data — MC68HC705J1A

# **Section 12. Ordering Information**

#### 12.1 Contents

| 12.2 | Introduction      | 135 |

|------|-------------------|-----|

| 12.3 | MCU Order Numbers | 135 |

#### 12.2 Introduction

This section contains ordering information for the available package types.

#### 12.3 MCU Order Numbers

Table 12-1 lists the MC order numbers.

**Table 12-1. Order Numbers**

| Package<br>Type | Case<br>Outline | Pin<br>Count | Operating<br>Temperature                   | Order Number <sup>(1)</sup>                                                                      |

|-----------------|-----------------|--------------|--------------------------------------------|--------------------------------------------------------------------------------------------------|

| PDIP            | 738-03          | 20           | 0 to 70°C<br>-40 to +85°C<br>-40 to +105°C | MC68HC705J1AP <sup>(2)</sup><br>MC68HC705J1AC <sup>(3)</sup> P<br>MC68HC705J1AV <sup>(4)</sup> P |

| SOIC            | 751D-04         | 20           | 0 to 70°C<br>-40 to +85°C<br>-40 to +105°C | MC68HC705J1ADW <sup>(5)</sup><br>MC68HC705J1ACDW<br>MC68HC705J1AVDW                              |

| Cerdip          | 732-03          | 20           | 0 to 70°C<br>-40 to +85°C<br>-40 to +105°C | MC68HC705J1AS <sup>(6)</sup><br>MC68HC705J1ACS<br>MC68HC705J1AVS                                 |

Refer to Appendix A. MC68HRC705J1A, Appendix B. MC68HSC705J1A, and Appendix C. MC68HSR705J1A for ordering information on optional high-speed and resistor-capacitor oscillator devices.

- 2. P = Plastic dual in-line package (PDIP)

- 3. C = Extended temperature range

- 4. V = Automotive temperature range

- 5. DW = Small outline integrated circuit (SOIC)

- 6. S = Ceramic dual in-line package (cerdip)

MC68HC705J1A — Rev. 4.0

### MC68HRC705J1A

#### A.3 RC Oscillator Connections

For greater cost reduction, the RC oscillator mask option allows the configuration shown in **Figure A-1** to drive the on-chip oscillator. Mount the RC components as close as possible to the pins for startup stabilization and to minimize output distortion.

**Figure A-1. RC Oscillator Connections**

**NOTE:** The optional internal resistor is **not** recommended for configurations that use the RC oscillator connections as shown in **Figure A-1**. For such configurations, the oscillator internal resistor (OSCRES) bit of the mask option register should be programmed to a logic 0.

**Technical Data**

Index

# Freescale Semiconductor, Inc.

| CPU registers                                       |

|-----------------------------------------------------|

| accumulator register (A)48                          |

| index register (X)                                  |

| program counter register (PC)                       |

| stack pointer register (SP)                         |

|                                                     |

| D                                                   |

| data direction registers                            |

| data direction register A (DDRA)                    |

| data direction register B (DDRB)                    |

| data-retention mode                                 |

|                                                     |

| E                                                   |

| ELAT bit                                            |

| electrical specifications                           |

| control timing                                      |

| DC electrical characteristics                       |

| driver characteristics                              |

| maximum ratings                                     |

| MC68HSC705J1A (high-speed option)                   |

| MC68HSR705J1A (high-speed RC oscillator option) 145 |

| operating temperature range                         |

| port A                                              |

| port B                                              |

| power considerations                                |

| thermal resistance                                  |

| typical supply currents                             |

| electrostatic damage                                |

| EPGM bit                                            |

| EPMSEC bit                                          |

| EPROM                                               |

|                                                     |

| EPROM security programmable option                  |

| EPROM/OTPROM                                        |

| erasing                                             |

| programming                                         |

| programming characteristics                         |

| programming register (EPROG)                        |

|                                                     |

| MC68HC705J1A — Rev. 4.0                             |