Welcome to **E-XFL.COM**

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                              |

|----------------------------|--------------------------------------------------------------|

| Product Status             | Active                                                       |

| Core Processor             | HC05                                                         |

| Core Size                  | 8-Bit                                                        |

| Speed                      | 4MHz                                                         |

| Connectivity               | -                                                            |

| Peripherals                | POR, WDT                                                     |

| Number of I/O              | 14                                                           |

| Program Memory Size        | 1.2KB (1.2K x 8)                                             |

| Program Memory Type        | OTP                                                          |

| EEPROM Size                | -                                                            |

| RAM Size                   | 64 x 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                    |

| Data Converters            | -                                                            |

| Oscillator Type            | Internal                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                            |

| Mounting Type              | Surface Mount                                                |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                               |

| Supplier Device Package    | 20-SOIC                                                      |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mchrc705j1acdwe |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **List of Sections**

| Section 1. General Description21                      |

|-------------------------------------------------------|

| Section 2. Memory33                                   |

| Section 3. Central Processor Unit (CPU)45             |

| Section 4. Resets and Interrupts                      |

| Section 5. Low-Power Modes79                          |

| Section 6. Parallel Input/Output (I/O) Ports87        |

| Section 7. Computer Operating Properly (COP) Module97 |

| Section 8. External Interrupt Module (IRQ)101         |

| Section 9. Multifunction Timer Module                 |

| Section 10. Electrical Specifications117              |

| Section 11. Mechanical Specifications                 |

| Section 12. Ordering Information                      |

| Appendix A. MC68HRC705J1A137                          |

| Appendix B. MC68HSC705J1A141                          |

| Appendix C. MC68HSR705J1A145                          |

| Index                                                 |

MC68HC705J1A — Rev. 4.0

# **General Description**

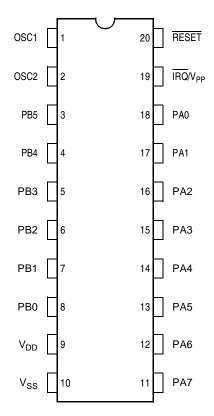

Figure 1-2. Pin Assignments

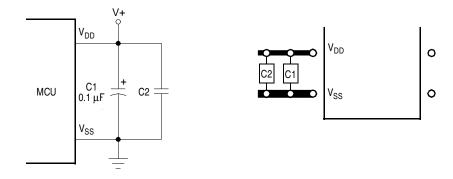

Figure 1-3. Bypassing Layout Recommendation

Memory

Mask Option Register

Take these steps to program the mask option register:

- 1. Apply the programming voltage,  $V_{PP}$ , to the  $\overline{IRQ}/V_{PP}$  pin.

- 2. Write to the MOR.

- 3. Set the MPGM bit and wait for a time, t<sub>MPGM</sub>.

- Clear the MPGM bit.

- 5. Reset the MCU.

Figure 2-4. Mask Option Register (MOR)

SOSCD — Short Oscillator Delay Bit

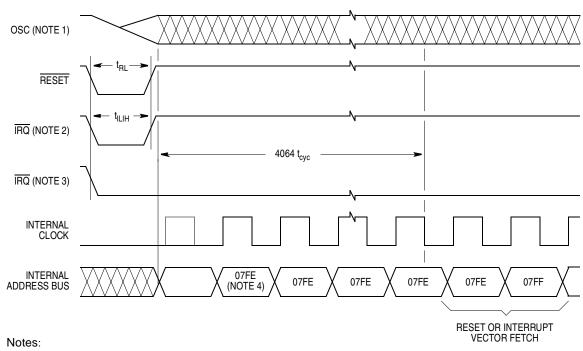

The SOSCD bit controls the oscillator stabilization counter. The normal stabilization delay following reset or exit from stop mode is 4064  $t_{\rm cyc}$ . Setting SOSCD enables a short oscillator stabilization delay.

- 1 = Short oscillator delay enabled

- 0 = Short oscillator delay disabled

EPMSEC — EPROM Security Bit

The EPMSEC bit controls access to the EPROM/OTPROM.

- 1 = External access to EPROM/OTPROM denied

- 0 = External access to EPROM/OTPROM not denied

OSCRES — Oscillator Internal Resistor Bit

The OSCRES bit enables a 2-M $\Omega$  internal resistor in the oscillator circuit.

- 1 = Oscillator internal resistor enabled

- 0 = Oscillator internal resistor disabled

**NOTE:** Program the OSCRES bit to logic 0 in devices using RC oscillators.

MC68HC705J1A — Rev. 4.0

# **Section 3. Central Processor Unit (CPU)**

### 3.1 Contents

| 3.2                     | 2 In  | ntroduction                    | 46           |

|-------------------------|-------|--------------------------------|--------------|

| 3.3                     | 3 CI  | PU Control Unit                | 46           |

| 3.4                     | 4 Ar  | rithmetic/Logic Unit           | 46           |

| 3.5                     | 5 CI  | PU Registers                   | 48           |

| 3.5                     | 5.1   | Accumulator                    | 48           |

| 3.5                     | 5.2   | Index Register                 | 48           |

| 3.5                     | 5.3   | Stack Pointer                  | 49           |

| 3.5                     | 5.4   | Program Counter                | 50           |

| 3.5                     | 5.5   | Condition Code Register        | 50           |

| 3.6                     | 6 In  | nstruction Set                 | 52           |

| 3.6                     | 6.1   | Addressing Modes               | 52           |

| 3.6                     | 6.1.1 | Inherent                       | 52           |

| 3.6                     | 6.1.2 | Immediate                      | 52           |

| 3.6                     | 6.1.3 | Direct                         | 53           |

| 3.6                     | 6.1.4 | Extended                       | 53           |

| 3.6                     | 6.1.5 | Indexed, No Offset             | 53           |

| 3.6                     | 6.1.6 | Indexed, 8-Bit Offset          | 53           |

| 3.6                     | 6.1.7 | Indexed, 16-Bit Offset         | 54           |

| 3.6                     | 6.1.8 | Relative                       | 54           |

| 3.6                     | 6.2   | Instruction Types              | 55           |

| 3.6                     | 6.2.1 | Register/Memory Instructions   | 55           |

| 3.6                     | 6.2.2 | Read-Modify-Write Instructions | 56           |

| 3.6                     | 6.2.3 | Jump/Branch Instructions       | 57           |

| 3.6                     | 6.2.4 | Bit Manipulation Instructions  | 59           |

| 3.6                     | 6.2.5 | Control Instructions           | 60           |

| 3.7                     | 7 In  | nstruction Set Summary         | 61           |

| 3.8                     | 8 O   | pcode Map                      | 66           |

| MC68HC705J1A — Rev. 4.0 |       | Te                             | chnical Data |

Central Processor Unit (CPU)

Central Processor Unit (CPU)

CPU Registers

### H — Half-Carry Flag

The CPU sets the half-carry flag when a carry occurs between bits 3 and 4 of the accumulator during an ADD (add without carry) or ADC (add with carry) operation. The half-carry flag is required for binary-coded decimal (BCD) arithmetic operations.

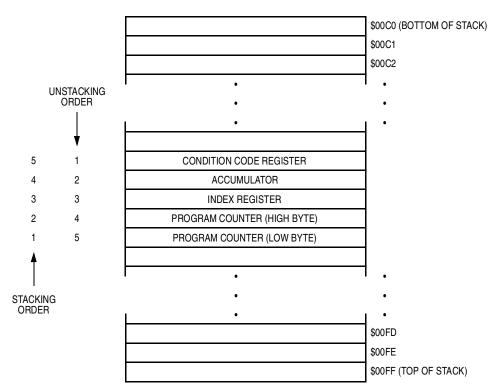

#### I — Interrupt Mask Bit

Setting the interrupt mask disables interrupts. If an interrupt request occurs while the interrupt mask is logic 0, the CPU saves the CPU registers on the stack, sets the interrupt mask, and then fetches the interrupt vector. If an interrupt request occurs while the interrupt mask is logic 1, the interrupt request is latched. Normally, the CPU processes the latched interrupt request as soon as the interrupt mask is cleared again.

A return-from-interrupt instruction (RTI) unstacks the CPU registers, restoring the interrupt mask to its cleared state. After any reset, the interrupt mask is set and can be cleared only by a software instruction.

### N — Negative Flag

The CPU sets the negative flag when an ALU operation produces a negative result.

#### Z — Zero Flag

The CPU sets the zero flag when an ALU operation produces a result of \$00.

### C — Carry/Borrow Flag

The CPU sets the carry/borrow flag when an addition operation produces a carry out of bit 7 of the accumulator or when a subtraction operation requires a borrow. Some logical operations and data manipulation instructions also clear or set the carry/borrow flag.

MC68HC705J1A — Rev. 4.0

## **Resets and Interrupts**

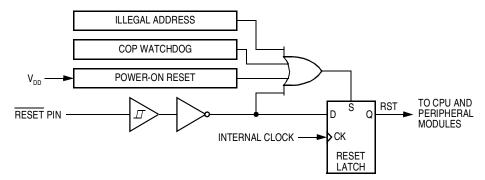

#### 4.3 Resets

A reset immediately stops the operation of the instruction being executed, initializes certain control and status bits, and loads the program counter with a user-defined reset vector address. These sources can generate a reset:

- Power-on reset (POR) circuit

- RESET pin

- Computer operating properly (COP) watchdog

- Illegal address

Figure 4-1. Reset Sources

Resets and Interrupts

Interrupts

Figure 4-6. Interrupt Stacking Order

Table 4-4. Reset/Interrupt Vector Addresses

| Function                 | Source                                                         | Local<br>Mask        | Global<br>Mask | Priority<br>(1 = Highest)    | Vector<br>Address |

|--------------------------|----------------------------------------------------------------|----------------------|----------------|------------------------------|-------------------|

| Reset                    | Power-on RESET pin COP watchdog <sup>(1)</sup> illegal address | None                 | None           | 1                            | \$07FE-\$07FF     |

| Software interrupt (SWI) | User code                                                      | None                 | None           | Same priority as instruction | \$07FC-\$07FD     |

| External interrupt       | IRQ/V <sub>PP</sub> pin                                        | IRQE                 | I bit          | 2                            | \$07FA-\$07FB     |

| Timer interrupts         | RTIF bit<br>TOF bit                                            | RTIE bit<br>TOIE bit | l bit          | 3                            | \$07F8-\$07F9     |

<sup>1.</sup> The COP watchdog is programmable in the mask option register.

MC68HC705J1A — Rev. 4.0

# Section 5. Low-Power Modes

### 5.1 Contents

| 5.2   | Introduction                   | .79 |

|-------|--------------------------------|-----|

| 5.3   | Exiting Stop and Wait Modes    | .80 |

| 5.4   | Effects of Stop and Wait Modes | .81 |

| 5.4.1 | Clock Generation               | .81 |

| 5.4.2 | CPU                            | .82 |

| 5.4.3 | COP Watchdog                   | .82 |

| 5.4.4 | Timer                          | .83 |

| 5.4.5 | EPROM/OTPROM                   | .84 |

| 5.4.6 | Data-Retention Mode            | .84 |

| 5.5   | Timing                         | .85 |

### 5.2 Introduction

The microcontroller unit (MCU) can enter these low-power standby modes:

- Stop mode The STOP instruction puts the MCU in its lowest power-consumption mode.

- Wait mode The WAIT instruction puts the MCU in an intermediate power-consumption mode.

- Halt mode Halt mode is identical to wait mode, except that an oscillator stabilization delay of 1 to 4064 internal clock cycles occurs when the MCU exits halt mode. The stop-to-wait conversion bit, SWAIT, in the mask option register, enables halt mode.

MC68HC705J1A — Rev. 4.0

### **Low-Power Modes**

#### 5.4.2 CPU

#### The STOP instruction:

- Clears the interrupt mask (I bit) in the condition code register, enabling external interrupts

- Disables the CPU clock

After exiting stop mode, the CPU clock begins running after the oscillator stabilization delay.

After exit from stop mode by external interrupt, the I bit remains clear. After exit from stop mode by reset, the I bit is set.

# The WAIT instruction:

- Clears the interrupt mask (I bit) in the condition code register, enabling interrupts

- Disables the CPU clock

After exit from wait mode by interrupt, the I bit remains clear.

After exit from wait mode by reset, the I bit is set.

### 5.4.3 COP Watchdog

#### The STOP instruction:

- Clears the COP watchdog counter

- Disables the COP watchdog clock

# **NOTE:** To prevent the STOP instruction from disabling the COP watchdog, program the stop-to-wait conversion bit (SWAIT) in the mask option register to logic 1.

After exit from stop mode by external interrupt, the COP watchdog counter immediately begins counting from \$0000 and continues counting throughout the oscillator stabilization delay.

**NOTE:** Immediately after exiting stop mode by external interrupt, service the COP to ensure a full COP timeout period.

Technical Data

MC68HC705J1A — Rev. 4.0

# Section 6. Parallel Input/Output (I/O) Ports

### 6.1 Contents

| 6.2   | Introduction87                               |

|-------|----------------------------------------------|

| 6.3   | Port A                                       |

| 6.3.1 | Port A Data Register89                       |

| 6.3.2 | Data Direction Register A90                  |

| 6.3.3 | Pulldown Register A91                        |

| 6.3.4 | Port A LED Drive Capability                  |

| 6.3.5 | Port A I/O Pin Interrupts                    |

| 6.4   | Port B                                       |

| 6.4.1 | Port B Data Register92                       |

| 6.4.2 | Data Direction Register B93                  |

| 6.4.3 | Pulldown Register B94                        |

| 6.5   | 5.0-Volt I/O Port Electrical Characteristics |

| 6.6   | 3.3-Volt I/O Port Electrical Characteristics |

### 6.2 Introduction

Fourteen bidirectional pins form one 8-bit input/output (I/O) port and one 6-bit I/O port. All the bidirectional port pins are programmable as inputs or outputs.

#### NOTE:

Connect any unused I/O pins to an appropriate logic level, either  $V_{DD}$  or  $V_{SS.}$  Although the I/O ports do not require termination for proper operation, termination reduces excess current consumption and the possibility of electrostatic damage.

MC68HC705J1A — Rev. 4.0

Parallel Input/Output (I/O) Ports

Port B

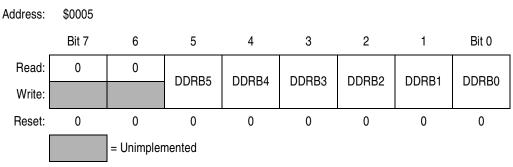

#### 6.4.2 Data Direction Register B

Data direction register B (DDRB) determines whether each port B pin is an input or an output.

Figure 6-7. Data Direction Register B (DDRB)

DDRB[5:0] — Data Direction Register B Bits

These read/write bits control port B data direction. Reset clears DDRB[5:0], configuring all port B pins as inputs.

- 1 = Corresponding port B pin configured as output

- 0 = Corresponding port B pin configured as input

**NOTE:** Avoid glitches on port B pins by writing to the port B data register before changing data direction register B bits from 0 to 1.

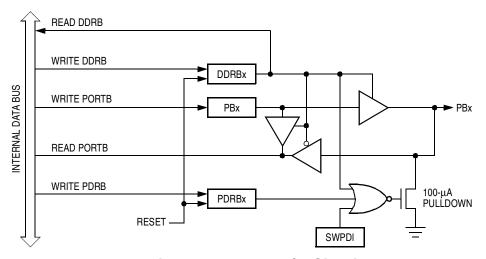

Figure 6-8 shows the I/O logic of port B.

Figure 6-8. Port B I/O Circuitry

MC68HC705J1A — Rev. 4.0

# Section 9. Multifunction Timer Module

### 9.1 Contents

| 9.2   | Introduction    |

|-------|-----------------|

| 9.3   | Operation       |

| 9.4   | Interrupts      |

| 9.5.1 | I/O Registers   |

|       | Low-Power Modes |

### 9.2 Introduction

The multifunction timer provides a timing reference with programmable real-time interrupt (RTI) capability. **Figure 9-1** shows the timer organization.

#### Features include:

- Timer overflow

- Four selectable interrupt rates

- Computer operating properly (COP) watchdog timer

Electrical Specifications

Operating Temperature Range

# 10.4 Operating Temperature Range

| Package Type                                                        | Symbol         | Value<br>(T <sub>L</sub> to T <sub>H</sub> ) | Unit |

|---------------------------------------------------------------------|----------------|----------------------------------------------|------|

| MC68HC705J1AP <sup>(1)</sup> , DW <sup>(2)</sup> , S <sup>(3)</sup> | T <sub>A</sub> | 0 to 70                                      | °C   |

| MC68HC705J1AC <sup>(4)</sup> P, CDW, CS                             | T <sub>A</sub> | -40 to +85                                   | °C   |

| MC68HC705J1AV <sup>(5)</sup> P, VDW, VS                             | T <sub>A</sub> | -40 to +105                                  | °C   |

- 1. P = plastic dual in-line package (PDIP)

- 2. DW = small outline integrated circuit (SOIC)

- 3. S = ceramic DIP (cerdip)

- 4. C = extended temperature range

- 5. V = automotive temperature range

### 10.5 Thermal Characteristics

| Characteristic                                                                                             | Symbol            | Value | Unit |

|------------------------------------------------------------------------------------------------------------|-------------------|-------|------|

| Thermal resistance MC68HC705J1AP <sup>(1)</sup> MC68HC705J1ADW <sup>(2)</sup> MC68HC705J1AS <sup>(3)</sup> | $\theta_{\sf JA}$ | 60    | °C/W |

- 1. P = plastic dual in-line package (PDIP)

- 2. DW = small outline integrated circuit (SOIC)

- 3. S = ceramic DIP (cerdip)

**Electrical Specifications** 3.3-Volt Control Timing

## 10.13 3.3-Volt Control Timing

| Characteristic <sup>(1)</sup>                                                         | Symbol                            | Min     | Max                 | Unit             |

|---------------------------------------------------------------------------------------|-----------------------------------|---------|---------------------|------------------|

| Oscillator frequency Crystal oscillator option External clock source                  | f <sub>osc</sub>                  | —<br>dc | 2.0<br>2.0          | MHz              |

| Internal operating frequency (f <sub>osc</sub> ÷ 2) Crystal oscillator External clock | f <sub>op</sub>                   | —<br>dc | 1.0<br>1.0          | MHz              |

| Cycle time (1 ÷ f <sub>OP</sub> )                                                     | t <sub>cyc</sub>                  | 1000    | _                   | ns               |

| RESET pulse width low                                                                 | t <sub>RL</sub>                   | 1.5     | _                   | t <sub>cyc</sub> |

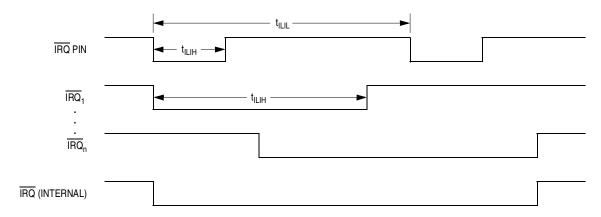

| IRQ interrupt pulse width low (edge-triggered)                                        | t <sub>ILIH</sub>                 | 1.5     | _                   | t <sub>cyc</sub> |

| IRQ interrupt pulse width low (edge- and level-triggered)                             | t <sub>ILIL</sub>                 | 1.5     | Note <sup>(2)</sup> | t <sub>cyc</sub> |

| PA0-PA3 interrupt pulse width high (edge-triggered)                                   | t <sub>IHIL</sub>                 | 1.5     | _                   | t <sub>cyc</sub> |

| PA0-PA3 interrupt pulse width (edge- and level-triggered)                             | t <sub>IHIH</sub>                 | 1.5     | Note <sup>(2)</sup> | t <sub>cyc</sub> |

| OSC1 pulse width                                                                      | t <sub>OH</sub> , t <sub>OL</sub> | 400     | _                   | ns               |

<sup>1.</sup>  $V_{DD} = 3.3 \text{ Vdc} \pm 10\%$ ,  $V_{SS} = 0 \text{ Vdc}$ ,  $T_{A} = -40^{\circ}\text{C}$  to +105°C, unless otherwise noted 2. The maximum width,  $t_{ILIL}$  or  $t_{ILIH}$ , should not be more than the number of cycles it takes to execute the interrupt service routine plus 19  $t_{cyc}$  or the interrupt service routine will be re-entered.

# **Electrical Specifications**

Figure 10-6. External Interrupt Timing

- Internal clocking from OSC1 pin

Edge-triggered external interrupt mask option

Edge- and level-triggered external interrupt mask option

- 4. Reset vector shown as example

Figure 10-7. Stop Mode Recovery Timing

**Technical Data**

MC68HC705J1A — Rev. 4.0

Technical Data MC68HC705J1A — Rev. 4.0

# **Section 11. Mechanical Specifications**

### 11.1 Contents

| 11.2 | Introduction                                |

|------|---------------------------------------------|

| 11.3 | Plastic Dual In-Line Package (Case 738)132  |

| 11.4 | Small Outline Integrated Circuit (Case 751) |

| 11.5 | Ceramic Dual In-Line Package (Case 732)     |

### 11.2 Introduction

The MC68HC705J1A, the resistor-capacitor (RC) oscillator, and high-speed option devices described in **Appendix A**.

MC68HRC705J1A, **Appendix B**. MC68HSC705J1A, and **Appendix C**.

MC68HSR705J1A are available in the following packages:

- 738-03 plastic dual in-line package (PDIP)

- 751D-04 small outline integrated circuit (SOIC)

- 732-03 ceramic DIP (cerdip) (windowed)

MC68HRC705J1A

Typical Internal Operating Frequency for RC Oscillator Option

### A.4 Typical Internal Operating Frequency for RC Oscillator Option

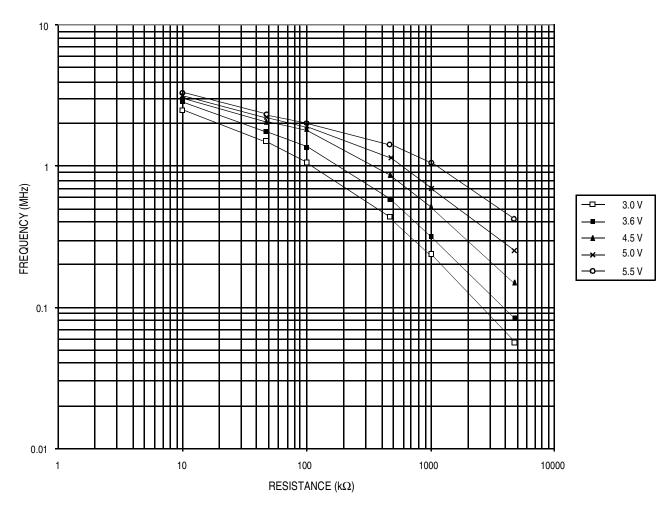

**Figure A-2** shows typical internal operating frequencies at 25°C for the RC oscillator option.

**NOTE:**

Tolerance for resistance is  $\pm 50\%$ . When selecting resistor size, consider the tolerance to ensure that the resulting oscillator frequency does not exceed the maximum operating frequency.

Figure A-2. Typical Internal Operating Frequency for Various V<sub>DD</sub> at 25°C — RC Oscillator Option Only

MC68HC705J1A — Rev. 4.0

## MC68HSR705J1A

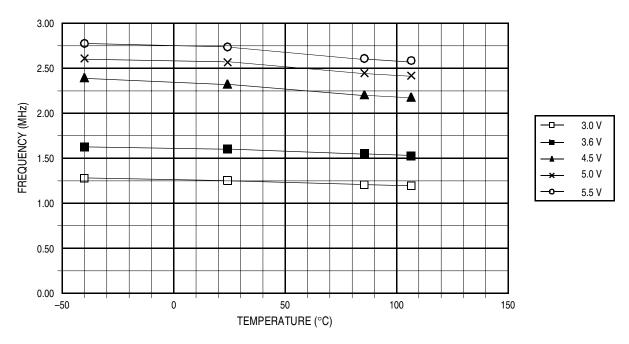

# C.6 Typical Internal Operating Frequency versus Temperature (No External Resistor)

Figure C-3. Typical Internal Operating Frequency versus Temperature (OSCRES Bit = 1)

NOTE:

Due to process variations, operating voltages, and temperature requirements, the internal resistance and tolerance are unspecified. Typically for a given voltage and temperature, the frequency should not vary more than ±500 kHz. However, this data is not guaranteed. It is the user's responsibility to ensure that the resulting internal operating frequency meets the user's requirements.

Index

| I/O circuitry                      | 3 |

|------------------------------------|---|

| pin operation                      | 4 |

| pins                               | 1 |

| port B data register (PORTB)9      |   |

| pulldown register (PDRB)           | 4 |

| power dissipation                  | 0 |

| power-on reset                     | 1 |

| program counter (PC)               | 0 |

| programmable options2              | 5 |

| programming model (CPU)            | 7 |

| pulldown register A (PDRA)9        |   |

| pulldown register B (PDRB)         |   |

| pulldown resistors                 |   |

| programmable option                | 5 |

|                                    |   |

| R                                  |   |

| RAM3                               | 7 |

| stack RAM                          | 6 |

| registers                          |   |

| CPU                                |   |

| I/O register summary               |   |

| parallel I/O port register summary |   |

| RESET pin                          | 2 |

| resets                             | 0 |

| COP register (COPR)                |   |

| COP watchdog reset                 |   |

| external reset                     |   |

| external reset timing              |   |

| illegal address                    |   |

| power-on reset (POR)               |   |

| power-on reset timing              |   |

| reset sources                      |   |

| reset/interrupt vector addresses   | 1 |

| resistors (pulldown)               | F |

| programmable option                |   |

| RT1, RT0 bits                      | J |

MC68HC705J1A — Rev. 4.0