Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | ARM® Cortex®-M3                                                                   |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 180MHz                                                                            |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, IrDA, Microwire, SD, SPI, SSI, SSP, UART/USART |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, WDT                           |

| Number of I/O              | 49                                                                                |

| Program Memory Size        | 512KB (512K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | 16K x 8                                                                           |

| RAM Size                   | 104К х 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.2V ~ 3.6V                                                                       |

| Data Converters            | A/D 4x10b; D/A 1x10b                                                              |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 100-TFBGA                                                                         |

| Supplier Device Package    | 100-TFBGA (9x9)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/lpc1812jet100e            |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin name | LBGA256 | TFBGA100 | LQFP144 | LQFP208 |     | Reset state | Type | Description                                                 |

|----------|---------|----------|---------|---------|-----|-------------|------|-------------------------------------------------------------|

| P1_12    | R9      | K7       | 56      | 78      | [2] | N;          | I/O  | <b>GPIO1[5]</b> — General purpose digital input/output pin. |

|          |         |          |         |         |     | PU          | Ι    | <b>U1_DCD</b> — Data Carrier Detect input for UART1.        |

|          |         |          |         |         |     |             | -    | R — Function reserved.                                      |

|          |         |          |         |         |     |             | I/O  | <b>EMC_D5</b> — External memory data line 5.                |

|          |         |          |         |         |     |             | I    | <b>T0_CAP1</b> — Capture input 1 of timer 0.                |

|          |         |          |         |         |     |             | -    | R — Function reserved.                                      |

|          |         |          |         |         |     |             | -    | R — Function reserved.                                      |

|          |         |          |         |         |     |             | I/O  | <b>SD_DAT3</b> — SD/MMC data bus line 3.                    |

| P1_13    | R10     | H8       | 60      | 83      | [2] | N;          | I/O  | <b>GPIO1[6]</b> — General purpose digital input/output pin. |

|          |         |          |         |         |     | PU          | 0    | <b>U1_TXD</b> — Transmitter output for UART1.               |

|          |         |          |         |         |     |             | -    | R — Function reserved.                                      |

|          |         |          |         |         |     |             | I/O  | <b>EMC_D6</b> — External memory data line 6.                |

|          |         |          |         |         |     |             | Ι    | <b>T0_CAP0</b> — Capture input 0 of timer 0.                |

|          |         |          |         |         |     |             | -    | R — Function reserved.                                      |

|          |         |          |         |         |     |             | -    | R — Function reserved.                                      |

|          |         |          |         |         |     |             | I    | <b>SD_CD</b> — SD/MMC card detect input.                    |

| P1_14    | R11     | J8       | 61      | 85      | [2] | N;          | I/O  | <b>GPIO1[7]</b> — General purpose digital input/output pin. |

|          |         |          |         |         |     | PU          | I    | <b>U1_RXD</b> — Receiver input for UART1.                   |

|          |         |          |         |         |     |             | -    | R — Function reserved.                                      |

|          |         |          |         |         |     |             | I/O  | <b>EMC_D7</b> — External memory data line 7.                |

|          |         |          |         |         |     |             | 0    | <b>T0_MAT2</b> — Match output 2 of timer 0.                 |

|          |         |          |         |         |     |             | -    | R — Function reserved.                                      |

|          |         |          |         |         |     |             | -    | R — Function reserved.                                      |

|          |         |          |         |         |     |             | -    | R — Function reserved.                                      |

| P1_15    | T12     | K8       | 62      | 87      | [2] | N;          | I/O  | <b>GPIO0[2]</b> — General purpose digital input/output pin. |

|          |         |          |         |         |     | PU          | 0    | <b>U2_TXD</b> — Transmitter output for USART2.              |

|          |         |          |         |         |     |             | -    | R — Function reserved.                                      |

|          |         |          |         |         |     |             | I    | ENET_RXD0 — Ethernet receive data 0 (RMII/MII interface).   |

|          |         |          |         |         |     |             | 0    | T0_MAT1 — Match output 1 of timer 0.                        |

|          |         |          |         |         |     |             | -    | R — Function reserved.                                      |

|          |         |          |         |         |     |             | I/O  | EMC_D8 — External memory data line 8.                       |

|          |         |          |         |         |     |             | -    | R — Function reserved.                                      |

Table 3.

Pin description ...continued

| Pin name | LBGA256 | TFBGA100 | LQFP144 | LQFP208 |     | Reset state | Type                | Description                                                                                                                                            |

|----------|---------|----------|---------|---------|-----|-------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| P4_3     | C2      | -        | 7       | 10      | [5] | N;          | I/O                 | GPIO2[3] — General purpose digital input/output pin.                                                                                                   |

|          |         |          |         |         |     | PU          | 0                   | <b>CTOUT_3</b> — SCTimer/PWM output 3. Match output 3 of timer 0.                                                                                      |

|          |         |          |         |         |     |             | 0                   | LCD_VD2 — LCD data.                                                                                                                                    |

|          |         |          |         |         |     |             | -                   | R — Function reserved.                                                                                                                                 |

|          |         |          |         |         |     |             | -                   | R — Function reserved.                                                                                                                                 |

|          |         |          |         |         |     |             | 0                   | LCD_VD21 — LCD data.                                                                                                                                   |

|          |         |          |         |         |     |             | I/O                 | U3_BAUD — Baud pin for USART3.                                                                                                                         |

|          |         |          |         |         |     |             | -                   | R — Function reserved.                                                                                                                                 |

|          |         |          |         |         |     |             | AI                  | <b>ADC0_0</b> — ADC0 and ADC1, input channel 0. Configure the pin as GPIO input and use the ADC function select register in the SCU to select the ADC. |

| P4_4     | B1      | -        | 9       | 14      | [5] | N;          | I/O                 | GPIO2[4] — General purpose digital input/output pin.                                                                                                   |

|          |         |          |         |         |     | PU          | 0                   | <b>CTOUT_2</b> — SCTimer/PWM output 2. Match output 2 of timer 0.                                                                                      |

|          |         |          |         |         |     | 0           | LCD_VD1 — LCD data. |                                                                                                                                                        |

|          |         |          |         |         |     |             | -                   | R — Function reserved.                                                                                                                                 |

|          |         |          |         |         |     |             | -                   | R — Function reserved.                                                                                                                                 |

|          |         |          |         |         |     |             | 0                   | LCD_VD20 — LCD data.                                                                                                                                   |

|          |         |          |         |         |     |             | I/O                 | <b>U3_DIR</b> — RS-485/EIA-485 output enable/direction control for USART3.                                                                             |

|          |         |          |         |         |     |             | -                   | R — Function reserved.                                                                                                                                 |

|          |         |          |         |         |     |             | AO                  | <b>DAC</b> — DAC output. Configure the pin as GPIO input and use the analog function select register in the SCU to select the DAC.                     |

| P4_5     | D2      | -        | 10      | 15      | [2] | N;          | I/O                 | <b>GPIO2[5]</b> — General purpose digital input/output pin.                                                                                            |

|          |         |          |         |         |     | PU          | 0                   | <b>CTOUT_5</b> — SCTimer/PWM output 5. Match output 3 of timer 3.                                                                                      |

|          |         |          |         |         |     |             | 0                   | <b>LCD_FP</b> — Frame pulse (STN). Vertical synchronization pulse (TFT).                                                                               |

|          |         |          |         |         |     |             | -                   | R — Function reserved.                                                                                                                                 |

|          |         |          |         |         |     |             | -                   | R — Function reserved.                                                                                                                                 |

|          |         |          |         |         |     |             | -                   | R — Function reserved.                                                                                                                                 |

|          |         |          |         |         |     |             | -                   | R — Function reserved.                                                                                                                                 |

|          |         |          |         |         |     |             | -                   | R — Function reserved.                                                                                                                                 |

Table 3.

Pin description ...continued

|          | n descri |          | .comm   | Jeu     |     |                    |      |                                                                                                                                                        |

|----------|----------|----------|---------|---------|-----|--------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin name | LBGA256  | TFBGA100 | LQFP144 | LQFP208 |     | Reset state<br>[1] | Type | Description                                                                                                                                            |

| PC_3     | F5       | -        | -       | 11      | [5] | N;                 | I/O  | USB1_ULPI_D5 — ULPI link bidirectional data line 5.                                                                                                    |

|          |          |          |         |         |     | PU                 | -    | R — Function reserved.                                                                                                                                 |

|          |          |          |         |         |     |                    | 0    | <b>U1_RTS</b> — Request to Send output for UART1. Can also be configured to be an RS-485/EIA-485 output enable signal for UART1.                       |

|          |          |          |         |         |     |                    | 0    | ENET_TXD3 — Ethernet transmit data 3 (MII interface).                                                                                                  |

|          |          |          |         |         |     |                    | I/O  | GPIO6[2] — General purpose digital input/output pin.                                                                                                   |

|          |          |          |         |         |     |                    | -    | R — Function reserved.                                                                                                                                 |

|          |          |          |         |         |     |                    | -    | R — Function reserved.                                                                                                                                 |

|          |          |          |         |         |     |                    | 0    | SD_VOLT1 — SD/MMC bus voltage select output 1.                                                                                                         |

|          |          |          |         |         |     |                    | AI   | <b>ADC1_0</b> — ADC1 and ADC0, input channel 0. Configure the pin as GPIO input and use the ADC function select register in the SCU to select the ADC. |

| PC_4     | F4       | -        | -       | 16      | [2] | N;                 | -    | R — Function reserved.                                                                                                                                 |

|          |          |          |         |         |     | PU                 | I/O  | <b>USB1_ULPI_D4</b> — ULPI link bidirectional data line 4.                                                                                             |

|          |          |          |         |         |     |                    | -    | R — Function reserved.                                                                                                                                 |

|          |          |          |         |         |     |                    |      | <b>ENET_TX_EN</b> — Ethernet transmit enable (RMII/MII interface).                                                                                     |

|          |          |          |         |         |     |                    | I/O  | <b>GPIO6[3]</b> — General purpose digital input/output pin.                                                                                            |

|          |          |          |         |         |     |                    | -    | R — Function reserved.                                                                                                                                 |

|          |          |          |         |         |     |                    | I    | T3_CAP1 — Capture input 1 of timer 3.                                                                                                                  |

|          |          |          |         |         |     |                    | I/O  | <b>SD_DAT0</b> — SD/MMC data bus line 0.                                                                                                               |

| PC_5     | G4       | -        | -       | 20      | [2] | N;                 | -    | R — Function reserved.                                                                                                                                 |

|          |          |          |         |         |     | PU                 | I/O  | <b>USB1_ULPI_D3</b> — ULPI link bidirectional data line 3.                                                                                             |

|          |          |          |         |         |     |                    | -    | R — Function reserved.                                                                                                                                 |

|          |          |          |         |         |     |                    | 0    | <b>ENET_TX_ER</b> — Ethernet Transmit Error (MII interface).                                                                                           |

|          |          |          |         |         |     |                    | I/O  | <b>GPIO6[4]</b> — General purpose digital input/output pin.                                                                                            |

|          |          |          |         |         |     |                    | -    | R — Function reserved.                                                                                                                                 |

|          |          |          |         |         |     |                    | I    | T3_CAP2 — Capture input 2 of timer 3.                                                                                                                  |

|          |          |          |         |         |     |                    | I/O  | <b>SD_DAT1</b> — SD/MMC data bus line 1.                                                                                                               |

| PC_6     | H6       | -        | -       | 22      | [2] | N;<br>PU           | -    | R — Function reserved.                                                                                                                                 |

|          |          |          |         |         |     | FU                 | I/O  | <b>USB1_ULPI_D2</b> — ULPI link bidirectional data line 2.                                                                                             |

|          |          |          |         |         |     |                    | -    | R — Function reserved.                                                                                                                                 |

|          |          |          |         |         |     |                    |      | ENET_RXD2 — Ethernet receive data 2 (MII interface).                                                                                                   |

|          |          |          |         |         |     |                    | I/O  | <b>GPIO6[5]</b> — General purpose digital input/output pin.                                                                                            |

|          |          |          |         |         |     |                    | -    | R — Function reserved.                                                                                                                                 |

|          |          |          |         |         |     |                    |      | T3_CAP3 — Capture input 3 of timer 3.                                                                                                                  |

|          |          |          |         |         |     |                    | I/O  | <b>SD_DAT2</b> — SD/MMC data bus line 2.                                                                                                               |

Table 3.

Pin description ...continued

32-bit ARM Cortex-M3 microcontroller

| Pin name |         |   | 0        | _        |         |          | ate         |      | Description                                                                                          |

|----------|---------|---|----------|----------|---------|----------|-------------|------|------------------------------------------------------------------------------------------------------|

|          | LBGA256 |   | TFBGA100 | LQFP144  | LQFP208 |          | Reset state |      |                                                                                                      |

|          | BG/     |   | FBG      | QFP      | QFP     |          | ese         | Type |                                                                                                      |

| PC_11    |         |   | -        | -        | -       | [2]      | ₩ Ξ<br>N;   | Ϋ́   | R — Function reserved.                                                                               |

| 10_11    | L       | 5 | -        | <b>_</b> | -       | <u> </u> | PU          | -    | USB1_ULPI_DIR — ULPI link DIR signal. Controls the ULP                                               |

|          |         |   |          |          |         |          |             |      | data line direction.                                                                                 |

|          |         |   |          |          |         |          |             | I    | <b>U1_DCD</b> — Data Carrier Detect input for UART1.                                                 |

|          |         |   |          |          |         |          |             | -    | R — Function reserved.                                                                               |

|          |         |   |          |          |         |          |             | I/O  | <b>GPIO6[10]</b> — General purpose digital input/output pin.                                         |

|          |         |   |          |          |         |          |             | -    | R — Function reserved.                                                                               |

|          |         |   |          |          |         |          |             | -    | R — Function reserved.                                                                               |

|          |         |   |          |          |         |          |             | I/O  | <b>SD_DAT4</b> — SD/MMC data bus line 4.                                                             |

| PC_12    | Le      | 6 | -        | -        | -       | [2]      | N;          | -    | R — Function reserved.                                                                               |

|          |         |   |          |          |         |          | PU          | -    | R — Function reserved.                                                                               |

|          |         |   |          |          |         |          |             | 0    | <b>U1_DTR</b> — Data Terminal Ready output for UART1. Can also                                       |

|          |         |   |          |          |         |          |             |      | be configured to be an RS-485/EIA-485 output enable signal for UART1.                                |

|          |         |   |          |          |         |          |             | -    | R — Function reserved.                                                                               |

|          |         |   |          |          |         |          |             | I/O  | GPIO6[11] — General purpose digital input/output pin.                                                |

|          |         |   |          |          |         |          |             | -    | R — Function reserved.                                                                               |

|          |         |   |          |          |         |          |             | I/O  | I2S0_TX_SDA — I <sup>2</sup> S transmit data. It is driven by the                                    |

|          |         |   |          |          |         |          |             |      | transmitter and read by the receiver. Corresponds to the signal SD in the $l^2S$ -bus specification. |

|          |         |   |          |          |         |          |             | I/O  | SD_DAT5 — SD/MMC data bus line 5.                                                                    |

| PC_13    | М       | 1 | -        | -        | -       | [2]      | N;          | -    | <b>R</b> — Function reserved.                                                                        |

| 10_10    |         |   |          |          |         |          | PU          | -    | R — Function reserved.                                                                               |

|          |         |   |          |          |         |          |             | 0    | <b>U1_TXD</b> — Transmitter output for UART1.                                                        |

|          |         |   |          |          |         |          |             | -    | <b>R</b> — Function reserved.                                                                        |

|          |         |   |          |          |         |          |             | I/O  | GPIO6[12] — General purpose digital input/output pin.                                                |

|          |         |   |          |          |         |          |             | -    | R — Function reserved.                                                                               |

|          |         |   |          |          |         |          |             | I/O  | I2S0_TX_WS — Transmit Word Select. It is driven by the                                               |

|          |         |   |          |          |         |          |             |      | master and received by the slave. Corresponds to the signal                                          |

|          |         |   |          |          |         |          |             | I/O  | WS in the $PS$ -bus specification.<br><b>SD_DAT6</b> — SD/MMC data bus line 6.                       |

| PC_14    | N       | 1 | _        | -        | -       | [2]      | N;          | -    | <b>R</b> — Function reserved.                                                                        |

| 10_14    | IN      | 1 |          | -        |         | <u> </u> | PU          | -    | R — Function reserved.                                                                               |

|          |         |   |          |          |         |          |             | 1    | <b>U1_RXD</b> — Receiver input for UART1.                                                            |

|          |         |   |          |          |         |          |             | -    | <b>R</b> — Function reserved.                                                                        |

|          |         |   |          |          |         |          |             | I/O  | <b>GPI06[13]</b> — General purpose digital input/output pin.                                         |

|          |         |   |          |          |         |          |             | -    | $\mathbf{R}$ — Function reserved.                                                                    |

|          |         |   |          |          |         |          |             | 0    | ENET_TX_ER — Ethernet Transmit Error (MII interface).                                                |

|          |         |   |          |          |         |          |             | I/O  | <b>SD_DAT7</b> — SD/MMC data bus line 7.                                                             |

Table 3.

Pin description ...continued

LPC185X\_3X\_2X\_1X

| Pin name                  | 56      | 100      | 4       | 8       |             | tate        |      | Description                                                                                                                                                                                                              |

|---------------------------|---------|----------|---------|---------|-------------|-------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                           | LBGA256 | TFBGA100 | LQFP144 | LQFP208 |             | Reset state | Type |                                                                                                                                                                                                                          |

| Debug pins                |         |          |         |         |             |             |      |                                                                                                                                                                                                                          |

| DBGEN                     | L4      | A6       | 28      | 41      | [2]         | I           | I    | JTAG interface control signal. Also used for boundary scan. To<br>use the part in functional mode, connect this pin in one of the<br>following ways:                                                                     |

|                           |         |          |         |         |             |             |      | <ul> <li>Leave DBGEN open. The DBGEN pin is pulled up internally by a 50 kΩ resistor.</li> <li>Tie DBGEN to VDDIO.</li> </ul>                                                                                            |

|                           |         |          |         |         |             |             |      | <ul> <li>Pull DBGEN up to VDDIO with an external pull-up resistor.</li> </ul>                                                                                                                                            |

| TCK/SWDCLK                | J5      | H2       | 27      | 38      | [2]         | l; F        | I    | Test Clock for JTAG interface (default) or Serial Wire (SW) clock.                                                                                                                                                       |

| TRST                      | M4      | B4       | 29      | 42      | [2]         | I; PU       | I    | Test Reset for JTAG interface.                                                                                                                                                                                           |

| TMS/SWDIO                 | K6      | C4       | 30      | 44      | [2]         | I; PU       | I    | Test Mode Select for JTAG interface (default) or SW debug data input/output.                                                                                                                                             |

| TDO/SWO                   | K5      | H3       | 31      | 46      | [2]         | 0           | 0    | Test Data Out for JTAG interface (default) or SW trace output.                                                                                                                                                           |

| TDI                       | J4      | G3       | 26      | 35      | [2]         | I; PU       | I    | Test Data In for JTAG interface.                                                                                                                                                                                         |

| USB0 pins                 |         |          |         |         |             |             |      |                                                                                                                                                                                                                          |

| USB0_DP                   | F2      | E1       | 18      | 26      | [6]         | -           | I/O  | USB0 bidirectional D+ line. Do not add an external series resistor.                                                                                                                                                      |

| USB0_DM                   | G2      | E2       | 20      | 28      | [6]         | -           | I/O  | USB0 bidirectional D– line. Do not add an external series resistor.                                                                                                                                                      |

| USB0_VBUS                 | F1      | E3       | 21      | 29      | [6]<br>[7]  | -           | I    | VBUS pin (power on USB cable). This pin includes an internal pull-down resistor of 70 k $\Omega$ (typical) $\pm$ 30 k $\Omega$ .                                                                                         |

| USB0_ID                   | H2      | F1       | 22      | 30      | <u>[8]</u>  | -           | I    | Indicates to the transceiver whether connected as an A-device (USB0_ID LOW) or B-device (USB0_ID HIGH). For use with OTG, this pin has an internal pull-up resistor.                                                     |

| USB0_RREF                 | H1      | F3       | 24      | 32      | <u>[8]</u>  | -           |      | 12.0 k $\Omega$ (accuracy 1 %) on-board resistor to ground for current reference.                                                                                                                                        |

| USB1 pins                 |         |          |         |         |             |             |      |                                                                                                                                                                                                                          |

| USB1_DP                   | F12     | E9       | 89      | 129     | [9]         | -           | I/O  | USB1 bidirectional D+ line. Add an external series resistor of 33 $\Omega$ +/- 2 %.                                                                                                                                      |

| USB1_DM                   | G12     | E10      | 90      | 130     | [9]         | -           | I/O  | USB1 bidirectional D– line. Add an external series resistor of 33 $\Omega$ +/- 2 %.                                                                                                                                      |

| I <sup>2</sup> C-bus pins |         |          |         |         |             |             |      |                                                                                                                                                                                                                          |

| I2C0_SCL                  | L15     | D6       | 92      | 132     | <u>[10]</u> | l; F        | I/O  | I <sup>2</sup> C clock input/output. Open-drain output (for I <sup>2</sup> C-bus compliance).                                                                                                                            |

| I2C0_SDA                  | L16     | E6       | 93      | 133     | <u>[10]</u> | l; F        | I/O  | I <sup>2</sup> C data input/output. Open-drain output (for I <sup>2</sup> C-bus compliance).                                                                                                                             |

| Reset and wake            | e-up pi | ns       |         |         |             |             |      |                                                                                                                                                                                                                          |

| RESET                     | D9      | B6       | 128     | 185     | [11]        | I; IA       | 1    | External reset input: A LOW on this pin resets the device, causing I/O ports and peripherals to take on their default states, and processor execution to begin at address 0. This pin does not have an internal pull-up. |

Table 3.

Pin description ...continued

### 32-bit ARM Cortex-M3 microcontroller

| Pin name              |         | 0        |         |         |             | te          |      | Description                                                                                                                                                                                                             |

|-----------------------|---------|----------|---------|---------|-------------|-------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                       | LBGA256 | TFBGA100 | LQFP144 | LQFP208 |             | Reset state | Type |                                                                                                                                                                                                                         |

| WAKEUP0               | A9      | A4       | 130     | 187     | [11]        | I; IA       | I    | External wake-up input; can raise an interrupt and can cause<br>wake-up from any of the low-power modes. A pulse with a<br>duration of at least 45 ns wakes up the part.                                                |

|                       |         |          |         |         |             |             |      | Input 0 of the event monitor. No internal pull-up is enabled when this pin is configured as input.                                                                                                                      |

| WAKEUP1               | A10     | -        | -       | -       | <u>[11]</u> | I; IA       | I    | External wake-up input; can raise an interrupt and can cause wake-up from any of the low-power modes. A pulse with a duration of at least 45 ns wakes up the part.                                                      |

|                       |         |          |         |         |             |             |      | Input 1 of the event monitor. No internal pull-up is enabled when this pin is configured as input.                                                                                                                      |

| WAKEUP2               | C9      | -        | -       | -       | [11]        | I; IA       | I    | External wake-up input; can raise an interrupt and can cause<br>wake-up from any of the low-power modes. A pulse with a<br>duration of at least 45 ns wakes up the part.                                                |

|                       |         |          |         |         |             |             |      | Input 2 of the event monitor. This pin does not have an internal pull-up.                                                                                                                                               |

| WAKEUP3               | D8      | -        | -       | -       | [11]        | I; IA       | I    | External wake-up input; can raise an interrupt and can cause<br>wake-up from any of the low-power modes. A pulse with a<br>duration of at least 45 ns wakes up the part. This pin does not<br>have an internal pull-up. |

| ADC pins              |         |          |         |         |             |             |      |                                                                                                                                                                                                                         |

| ADC0_0/<br>ADC1_0/DAC | E3      | A2       | 6       | 8       | [8]         | AI;<br>IA   | I    | ADC input channel 0. Shared between 10-bit ADC0/1 and DAC.                                                                                                                                                              |

| ADC0_1/<br>ADC1_1     | C3      | A1       | 2       | 4       | <u>[8]</u>  | AI;<br>IA   | I    | ADC input channel 1. Shared between 10-bit ADC0/1.                                                                                                                                                                      |

| ADC0_2/<br>ADC1_2     | A4      | B3       | 143     | 206     | [8]         | AI;<br>IA   | I    | ADC input channel 2. Shared between 10-bit ADC0/1.                                                                                                                                                                      |

| ADC0_3/<br>ADC1_3     | B5      | A3       | 139     | 200     | [8]         | AI;<br>IA   | I    | ADC input channel 3. Shared between 10-bit ADC0/1.                                                                                                                                                                      |

| ADC0_4/<br>ADC1_4     | C6      | -        | 138     | 199     | [8]         | AI;<br>IA   | I    | ADC input channel 4. Shared between 10-bit ADC0/1.                                                                                                                                                                      |

| ADC0_5/<br>ADC1_5     | B3      | -        | 144     | 208     | <u>[8]</u>  | AI;<br>IA   | I    | ADC input channel 5. Shared between 10-bit ADC0/1.                                                                                                                                                                      |

| ADC0_6/<br>ADC1_6     | A5      | -        | 142     | 204     | <u>[8]</u>  | AI;<br>IA   | I    | ADC input channel 6. Shared between 10-bit ADC0/1.                                                                                                                                                                      |

| ADC0_7/<br>ADC1_7     | C5      | -        | 136     | 197     | [8]         | AI;<br>IA   | I    | ADC input channel 7. Shared between 10-bit ADC0/1.                                                                                                                                                                      |

| RTC pins              |         |          |         |         |             |             |      |                                                                                                                                                                                                                         |

| RTC_ALARM             | A11     | C3       | 129     | 186     | [11]        | -           | 0    | RTC controlled output.                                                                                                                                                                                                  |

| RTCX1                 | A8      | A5       | 125     | 182     | [8]         | -           | I    | Input to the RTC 32 kHz ultra-low power oscillator circuit.                                                                                                                                                             |

| RTCX2                 | B8      | B5       | 126     | 183     | [8]         | -           | 0    | Output from the RTC 32 kHz ultra-low power oscillator circuit.                                                                                                                                                          |

| SAMPLE                | B9      | -        | -       | -       | [11]        | 0           | 0    | Event monitor sample output.                                                                                                                                                                                            |

| Crystal oscillat      | or pins | 5        |         |         |             |             |      | ·                                                                                                                                                                                                                       |

| XTAL1                 | D1      | B1       | 12      | 18      | <u>[8]</u>  | -           | I    | Input to the oscillator circuit and internal clock generator circuits.                                                                                                                                                  |

Table 3.

Pin description ...continued

LPC185X\_3X\_2X\_1X

Product data sheet

#### 32-bit ARM Cortex-M3 microcontroller

#### 7.15.7 High-speed USB Host/Device interface with ULPI (USB1)

**Remark:** USB1 is available on the following parts: LPC185x and LPC183x. USB1 is not available on the LPC182x and LPC181x parts.

The USB1 interface can operate as a full-speed USB host/device interface or can connect to an external ULPI PHY for High-speed operation.

#### 7.15.7.1 Features

- Complies with Universal Serial Bus specification 2.0.

- Complies with Enhanced Host Controller Interface Specification.

- Supports auto USB 2.0 mode discovery.

- Supports all high-speed USB-compliant peripherals if connected to external ULPI PHY.

- Supports all full-speed USB-compliant peripherals.

- Supports interrupts.

- Supports Start Of Frame (SOF) frame length adjust.

- This module has its own, integrated DMA engine.

- USB interface electrical test software included in ROM USB stack.

#### 7.15.8 LCD controller

**Remark:** The LCD controller is only available on parts LPC185x. LCD is not available on parts LPC183x, LPC182x, and LPC181x.

The LCD controller provides all of the necessary control signals to interface directly to various color and monochrome LCD panels. Both STN (single and dual panel) and TFT panels can be operated. The display resolution is selectable and can be up to  $1024 \times 768$  pixels. Several color modes are provided, up to a 24-bit true-color non-palettized mode. An on-chip 512 byte color palette allows reducing bus utilization (that is, memory size of the displayed data) while still supporting many colors.

The LCD interface includes its own DMA controller to allow it to operate independently of the CPU and other system functions. A built-in FIFO acts as a buffer for display data, providing flexibility for system timing. Hardware cursor support can further reduce the amount of CPU time required to operate the display.

#### 7.15.8.1 Features

- AHB master interface to access frame buffer.

- Setup and control via a separate AHB slave interface.

- Dual 16-deep programmable 64-bit wide FIFOs for buffering incoming display data.

- Supports single and dual-panel monochrome Super Twisted Nematic (STN) displays with 4-bit or 8-bit interfaces.

- Supports single and dual-panel color STN displays.

- Supports Thin Film Transistor (TFT) color displays.

- Programmable display resolution including, but not limited to:  $320 \times 200$ ,  $320 \times 240$ ,  $640 \times 200$ ,  $640 \times 240$ ,  $640 \times 480$ ,  $800 \times 600$ , and  $1024 \times 768$ .

- Hardware cursor support for single-panel displays.

#### 32-bit ARM Cortex-M3 microcontroller

- Increments/decrements depending on direction.

- Programmable for 2× or 4× position counting.

- Velocity capture using built-in timer.

- Velocity compare function with "less than" interrupt.

- Uses 32-bit registers for position and velocity.

- Three position-compare registers with interrupts.

- Index counter for revolution counting.

- Index compare register with interrupts.

- Can combine index and position interrupts to produce an interrupt for whole and partial revolution displacement.

- Digital filter with programmable delays for encoder input signals.

- Can accept decoded signal inputs (clk and direction).

### 7.17.4 Repetitive Interrupt (RI) timer

The repetitive interrupt timer provides a free-running 32-bit counter which is compared to a selectable value, generating an interrupt when a match occurs. Any bits of the timer compare function can be masked such that they do not contribute to the match detection. The repetitive interrupt timer can be used to create an interrupt that repeats at predetermined intervals.

#### 7.17.4.1 Features

- 32-bit counter. Counter can be free-running or be reset by a generated interrupt.

- 32-bit compare value.

- 32-bit compare mask. An interrupt is generated when the counter value equals the compare value, after masking. This mechanism allows for combinations not possible with a simple compare.

#### 7.17.5 Windowed WatchDog Timer (WWDT)

The purpose of the watchdog is to reset the controller if software fails to periodically service it within a programmable time window.

#### 7.17.5.1 Features

- Internally resets chip if not periodically reloaded during the programmable time-out period.

- Optional windowed operation requires reload to occur between a minimum and maximum time period, both programmable.

- Optional warning interrupt can be generated at a programmable time prior to watchdog time-out.

- Enabled by software but requires a hardware reset or a watchdog reset/interrupt to be disabled.

- Incorrect feed sequence causes reset or interrupt if enabled.

- Flag to indicate watchdog reset.

- Programmable 24-bit timer with internal prescaler.

LPC185X 3X 2X 1X

#### 32-bit ARM Cortex-M3 microcontroller

- Selectable time period from  $(T_{cy(WDCLK)} \times 256 \times 4)$  to  $(T_{cy(WDCLK)} \times 2^{24} \times 4)$  in multiples of  $T_{cy(WDCLK)} \times 4$ .

- The Watchdog Clock (WDCLK) uses the IRC as the clock source.

### 7.18 Analog peripherals

### 7.18.1 Analog-to-Digital Converter

**Remark:** The LPC185x/3x/2x/1x contain two 10-bit ADCs. All input channels are shared between ADC0 and ADC1.

### 7.18.1.1 Features

- 10-bit successive approximation analog to digital converter.

- Input multiplexing among 8 pins.

- Power-down mode.

- Measurement range 0 to VDDA.

- Sampling frequency up to 400 kSamples/s.

- Burst conversion mode for single or multiple inputs.

- Optional conversion on transition on ADCTRIG0 or ADCTRIG1 pins, combined timer outputs 8 or 15, or the PWM output MCOA2.

- Individual result registers for each A/D channel to reduce interrupt overhead.

- DMA support.

### 7.18.2 Digital-to-Analog Converter (DAC)

#### 7.18.2.1 Features

- 10-bit resolution.

- Monotonic by design (resistor string architecture).

- Controllable conversion speed.

- Low power consumption.

### 7.19 Peripherals in the RTC power domain

7.19.1 RTC

The Real-Time Clock (RTC) is a set of counters for measuring time when system power is on, and optionally when it is off. It uses little power when the CPU does not access its registers, especially in the reduced power modes. A separate 32 kHz oscillator clocks the RTC. The oscillator produces a 1 Hz internal time reference and is powered by its own power supply pin, VBAT.

#### 7.19.1.1 Features

- Measures the passage of time to maintain a calendar and clock. Provides seconds, minutes, hours, day of month, month, year, day of week, and day of year.

- Ultra-low power design to support battery powered systems. Uses power from the CPU power supply when it is present.

#### 32-bit ARM Cortex-M3 microcontroller

- Timer/USART inputs

- Enabling the USB controllers

In addition, the CREG block contains the part identification and part configuration information.

#### 7.20.2 System Control Unit (SCU)

The system control unit determines the function and electrical mode of the digital pins. By default function 0 is selected for all pins with pull-up enabled. For pins that support a digital and analog function, the ADC function select registers in the SCU enable the analog function.

A separate set of analog I/Os for the ADCs and the DAC as well as most USB pins are located on separate pads and are not controlled through the SCU.

In addition, the clock delay register for the SDRAM EMC\_CLK pins and the registers that select the pin interrupts are located in the SCU.

#### 7.20.3 Clock Generation Unit (CGU)

The Clock Generator Unit (CGU) generates several base clocks. The base clocks can be unrelated in frequency and phase and can have different clock sources within the CGU. One CGU base clock is routed to the CLKOUT pins. The base clock that generates the CPU clock is referred to as CCLK.

Multiple branch clocks are derived from each base clock. The branch clocks offer flexible control for power-management purposes. All branch clocks are outputs of one of two Clock Control Units (CCUs) and can be controlled independently. Branch clocks derived from the same base clock are synchronous in frequency and phase.

#### 7.20.4 Internal RC oscillator (IRC)

The IRC is used as the clock source for the WWDT and/or as the clock that drives the PLLs and the CPU. The nominal IRC frequency is 12 MHz. The IRC is trimmed to 1.5 % accuracy for  $T_{amb} = 0$  °C to 85 °C and 3% accuracy for  $T_{amb} = -40$  °C to 0 °C and  $T_{amb} = 85$  °C to 105 °C.

Upon power-up or any chip reset, the LPC185x/3x/2x/1x use the IRC as the clock source. The boot loader then configures the PLL1 to provide a 96 MHz clock for the core and the PLL0USB or PLL0AUDIO as needed if an external boot source is selected.

#### 7.20.5 PLL0USB (for USB0)

PLL0 is a dedicated PLL for the USB0 High-speed controller.

PLL0 accepts an input clock frequency from an external oscillator in the range of 14 kHz to 25 MHz. The input frequency is multiplied up to a high frequency with a Current Controlled Oscillator (CCO). The CCO operates in the range of 4.3 MHz to 550 MHz.

#### 7.20.6 PLL0AUDIO (for audio)

The audio PLL PLL0AUDIO is a general-purpose PLL with a small step size. This PLL accepts an input clock frequency derived from an external oscillator or internal IRC. The input frequency is multiplied up to a high frequency with a Current Controlled Oscillator (CCO). A sigma-delta converter modulates the PLL divider ratios to obtain the desired

LPC185X 3X 2X 1X

32-bit ARM Cortex-M3 microcontroller

### 8. Limiting values

#### Table 7. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134).[1]

| Symbol                    | Parameter                             | Conditions                                                                |     | Min  | Max                   | Unit |

|---------------------------|---------------------------------------|---------------------------------------------------------------------------|-----|------|-----------------------|------|

| V <sub>DD(REG)(3V3)</sub> | regulator supply voltage (3.3 V)      | on pin VDDREG                                                             |     | -0.5 | 3.6                   | V    |

| V <sub>DD(IO)</sub>       | input/output supply voltage           | on pin VDDIO                                                              |     | -0.5 | 3.6                   | V    |

| V <sub>DDA(3V3)</sub>     | analog supply voltage<br>(3.3 V)      | on pin VDDA                                                               |     | -0.5 | 3.6                   | V    |

| V <sub>BAT</sub>          | battery supply voltage                | on pin VBAT                                                               |     | -0.5 | 3.6                   | V    |

| V <sub>prog(pf)</sub>     | polyfuse programming voltage          | on pin VPP                                                                |     | -0.5 | 3.6                   | V    |

| VI                        | input voltage                         | when $V_{DD(IO)} \ge 2.4 \text{ V}$<br>5 V tolerant digital I/O pins      | [2] | -0.5 | 5.5                   | V    |

|                           |                                       | ADC/DAC pins and digital I/O<br>pins configured for an analog<br>function |     | -0.5 | V <sub>DDA(3V3)</sub> | V    |

|                           |                                       | USB0 pins USB0_DP;<br>USB0_DM; USB0_VBUS                                  |     | -0.3 | 5.2                   | V    |

|                           |                                       | USB0 pins USB0_ID;<br>USB0_RREF                                           |     | -0.3 | 3.6                   | V    |

|                           |                                       | USB1 pins USB1_DP and USB1_DM                                             |     | -0.3 | 5.2                   | V    |

| I <sub>DD</sub>           | supply current                        | per supply pin                                                            | [3] | -    | 100                   | mA   |

| I <sub>SS</sub>           | ground current                        | per ground pin                                                            | [3] | -    | 100                   | mA   |

| l <sub>latch</sub>        | I/O latch-up current                  | $-(0.5V_{DD(IO)}) < V_I < (1.5V_{DD(IO)});$<br>T <sub>j</sub> < 125 °C    |     | -    | 100                   | mA   |

| T <sub>stg</sub>          | storage temperature                   |                                                                           | [4] | -65  | +150                  | °C   |

| P <sub>tot(pack)</sub>    | total power dissipation (per package) | based on package heat transfer,<br>not device power consumption           |     | -    | 1.5                   | W    |

| V <sub>ESD</sub>          | electrostatic discharge voltage       | human body model; all pins                                                | [5] | -    | 2000                  | V    |

[1] The following applies to the limiting values:

a) This product includes circuitry designed for the protection of its internal devices from the damaging effects of excessive static charge. Nonetheless, it is suggested that conventional precautions be taken to avoid applying greater than the rated maximum.

b) Parameters are valid over operating temperature range unless otherwise specified. All voltages are with respect to V<sub>SS</sub> unless otherwise noted.

- [2] Including voltage on outputs in 3-state mode.

- [3] The peak current is limited to 25 times the corresponding maximum current.

- [4] Dependent on package type.

- [5] Human body model: equivalent to discharging a 100 pF capacitor through a 1.5 k $\Omega$  series resistor.

#### 32-bit ARM Cortex-M3 microcontroller

LPC185X\_3X\_2X\_1X

32-bit ARM Cortex-M3 microcontroller

### 10.4 BOD and band gap static characteristics

#### Table 13. BOD static characteristics<sup>[1]</sup>

$T_{amb} = 25 \ ^{\circ}C$ ; simulated values for nominal processing.

| Symbol          | Parameter         | Conditions        | Min | Тур  | Max | Unit |

|-----------------|-------------------|-------------------|-----|------|-----|------|

| V <sub>th</sub> | threshold voltage | interrupt level 2 |     |      |     |      |

|                 |                   | assertion         | -   | 2.95 | -   | V    |

|                 |                   | de-assertion      | -   | 3.03 | -   | V    |

|                 |                   | interrupt level 3 |     |      |     |      |

|                 |                   | assertion         | -   | 3.05 | -   | V    |

|                 |                   | de-assertion      | -   | 3.13 | -   | V    |

|                 |                   | reset level 2     |     |      |     |      |

|                 |                   | assertion         | -   | 2.1  | -   | V    |

|                 |                   | de-assertion      | -   | 2.18 | -   | V    |

|                 |                   | reset level 3     |     |      |     |      |

|                 |                   | assertion         | -   | 2.2  | -   | V    |

|                 |                   | de-assertion      | -   | 2.28 | -   | V    |

[1] Interrupt and reset levels are selected by writing to the BODLV1/2 bits in the control register CREGE0, see the LPC18xx user manual.

#### Table 14. Band gap characteristics

$V_{DDA(3V3)}$  over specified ranges;  $T_{amb} = -40 \degree C$  to +105  $\degree C$ ; unless otherwise specified

| Symbol               | Parameter                  |     | Min   | Тур   | Max   | Unit |

|----------------------|----------------------------|-----|-------|-------|-------|------|

| V <sub>ref(bg)</sub> | band gap reference voltage | [1] | 0.707 | 0.745 | 0.783 | mV   |

[1] Based on characterization, not tested in production.

LPC185X\_3X\_2X\_1X

#### 32-bit ARM Cortex-M3 microcontroller

### 11.4 Crystal oscillator

#### Table 19. Dynamic characteristic: oscillator

$T_{amb} = -40 \text{ }^{\circ}\text{C} \text{ to } +105 \text{ }^{\circ}\text{C}; V_{DD(IO)} \text{ over specified ranges}; 2.4 \text{ V} \le V_{DD(REG)(3V3)} \le 3.6 \text{ V}.$

| Symbol                                       | Parameter           | Conditions     |        | Min | Typ[2] | Max | Unit |  |  |  |  |

|----------------------------------------------|---------------------|----------------|--------|-----|--------|-----|------|--|--|--|--|

| _ow-frequency mode (1-20 MHz) <sup>[5]</sup> |                     |                |        |     |        |     |      |  |  |  |  |

| t <sub>jit(per)</sub>                        | period jitter time  | 5 MHz crystal  | [3][4] | -   | 13.2   | -   | ps   |  |  |  |  |

|                                              |                     | 10 MHz crystal |        | -   | 6.6    | -   | ps   |  |  |  |  |

|                                              |                     | 15 MHz crystal |        | -   | 4.8    | -   | ps   |  |  |  |  |

| High-freq                                    | uency mode (20 - 25 | MHz)[6]        |        |     |        |     |      |  |  |  |  |

| t <sub>jit(per)</sub>                        | period jitter time  | 20 MHz crystal | [3][4] | -   | 4.3    | -   | ps   |  |  |  |  |

|                                              |                     | 25 MHz crystal |        | -   | 3.7    | -   | ps   |  |  |  |  |

[1] Parameters are valid over operating temperature range unless otherwise specified.

- [2] Typical ratings are not guaranteed. The values listed are at room temperature (25 °C), nominal supply voltages.

- [3] Indicates RMS period jitter.

- [4] PLL-induced jitter is not included.

- [5] Select HF = 0 in the XTAL\_OSC\_CTRL register.

- [6] Select HF = 1 in the XTAL\_OSC\_CTRL register.

### 11.5 IRC oscillator

#### Table 20. Dynamic characteristic: IRC oscillator

$2.4 \text{ V} \le \text{V}_{DD(REG)(3V3)} \le 3.6 \text{ V}$

| Symbol               | Parameter                                 | Conditions                                   | Min          | Typ <u>[1]</u> | Max          | Unit |

|----------------------|-------------------------------------------|----------------------------------------------|--------------|----------------|--------------|------|

| f <sub>osc(RC)</sub> |                                           | -40 °C $\leq$ T <sub>amb</sub> $<$ 0 °C      | 12.0 - 3 %   | 12.0           | 12.0 + 3 %   | MHz  |

|                      | oscillator<br>frequency                   | $0~^{\circ}C \leq T_{amb} \leq 85~^{\circ}C$ | 12.0 - 1.5 % | 12.0           | 12.0 + 1.5 % | MHz  |

| nequency             | $85~^\circ C < T_{amb} \leq 105~^\circ C$ | 12.0 - 3 %                                   | 12.0         | 12.0 + 3 %     | MHz          |      |

Typical ratings are not guaranteed. The values listed are at room temperature (25 °C), nominal supply voltages.

### 11.6 RTC oscillator

See Section 13.3 for connecting the RTC oscillator to an external clock source.

#### Table 21. Dynamic characteristic: RTC oscillator

$T_{amb} = -40 \text{ °C to } +105 \text{ °C}; 2.4 \text{ V} \le V_{DD(REG)(3V3)} \le 3.6 \text{ V or } 2.4 \text{ V} \le V_{BAT} \le 3.6 \text{ V}_{emb}^{[1]}$

| Symbol               | Parameter                    | Conditions | Min | Typ <u>[1]</u> | Мах | Unit |

|----------------------|------------------------------|------------|-----|----------------|-----|------|

| fi                   | input frequency              | -          | -   | 32.768         | -   | kHz  |

| I <sub>CC(osc)</sub> | oscillator supply<br>current |            |     | 280            | 800 | nA   |

[1] Parameters are valid over operating temperature range unless otherwise specified.

[2] Typical ratings are not guaranteed. The values listed are at room temperature (25 °C), nominal supply voltages.

32-bit ARM Cortex-M3 microcontroller

LPC185X\_3X\_2X\_1X

#### 32-bit ARM Cortex-M3 microcontroller

#### Table 27. Dynamic characteristics: SSP pins in SPI mode

$T_{amb} = -40 \degree C$  to +105  $\degree C$ ; 2.4 V  $\leq V_{DD(REG)(3V3)} \leq 3.6$  V; 2.7 V  $\leq V_{DD(IO)} \leq 3.6$  V;  $C_L = 20 \text{ pF}$ ; sampled at 10 % and 90 % of the signal level; EHS = 1 for all pins. Simulated values.

| Symbol               | Parameter  | Conditions                       | Min                              | Тур                             | Max | Unit |

|----------------------|------------|----------------------------------|----------------------------------|---------------------------------|-----|------|

| t <sub>lag</sub> lag | lag time   | continuous transfer mode         | 0.5 x T <sub>cy(clk)</sub> + 1.5 | -                               | -   | ns   |

|                      |            | SPI mode; CPOL = 0;<br>CPHA = 0  |                                  |                                 |     |      |

|                      |            | SPI mode; CPOL = 0;<br>CPHA = 1  | T <sub>cy(clk)</sub> + 1.5       | -                               | -   | ns   |

|                      |            | SPI mode; CPOL = 1;<br>CPHA = 0  | $0.5 	imes T_{cy(clk)} + 1.5$    | -                               | -   | ns   |

|                      |            | SPI mode; CPOL = 1;<br>CPHA = 1  | $T_{cy(clk)}$ + 1.5              | -                               | -   | ns   |

|                      |            | synchronous serial frame mode    | T <sub>cy(clk)</sub> + 1.5       | -                               | -   | ns   |

|                      |            | microwire frame format           | $0.5\times T_{cy(clk)}$          | -                               | -   | ns   |

| t <sub>d</sub>       | delay time | continuous transfer mode         | -                                | $0.5\times T_{cy(clk)}$         | -   | ns   |

|                      |            | SPI mode; CPOL = 0;<br>CPHA = 0  |                                  |                                 |     |      |

|                      |            | SPI mode; CPOL = 0;<br>CPHA = 1  | -                                | n/a                             | -   | ns   |

|                      |            | SPI mode; CPOL = 1;<br>CPHA = 0  | -                                | $0.5 \times T_{\text{cy(clk)}}$ | -   | ns   |

|                      |            | SPI mode; CPOL = 1;<br>CPHA = 1  | -                                | n/a                             | -   | ns   |

|                      |            | synchronous serial<br>frame mode | -                                | T <sub>cy(clk)</sub>            | -   | ns   |

|                      |            | microwire frame format           | -                                | n/a                             | -   | ns   |

[1]  $T_{cy(clk)} = (SSPCLKDIV \times (1 + SCR) \times CPSDVSR) / f_{main}$ . The clock cycle time derived from the SPI bit rate  $T_{cy(clk)}$  is a function of the main clock frequency  $f_{main}$ , the SSP peripheral clock divider (SSPCLKDIV), the SSP SCR parameter (specified in the SSP0CR0 register), and the SSP CPSDVSR parameter (specified in the SSP clock prescale register).

### **NXP Semiconductors**

## LPC185x/3x/2x/1x

#### 32-bit ARM Cortex-M3 microcontroller

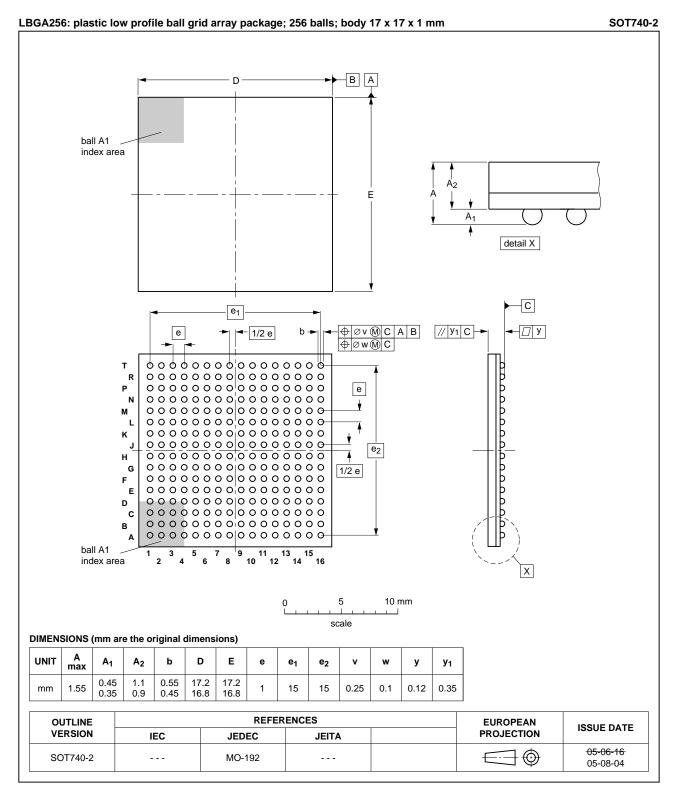

### 14. Package outline

All information provided in this document is subject to legal disclaimers.

LPC185X 3X 2X 1X

#### 32-bit ARM Cortex-M3 microcontroller

Table 44. Abbreviations ... continued

| Acronym | Description                                             |

|---------|---------------------------------------------------------|

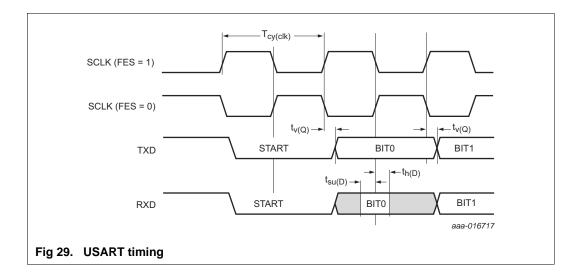

| USART   | Universal Synchronous Asynchronous Receiver/Transmitter |

| USB     | Universal Serial Bus                                    |

| UTMI    | USB 2.0 Transceiver Macrocell Interface                 |

### 17. References

- [1] LPC18xx User manual UM10430: http://www.nxp.com/documents/user\_manual/UM10430.pdf

- [2] LPC18xx Errata sheet: http://www.nxp.com/documents/errata\_sheet/ES\_LPC18XX.pdf

### 32-bit ARM Cortex-M3 microcontroller

| Document ID          | Release date         Data sheet status         Change notice         Supersedes                                                                                                                                    |  |  |  |  |  |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Modifications:       | <ul> <li>Parameter t<sub>ret</sub> (retention time) for EEPROM updated in Table 15.</li> </ul>                                                                                                                     |  |  |  |  |  |

|                      | <ul> <li>Parameter V<sub>DDA(3V3)</sub> added for pins USB0_VDDA3V3_DRIVER and<br/>USB0_VDDA3V3 in Table 11.</li> </ul>                                                                                            |  |  |  |  |  |

|                      | <ul> <li>Parameter name I<sub>DD(ADC)</sub> changed to I<sub>DDA</sub> in Table 11.</li> </ul>                                                                                                                     |  |  |  |  |  |

|                      | <ul> <li>Minimum wake-up time from sleep mode added in Table 16.</li> </ul>                                                                                                                                        |  |  |  |  |  |

|                      | <ul> <li>Data for I<sub>DD(IO)</sub> added in Table 11.</li> </ul>                                                                                                                                                 |  |  |  |  |  |

|                      | <ul> <li>Data sheet status changed to Product data sheet.</li> </ul>                                                                                                                                               |  |  |  |  |  |

|                      | <ul> <li>IRC specifications corrected in Table 19 "Dynamic characteristic: IRC oscillator" and<br/>Section 2: Accuracy changed to +/- 3 % over the entire temperature range.</li> </ul>                            |  |  |  |  |  |

|                      | Bandgap characteristics removed.                                                                                                                                                                                   |  |  |  |  |  |

|                      | <ul> <li>Section 13.7 "Suggested USB interface solutions" added.</li> </ul>                                                                                                                                        |  |  |  |  |  |

|                      | <ul> <li>I<sub>DD(REG)(3V3)</sub> updated in Table 11 "Static characteristics" for the following conditions:</li> </ul>                                                                                            |  |  |  |  |  |

|                      | - Active mode: CCLK = 12 MHz; $I_{DD(REG)(3V3)}$ changed from 9.3 mA to 10 mA.                                                                                                                                     |  |  |  |  |  |

|                      | - Active mode: CCLK = 60 MHz; $I_{DD(REG)(3V3)}$ changed from 26 mA to 28 mA.                                                                                                                                      |  |  |  |  |  |

|                      | - Active mode: CCLK = 120 MHz; $I_{DD(REG)(3V3)}$ changed from 46 mA to 51 mA.                                                                                                                                     |  |  |  |  |  |

|                      | - Active mode: CCLK = 180 MHz; $I_{DD(REG)(3V3)}$ changed from 66 mA to 74 mA.                                                                                                                                     |  |  |  |  |  |

|                      | - Sleep mode: CCLK = 12 MHz; $I_{DD(REG)(3V3)}$ changed from 6.2 mA to 8.8 mA.                                                                                                                                     |  |  |  |  |  |